Professional Documents

Culture Documents

500W High Efficiency Switched-Tank Converter (STC) Reference Design Based On STNRG328S and STPRDC02A For 54V Bus Conversion in Server Application

Uploaded by

GanapathiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

500W High Efficiency Switched-Tank Converter (STC) Reference Design Based On STNRG328S and STPRDC02A For 54V Bus Conversion in Server Application

Uploaded by

GanapathiCopyright:

Available Formats

AN5810

Application note

500W high efficiency switched-tank converter (STC) reference design based on

STNRG328S and STPRDC02A for 54V bus conversion in server application

Introduction

This application note describes the 54 V input, 13.5 V unregulated output (54 V divided by 4), 500 W, 98% efficient, switched-

tank converter based on the STNRG328S digital controller and four STPRDC02A full bridge MOSFET drivers tailored to a

typical 12 V bus generation in computer and server applications.

The STC is an open loop resonant converter that performs a power conversion from an input voltage to an output voltage with

a fixed duty cycle. The zero current detection feature allows synchronization with the real resonant LC frequently in case of full

X7R capacitors used.

The power section scheme is composed of an LC resonant network, flying MOSFETs and rectification MOSFETs driven by four

STPRDC02A full bridge MOSFET drivers with ZCD.

The STNRG328S is a “State Machine Event Driven” (SMED) digital controller and it implements the STC control strategy and

the necessary functions. Various control actions are required to ensure the proper architecture behavior and best performances

with ZCD (Zero Current Detection).

Additional components have been used to implement the functions controlled by the SMED digital engine (drivers, hot swap,

charge pump, etc.). Populating passive power components only on the top side for 500 W, instead of both sides for 1 KW.

Figure 1. 500W, ⅛ brick STC converter

AN5810 - Rev 1 - February 2023 www.st.com

For further information contact your local STMicroelectronics sales office.

AN5810

Main features and circuit description

1 Main features and circuit description

Table 1. Main features

Parameter Value

From 40V up to 60V – Typical operative range: 54V

Input range

Absolute maximum rating = 62V

Output voltage 13.5V at 45A, ~ 600W continues, 900Wpk operation at 54V input

Peak efficiency 98% at 54V input

Efficiency

Max. load efficiency 97.4% at 54V input

Typ. operative switching frequency Variable within 140kHz to 300kHz

1.4” x 2.3” (4 to 1 conversion evaluation board)

Dimensions

0.8” x 2” x 0.5 (active area)

PCB 10 layers (2 oz)

The STC principle schematic is shown in Figure 2.

In first approximation, the circuit operates with just one PWM signal:

• TON phase: RED FETs are ON and BLUE FETs are OFF (Figure 3)

• TOUT phase: RED FETs are OFF and BLUE FETs are ON (Figure 4)

To better understand the STC functionality, as a first step let us consider L = 0 and Iout = 0. In this case, the STC

behaves like a Charge Pump and the capacitors behave like a voltage generator → C ≈ Voltage Generator, see

Figure 5.

The relation between VIN and VOUT is obtained solving the equations that describe the circuit in Figure 5 (L = 0

and IOUT = 0):

V

Vout = 4in (1)

The inductors L1 and L2 are required to create the resonance and to allow the commutation of the FETs at

Zero Current (ZCS). The ZCS is guaranteed if the switching frequency of the STC is equal to the LC resonance

frequency.

FSWnom = 1 (2)

2 π Lres ∙ Cres + Tdead

Using U2J capacitors the CF>>CR (CR = Cres)

Figure 2. STC principle schematic

AN5810 - Rev 1 page 2/45

AN5810

Main features and circuit description

Figure 3. Ton phase

IOUT = IL1+ IL2

Figure 4. TOFF phase

IOUT = IL1+ IL2

Figure 5. STC concept

The output current is the sum of the current in the inductors L1 and L2 as shown in Figure 3 and in Figure 4.

Therefore, the peak current in the inductors is:

I

IL_peak = out π

2 ∙2 (3)

To avoid instability, condition the saturation current in the inductor must be higher than the maximum inductor

peak current:

IL_sat ≫ IL i . e . IL > 1.3 ∙ IL_peak (4)

peak sat

About the resonant capacitor, the maximum peak voltage on C3 must be lower than the minimum VOUT to avoid

negative nodes:

IL_peak LRES

VC_peak =

ω ∙ CRES = IL_peak ∙ CRES < Voutmin

(5)

AN5810 - Rev 1 page 3/45

AN5810

Main features and circuit description

Instead of using U2J, this rev 2 of demo focuses on X7R capacitor and the above rules change. CF and CR are

comparable and the total capacitance is the parallel of CF and CR . STC configurations tested reported in Table 2.

Table 2. STC tested configurations

POUT fsw CIN CRES LRES Creservior

1Res : 10 * 4.7uF _50V

GRM31CR71H475KA1

2L

12 *10uF _100V Double

8*0.47µH/ 12* 10uF_50V

Variable GRM32EC72A106KE0 phase25.92µF@54V inductor

GRM32ER71H106KA1

5L 33.85µF@40V 56nH per phase @ 2L

600W 140kHz

33.6uF@54V 600W

280Khz 72.8uF @54V

2 Res: 13 * 4.7uF _25V

46.2uF@40V or double 56nH/phase

88.2uF @40V

TMK212AB7475KG @ 1KW

19.8uF@54V

25.2uF@40V

Figure 6 and Figure 7 show STC simulations in case of POUT = 500W and VIN = 54V.

Figure 6. STC simulation POUT = 500 W and VIN = 54 V → main STC nodes

AN5810 - Rev 1 page 4/45

AN5810

Main features and circuit description

Figure 7. STC simulation POUT = 500 W and VIN = 54 V → C voltage & L current

The resonant current is always null at the end of every cycle, thanks to the ZCD information from the driver

STPRDC02A, the controller STNRG algorithm adjusts the switching frequency and the deadtime according to

both branches, allowing the MOSFETs to commutate in zero current switching mode.

At light load the ZCD logic is blind due to lack of current information, but above 10 A the loop starts working and

the switching freq is lowered and the deadtime is shorted.

X7R capacitors vary more than 40% with bias voltage/temperature and inductor accuracy is around 10%; the

STNRG controller modifies the Switching Freq and deadtime accordingly and in real-time.

AN5810 - Rev 1 page 5/45

AN5810

STC power section & drivers

2 STC power section & drivers

ICs STC power section is managed by four STPRDC02A that provide high current driving for the Flying MOSFETs

(Q1, Q2, Q3 and Q4 in Figure 2) and Rectification MOSFETs (Q5, Q6, Q7, Q8, Q9 and Q10 in Figure 2) as

well as input current monitoring and protection. Floating drivers are needed for the flying MOSFETs while ground

referred drivers are needed for the rectification MOSFETs.

The STPRDC02A is a 75 V, high voltage, full bridge MOSFET driver IC. It provides four high current gate drive

outputs, each capable of driving one or more N-channel power MOSFETs.

The device features programmable deadtime control to optimize MOSFETs switching losses, so optimizing the

overall efficiency. Translating the ZVD parasitic diode information on the X driver side to a logic information by

ZVCX_OUT pin 13 (on previous driver was called FAULT pin) allows HIZ management by the EN driver pin during

the deadtime period.

Based on Config pin level, the two PWM inputs control the two half-bridge sections independently. The driver EN

pin, when low, forces all the gate drive to low regardless of the PWMs status implementing a HiZ. This is used

in deadtime. The driver also allowed to detect ZCD in the resonant component. The ZCD information is useful for

the STNRG328S frequency management.

Figure 8. Rectification MOSFETs driver section

AN5810 - Rev 1 page 6/45

AN5810

STC power section & drivers

Figure 9. Floating MOSFETs driver section

AN5810 - Rev 1 page 7/45

AN5810

STC digital control engine

3 STC digital control engine

The STNRG328S, a “State Machine Event Driven” (SMED) digital architecture (see Figure 2), is used to

implement the STC control strategy and the necessary functions. Some key control features are required to

perform an efficient and reliable power conversion function. The most important feature set is summarized below:

• Initial set-up

• Current limit in combination with hot swap controller

• Operating input voltage window

• Conversion ration control

• PWM frequency and deadtime management to guarantee ZCD

• Soft-start control

• Driver section

• Temperature control

Figure 10. SMED digital engine STNRG328S block diagram

The STNRG328S can be programmed by SWIM bus (IAR debugger) or just using a UART bus to download the

firmware (refer to STNRG328S Upgrade Firmware Procedure). PMBUs is only used for telemetry and parameter

tuning.

AN5810 - Rev 1 page 8/45

AN5810

STC digital control engine

Table 3. Pin12 cpp0

Pin12 Cpp0 allows to configure initial setting: Ratio/Freq:

Config. Board Ratio V_CPP0 Freq.SW (kHz)

0 STC 4:1 41mV ZCD

1 STC 3:1 123mV ZCD

2 STC 2:1 205mV ZCD

3 STC 2:1 287mV 330

4 STC 2:1 369mV 360

5 STC 3:1 451mV 330

6 STC 4:1 533mV 330

7 STC 4:1 615mV 360

8 HSTC 4:1 697mV 390

9 HSTC 4:1 779mV 180

10 HSTC 5:1 861mV 200

11 HSTC 5:1 943mV 500

12 HSTC 6:1 1025mV 180

13 HSTC 8:1 1107mV 180

14 HSTC 10:1 1189mV 180

Table 4. Resistors setting for cpp0 configurations

Config. board Ratio Rup Rdown VCppo,PART,CALC

0 4:1 - - -

1 3:1 145K 11K 126,9mV

2 2:1 91K 12K 209,7mV

3 2:1 54K 10K 281mV

4 2:1 77K 20K 371mV

5 3:1 300K 100K 450mV

6 4:1 210K 90K 540mV

7 4:1 200K 100K 599mV

8 4:1 150K 697mV 724mV

9 4:1 130K 100K 782,6mV

10 5:1 110K 100K 857mV

11 5:1 91K 100K 942mV

12 6:1 75K 100K 1028mV

13 8:1 62K 100K 1111mV

14 10:1 51K1 100K 1191mV

For setting a different configuration than 4:1 with ZCD, it is enough to change the default pull-down resistor value

RdwOut at Vout resistor divider, and to never change the input resistors divider that is tuned for accurate input

voltage telemetry reading.

AN5810 - Rev 1 page 9/45

AN5810

STC digital control engine

Table 5. Ration & RdwOut 1

Ratio Rdonw

2:1 650 Ω

3:1 950 Ω

4:1 1200 Ω

5:1 1500 Ω

6:1 1700 Ω

8:1 2500 Ω

10:1 3500 Ω

Figure 11. Ration & RdwOut 2

STC supervisory state machine implemented by firmware in the main loop is reported below in Figure 12.

AN5810 - Rev 1 page 10/45

AN5810

STC digital control engine

Figure 12. STC state machine

Elapsed WAIT_TIME

PWR UP (100msec)? No

POWER_UP Acquisition ADC Stable

Acquisition DIGIN0

Stabilization Vin Yes

Initialization ST INIT F switching

Peripheral ST_WAIT

I2C bus PWR UP

Ratio

DIGIN0 HIGH? No

DIGIN0 HIGH? No

ST_CHN

PWR UP

ST_OFF Yes

DIGIN0 HIGH?

DIGIN0 HIGH? Yes

Vout HOTSWAP Record and Clear UVP,OVP,OCP, Thermal flags

< 10V? Yes

Disable PWM0

DIGIN0 LOW? Yes

& PMW01 DIGIN0 LOW

or UVP or OVP or OCP or HS OC or

thermal ?

Yes Vin > or = 60V?

Disable

HOT SWAP Yes

ST_Vin ST_Vin Vin < 44V?

No ST_SHUT OUT OF START UP

DOWN RANGE No

Vin < or =58V?

DIGIN0 LOW? Yes

DIGIN0 LOW Yes

Vin >60V? (Vin > or =

or UVP or OVP Vin < or =58V?

Yes 44V) ? Yes

PWM01 or OCP or HS Yes

Yes Disable

Disable OC or thermal ? Enable ST_VOUT Check HS and

HOT SWAP

Vin<10V? Disable SMED 4&5 HOT SWAP START UP Enable PWM0

Disable HOT SWAP & PMW1

Yes

Vin < 40V?

Yes Vout > or = 2V? No

Disable SMED 4&5

ST_ON

& Disable HOT SWAP

ST_UVLO ZCD (Vout < 2V) ? Yes

Vin > or = 48V ?

No Enable SMED 4&5 & Enable HOT SWAP

DIGIN0 LOW

Vin > or = 44V ? 1

or UVP or OVP or OCP , HS OC ,

Yes

thermal P ? No

Enable HS

1. Current limit

– Current limit provides the protection to the circuit during normal operations and during potential

overload of the output. An upstream hot swap device drives the digital engine. The hot swap has

the function to disconnect the input from the STC block in the event of an overload, thus protecting

the downstream circuitry. A current limit function for the 1 kW brick is based either on the inductor

DCR (for the LTC7801), or the on-resistance of the STEF48H, depending on evaluation version. The

STNRG keeps hot swap in latched condition.

2. Operating input voltage window

– STC input voltage (40 V to 60 V) has to be constantly monitored to ensure that the unregulated

output voltage is between the desired values. If input voltage falls outside the predefined boundaries,

the STC system is disconnected from the input voltage bus through the hot swap device.

3. VIN/VOUT ratio control

– Conversion ratio control: since the systems works on a fixed VIN/VOUT ratio, defined by the

hardware structure (that is, the number of C-L/C legs implemented) an accurate control of this ratio is

necessary to ensure that the output voltage is not deviating from the target value. If this happens, the

activity is suspended, the hot swap is opened and a fault signal is asserted.

4. PWM frequency control

– In ST_ON state, the accuracy of the PWM frequency is an important parameter to ensure the

matching with the LC resonant tank and thus an optimum efficiency performance and VOUT control.

This feature is implemented through an adaptive control strategy. PWM frequency and deadtime is

programmed by PMBus® setting the minimum and maximum range to ensure a good resonance

in the LC resonant tank, in ZCD setting the min. and max. freqency and deadtime are reported in

Table 6.

AN5810 - Rev 1 page 11/45

AN5810

STC digital control engine

5. Temperature control

– Temperature control is an important variable to monitor due to the application high power density

(~200W/in2) and the power flowing through the STC structure. Components’ temperature could rise

in case of overload.

The STNRG328S could also monitor 2 NTC temperature sensing points by adding a dual selector

(74LVC2G14GV) driven by pin 6 and ADC0 is the only one to read both the NTCs at different period

(few Sec).

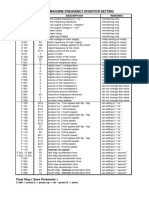

Table 6. PWM frequency control

# Vin Vin_Entry Vin_Exit FREQ_min FREQ_max DEAD_Time_min DEAD_Time_max

0 41 39.5 42.5 0x0067 0x00E4 0x0004 0x001E

1 42 40.5 43.5 0x006A 0x00E7 0x0003 0x001E

2 43 41.5 44.5 0x006D 0x00EA 0x0004 0x001D

3 44 42.5 45.5 0x0071 0x00ED 0x0003 0x001D

4 45 43.5 46.5 0x0074 0x00F1 0x0004 0x001C

5 46 44.5 47.5 0x0077 0x00F4 0x0003 0x001C

6 47 45.5 48.5 0x007A 0x00F7 0x0004 0x001B

7 48 46.5 49.5 0x007D 0x00FA 0x0003 0x001B

8 49 47.5 50.5 0x0081 0x00FD 0x0004 0x001B

9 50 48.5 51.5 0x0084 0x0101 0x0003 0x001A

10 51 49.5 52.5 0x0087 0x0104 0x0004 0x001A

11 52 50.5 53.5 0x008A 0x0107 0x0003 0x001A

12 53 51.5 54.5 0x008D 0x010A 0x0004 0x0019

13 54 52.5 55.5 0x0091 0x010D 0x0003 0x0019

14 55 53.5 56.5 0x0094 0x0111 0x0004 0x0019

15 56 54.5 57.5 0x0097 0x0114 0x0003 0x0018

16 57 55.5 58.5 0x009A 0x0117 0x0004 0x0018

17 58 56.5 59.5 0x009D 0x011A 0x0003 0x0018

18 59 57.5 60.5 0x009D 0x011A 0x0004 0x0018

AN5810 - Rev 1 page 12/45

AN5810

STC digital control engine

Figure 13. Digital engine STNRG328S section

AN5810 - Rev 1 page 13/45

AN5810

Hot swap

3.1 Hot swap

The hot swap function using an input buck regulator is shown in Figures 14 and 15.

The input buck regulator acts as an eFuse (electronic fuse) limiting the inrush current and the output voltage slew

rate for a smooth soft-start of STC output voltage.

The STC is a very fast converter and requires a smooth input voltage edge to avoid huge inrush current.

The STNRG controller controls the hot swap enable pin to manage the power ON and OFF sequence.

Two options for a hot swap solution have been evaluated (TI and LTC):

Figure 14. Input section A

TI _Hot swap

Figure 15. Input section B

LTC ( dcdc with 100% duty)

AN5810 - Rev 1 page 14/45

AN5810

Auxiliary power

3.2 Auxiliary power

The connection of external voltage sources 5 V is required before the application of the input voltage.

After the output voltage ramps, PM6644 rises 5 V to 7 V for efficiency improvement and for bigger MOSFET

commutation (if needed) and thus the external 5 V current drops to zero. The VDRIVER is the output of ext. 5 V

and PM6644 OR’diode. The other 3.3 V rail required to supply STNRGs is generated by an LDO (LDK220) from

VDRIVER.

3.3 Startup sequence

Apply 5 V and 3.3 V prior to input voltage. The STNRG328S wakes up and as soon as the STC enable signal

(STC EN) arrives, it enables the soft-start of the input buck and turns on the STC. The STC output voltage

follows the soft-start of the input buck output as shown in Figure 18. During the soft-start, the ZCD algorithm

starts working in order to synchronize the external resonant LC with its own internal logic starting from the max.

frequency allowed. Upon the end of STC output voltage ramping, PGOOD is asserted within several mS.

Note: 1

PGOOD signal is pulled up through a resistor divider ( 4.3 ) from the VOUT. Therefore, its high voltage level is:

VOUT

4.3 (6)

Table 7. PGOOD

Min. Type Max.

NAME

(VIN = 40V) (VIN = 54V) (VIN = 60V)

PGOOD high level 2.3V 3.1V 3.5V

Prior to applying an input voltage VIN to the evaluation board, external voltages 5 V and 3.3 V are highly

recommended to connect first, as illustrated in Figure 18.

AN5810 - Rev 1 page 15/45

AN5810

Design guidelines with special focus on the inductor and capacitor selections

Figure 16. Startup sequence with EN STC asserted after VIN

3.4 Design guidelines with special focus on the inductor and capacitor selections

A good inductor and capacitor selection is fundamental to maintain system performances (efficiency and power

delivery).

The flying (CF) can be a Class II (X7R) capacitor since it works like a DC voltage source with minimum AC

voltage ripple. In this case, the higher tolerance of the Class II does not affect the performance of the STC due to

frequency variation thank to the ZCD feature.

The rules for the X7R capacitor selection are:

1. To match the total Cap required for matching the resonant Freq in all 4 resonant periods.

2. To consider the variation of capacitance at different Input voltage.

3. To choose adequate breakdown voltage of capacitors (each branch has different voltage applied).

4. To verify the total RMS current of each current path based on the output current.

5. To select capacitors with very low ESR (few mOhm max.).

AN5810 - Rev 1 page 16/45

AN5810

Design guidelines with special focus on the inductor and capacitor selections

Table 8. Suggested pin to pin capacitors part numbers

Name Nbr Part nbr

1 Murata GRM31CR71H475KA12L

Cres 1 2 Samsung CL31B475KBHN3NE

3 TDK C3216X7R1H475K160AC

1 Murata GRM32ER71H106KA12L

Creservior 2 TDK CNA6P1X7R1H106K250AE

3 AVX 12105C106KAT2A

1 Samsung CL21B225KAFNNNF

2 AVX 08053C225KAT2A

Cres 2

3 Taiyo Yuden TMK212AB7475KG

4 (7uF)

1 Murata GRM32EC72A106KE05

2 Taiyo Yuden HMK325C7475KM-PE

Cin

4 (7uF)

2 Samsung CL32B475KCVZ3WE (4uF)

Spreadsheet used for 500 W design

Table 9. Equivalent resonant capacitances

Typ.val Quantit Tot Tot C Tot C

Name 54V 48V 40V A each Tot 54V

ue y current 48V 40V

Cres 1 4.7 1.62 2.116 10 3.42 34.2 16.2 21.16

Creservior 10 5.2 6.3 12 5 60 62.4 75.6

Cres 2 2.2 1.1 1.4 13 3 39 14.3 18.2

Cin 10 2.4 3.3 12 4 48 28.8 39.6

C equivalent 54 V 48 40

12.643 16.698

Cres 1A

9 6

14.668

Cres 2A 11.6339

7

16.532

Cres 1B 12.8611

6

Cres 2B 14.3 18.2

2.14E+

Fres_res1 =

05

2.04E+

Freq_res2 =

05

While the characteristic of the resonant inductor LR must be flat up to 1.3 times the maximum current

(ISAT> 1.3*IL_peak):

I

IL_peak = out π

2 ∙2 (7)

AN5810 - Rev 1 page 17/45

AN5810

Power losses and efficiency

Another important challenge for the LR is to reach the lowest Rac and to minimize core losses. In order to

minimize the power dissipated into the magnetic core, design consideration for balance between the equivalent

area and flux density (number of turns) is required.

Simulation and experimental results show that a 10% resonant inductor variation and 30% resonant capacitor

variation affects the STC efficiency less than 0.2%.

Figure 17. Inductors selection

With respect to the MOSFET selections in the 4:1 STC application note design, the Flying MOSFETs are rated at

twice the output voltage (2*VOUT) and the Rectification MOSFETs are rated at the output voltage (VOUT). Thus,

40 V MOSFETs and 25 V MOSFETS for the Flying and Rectification MOSFETs, respectively, fit the criteria. These

MOSFET selections, by design via the optimum Figure of Merit (FoM), to achieve high efficiency and thus highest

achievable power density possible. To enable a “completely autonomous STC design”, simulation tools, SIMPLIS

Technologies and Microsoft Excel, are available upon request.

3.5 Power losses and efficiency

Figure 19 and Figure 20 show a calculation of the power losses and of the efficiency without bias (Figure 19 : VIN

= 54 V and Pout = 500 W, Figure 20 : VIN = 54 V and POUT = 1 kW) using the Microsoft Excel Design file.

Power losses and efficiency calculation (POUT = 500 W)

AN5810 - Rev 1 page 18/45

AN5810

Power losses and efficiency

Figure 18. Power losses and efficiency calculations (POUT = 500 W)

POWER LOSS STC

Vin [V] = 5.40E+01 STC Input Volatge

Lr [H] = 7.80E-08 Resonance Inductor

Cr [F] = 1.20E-05 Resonance Capacitor

Vout [V] = 1.35E+01 STC Output Voltage

fsw [Hz] = 1.80E+05 STC Switching Frequency

Tdead [sec] = 1.00E-07 Driver dead time

Duty = 9.64E-01 Duty cicle ( =( −2∗ )/ )

Pout [W] = 5.00E+02 Output Power

Iout [A] = 3.70E+01 STC Output Current

Power Loss SR FETs (Infineon 25V - 40A)

Vdrv[V] = 6.00E+00 Gate Driver Voltage

RDSON [Ω] = 1.30E-03 Drain Source ON resistance

Coss [F] = 1.20E-09 Coss=Cds+Cgd

Qg [C] = 1.60E-08 Gate Charge

Vds [V] = 1.35E+01 Drain Source OFF Voltage

SR FETs # = 6.00E+00 Numebr of SR FETs

PdrvSR [W] = 0.02 Driver Power Loss = ∗ ∗

2

∗ ∗

PCossSR [W] = 0.03 Coss Power Loss =

1.5

2

PcondSR [W] = 0.27 Conduction Power Loss = ∗ ∗

4 ∗2

P totSR [W] = 1.97 Total SR FETs Power Loss =# ∗ / + +

P totSR [%] = 22.36 Total SR FETs Power Loss %

Power Loss Fly FETs (Infineon 40V - 40A)

Vdrv[V] = 5.00E+00 Gate Driver Voltage

RDSON [Ω] = 2.40E-03 Drain Source ON resistance

Coss [F] = 7.50E-10 Coss=Cds+Cgd

Qg [C] = 2.00E-08 Gate Charge

Vds [V] = 2.70E+01 Drain Source OFF Voltage

Fly FETs # = 4.00E+00 Numebr of Fly FETs

PdrvFLY [W] = 0.02 Driver Power Loss = ∗ ∗

2

∗ ∗

PCossFLY [W] = 0.07 Coss Power Loss =

1.5

2

PcondFLY [W] = 0.51 Conduction Power Loss = ∗ ∗

4 ∗2

P totFLY [W] = 2.44 Total FLY FETs Power Loss =# ∗ / + +

P totFLY [%] = 27.67 Total FLY FETs Power Loss %

Power Loss L and C parasitic R

CESR[Ω] = 2.00E-04 Resonance Capacitor ESR

LRcore [Ω] = 1.00E-03 Resonance Inductor Rcore

LRac [Ω] = 3.00E-03 Resonance Inductor Rac

2

P Cesr [W] = 0.26 Resonance Capacitor ESR Power Loss =3∗ ∗ ∗

4∗ 2

P Cesr [%] = 2.98 Resonance Capacitor ESR Power Loss %

2

/ 16

P Lr [W] = 3.51 Resonance Inductor Power Loss = + ∗ 2

∗

P Lr [%] = 39.79 Resonance Inductor Power Loss %

PCB Power Loss

RPCB[Ω] = 3.00E-03 PCB resistance

2

P PCB [W] = 0.63 PCB resistance Power Loss = ∗ ∗

4 ∗2

P PCB [%] = 7.19 PCB resistance Power Loss %

P STCtot[W] 8.81 Total STC Power Loss = + + + +

∗

Efficiency [%] 98.27 Efficiency η=

∗ +

AN5810 - Rev 1 page 19/45

AN5810

Power losses and efficiency

Figure 19. Power losses and efficiency calculation (POUT = 1 kW)

POWER LOSS STC

Vin [V] = 5.40E+01 STC Input Volatge

Lr [H] = 3.90E-08 Resonance Inductor

Cr [F] = 2.00E-05 Resonance Capacitor

Vout [V] = 1.35E+01 STC Output Voltage

fsw [Hz] = 1.90E+05 STC Switching Frequency

Tdead [sec] = 1.00E-07 Driver dead time

Duty = 9.62E-01 Duty cicle ( =( −2∗ )/ )

Pout [W] = 1.00E+03 Output Power

Iout [A] = 7.41E+01 STC Output Current

Power Loss SR FETs (Infineon 25V - 40A)

Vdrv[V] = 6.00E+00 Gate Driver Voltage

RDSON [Ω] = 7.00E-04 Drain Source ON resistance

Coss [F] = 1.20E-09 Coss=Cds+Cgd

Qg [C] = 1.60E-08 Gate Charge

Vds [V] = 1.35E+01 Drain Source OFF Voltage

SR FETs # = 1.20E+01 Numebr of SR FETs

PdrvSR [W] = 0.02 Driver Power Loss = ∗ ∗

2

∗ ∗

PCossSR [W] = 0.03 Coss Power Loss =

1.5

2

PcondSR [W] = 0.59 Conduction Power Loss = ∗ ∗

4 ∗2

P totSR [W] = 7.93 Total SR FETs Power Loss =# ∗ / + +

P totSR [%] = 25.26 Total SR FETs Power Loss %

Power Loss Fly FETs (Infineon 40V - 40A)

Vdrv[V] = 5.00E+00 Gate Driver Voltage

RDSON [Ω] = 1.20E-03 Drain Source ON resistance

Coss [F] = 7.50E-10 Coss=Cds+Cgd

Qg [C] = 2.00E-08 Gate Charge

Vds [V] = 2.70E+01 Drain Source OFF Voltage

Fly FETs # = 8.00E+00 Numebr of Fly FETs

PdrvFLY [W] = 0.02 Driver Power Loss = ∗ ∗

2

∗ ∗

PCossFLY [W] = 0.07 Coss Power Loss =

1.5

2

PcondFLY [W] = 1.01 Conduction Power Loss = ∗ ∗

4 ∗2

P totFLY [W] = 9.14 Total FLY FETs Power Loss =# ∗ / + +

P totFLY [%] = 29.12 Total FLY FETs Power Loss %

Power Loss L and C parasitic R

CESR[Ω] = 5.00E-05 Resonance Capacitor ESR

LRcore [Ω] = 2.00E-03 Resonance Inductor Rcore

LRac [Ω] = 2.00E-03 Resonance Inductor Rac

2

P Cesr [W] = 0.26 Resonance Capacitor ESR Power Loss =3∗ ∗ ∗

4∗ 2

P Cesr [%] = 0.84 Resonance Capacitor ESR Power Loss %

2

/16

P Lr [W] = 14.06 Resonance Inductor Power Loss = + ∗ 2

∗

P Lr [%] = 44.78 Resonance Inductor Power Loss %

PCB Power Loss

RPCB[Ω] = 0.00E+00 PCB resistance

2

P PCB [W] = 0.00 PCB resistance Power Loss = ∗ ∗

4 ∗2

P PCB [%] = 0.00 PCB resistance Power Loss %

P STCtot[W] 31.40 Total STC Power Loss = + + + +

∗

Efficiency [%] 96.96 Efficiency η=

∗ +

AN5810 - Rev 1 page 20/45

AN5810

Efficiency

Figure 17. Full System Efficiency

3.6 Efficiency

The first measurement shown below is the comparison between STC using U2J and STC using only X7R

capacitors for a 500 W solution (not including bias losses). The second measurement is the efficiency at 54 V

up to 500 W conversion comparing with and without Bias losses. Peak efficiency is above 98% in 1/8 brick form

factor.

Figure 20. 2UJ vs X7R EFF comparison

X7R EFF W and W/o bias

AN5810 - Rev 1 page 21/45

AN5810

Efficiency

Figure 21. Efficiency w/o B.

EFF @54V and 48 V w. Bias vs w/o B.

99.0%

98.5%

98.0%

97.5%

97.0%

96.5%

0 5 10 15 20 25 30 35 40 45

AN5810 - Rev 1 page 22/45

AN5810

Output voltage ripple

3.7 Output voltage ripple

Output voltage ripple is shown in Figure 23 at a nominal input voltage (54 V and 42 V), at half load condition (500

W) on the right. The maximum peak-to-peak voltage at 500 W is 300 mVpp, which represents less than 0.3% of

the output voltage, that is, 13.5 V.

Output voltage ripple at minimum input voltage (42 V), at full load condition (600 W) on the right. The maximum

peak-to-peak voltage at 600 W is 221 mVpp, which represents less than 2.2% of the output voltage, that is, 10 V:

Figure 22. Output voltage ripple vs. VIN

VIN = 54V, 500W VIN = 42V, 500W Load

Figure 23. Output voltage tracking dynamic VIN

Dynamic Vin = 54V to 45V

AN5810 - Rev 1 page 23/45

AN5810

Load regulation

3.8 Load regulation

Output voltage droop vs. current load called Rdroop is shown in Figure 24.

Figure 24. Output voltage droop vs. current load

Vdroop vs Iout @different Dead T

500

450

400

350

300

250

200

150

100

50

0

0 5 10 15 20 25 30 35 40

3.9 Transient response

Figure 25. 20 to 60 A @54 V and 20 A to 50 A at 48 V Load step

AN5810 - Rev 1 page 24/45

AN5810

Startup

3.10 Startup

Figure 26 and Figure 27 show the startup sequence in case of EN STC asserted after and before the application

of VIN.

Figure 26. System startup with EN STC asserted after VIN

Figure 27. System startup and turn OFF with VIN

3.11 Overcurrent and short-circuit protection

Table 10 contains the Input Buck and SMED Controller Response in case of an output short-circuit condition.

Shown in Table 11 are the OV/UV/OT protection thresholds and hysteresis.

Table 10. Overcurrent protection summary

OCP description Input buck response SMED controller response

Short at VOUT during Controller initiates OCP protection due to VIN/

Buck initiates OCP protection

normal operation VOUTEFUSE delta (>5V)

Short at VOUT during Buck begins switching to limit I PGOOD low

OUT and after 150ms

soft-start (watchdog) EN eFuse is reset EN eFuse low after 150ms

Hard short at buck Buck begins switching to limit IOUT and after 150ms PGOOD low

during soft-start (watchdog) EN eFuse is reset EN eFuse low after 150ms

AN5810 - Rev 1 page 25/45

AN5810

Overcurrent and short-circuit protection

Table 11. Protection thresholds

Protection Threshold Hysteresis

VIN Undervoltage 39V +5V

VIN Overvoltage(1) 61V NA

VOUT Undervoltage(1) VIN/4 - 25% NA

VOUT Overvoltage(1) VIN/4 + 15% NA

VDRIVER(1) 4.8V NA

Overtemperature(1) 115°C NA

Protection Threshold Hysteresis

VIN Undervoltage 39V +5V

VIN Overvoltage(1) 61V NA

VOUT Undervoltage(1) VIN/4 - 25% NA

VOUT Overvoltage(1) VIN/4 + 15% NA

VDRIVER(1) 4.8V NA

Overtemperature(1) 115°C NA

1. In case the threshold protection is triggered to restart the STC it is necessary to toggle the EN STC. All the protection events

are recorded in the STNRG’s ROM and readable by PMbus commands.

At the startup, as soon as the input buck is enabled, a watchdog timer starts and if, after 150 ms, the input buck

VOUT-EFUSE is not ready, the input buck and then the STC are turned off as shown in Figure 28 on the left.

AN5810 - Rev 1 page 26/45

AN5810

Overcurrent and short-circuit protection

Figure 28. Startup in short-circuit (first mage) and overcurrent protection (second image)

AN5810 - Rev 1 page 27/45

AN5810

Thermal imaging

If during a normal operation and undervoltage (UV) is detected on VDRIVER, the PWMs turn OFF in a latched

mode. Due to STC, bidirectional converter is safer to latch it and avoid uncontrolled in and out input current as

shown in Figure 29 . .

Figure 29. Undervoltage on VDRIVER during normal operation

Magenta = EN STC, Yellow = STC, Green = VDRIVER,

Blue = EN Hot Swap

3.12 Thermal imaging

In Figure 30 and Figure 31 below, an IR image sensor measures the evaluation board temperature of active

areas, the STNRG328S SMED controller, STPRDC02A MOSFET drivers and power MOSFETs under loads of

800 W, 900 W. To reach 500 W it required a Heatsink on the flying MOSFETs (top and bottom side).

Test performed at VIN = 54 V and 48, respectfully, at no FAN and low fan speed air-cooling by means of a small

fan for keeping the operating temperature safe, below 125°C.

AN5810 - Rev 1 page 28/45

AN5810

Thermal imaging

Figure 30. Board thermal map; VIN = 54 V with NO Airflow, POUT =500 W

Figure 31. Board thermal map; VIN = 48 V with no fan and low fan at 500 W (right side)

AN5810 - Rev 1 page 29/45

AN5810

Supported PMBus commands

4 Supported PMBus commands

Latest Pmbus rev, to support X7R tuning parameters too, the default PMBus slave address is 0x50 (7-bit) with

both PIN6 and PIN7 pulled down, so the respective default address is 0xA0 with 0xA0 to write and 0xA1 to read.

With different schemes on PIN6 and PIN7, we could set the device slave address as the following:

Table 12. Pin6 and pin7

PMBus address 7-bit (Hex) PIN6 PIN7 Write (HEX) READ (HEX)

0x50 Pulled-down Pulled-down 0xA0 0xA1

0x52 Open Pulled-down 0xA4 0xA5

0x54 Pulled-down Open 0xA8 0xA9

0x56 Open Open 0xAC 0xAD

Table 13. PMBUS commands

Number

Command Transaction

Command name of data Description

code type

bytes

On/Off configuration

ON_OFF_CONFIG 0x02 1 R/W 0x0C turns off the STC,

0x1C it turns on

CLEAR_FAULTS 0x03 1 Send byte Clear status registers

WRITE_PROTECT 0x10 1 R/W Protection against accidental changes

Key capabilities of the device

Current set capabilities:

CAPABILITY 0x19 1 R • Packet error checking

• Maximum bus speed 100kHz

• SMBALERT# signal available

Used to set every status register whose bits can

SMBALERT_MASK 0x1B 2 R/W

affect the assertion of the SMB_ALERT# pin

VOUT_MODE 0x20 2 R VOUT format not implemented

PMBUS_VIN_ON 0x35 2 R/W Set/get the input voltage beyond STC turns on

Set/get Vin_off which intervenes when an

undervoltage occurs, the STC goes into the

PMBUS_VIN_OFF 0x36 2 R/W

UVLO state but is still on, if it remains there for

a certain time then it goes into the shutdown state

Set/get the input voltage that causes an input

PMBUS_VIN_OV FAULT LIMIT 0x55 2 R/W

overvoltage

Critical faults information (one byte)

Supported the following status bits:

• bit 6 UNIT IS OFF

STATUS_BYTE 0x78 1 R/W • bit 5 VOUT_OV_FAULT

• bit 4 IOUT_OC_FAULT

• bit 3 VIN_UV_FAULT

• bit 2 TEMPERATURE FAULT

Critical faults information (one word)

STATUS_WORD 0x79 2 R/W Supported the following status bits in low byte:

• same bits of STATUS_BYTE

AN5810 - Rev 1 page 30/45

AN5810

Supported PMBus commands

Number

Command Transaction

Command name of data Description

code type

bytes

Supported the following status bits in high byte:

• bit 7 VOUT fault

• bit 6 IOUT fault

• bit 5 INPUT FAULT

• bit 4 VDRIVER_UVP

• bit 3 POWER_GOOD Negated

Output voltage warnings and faults

Supported the following status bits:

STATUS_VOUT 0x7A 1 R/W

• bit 7 VOUT_OV_FAULT

• bit 4 VOUT_UV_FAULT

Output current warnings and faults

STATUS_IOUT 0x7B 1 R/W Supported the following status bits:

• bit 7 IOUT_OC_FAULT

Input warnings and faults

Supported the following status bits:

STATUS_INPUT 0x7C 1 R/W • bit 7 VIN_OV_FAULT

• bit 4 VIN_UV_FAULT

• bit 3 Unit Off for insufficient input voltage

Temperature warnings and faults

STATUS_TEMPERATURE 0x7D 1 R/W Supported the following status bits:

• bit 7 OT_FAULT

Communication and memory status

Supported the following status bits:

• bit 7 Invalid or unsupported command

STATUS_CML 0x7E 1 R/W

– received

• bit 6 Invalid or unsupported data received

• bit 5 Packet error check failed

• bit 4 Memory fault detected

Vdriver fault protection flag:

MFR SPECIFIC 0x80 1 R/W 0 for no triggered protection

1 for triggered protection

Read input voltage

READ_VIN 0x88 2 R Format: LINEAR11

Exponent: -2

Read output voltage

READ_VOUT 0x8B 2 R Format: LINEAR16

Exponent: -5

Read temperature NTC [°C]

READ_TEMPERATURE1 0x8D 2 R Format: LINEAR11

Exponent: 0

Read temperature eFuse [°C]

READ_TEMPERATURE2 0x8E 2 R Format: LINEAR11

Exponent: 0

Read PWM frequency[kHz]

READ_FREQUENCY 0x95 2 R

Format: LINEAR11

AN5810 - Rev 1 page 31/45

AN5810

Supported PMBus commands

Number

Command Transaction

Command name of data Description

code type

bytes

Exponent: 0

Read PMBus revision

PMBUS_REVISION 0x98 1 R

Revision 1.3

Read manufacturer model number

MFR_MODEL 0x9A 10 R/

(ASCII: STNRG328A)

MFR_REVISION 0x9B 5 R/W Read/store firmware revision (ASCII)

MFR_DATE 0x9D 5 R/ Returns WWYY of firmware production

PMBUS_USER_DATA02 0xB2 1 R Read the configuration ZCD master/slave

PMBUS_USER_DATA03 0xB3 1 R Return the board configuration

The command set/get the 1st max. rated

MFR MAX TEMP 1 0XC0 2 R/W temperature of the manufacturer. Unit is degree

Celsius

The command set/get the 2nd max. rated

MFR MAX TEMP 2 0XC1 2 R/W temperature of the manufacturer. Unit is degree

Celsius

MFR_WAIT_EN_FAULT: set/get the number of

MFR SPECIFIC 12 0XD0 2 R/W system ticks before enabling faults, after entering

ST_ON

MFR_WAIT_EN_FAULT1: set/get the number of

MFR SPECIFIC 13 0XD1 2 R/W system ticks before enabling faults, after entering

ST_ON (second restart)

MFR_WAIT_TIMEPWRUP: read/write the

MFR SPECIFIC 14 0XD2 2 R/W

number of ticks to wait at power-up

MFR_WAIT_BEFORE_EFUSE: read/write the

MFR SPECIFIC 15 0XD3 2 R/W

number of ticks to wait before ENEFuse asserted

MFR_VOUT_EFUSE_MIN: set/get minimum

MFR SPECIFIC 17 0XD5 2 R/W value of Vout eFuse for which Vout eFuse

undervoltage is triggered

MFR_OCP_VALUEDIF: voltage difference

MFR SPECIFIC 18 0XD6 2 R/W between input voltage and Vout eFuse to detect a

hot swap overcurrent condition

MFR SPECIFIC 19 0XD7 2 R/W Read conversion ratio

MFR_ VDRIVER_UVP_DAC: set/get the internal

MFR SPECIFIC 21 0XD9 2 R/W reference for undervoltage for Vdriver. Numeric

format is LINEAR11

MFR_VIN_SHUTDOWN: set/get input voltage

threshold. When the input voltage becomes less

MFR SPECIFIC 22 0XDA 2 R/W

than this value, the STC is put in OFF state.

Numeric format is LINEAR11

MFR_SWITCHFREQ_FF_STEP: set/get the step

of the switching frequency. At feedforward

MFR SPECIFIC 23 0XDB 2 R/W

threshold, switching frequency changes by this

value (kHz),

MFR_FF_THRESHOLD_VMIN: set/get the

feedforward frequency step threshold

MFR SPECIFIC 24 0XDC 2 R/W (min. voltage) put this value into

FF_THRESHOLD_VMIN. Numeric format is

LINEAR11

AN5810 - Rev 1 page 32/45

AN5810

Supported PMBus commands

Number

Command Transaction

Command name of data Description

code type

bytes

MFR_FF_THRESHOLD_VMAX: set/get

feedforward frequency step threshold

MFR SPECIFIC 25 0XDD 2 R/W (max. voltage) put this value into

FF_THRESHOLD_VMAX. Numeric format is

LINEAR11

MFR_ENABLE_BOOTLOADER: Enable/disable

MFR SPECIFIC 26 0XDE 2 R/W

bootloader by UART

MFR_SWITCH_FREQ: set/get the programmable

MFR SPECIFIC 27 0XDF 2 R/W

switching frequency. Numeric format is LINEAR11

MFR_OVP_COUNTER 0xE0 2 R/W Vout OVP protection counter

MFR_UVP_COUNTER 0xE1 2 R/W Vout UVP protection counter

MFR_OCP_COUNTER 0xE2 2 R/W Input OCP protection counter

MFR_THERMSHDW_COUNTER 0xE3 2 R/W NTC OT protection counter

MFR_LOCK: insert password (6 bytes) to lock

MFR SPECIFIC 32 0XE4 6 R/W

EEPROM writing.

MFR_UNLOCK: insert password (6 bytes) to

MFR SPECIFIC 33 0xE5 6 R/W

unlock EEPROM writing.

MFR SPECIFIC 36 0XE8 2 R/W Return the count of Vout_Efuse fails

MFR_START_CRC_CHECK: start the CRC

MFR SPECIFIC 38 0XEA 1 R

check

MFR_GET_CRC_RESULT: get the CODE CRC

MFR SPECIFIC 39 0XEB 4 R

result

MFR_GET_EEPROM_CHECKSUM: get the

MFR SPECIFIC 40 0XEC 2 R

EEPROM checksum

MFR_GRT_DATA_CRC_RESULT: Get the DATA

MFR SPECIFIC 44 0XF0 4 R

CRC result

Get/set the index of ZCD Matrix table. The range

PMBUS_USER_DATA00 0XB0 1 R/W is [0,18], outside of this range the command

returns the error code 0xFF.

Read/write the ZCD parameters in the ZCD

Matrix table (RAM if STC is ON, EEPROM if STC

MFR SPECIFIC 45 0XF1 8 R/W is OFF) at the index specified by the command.

If the index is out of range, the command returns

the sequence of error code 0xFF.

The command loads the ZCD Matrix table from

MFR SPECIFIC 46 0XF2 1 R/W RAM to FLASH. It returns 1 if the copy is

successful, or else it returns 0.

The command read/write the increment of

SMED0 clock from/to FLASH memory. The range

MFR SPECIFIC 41 0XED 1 R/W

is [0,50]. The command returns 0xFF when the

value is out of the range or when the STC is ON.

The command returns the current line and the

relative index of the ZCD Matrix, corresponding to

PMBUS_USER_DATA01 0xB1 9 R/

Vin applied when STC is ON. If STC is OFF the

bytes are 0xFF.

Max. precharged Vout threshold before turning-

VOUT_STUPSWITCH 0xF3 2 R/W

ON

AN5810 - Rev 1 page 33/45

AN5810

Bill of material

5 Bill of material

Table 14. Bill of material

Item Reference Quantity Value Supplier Description

CVCC_2, CVCC_3,

CVCC_5, CVCC_6,

CBY_6, CVDR1_5,

CAP CER 16V X5R

2 CVDR1_6, 11 1µF Murata

0402

CVDR2_5,

CVDR2_6, C21_10,

C21_12

C4, CF1_7, C6_7, CAP CER 16V X5R

3 4 1µF Murata

C17_9 0402

C2, Cuart_7, CF2_7,

CAP CER 25V X5R

4 C3_7, CF4_7, C4_7, 8 0.1µF Murata

0402

C5_7, C9_9

CAP CER 25V X5R

5 C3, CF3_7, Fsw_C 3 10000pF TDK

0402

GRM31CR71H475K

6 Cres1 to 16 10 10uF Murata

A12L

Cres 18 to 40 13 4.7uF TaiyoYuden TMK212AB7475KG

CVIN1_2, CVIN2_2,

CVIN3_2, CVIN4_2,

CVIN5_2, C5_9,

CVIN6_2, CVIN7_2, CAP CER 100V X7S

CVIN8_2, C8_9, 1210

7 CVIN9_2, CVIN10_2, 12 10µF Murata

CVIN11_2, GRM32EC72A106K

CVIN12_2, E05L

CVIN13_2,

CVIN14_2, C16_9,

C14_10, C14_12,

CVIN1_3, CVIN2_3,

CVIN3_3, CVIN4_3,

CVIN5_3, CVIN6_3, CAP CER 50V X7S

CVIN7_3, CVIN8_3, 1210

8 CVIN9_3, CVIN10_3, 12 10µF Murata

CVIN11_3, GRM32ER71H106K

CVIN12_3, A12L

CVIN13_3,

CVIN14_3,

CAP CER 50V

9 Cconf2, Cconf3 2 100pF Murata

C0G/Np0 0402

CAP CER 50V

10 Cconf5, Cconf6 2 100pF Murata

C0G/Np0 0402

CAP CER 100V X7R

11 Ccp2, Ccp_3 2 0.47µF Murata

0805

Cout4_7, Cout4_8,

Cout2_7, Cout2_9,

Cout4_10, Cout2_8,

Cout1_5, Cout2_5,

Cout3_5, Cout10_7,

Cout11_7, Cout12_7, Taiyo CAP CER 25V X5R

12 24 22µF

Cout10_5, Cout11_5, Yuden 1206

Cout1_8, Cout2_10,

Cout3_8, Cout1_6,

Cout12_5, Cout1_9,

Cout2_11, Cout3_9,

Cout2_6, Cout3_6,

AN5810 - Rev 1 page 34/45

AN5810

Bill of material

Item Reference Quantity Value Supplier Description

CAP ALUM POLY

13 Cout5_5 1 270µF Panasonic

20% 25V SMD

14 Cp 1 22pF Murata CAP CER 0402 X5R

CAP CER 25V X5R

15 C5 1 2.2µF Murata

0402

CAP CER 10V X5R

16 C7 1 22µF Murata

0603

CAP ALUM 20% 63V

17 C1_9 1 100µF Panasonic

SMD

CAP CE 50V X7R

18 C18_A, C19_A 4 2.2µF TDK

0805

CAP CER 50V X7R

19 C4_9 1 0.1µF Yageo

0402

CAP CER 10V X5R

20 C6_9 1 10µF Samsung

0402

CAP CER 25V X5R

21 C7_7 1 0.1µF Murata

0402

100V ±10% X5R

22 C11_9 1 0.1µF Murata

0402SMD

CAP CER 100V X7R

23 C7_9, 6 0.1µF AVX

1206

Taiyo CAP CER 16V X7R

24 C12_9 1 4700pF

Yuden 0402

CAP CER 100V Np0

25 C14_9 1 10pF AVX

0603

CAP CER 25V X5R

26 C15_9 1 10µF Murata

0603

CAP CER 50V X7R

27 C18_9 1 1000pF Murata

0402

Taiyo CAP CER 6V X7R

28 C21_9 1 100pF

Yuden 0402

CAP CER 16V X5R

29 C17_10, 1 0.47µF Murata

0402

Schottky diodes &

DBY_5, DBX_5,

30 4 Infineon rectifiers Lw VF

DBX_6, DBY_7

Schottky diode

DB_2, DBY2, DB_3,

2A, 40V Schottky

31 DBY3, DBX3, 6 ONSemi

barrier diode

DBX2_2

Schottky diodes &

32 DBX4, DBX5 2 Infineon rectifiers Lw VF

Schottky diode

LED RED

33 D2 1 Broadcom DIFFUSED 1206

SMD

DIODE SCHOTTKY

34 D3 1 Diodes

100V

RES SMD 1kΩ 5%

35 Fsw_R_1k 1 Panasonic

1/10W 0402

RES SMD 910 Ω 1%

36 Fsw_set_R 1 Panasonic

1/10W 0402

AN5810 - Rev 1 page 35/45

AN5810

Bill of material

Item Reference Quantity Value Supplier Description

TERM SCREW 6-32

37 M1, GND1 2 Keystone

4 PIN PCB

J1_PWM,

38 2

J2_I2C_SWIM

Heavy duty power

J2_EF, J5_EF,

39 3 Anderson connectors pp15/45

J1_EF1

contact pin

Heavy duty power

J3_EF, J4_EF,

40 4 Anderson connectors pp15/45

J6_EF, J6_EFF1

contact pin

41 J4_V, J4_V1, J4_V2 3

TERM SCREW 6-32

42 J5_EFF, J6_EFF 2 Keystone

4 PIN PCB

Heavy duty power

43 J5_EFF1 1 Anderson connectors pp15/45

contact pin

44 L1 1 47µH Murata LQH32PB470MNO

1 ELEMENT,

0.33µH, GENERAL

45 Lin1, Lin 2 330nH ITG

PURPOSE

INDUCTOR, SMD

TPI078060l056N

46 L2, L3, L5, L6 2 56nH Kemet or Pulse

PA0512.700NLT

Wurth FERRITE BEAD 120

47 L1_7 1 120

Electronics Ω 0603 1LN

MHD1, MHD3, CONNECTION

48 4

MHD4, MHD5 TERMINALS

NO CONNECT

49 R27_10 1

(OPEN)

Q5, Q6, Q9, Q10, MOSFET N-CH 25V

50 8 Infineon/ ONsemi

Q25, Q27, Q29, Q30 32A 8SON

Infineon/ MOSFET N-CH 25V

51 Q7, Q8, Q26, Q28 4

STMicroelectronics 32A 8SON

MOSFET N-CH 80V

52 Q1__HSW1 1 STMicroelectronics POWERFLAT5X6

STL130N8

53 Q1__HSW3 1 STMicroelectronics STL3575

Q13, Q14, Q15, Q16, STMicroelectronics/ MOSFET N-CH 40V

54 4

Q17, Q18, Q19, Q20 Infineon 22A TSDSON-8

RES SMD 0.1%

55 RDWN_VDRIVE 1 1.07kΩ Panasonic

1/16W 0402

RVCC_2, RVCC_3,

RES SMD 5% 1/10W

56 RVCC_5, RVCC_6, 5 2.2Ω Panasonic

0603

RF_7

RTD_2, RTD_3, RES SMD1% 1/10W

57 4 53.6kΩ Panasonic

RTD_5, RTD_6 0402

RTdw1, RTdw2, RES SMD5% 1/10W

58 3 100kΩ Panasonic

R22_10 0402

RTup1, RTup2, RES SMD1% 1/10W

59 3 150kΩ Panasonic

R22_9 0402

AN5810 - Rev 1 page 36/45

AN5810

Bill of material

Item Reference Quantity Value Supplier Description

RES SMD0.1%

60 RUP_VDRIVE 1 3.92kΩ Panasonic

1/16W 0402

RES SMD 5% 1/10W

61 RUart_I2C 1 2.2kΩ Panasonic

0402

R1, R2, RVDRY_5,

RVDRX_5,

RES SMDJUMPER

62 RVDRY_6, 8 0Ω Yageo

1/16W 0402

RVDRX_6, R25_9,

R27_9

RES SMD 5% 1/10W

63 RdwOut 1 1.2kΩ Panasonic

0402

RES SMD 5% 1/10W

64 RdwVin, RdwVef 2 2.2kΩ Panasonic

0402

RES SMD 5% 1/10W

65 RdwnENE 1 1MΩ Panasonic

0402

NTC thermistor 5%

66 Rntc1, Rntc2 2 100kΩ Vishay

0603

RES SMD 5% 1/10W

67 RupOut 1 18kΩ Panasonic

0402

68 RupVin, RupVef 2 Yageo Thin film resistor

RES SMD 1% 1/16W

69 R3 1 80.6kΩ Yageo

0402

RES SMD 5% 1/16W

70 R4, R15_9 2 10kΩ Yageo

0402

RES SMD 5% 1/10W

71 R5 1 1.5MΩ Panasonic

0402

RES SMD 1% 1/10W

72 R6 1 4.99kΩ Panasonic

0402

RES SMD 1% 1/10W

73 R7 1 32.4kΩ Panasonic

0402

RES SMD 1% 1/16W

74 R1_9 1 60.4kΩ Yageo

0402

RES SMD 1% 1/16W

75 R2_9 1 1.91kΩ Yageo

0402

R3_7, R4_7,

RES SMD 5% 1/10W

76 R6_N_7, R28_9, 6 1kΩ Panasonic

0402

R28_11, R28_13

77 R3_9 1 Yageo Thin film resistor

RES SMD 5% 1/10W

78 R5_N_7 1 1kΩ Panasonic

0402

RES SMDJUMPER

79 R6_9, R16_9, R18_9 3 0Ω Yageo

1/16W 0402

RES SMD 1% 1/16W

80 R7_9 1 301kΩ Yageo

0402

RES SMD 1% 1/16W

81 R8_9 1 80.6kΩ Yageo

0402

R10_9, R24_10, RES SMD 1% 1/16W

82 4 2kΩ Yageo

R25_10 0402

RES SMD 1% 1/10W

83 R23_9 1 90.9kΩ Panasonic

0402

RES SMD JUMPER

84 R24_9, R26_9 2 0Ω Yageo

1/16W 0402

AN5810 - Rev 1 page 37/45

AN5810

Bill of material

Item Reference Quantity Value Supplier Description

RES SMD 5% 1/16W

85 R25_9 1 10kΩ Yageo

0402

RES SMD 5% 1/10W

86 R23_10 1 1Ω Panasonic

0603

RES SMD 1% 1/10W

87 1 4.99kΩ Panasonic

0402

CTS Electro SWITCH SLIDE DIP

88 SW1 1

components SPST 100mA 20V

High-performance

89 U2, U3, U5, U6 4 STMicroelectronics high-voltage full-

bridge Driver

90 U7 1 STMicroelectronics STNRG328S

IC REG LDO 3.3V

91 U8_A 1 STMicroelectronics

0.2A 6DFN

IC REG CTRLR

92 U9 1 Linear Technology

SYNC BUCK 24QFN

93 U1 2 STMicroelectronics eFuse

94 D6 1 ZENER DIODE

R24_11, R28_12,

95 2 LittleFuse NO CONNECT

R24_13

96 R24_12 1 Yageo NO CONNECT

RES SMD 5% 1/16W

97 R33_9 1 120k Yageo

0402

98 C16_10 1 100nF Yageo 100nF, 100V

C16_11, C222,

C223, C7_12,

Samsung Electro-

99 C7_13, Cconf2, 7 100nF 100nF, 16V

Mechanics

Cconf3, Cconf6,

Cconf5

C2_11, C3_11,

100 4 10µF Murata 10µF, 10V

C2_10, C3_10

101 C2_9, C3_9 2 2.2µF Murata 2.2µF, 100V

102 R6_10 1 0 Murata 0Ω

RES SMD 5% 1/16W

103 R30_9 1 10k Yageo

0402

R_ZVS2, R_ZVS1,

104 R_ZVS, R_ZVS4, 6 1KΩ

RDTdw3, RDTdw4,

105 R_ZVS3, R_ZVS5 2 420Ω

106

AN5810 - Rev 1 page 38/45

AN5810

Package information

6 Package information

Reference top and bottom layout:

Figure

Reference TOP and Bottom 32. Top

Layout : and bottom layout

Drivers , Resonant LC , rectification Mosfet , Floating mosfet

CONTROLLER

January 2021 ST Confidential 36/39

www.st.com

AN5810 - Rev 1 page 39/45

AN5810

Support material

7 Support material

Table 15. Main IC description

Related design support material

Gerber files – ask your ST representative

PCB layout, bill of materials and schematics files – ask your ST representative

STNRG328 Upgrade Firmware Procedure – ask your ST representative

Documentation

STNRG328S; Digital controller for power conversion applications with up to 6 programmable PWM generators, 96 MHz PLL

STPRDC02A; High-Performance High-Voltage Full-Bridge Driver

STL130N8F7; N-channel 80 V, 3.0 mΩ typ., 120 A STripFET™ F7 Power MOSFET in a PowerFLAT™ 5x6 package

STL35N3LH8; N-channel 75 V, 20 mΩ typ., 32 A STripFET™ F3 Power MOSFET in a PowerFLAT™ 3.3x3.3 package

STL260N45LH7; N-channel 45 V

LDK220PU33R; 200mA low quiescent current and low noise LDO

LTC7801,LM5060 or LTC7801.; 150V Low IQ, Synchronous Step-Down DC/DC Controller

AN5810 - Rev 1 page 40/45

AN5810

Revision history

Table 16. Document revision history

Date Version Changes

7-Feb-2023 1 Initial release.

AN5810 - Rev 1 page 41/45

AN5810

Contents

Contents

1 Main features and circuit description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2 STC power section & drivers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3 STC digital control engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.1 Hot swap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.2 Auxiliary power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.3 Startup sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.4 Design guidelines with special focus on the inductor and capacitor selections . . . . . . . . . . . 16

3.5 Power losses and efficiency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.6 Efficiency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.7 Output voltage ripple. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.8 Load regulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.9 Transient response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.10 Startup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.11 Overcurrent and short-circuit protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.12 Thermal imaging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4 Supported PMBus commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

5 Bill of material . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

6 Package information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

7 Support material. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

List of tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

List of figures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

AN5810 - Rev 1 page 42/45

AN5810

List of tables

List of tables

Table 1. Main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Table 2. STC tested configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 3. Pin12 cpp0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 4. Resistors setting for cpp0 configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 5. Ration & RdwOut 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 6. PWM frequency control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 7. PGOOD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 8. Suggested pin to pin capacitors part numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 9. Equivalent resonant capacitances . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 10. Overcurrent protection summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 11. Protection thresholds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 12. Pin6 and pin7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 13. PMBUS commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 14. Bill of material . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 15. Main IC description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 16. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

AN5810 - Rev 1 page 43/45

AN5810

List of figures

List of figures

Figure 1. 500W, ⅛ brick STC converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 2. STC principle schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Figure 3. Ton phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Figure 4. TOFF phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Figure 5. STC concept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Figure 6. STC simulation POUT = 500 W and VIN = 54 V → main STC nodes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 7. STC simulation POUT = 500 W and VIN = 54 V → C voltage & L current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 8. Rectification MOSFETs driver section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 9. Floating MOSFETs driver section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 10. SMED digital engine STNRG328S block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 11. Ration & RdwOut 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 12. STC state machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 13. Digital engine STNRG328S section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 14. Input section A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 15. Input section B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 16. Startup sequence with EN STC asserted after VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 17. Inductors selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 18. Power losses and efficiency calculations (POUT = 500 W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 19. Power losses and efficiency calculation (POUT = 1 kW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 20. 2UJ vs X7R EFF comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 21. Efficiency w/o B. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 22. Output voltage ripple vs. VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 23. Output voltage tracking dynamic VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 24. Output voltage droop vs. current load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 25. 20 to 60 A @54 V and 20 A to 50 A at 48 V Load step . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 26. System startup with EN STC asserted after VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 27. System startup and turn OFF with VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 28. Startup in short-circuit (first mage) and overcurrent protection (second image) . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 29. Undervoltage on VDRIVER during normal operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 30. Board thermal map; VIN = 54 V with NO Airflow, POUT =500 W . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 31. Board thermal map; VIN = 48 V with no fan and low fan at 500 W (right side) . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 32. Top and bottom layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

AN5810 - Rev 1 page 44/45

AN5810

IMPORTANT NOTICE – READ CAREFULLY

STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST

products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST

products are sold pursuant to ST’s terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of

purchasers’ products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names

are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics – All rights reserved

AN5810 - Rev 1 page 45/45

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- TK 51916-18-OP Direct Drive DSR Operators Manual Rev 12 06-16 - ML PDFDocument334 pagesTK 51916-18-OP Direct Drive DSR Operators Manual Rev 12 06-16 - ML PDFRaphael GamaNo ratings yet

- Fender Jazzmaster Ultralight Amp ManualDocument10 pagesFender Jazzmaster Ultralight Amp ManualBenNo ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Ulta Stepup DC To DC Conveter With Reduced Switch StressDocument21 pagesUlta Stepup DC To DC Conveter With Reduced Switch StressDRISHYANo ratings yet

- 555 Timer Ic: Project ReportDocument10 pages555 Timer Ic: Project ReportHarshada HalarnkarNo ratings yet

- MA5600T&MA5603T&MA5608T Hardware Description 23Document973 pagesMA5600T&MA5603T&MA5608T Hardware Description 23ibitisamNo ratings yet

- Expt 9 - Astable-Multivibrator (2020)Document5 pagesExpt 9 - Astable-Multivibrator (2020)samarth100% (1)

- Industrial Contact Nashik PDFDocument196 pagesIndustrial Contact Nashik PDFGanesh Mali0% (1)

- Troubleshooting DS 610 SLDocument11 pagesTroubleshooting DS 610 SLcraigh100% (1)

- EDS Index 2015 02 24Document138 pagesEDS Index 2015 02 24SANGRAMNo ratings yet

- Slua 053Document13 pagesSlua 053carlosibaNo ratings yet

- TA8251AH: Max Power 30W BTL × 4ch Audio Power ICDocument13 pagesTA8251AH: Max Power 30W BTL × 4ch Audio Power ICРамиль Невмянов100% (1)

- Module-5 - INVERTER - VII-POWER ELECTRONICS - 2015-17 SchemeDocument22 pagesModule-5 - INVERTER - VII-POWER ELECTRONICS - 2015-17 SchemeK N DEEPSHINo ratings yet

- Current Controller For Stepping Motors: DescriptionDocument8 pagesCurrent Controller For Stepping Motors: Descriptiontryu40No ratings yet

- Uc3842 - Current-Mode ControlDocument16 pagesUc3842 - Current-Mode ControlGiovani AkNo ratings yet

- Laboratory Report on Integrator and Differentiator CircuitDocument22 pagesLaboratory Report on Integrator and Differentiator CircuitHrivu Dasmunshi (RA1911004010566)No ratings yet

- STK401-090 50W Audio Amp Spec SheetDocument10 pagesSTK401-090 50W Audio Amp Spec SheetHERNANDO A BECERRANo ratings yet

- Toshiba Bipolar IC Drives DC MotorsDocument14 pagesToshiba Bipolar IC Drives DC MotorsrikyNo ratings yet

- DC DC 2 Pe Au 20 11 08Document31 pagesDC DC 2 Pe Au 20 11 08Ali AhmadNo ratings yet

- Rectification. 10 CO2 L3 Sol N.: Maharaja Institute of Technology MysoreDocument7 pagesRectification. 10 CO2 L3 Sol N.: Maharaja Institute of Technology MysoreSpoorthy HUNo ratings yet

- Oscillator ManualDocument22 pagesOscillator ManualckooipgNo ratings yet

- 2 STL 2580Document14 pages2 STL 2580The FatherNo ratings yet

- Electronic Circuits LatestDocument69 pagesElectronic Circuits LatestSai SadiqNo ratings yet

- DP8600C YwDocument9 pagesDP8600C YwSURESH CHANDRA ROUTNo ratings yet

- Iris 4015Document6 pagesIris 4015vetchboyNo ratings yet

- 固电半导体 Inchange Semicondutor: Silicon NPN Power TransistorsDocument3 pages固电半导体 Inchange Semicondutor: Silicon NPN Power Transistorsyiyus1No ratings yet

- Single-Stage BJT Amplifiers: Experiment-2Document19 pagesSingle-Stage BJT Amplifiers: Experiment-2karan007_mNo ratings yet

- Trickle-Charge IC For Two-Cell, Lithium-Ion BatteriesDocument8 pagesTrickle-Charge IC For Two-Cell, Lithium-Ion BatteriesDary CalaçaNo ratings yet

- EC6304 Electronic Circuits I Question BankDocument10 pagesEC6304 Electronic Circuits I Question BankAnonymous kQZgP8No ratings yet

- En CD00003897 PDFDocument7 pagesEn CD00003897 PDFJosias AndradeNo ratings yet

- AN948Document6 pagesAN948cubucetaNo ratings yet

- Vco WDocument8 pagesVco Wapi-3725139No ratings yet

- BU808DFIDocument8 pagesBU808DFIjsalinas78No ratings yet

- Aec AssignmentDocument14 pagesAec AssignmentAnnu YadavNo ratings yet

- STK401-110 AF Power Amplifier (Split Power Supply) Technical DocumentationDocument8 pagesSTK401-110 AF Power Amplifier (Split Power Supply) Technical DocumentationKyaw San OoNo ratings yet

- Unijunction TransistorDocument54 pagesUnijunction TransistorPaoNo ratings yet

- TB2929HQ: 45W × 4-ch BTL Audio Power ICDocument17 pagesTB2929HQ: 45W × 4-ch BTL Audio Power ICmicaelfnNo ratings yet

- Linear Integrated Circuit Tone RingerDocument3 pagesLinear Integrated Circuit Tone RingerLenon Salazar100% (1)

- MC13783 Buck and Boost Inductor Sizing: Application NoteDocument8 pagesMC13783 Buck and Boost Inductor Sizing: Application NoteVitaliyGNo ratings yet

- Boost ProjectDocument13 pagesBoost ProjectAbdur RahmanNo ratings yet

- Data SheetDocument17 pagesData SheetSaprinus SapNo ratings yet

- Two-Phase Stepper Motor Driver: DescriptionDocument19 pagesTwo-Phase Stepper Motor Driver: DescriptionDan EsentherNo ratings yet

- Ultra-Fast Acting Electronic Circuit BreakerDocument55 pagesUltra-Fast Acting Electronic Circuit Breakerpandi60% (5)

- AND8099/D 5.0 V, 2.0 A Flyback Converter: Application NoteDocument8 pagesAND8099/D 5.0 V, 2.0 A Flyback Converter: Application NoteIgor MairinckNo ratings yet

- Expt - 7 :transistorized Astable MultivibratorDocument4 pagesExpt - 7 :transistorized Astable Multivibratorsamarth100% (1)

- ST1802FX: High Voltage Fast - Switching NPN Power TransistorDocument10 pagesST1802FX: High Voltage Fast - Switching NPN Power Transistorvali dNo ratings yet

- ST1510FX-ST MicroelectronicsDocument10 pagesST1510FX-ST MicroelectronicsSastra DjinggaNo ratings yet

- BU808DFI: High Voltage Fast-Switching NPN Power DarlingtonDocument8 pagesBU808DFI: High Voltage Fast-Switching NPN Power DarlingtonOvo BabaAzizi OvoNo ratings yet

- BU808DFI: High Voltage Fast-Switching NPN Power DarlingtonDocument7 pagesBU808DFI: High Voltage Fast-Switching NPN Power DarlingtonEsoj NoryaleNo ratings yet

- Variable DC Power Using Full Bridge ConverterDocument6 pagesVariable DC Power Using Full Bridge Convertergoten10daNo ratings yet

- Open Ended 1Document12 pagesOpen Ended 1AneeshaNo ratings yet

- ELET 201 - Basic Industrial Electronics - Lab Manual - 2023Document140 pagesELET 201 - Basic Industrial Electronics - Lab Manual - 2023bandr almalkiNo ratings yet

- Unisonic Technologies Co., LTD: High Performance Current Mode PWM ControllersDocument7 pagesUnisonic Technologies Co., LTD: High Performance Current Mode PWM ControllersCesra HMNo ratings yet

- 固电半导体 Inchange Semiconductor: Silicon NPN Power TransistorsDocument4 pages固电半导体 Inchange Semiconductor: Silicon NPN Power TransistorsJosé Joaquim Braga BragaNo ratings yet

- Electroestimulador Mettler - ME200 ServiceDocument13 pagesElectroestimulador Mettler - ME200 ServicedanielNo ratings yet

- TA7280P, TA7281P: 5.8W Dual Audio Power Amplifier. 22W BTL Audio Power AmplifierDocument15 pagesTA7280P, TA7281P: 5.8W Dual Audio Power Amplifier. 22W BTL Audio Power AmplifierMates IoanNo ratings yet

- Phototransistor Switching Time Analysis: Output WaveformsDocument8 pagesPhototransistor Switching Time Analysis: Output WaveformsklklkNo ratings yet

- Ece Vii Power Electronics (10ec73) AssignmentDocument6 pagesEce Vii Power Electronics (10ec73) AssignmentThomas PriceNo ratings yet

- 260-Article Text-451-1-10-20171230Document4 pages260-Article Text-451-1-10-20171230Shayan RiazAhmedNo ratings yet

- STGW 30 NC 60 WDDocument14 pagesSTGW 30 NC 60 WDacajevtic94No ratings yet

- 固电半导体 Inchange Semicondutor: Silicon NPN Power TransistorsDocument4 pages固电半导体 Inchange Semicondutor: Silicon NPN Power TransistorssighbalaNo ratings yet

- A Low Voltage High Performance OTA in 0.18 Micron With High LinearityDocument10 pagesA Low Voltage High Performance OTA in 0.18 Micron With High LinearitymohsenparsauniNo ratings yet

- Pulse Density ModulationDocument4 pagesPulse Density ModulationrhusheinNo ratings yet

- Pplication OTE: Low Voltage DC Supply Dimmable Ballast For 1 X 36W T8 LampDocument13 pagesPplication OTE: Low Voltage DC Supply Dimmable Ballast For 1 X 36W T8 LampBravo MacNo ratings yet

- A Full-Bridge Phase-Shifted Inverter For Induction HeatingDocument78 pagesA Full-Bridge Phase-Shifted Inverter For Induction HeatingCCNo ratings yet

- LC5901S Data Sheet Rev.1.5: Sanken Electric Co., LTDDocument29 pagesLC5901S Data Sheet Rev.1.5: Sanken Electric Co., LTDRodolfo ArosemenaNo ratings yet

- VPM1RTDocument1 pageVPM1RTJulioCesar MagalhaesNo ratings yet

- 100W LED Flashlight PDFDocument5 pages100W LED Flashlight PDFRichard Kaven SerquinaNo ratings yet

- Inverter Setting For 55kw SIEI Inanam Spinning MachineDocument1 pageInverter Setting For 55kw SIEI Inanam Spinning Machinenoblas melNo ratings yet

- Sie-C887-5 1h 14 1 PDFDocument305 pagesSie-C887-5 1h 14 1 PDFЗлати ВълчевNo ratings yet

- Model Yuea36Fs-Uer-K V/PH/HZ 230/1/60: Exploded View and Spare Part ListDocument4 pagesModel Yuea36Fs-Uer-K V/PH/HZ 230/1/60: Exploded View and Spare Part ListJose Enrique Sanchez ThompsonNo ratings yet

- Coast LED Lenser Catalog 2009Document73 pagesCoast LED Lenser Catalog 2009rmnhsdNo ratings yet

- TIP41 / TIP41C: FeaturesDocument2 pagesTIP41 / TIP41C: FeaturesCAMILA ROMINA LUCANANo ratings yet

- MVD Universal Battery ChargersDocument4 pagesMVD Universal Battery ChargersYè Winț0% (1)

- Maintenance Manual For Embroidery Machine (Color Display Additional Manual)Document30 pagesMaintenance Manual For Embroidery Machine (Color Display Additional Manual)Azzy KickrNo ratings yet

- LG's Environmental Marketing StrategyDocument93 pagesLG's Environmental Marketing StrategyabhayNo ratings yet

- 6N137 OptocouplerDocument14 pages6N137 OptocouplerAhmad SubkhanNo ratings yet

- Tdq-172718De-65Fv02: Xxpol 1710 2690Mhz×2 65° 18dbi 0° 10° Manual or by Optional Rcu (Remote Control Unit) AntennaDocument1 pageTdq-172718De-65Fv02: Xxpol 1710 2690Mhz×2 65° 18dbi 0° 10° Manual or by Optional Rcu (Remote Control Unit) Antennakamel7777100% (1)

- Medium Voltage NPN Ignition Darlington: ApplicationsDocument4 pagesMedium Voltage NPN Ignition Darlington: ApplicationsJohan GuíaNo ratings yet

- Ass 1Document1 pageAss 1Itefa AnisaNo ratings yet

- Bike Turning Signal CircuitDocument3 pagesBike Turning Signal Circuittim schroder0% (1)

- Available IC List 03-11-2019Document18 pagesAvailable IC List 03-11-2019R. R. ArivazhaganNo ratings yet

- MT3367 Android ScatterDocument8 pagesMT3367 Android Scatterdipaamol9138No ratings yet

- AmfDocument5 pagesAmfJeffrey TeoNo ratings yet

- PS2 Manual Speed Controller GuideDocument1 pagePS2 Manual Speed Controller GuideLuis RolaNo ratings yet

- Motor Taller Sierra PDFDocument10 pagesMotor Taller Sierra PDFRolando Alfaro NuñezNo ratings yet

- 18ECE205J - FPGA-based Embedded System Design - Unit - 1Document151 pages18ECE205J - FPGA-based Embedded System Design - Unit - 1Vikram Adithya AnandNo ratings yet

- Over Current & Earth Fault Relay-Type Vn100R: FeaturesDocument4 pagesOver Current & Earth Fault Relay-Type Vn100R: Featuressujan723No ratings yet

- DO880Document4 pagesDO880sitaNo ratings yet