Professional Documents

Culture Documents

Datasheet SN3218

Uploaded by

Daniel SilvaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Datasheet SN3218

Uploaded by

Daniel SilvaCopyright:

Available Formats

SN3218

18 Channel LED Driver

Description Features

SN3218 is comprised of 18 constant current channels z 2.7V to 5.5V supply

each with independent PWM control, designed for z I2C interface, automatic address increment function

driving LEDs. The output current of each channel can be z Internal reset register

set at up to 23mA (Max.) by an external resistor. The z Modulate LED brightness with 256 steps PWM

average LED current of each channel can be changed in z Each channel can be controlled independently

256 steps by changing the PWM duty cycle through an

z -40°C to +85°C temperature range

I2C interface.

z QFN-24 (4mm × 4mm) package

The chip can be turned off by pulling the SDB pin low or

by using the software shutdown feature to reduce power

consumption. The slave address is fixed “1010 1000”.

SN3218 is available in QFN-24 (4mm × 4mm). It Applications

operates from 2.7V to 5.5V over the temperature range of

z Mobile phones and other hand-held devices for LED

-40°C to +85°C. display

z LED in home appliances

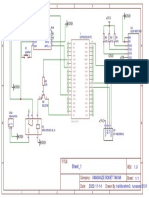

Typical Application Circuit

Figure 1 Typical application circuit

Jul. 2010 P0.1 1 SI-EN Technology

SN3218

Pin Configuration

Package Pin Configuration (Top View)

23 OUT17

22 OUT16

21 OUT15

20 OUT14

19 OUT13

24 SDB

OUT18 1 18 OUT12

R_EXT 2 17 OUT11

VDD 3 16 OUT10

QFN-24

GND 4 15 OUT9

SDA 5 14 OUT8

SCL 6 13 OUT7

OUT4 10

OUT5 11

OUT6 12

OUT1 7

OUT2 8

OUT3 9

Pin Description

No. Pin I/O Description

1 OUT18 O Output channel for LEDs.

Input terminal used to connect an external

2 R_EXT I

resistor. This regulates the output current.

3 VDD - Power supply.

4 GND - Ground.

5 SDA I/O I2C serial data.

6 SCL I I2C serial clock.

7~23 OUT1 ~ OUT17 O Output channel for LEDs.

24 SDB I Shutdown the chip when pulled low.

Thermal Pad - Connect to GND.

Oct. 2010 P0.1 2 SI-EN Technology

SN3218

Ordering Information

Order Number Package Type QTY/Reel Operating Temperature Range

SN3218I424E QFN-24 2500 -40°C ~ +85°C

SN3218 □ □ □ □

Environmental Code

E: Lead Free

Pin Code

24:24 pins

Package Type

4: QFN, 4mm × 4mm

Temperature Code

I: Industrial, -40°C ~ +85°C

Oct. 2010 P0.1 3 SI-EN Technology

SN3218

Absolute Maximum Ratings

Supply voltage, VDD ------------------------------------------------------------------------------------------------------ -0.3V ~ 6.0V

Voltage at SCL, SDA, SDB -------------------------------------------------------------------------------------- -0.3V ~ VDD +0.3V

Voltage at OUT1 to OUT18 -------------------------------------------------------------------------------------------------------- +5V

Operating temperature range ----------------------------------------------------------------------------------------- -40°C ~ +85°C

Storage temperature range ------------------------------------------------------------------------------------------ –55°C ~ +150°C

Thermal resistance, θJA (QFN-24) -------------------------------------------------------------------------------------------- 30°C/W

ESD HBM ---------------------------------------------------------------------------------------------------------------------------- 4kV

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the

specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Electrical Characteristics

TA = -40°C ~ +85°C, VDD = 2.7V ~ 5.5V, unless otherwise noted. Typical values are TA = 25°C, VDD = 3.6V.

Symbol Parameter Condition Min. Typ. Max. Unit

VDD Supply voltage 2.7 5.5 V

Maximum output current of each

IMAX VOUT = 0.6V, REXT = 3.3kΩ (Note 1) 23 mA

channel

IDD Quiescent power supply current REXT = 3.3kΩ 5.25 mA

ISD Shutdown current VSDB = 0V or software shutdown 3.1 μA

VSDB = 0V or software shutdown,

IOZ Output leakage current 1 μA

VOUT = 5V

VEXT Output voltage of R-EXT pin 1.3 V

Logic Electrical Characteristics (SDA, SCL, SDB)

VIL Logic “0” input voltage VDD = 2.7V 0.4 V

VIH Logic “1” input voltage VDD = 5.5V 1.4 V

IIL Logic “0” input current 5 nA

(Note 2)

IIH Logic “1” input current 5 nA

(Note 2)

Oct. 2010 P0.1 4 SI-EN Technology

SN3218

Digital Input Switching Characteristics (Note 2)

Symbol Parameter Condition Min. Typ. Max. Unit

fSCL Serial-Clock frequency 400 kHz

Bus free time between a STOP and a START

tBUF 1.3 μs

condition

tHD, STA Hold time (repeated) START condition 0.6 μs

tSU, STA Repeated START condition setup time 0.6 μs

tSU, STO STOP condition setup time 0.6 μs

tHD, DAT Data hold time 0.9 μs

tSU, DAT Data setup time 100 ns

tLOW SCL clock low period 1.3 μs

tHIGH SCL clock high period 0.7 μs

Rise time of both SDA and SCL signals,

tR (Note 3) 20+0.1Cb 300 ns

receiving

Fall time of both SDA and SCL signals,

tF (Note 3) 20+0.1Cb 300 ns

receiving

Note 1: The recommended minimum value of REXT is 3.3kΩ, or it may cause a large current.

Note 2: Guaranteed by design.

Note 3: Cb = total capacitance of one bus line in pF. ISINK ≤ 6mA. tR and tF measured between 0.3 × VDD and 0.7 × VDD.

Oct. 2010 P0.1 5 SI-EN Technology

SN3218

Detailed Description

I2C Interface Then the master sends an SCL pulse. If the SN3218 has

The SN3218 uses a serial bus, which conforms to the I2C received the address correctly, then it holds the SDA line

protocol, to control the chip’s functions with two wires: low during the SCL pulse. If the SDA line is not low, then

SCL and SDA. The SN3218’s slave address is “1010 the master should send a “STOP” signal (discussed later)

1000”. It only supports write operations. and abort the transfer.

The SCL line is uni-directional. The SDA line is Following acknowledge of SN3218, the register address

bi-directional (open-collector) with a pull-up resistor byte is sent, most significant bit first. SN3218 must

(typically 4.7kΩ). The maximum clock frequency generate another acknowledge indicating that the

specified by the I2C standard is 400kHz. In this register address has been received.

discussion, the master is the microcontroller and the slave Then 8-bit of data byte are sent next, most significant bit

is the SN3218. first. Each data bit should be valid while the SCL level is

The timing diagram for the I2C is shown in Figure 2. The stable high. After the data byte is sent, the SN3218 must

SDA is latched in on the stable high level of the SCL. generate another acknowledge to indicate that the data

When there is no interface activity, the SDA line should be was received.

held high. The “STOP” signal ends the transfer. To signal “STOP”,

The “START” signal is generated by lowering the SDA the SDA signal goes high while the SCL signal is high.

signal while the SCL signal is high. The start signal will Address Auto Increment

alert all devices attached to the I2C bus to check the To write multiple bytes of data into SN3218, load the

incoming address against their own chip address. address of the data register that the first data byte is

The 8-bit chip address is sent next, most significant bit intended for. During the SN3218 acknowledge of

first. Each address bit must be stable while the SCL level receiving the data byte, the internal address pointer will

is high. increment by one. The next data byte sent to SN3218 will

After the last bit of the chip address is sent, the master be placed in the new address, and so on. The auto

checks for the SN3218’s acknowledge. The master increment of the address will continue as long as data

releases the SDA line high (through a pull-up resistor). continues to be written to SN3218 (Figure 5).

Figure 2 Interface timing

SDA

SCL

DATA LINE STABLE; CHANGE OF DATA

DATA VALID ALLOWED

Figure 3 Bit transfer

Figure 4 Writing to SN3218(Typical)

Oct. 2010 P0.1 6 SI-EN Technology

SN3218

1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9

SDA D7 D6 D5 D4 D3 D2 D1 D0 A D7 D6 D5 D4 D3 D2 D1 D0 A D7 D6 D5 D4 D3 D2 D1 D0 A

SCL S

Start Ack Ack Ack

by SN3218 Address by Register Address by Data 1 Byte by

Master Byte SN3218 Byte m SN3218 (Write in Register m) SN3218

9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9

A D7 D6 D5 D4 D3 D2 D1 D0 A D7 D6 D5 D4 D3 D2 D1 D0 A

P

Ack Ack Ack Stop

by Data (n-1) Byte by Data n Byte by by

SN3218 (Write in Register m+n-2) SN3218 (Write in Register m+n-1) SN3218 Master

Figure 5 Writing to SN3218(Automatic address increment)

Registers Definitions

Table 1 Register Function

Address Name Function Table Default

00h Shutdown Register Set software shutdown mode of SN3218 2

01h~12h PWM Register 18 channels PWM duty cycle data register 3

13h LED Control Register1 Channel 1 to 6 enable bit 4 0000 0000

14h LED Control Register2 Channel 7 to 12 enable bit 5

15h LED Control Register3 Channel 13 to 18 enable bit 6

Load PWM Register and LED Control

16h Update Register -

Register’s data xxxx xxxx

17h Reset Register Reset all registers into default -

Table 2 00h Shutdown Register The average output current may be computed using the

Formula (1):

Bit D7:D1 D0

I MAX 7

Name Reserved SSD I OUT = ⋅ ∑ D[n] ⋅ 2 n (1)

256 n=0

Default 000000 0

Where “n” indicates the bit location in the respective

The Shutdown Register sets software shutdown mode of PWM register.

SN3218. For example: D7:D0 = 10110101,

SSD Software Shutdown Enable IOUT = IMAX (20+22+24+25+27)/256

0 Software shutdown mode See Formula (2) in Page 9 to calculate the IMAX.

1 Normal operation

Table 4 13h LED Control Register1(OUT1~OUT6)

Table 3 01h~12h PWM Register(OUT1~OUT18)

Bit D7:D0 Bit D7:D6 D5:D0

Name Reserved OUT6:OUT1

Name PWM

Default 00 000000

Default 0000 0000

Table 5 14h LED Control Register2(OUT7~OUT12)

The PWM Registers adjusts LED luminous intensity in

256 steps. Bit D7:D6 D5:D0

The value of a channel’s PWM Register decides the Name Reserved OUT12:OUT7

average output current for each output, OUT1~OUT18. Default 00 000000

Oct. 2010 P0.1 7 SI-EN Technology

SN3218

Table 6 15h LED Control Register3(OUT13~OUT18) 16h PWM Update Register

The data sent to the PWM Registers and the LED

Bit D7:D6 D5:D0

Control Registers will be stored in temporary registers. A

Name Reserved OUT18:OUT13 write operation of any 8-bit value to the Update Register

is required to update the registers (01h~15h).

Default 00 000000

The LED Control Registers store the on or off state of 17h Reset Register

each column LED. Once user writes any 8-bit data to the Reset Register,

OUTx LED State SN3218 will reset all registers to default value. On initial

0 LED off power-up, the SN3218 registers are reset to their default

1 LED on values for a blank display.

Oct. 2010 P0.1 8 SI-EN Technology

SN3218

Typical Application

256

PWM Control

224

The PWM Registers (01h~12h) can modulate LED

brightness of 18 channels with 256 steps. For example, if 192

the data in PWM Register is “0000 0100”, then the PWM

PWM Data

160

is the fourth step.

128

Writing new data continuously to the registers can

modulate the brightness of the LEDs to achieve a 96

breathing effect. 64

32

REXT

0

The maximum output current of OUT1~OUT18 can be 0 4 8 12 16 20 24 28 32

adjusted by the external resistor, REXT, as described in Intensity Steps

Formula (2). Figure 6 Gamma correction(32 steps)

VEXT Choosing more gamma steps provides for a more

I MAX = x ⋅ (2) continuous looking breathing effect. This is useful for

REXT

very long breathing cycles. The recommended

x = 58.5, VOUT = 0.6V, VEXT = 1.3V. configuration is defined by the breath cycle T. When

The recommended minimum value of REXT is 3.3kΩ. T=1s, choose 32 gamma steps, when T=2s, choose 64

gamma steps. The user must decide the final number of

gamma steps not only by the LED itself, but also based

Gamma Correction on the visual performance of the finished product.

In order to perform a better visual LED breathing effect

we recommend using a gamma corrected PWM value to 256

set the LED intensity. This results in a reduced number of 224

steps for the LED intensity setting, but causes the change

in intensity to appear more linear to the human eye. 192

Gamma correction, also known as gamma compression

PWM Data

160

or encoding, is used to encode linear luminance to match 128

the non-linear characteristics of display. Since the

SN3218 can modulate the brightness of the LEDs with 96

256 steps, a gamma correction function can be applied 64

when computing each subsequent LED intensity setting

32

such that the changes in brightness matches the human

eye's brightness curve. 0

0 8 16 24 32 40 48 56 64

Intensity Steps

Table 7 32 gamma steps with 256 PWM steps Figure 7 Gamma correction(64 steps)

C(0) C(1) C(2) C(3) C(4) C(5) C(6) C(7)

0 1 2 4 6 10 13 18 Shutdown Mode

C(8) C(9) C(10) C(11) C(12) C(13) C(14) C(15) Shutdown mode can either be used as a means of

reducing power consumption or generating a flashing

22 28 33 39 46 53 61 69

display (repeatedly entering and leaving shutdown mode).

C(16) C(17) C(18) C(19) C(20) C(21) C(22) C(23) During shutdown mode all registers retain their data.

78 86 96 106 116 126 138 149 Software Shutdown

C(24) C(25) C(26) C(27) C(28) C(29) C(30) C(31)

By setting SSD bit of the Configuration Register (00h) to

“0”, the SN3218 will operate in software shutdown mode,

161 173 186 199 212 226 240 255 wherein they consume only 3.1μA (typ.) current. When

the SN3218 is in software shutdown mode, all current

sources are switched off.

Hardware Shutdown

The chip enters hardware shutdown mode when the SDB

pin is pulled low.

Oct. 2010 P0.1 9 SI-EN Technology

SN3218

Classification Reflow Profiles

Profile Feature Pb-Free Assembly

Preheat & Soak

150°C

Temperature min (Tsmin)

200°C

Temperature max (Tsmax)

60-120 seconds

Time (Tsmin to Tsmax) (ts)

Average ramp-up rate (Tsmax to Tp) 3°C/second max.

Liquidous temperature (TL) 217°C

Time at liquidous (tL) 60-150 seconds

Peak package body temperature (Tp)* Max 260°C

Time (tp)** within 5°C of the specified

Max 30 seconds

classification temperature (Tc)

Average ramp-down rate (Tp to Tsmax) 6°C/second max.

Time 25°C to peak temperature 8 minutes max.

Figure 8 Classification profile

Oct. 2010 P0.1 10 SI-EN Technology

SN3218

Tape and Reel Information

Oct. 2010 P0.1 11 SI-EN Technology

SN3218

Package Information

QFN-24

IMPORTANT NOTICE

SI-EN Technology cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a

SI-EN Technology product. SI-EN Technology reserves the right to make corrections, modifications, enhancements,

improvements, and other changes to its specifications, products and services at any time and to discontinue any

product or service without notice. Customers should obtain the latest relevant information before placing orders and

should verify that such information is current and complete.

Oct. 2010 P0.1 12 SI-EN Technology

You might also like

- Idioms and Phrases MCQs - English Grammar For Competitive ExamsDocument6 pagesIdioms and Phrases MCQs - English Grammar For Competitive ExamsgeologistlakhanNo ratings yet

- Captured Ammunition Bulletin No 1Document34 pagesCaptured Ammunition Bulletin No 1roberto porto100% (1)

- How To Attract Love and Powerful Soul ConnectionsDocument5 pagesHow To Attract Love and Powerful Soul Connectionskinzaali71916No ratings yet

- Empowerment Technologies: Quarter 3 - 8: Imaging and Design Fo R The Online Environment IDocument14 pagesEmpowerment Technologies: Quarter 3 - 8: Imaging and Design Fo R The Online Environment IShaira Jane Estrella UcolNo ratings yet

- 7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetDocument4 pages7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetallisonNo ratings yet

- Phychem Chapter 3 Part 1Document14 pagesPhychem Chapter 3 Part 1Skye DiazNo ratings yet

- Care of Unconscious Nursing LessonDocument7 pagesCare of Unconscious Nursing LessonYendrembam Taruni90% (10)

- Assignment 12Document7 pagesAssignment 12Anonymous mqIqN5zNo ratings yet

- An5092 Ais328dq Highperformance Ultralowpower 3axis Digital Output Accelerometer For Automotive Nonsafety Applications StmicroelectronicsDocument30 pagesAn5092 Ais328dq Highperformance Ultralowpower 3axis Digital Output Accelerometer For Automotive Nonsafety Applications Stmicroelectronicstomislav_darlicNo ratings yet

- TM1638 enDocument18 pagesTM1638 enfotakis michaelNo ratings yet

- TB2906HQ Toshiba Bi-CMOS Digital Audio ICDocument17 pagesTB2906HQ Toshiba Bi-CMOS Digital Audio ICul3141592No ratings yet

- DatasheetDocument16 pagesDatasheetAndres GuerreroNo ratings yet

- TA8264 DatasheetDocument14 pagesTA8264 Datasheetmariofo100% (1)

- Datasheet en 20141224Document25 pagesDatasheet en 20141224Willam TumbacoNo ratings yet

- TB62747AFG ToshibaDocument20 pagesTB62747AFG ToshibavinNo ratings yet

- TB62747AFG, TB62747AFNG: 16-Output Constant Current LED DriverDocument20 pagesTB62747AFG, TB62747AFNG: 16-Output Constant Current LED DriverSaša DinčićNo ratings yet

- Smart Dust Bin Monitoring SystemDocument1 pageSmart Dust Bin Monitoring SystemAditya ConsultancyNo ratings yet

- Toshs13553 1Document18 pagesToshs13553 1josue herreraNo ratings yet

- Detector Sony I LX 511Document13 pagesDetector Sony I LX 511rocketzhenNo ratings yet

- Datasheet - HK tb2913hq 1321740Document15 pagesDatasheet - HK tb2913hq 1321740виктор колесниковNo ratings yet

- Coolaudio V3208 DatasheetsDocument5 pagesCoolaudio V3208 DatasheetsVictorNo ratings yet

- Dual 4-Channel Analog Multiplexer/Demultiplexer AZ4052Document18 pagesDual 4-Channel Analog Multiplexer/Demultiplexer AZ4052norgenNo ratings yet

- GS8208 LED Datasheet PDFDocument12 pagesGS8208 LED Datasheet PDFDaisyNo ratings yet

- Table 15-1:: Hirose 100-Pin FX2 Edge Connector (J3)Document2 pagesTable 15-1:: Hirose 100-Pin FX2 Edge Connector (J3)Tefyta BarberanNo ratings yet

- 7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetDocument32 pages7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetMecaSoftwareNo ratings yet

- Wiring DiagramDocument4 pagesWiring DiagramDjalma MoreiraNo ratings yet

- Tle5205 2Document23 pagesTle5205 2Richard MachadoNo ratings yet

- Wiring Diagram PDFDocument6 pagesWiring Diagram PDFZoran19731No ratings yet

- MBI6024 Datasheet VA.00-EnDocument39 pagesMBI6024 Datasheet VA.00-Enastral projectNo ratings yet

- Smart Octal Low-Side Switch: LogicDocument17 pagesSmart Octal Low-Side Switch: Logicjuan echeverryNo ratings yet

- Infineon Tle7230r Ds v03 04 enDocument15 pagesInfineon Tle7230r Ds v03 04 enياسين الطنفوريNo ratings yet

- TB2926HQ: 45 W × 4-ch BTL Audio Power ICDocument18 pagesTB2926HQ: 45 W × 4-ch BTL Audio Power ICOscar RamirezNo ratings yet

- 711e9psDocument1 page711e9psElvis LinaresNo ratings yet

- Wiring DiagramDocument4 pagesWiring DiagramSimon DrumsNo ratings yet

- 1 Tle5206 2 - 1Document23 pages1 Tle5206 2 - 1Fran CastanoNo ratings yet

- Wiring DiagramDocument16 pagesWiring DiagramdudekinyoNo ratings yet

- TOSHIBA 32AV500U Wiring - DiagramDocument1 pageTOSHIBA 32AV500U Wiring - Diagramdreamyson1983No ratings yet

- 143 FlückigerDocument7 pages143 Flückigerangesoukaina216No ratings yet

- Schematic - Ticari Sistem - 2022-11-14Document1 pageSchematic - Ticari Sistem - 2022-11-14Tuna ÖzerNo ratings yet

- 38+38 Watt Dual Bridge Amplifier TDA7379 Technical MrigankaDocument2 pages38+38 Watt Dual Bridge Amplifier TDA7379 Technical MrigankaRosmary de RangelNo ratings yet

- Scard SerialDocument1 pageScard SerialRayed Awad AlsahlaneeNo ratings yet

- Tle 4726 IacDocument23 pagesTle 4726 Iacfreddys merchanNo ratings yet

- UN32C5000QF Wiring DiagramDocument5 pagesUN32C5000QF Wiring Diagramsure2kNo ratings yet

- ROHM Semicon BD68610EFV E2 - C239853Document22 pagesROHM Semicon BD68610EFV E2 - C239853Fikri HidayatNo ratings yet

- TLE7209 R InfineonDocument16 pagesTLE7209 R Infineonmobil benerNo ratings yet

- Description: Technical DataDocument17 pagesDescription: Technical DataDhivya NNo ratings yet

- Levitation LightDocument1 pageLevitation LightHamza_AK100% (1)

- AVR and 8051 USB ISP Programmer Circuit DiagramDocument1 pageAVR and 8051 USB ISP Programmer Circuit DiagramPankaj Kumar100% (1)

- VU Meter Technical MrigankaDocument2 pagesVU Meter Technical MrigankaManshi SinghNo ratings yet

- E Service ManualDocument47 pagesE Service ManualwarjisahmedNo ratings yet

- WS3620-LED Coor Const LAMP - WinsemiDocument7 pagesWS3620-LED Coor Const LAMP - WinsemivmsaNo ratings yet

- Quad Low Side Driver CircuitDocument9 pagesQuad Low Side Driver CircuitSidnei100% (1)

- Self-programming USBasp programmer for Atmel AVR controllersDocument1 pageSelf-programming USBasp programmer for Atmel AVR controllerskvladderNo ratings yet

- Service Manual TV GenesisDocument19 pagesService Manual TV GenesisTecniksNo ratings yet

- AtomicPi PinoutsDocument1 pageAtomicPi PinoutsMuriloSouzaNo ratings yet

- Rda Microelectronics Rda6625Document14 pagesRda Microelectronics Rda6625api-432313169No ratings yet

- Mcp1407driver BufferDocument28 pagesMcp1407driver BufferAntonio NappaNo ratings yet

- MC2101 TM1628 PDFDocument22 pagesMC2101 TM1628 PDFPol ErnNo ratings yet

- D D D D D D D: SN54HC541, SN74HC541 Octal Buffers and Line Drivers With 3-State OutputsDocument13 pagesD D D D D D D: SN54HC541, SN74HC541 Octal Buffers and Line Drivers With 3-State OutputsYehiver Alexis Castro ReyNo ratings yet

- Adam26p16 AbovDocument37 pagesAdam26p16 Abovwilson de jesus miranda noreñaNo ratings yet

- Control LED Drive Circuit: FeaturesDocument14 pagesControl LED Drive Circuit: FeaturesJacksonVelozNo ratings yet

- SMSC LAN8720 PHY Daughter Board Information Sheet: Schematics (Continued)Document1 pageSMSC LAN8720 PHY Daughter Board Information Sheet: Schematics (Continued)hiperdrop pbiNo ratings yet

- TB2923HQ e 061130-47157Document18 pagesTB2923HQ e 061130-47157tarek ahmedNo ratings yet

- Tle 4269Document19 pagesTle 4269Edinaldo RamosNo ratings yet

- AS1115 Datasheet v1 06 LED DriverDocument24 pagesAS1115 Datasheet v1 06 LED Driverfarianek100% (1)

- Tugas Bahasa Inggris-1Document8 pagesTugas Bahasa Inggris-1Nur KomariyahNo ratings yet

- Ac+lic Lab Manual 2018-19Document76 pagesAc+lic Lab Manual 2018-19Samanvi SaatviNo ratings yet

- Calculation of Carbon Footprint: HouseDocument3 pagesCalculation of Carbon Footprint: HouseUmut ÇağırganNo ratings yet

- CHAPTER-9, Respiration in Organisms.Document3 pagesCHAPTER-9, Respiration in Organisms.HarshitAhelani2379ScribdNo ratings yet

- Impex Kitchen Appliances PDFDocument4 pagesImpex Kitchen Appliances PDFqwqw11No ratings yet

- Image Processing Based Leaf Rot Disease, Detection of Betel Vine (Piper Betlel.)Document7 pagesImage Processing Based Leaf Rot Disease, Detection of Betel Vine (Piper Betlel.)ManiNo ratings yet

- Bs. in P&O India. Syllabus 2010Document58 pagesBs. in P&O India. Syllabus 2010Priscila Arriagada PulgarNo ratings yet

- Philips HD5 enDocument5 pagesPhilips HD5 enmohamed boufasNo ratings yet

- Quest The Last RemnantDocument67 pagesQuest The Last Remnantding suheNo ratings yet

- Reading Test 7 - PassageDocument12 pagesReading Test 7 - PassageĐinh Quốc LiêmNo ratings yet

- Jean NouvelDocument1 pageJean Nouvelc.sioson.540553No ratings yet

- Shadows On The Moon by Zoe Marriott ExtractDocument20 pagesShadows On The Moon by Zoe Marriott ExtractWalker Books100% (1)

- Line Pack Presentation - Dec 2018Document7 pagesLine Pack Presentation - Dec 2018Goran JakupovićNo ratings yet

- Determine PH by PH Indicator and Universal IndicatorDocument3 pagesDetermine PH by PH Indicator and Universal IndicatorhaleelNo ratings yet

- TheologicalDiscipleship English 2011-1Document144 pagesTheologicalDiscipleship English 2011-1bilnyangnatNo ratings yet

- XMSDS Sunflower Seed Oil 9925156Document6 pagesXMSDS Sunflower Seed Oil 9925156Lisa RobertsonNo ratings yet

- Quarter 1-Module 2 Modern ArtDocument20 pagesQuarter 1-Module 2 Modern ArtKimberly Trocio Kim100% (1)

- Effect of Water Immersion On Mechanical Properties of Polyurethane ...Document8 pagesEffect of Water Immersion On Mechanical Properties of Polyurethane ...konshoeNo ratings yet

- Final Seminar ReportDocument35 pagesFinal Seminar ReportHrutik BhandareNo ratings yet

- Path Loss Models and Wireless Propagation EffectsDocument17 pagesPath Loss Models and Wireless Propagation EffectsAhsan RafiqNo ratings yet

- K2N Final Internship ReportDocument55 pagesK2N Final Internship ReportAceZeta0% (1)

- Bernard BTB MIG GunsDocument8 pagesBernard BTB MIG GunsEdwin Mauricio Gallego OsorioNo ratings yet

- Guide 111: International Electrotechnical CommissionDocument7 pagesGuide 111: International Electrotechnical CommissionSayyid JifriNo ratings yet