Professional Documents

Culture Documents

Differntial Amplifier4 PDF

Uploaded by

Kangkan medhiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Differntial Amplifier4 PDF

Uploaded by

Kangkan medhiCopyright:

Available Formats

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

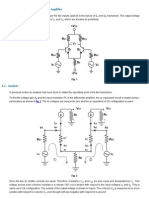

Configurations of Differential Amplifier

The differential amplifier, in the difference amplifier stage in the op-amp, can

be used in four configurations :

• Dual input balanced output differential amplifier.

• Dual input, unbalanced output differential amplifier.

• Single input, balanced output differential amplifier.

• Single input, unbalanced output differential amplifier.

The differential amplifier uses two transistors in common emitter configuration.

If output is taken between the two collectors it is called balanced output or double

ended output. While if the output is taken between one collector with respect to ground

it is called unbalanced output or single ended output. If the signal is given to both the

input terminals it is called dual input, while if the signal is given to only one input

terminal and other terminal is grounded it is called single input or single ended input.

Out of these four configurations the dual input, balanced output is the basic differential

amplifier configuration. This is shown in the Figure 2.11.1. (a). The dual input,

unbalanced output differential amplifier is shown in the Figure 2.11.1.(b). The single

input, balanced output differential amplifier is shown in the Figure 2.11.1 (c) and the

single input, unbalanced output differential amplifier is shown in the Figure 2.11.1.

(d).

EC8351 ELECTRONIC CIRCUITS I

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

Figure 2.11.1 The dual input, unbalanced output differential amplifier is shown in the

Fig.(b). The single input, balanced output differential amplifier is shown in the Fig (c) and the

single input, unbalanced output differential amplifier is shown in the Fig. (d).

Diagram Source Electronic Tutorials

EC8351 ELECTRONIC CIRCUITS I

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

A.C. Analysis of Differential Amplifier using h-Parameters

In the a.c. analysis, we will calculate the differential gain Ad, common mode

gain A C, input resistance Ri and the output resistance R 0 of the differential amplifier

circuit, using the h-parameters.

1. Differential Gain (A d)

For the differential gain calculation, the two input signals must be different from

each other. Let the two a.c. input signals be equal in magnitude but having 180" phase

difference in between them. The magnitude of each a.c. input voltage V S1 and

V S2beVs /2. The two a.c. emitter currents I e1 and I e2 are equal in magnitude and 180'

out of phase. Hence they cancel each other to get resultant a.c. current through the

emitter as zero. For the a.c. purposes emitter terminal can be grounded.

The a.c. small signal differential amplifier circuit with grounded emitter

terminal is shown in the Figure 2.11.2 As the two transistors are matched, the a.c.

equivalent circuit for the other transistor is identical to the one shown in the Fig..1.

Thus the circuit can be analyzed by considering only one transistor. This is called as

half circuit concept of analysis. The approximate hybrid model for the above circuit

can be shown as in the Fig.2, neglecting hoe,

EC8351 ELECTRONIC CIRCUITS I

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

Figure 2.11.2 AC Equvalent for differential Operation and its hybrid model

Diagram Source Electronic Tutorials

EC8351 ELECTRONIC CIRCUITS I

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

The negative sign indicates the phase difference between input and output. Now two

input signal magnitudes are VS /2 but they are opposite in polarity, as 180" out of

phase.

the expression for A d with balanced output changes as

EC8351 ELECTRONIC CIRCUITS I

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

This is the differential gain for balanced output dual input differential amplifier circuit.

2. Common Mode Gain (A C)

Let the magnitude of both the a.c. input signals be VS and are in phase with each other.

Hence the differential input Vd = 0 while the common mode input Vc is the average

value of the two.

But now both the emitter currents flows through R E in the Same direction. Hence the

total current flowing through R E is 2I e. considering only one transistor, as in the

figure 2.11.3

EC8351 ELECTRONIC CIRCUITS I

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

Figure 2.11.3 AC Equvalent for differential Operation and its hybrid model

Diagram Source Electronic Tutorials

EC8351 ELECTRONIC CIRCUITS I

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

Common Mode rejection Ratio (CMRR)

Once the differential and common mode gains are obtained, the expression for

the CMRR can be obtained as,

EC8351 ELECTRONIC CIRCUITS I

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

This is CMRR for dual input balanced output differential amplifier circuit.

EC8351 ELECTRONIC CIRCUITS I

You might also like

- Differential AmplifiersDocument8 pagesDifferential AmplifiersBhaskar YelamoluNo ratings yet

- Audio IC Circuits Manual: Newnes Circuits Manual SeriesFrom EverandAudio IC Circuits Manual: Newnes Circuits Manual SeriesRating: 5 out of 5 stars5/5 (1)

- 1differential AmpDocument5 pages1differential AmpMalliga UthirapathyNo ratings yet

- Iare - Ica - Lecture - Notes EeeDocument128 pagesIare - Ica - Lecture - Notes EeeAishwarya R100% (1)

- Electronics II Refernce NotesDocument129 pagesElectronics II Refernce NotesSri Harsha SappaNo ratings yet

- Differential AmplifierDocument15 pagesDifferential AmplifierrppvchNo ratings yet

- Operational AmplifiersDocument106 pagesOperational AmplifiersVivek GandhiNo ratings yet

- Basics of Differential AmplifierDocument6 pagesBasics of Differential AmplifierveeranjaneyulugopuNo ratings yet

- Opamp Lecture PDFDocument163 pagesOpamp Lecture PDFPriyatham KattaNo ratings yet

- Operational Amplifiers:: 1 2 E1 E2 C1 C2 CC EEDocument13 pagesOperational Amplifiers:: 1 2 E1 E2 C1 C2 CC EEAbdulhafeez ShaikNo ratings yet

- Differential Amplifier PDFDocument42 pagesDifferential Amplifier PDFrsbecool100% (2)

- Analog Circuts by Pramod Agrawal From Iit RookeeDocument168 pagesAnalog Circuts by Pramod Agrawal From Iit Rookeebalu2103100% (1)

- Op Amp LectureDocument39 pagesOp Amp LectureJani SkNo ratings yet

- APP Elec II CH - 2Document25 pagesAPP Elec II CH - 2Bizuayehu MamuyeNo ratings yet

- Printed Notes On Operational Amplifiers and Differential Amplifier and Numericals Based On The SameDocument98 pagesPrinted Notes On Operational Amplifiers and Differential Amplifier and Numericals Based On The SameDiptiNo ratings yet

- Differential Amplifiers:: 1 2 E1 E2 C1 C2 CC EEDocument8 pagesDifferential Amplifiers:: 1 2 E1 E2 C1 C2 CC EEMudit MittalNo ratings yet

- Diff - Op Amp PDFDocument5 pagesDiff - Op Amp PDFPoonam mirkaleNo ratings yet

- AC DC Analysis BJT Diffrential Amp PDFDocument8 pagesAC DC Analysis BJT Diffrential Amp PDFtanishk jainNo ratings yet

- Metallization Process Is Used in Interconn DesiredDocument52 pagesMetallization Process Is Used in Interconn DesiredSanjay KashiNo ratings yet

- Differential Amplifier CircuitDocument19 pagesDifferential Amplifier Circuitbbwx4114No ratings yet

- Chapter 11 Differential Amplifier CircuitsDocument34 pagesChapter 11 Differential Amplifier CircuitsNayr JTNo ratings yet

- 4 2 Eee 4237Document30 pages4 2 Eee 4237TEFTI Universitas PertaminaNo ratings yet

- Ac MergedDocument486 pagesAc Mergedsanket panchalNo ratings yet

- Analog Circuit EC 405 UNIT IIDocument23 pagesAnalog Circuit EC 405 UNIT IIErfana YasminNo ratings yet

- Electronics-Communication Engineering Analog-Electronics Differential-Amplifiers NotesDocument23 pagesElectronics-Communication Engineering Analog-Electronics Differential-Amplifiers Notesitsmoulali212No ratings yet

- EE2003-E03 Operational AmplifierDocument6 pagesEE2003-E03 Operational AmplifierntldvlaiNo ratings yet

- AC PPTDocument28 pagesAC PPTPrajwal BirwadkarNo ratings yet

- Differential Amplifier Omp Amplifier GateDocument8 pagesDifferential Amplifier Omp Amplifier GatewatsondalphyNo ratings yet

- Unit IiiDocument16 pagesUnit Iiikannan305No ratings yet

- Multi SimDocument4 pagesMulti SimSulman ShahzadNo ratings yet

- Biological Amplifiers PDFDocument5 pagesBiological Amplifiers PDFMariya JohnyNo ratings yet

- Dual InputDocument5 pagesDual InputPrempal TomarNo ratings yet

- Linear IC Applications and Its UsesDocument52 pagesLinear IC Applications and Its UsesVenkateshYadavNo ratings yet

- Operational AmplifierDocument112 pagesOperational AmplifierEdson TorresNo ratings yet

- Elctronics Assignment CMM DefinitionsDocument18 pagesElctronics Assignment CMM DefinitionsAbdul HafeezNo ratings yet

- Co-3 MaterialDocument35 pagesCo-3 MaterialMLM TELUGU GAMERSNo ratings yet

- Lica Unit-1 Notes (3-1 ECE)Document52 pagesLica Unit-1 Notes (3-1 ECE)vasantha_btech90% (20)

- Notes Opamp Sem 4Document18 pagesNotes Opamp Sem 4Narendra SinhaNo ratings yet

- Dual Input, Balanced Output Difference AmplifierDocument2 pagesDual Input, Balanced Output Difference AmplifierRamakrishna Vadlamudi100% (1)

- Operational AmplifierDocument20 pagesOperational Amplifiersenpaixd0110No ratings yet

- Op AmpDocument8 pagesOp Ampsalihbayar1464No ratings yet

- Unit 2 - NotesDocument52 pagesUnit 2 - NotesJohnsi JNo ratings yet

- Electronics CircuitDocument0 pagesElectronics Circuitwww.bhawesh.com.npNo ratings yet

- Unit 1 Intro To Op AmpDocument31 pagesUnit 1 Intro To Op AmpKrishna RamaNo ratings yet

- Unit V PDFDocument35 pagesUnit V PDFkarthiha12No ratings yet

- Quaid-E-Awam University of Engg., Sci. & Tech., Nawabshah Department of Telecommunication Engineering Amplifiers & OscillatorsDocument5 pagesQuaid-E-Awam University of Engg., Sci. & Tech., Nawabshah Department of Telecommunication Engineering Amplifiers & Oscillatorsakjan303No ratings yet

- Differential and Common Mode OperationDocument8 pagesDifferential and Common Mode OperationRoxanne LazarteNo ratings yet

- Nptel - Iitm.ac - in Courses Webcourse-Contents IIT-ROORKEEDocument2 pagesNptel - Iitm.ac - in Courses Webcourse-Contents IIT-ROORKEEbidyutNo ratings yet

- Ec8453-Linear Integrated Circuits-1451692048-Lic Notes Ec8453Document131 pagesEc8453-Linear Integrated Circuits-1451692048-Lic Notes Ec8453Dr.T.sivakami biherNo ratings yet

- Ldic Unit 1 3eeeDocument13 pagesLdic Unit 1 3eeespandanaNo ratings yet

- Common - Emitter Amplifier 3.1.1 ObjectiveDocument5 pagesCommon - Emitter Amplifier 3.1.1 ObjectiveQaim RazaNo ratings yet

- EDC ETRX Unit 3 Vijay Chakole - 1Document68 pagesEDC ETRX Unit 3 Vijay Chakole - 1Kavita KamerikarNo ratings yet

- Fully Differential Amplifiers: by Jim KarkiDocument5 pagesFully Differential Amplifiers: by Jim KarkithắngNo ratings yet

- Chapter Two Differential AmplifiersDocument38 pagesChapter Two Differential AmplifiersNatnaelmesfin NatnaelmesfinNo ratings yet

- Chapter 2 - L1Document20 pagesChapter 2 - L1Markos NiguseNo ratings yet

- Lecture Notes: Department of Electrical & Electronics EngineeringDocument47 pagesLecture Notes: Department of Electrical & Electronics EngineeringSivaranjaniNo ratings yet

- Differential AmplifierDocument9 pagesDifferential AmplifierAkshay RajputNo ratings yet

- ENGR2200 Lab Manual Lab2Document12 pagesENGR2200 Lab Manual Lab2Sure TipsNo ratings yet