Professional Documents

Culture Documents

Delaychip 22022000

Uploaded by

essen999Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Delaychip 22022000

Uploaded by

essen999Copyright:

Available Formats

4 Channel Programmable

Delay Generation ASIC

Thomas H. Toifl

EP/MIC

Delay Chip Thomas Toifl CERN / EP / MIC

Delaychip Overview

4Delays Digital signals

4Delay can be programmed in 1ns steps

44+1 independent delay channels

4Needs 40Mhz clock as timing reference

4Programmed via I2C interface

44 bit I2C address space

Delay Chip Thomas Toifl CERN / EP / MIC

Delaychip Block diagram

In0 Out0

delay/MUX

Out1

In1

delay/MUX

4 digital inputs In2 Out2 4 digital outputs

delay/MUX

Out3

In3

delay/MUX

Vcntr 4 5

Clk OutClk

40 Mhz clock DLL/MUX Skewed clock out

w_en delay

I2C

Interface

SCL

SDA } I2C Bus

5 Addr

Interface

Delay Chip Thomas Toifl CERN / EP / MIC

Delay Locked Loop (DLL)

in

Phase detector

Loop filter

Charge pump Vctrl

Multiplexer

out

Delay Chip Thomas Toifl CERN / EP / MIC

Timing diagram

T0

fIN

t

fOUT ...

t

0123 … 24ns

Delay Chip Thomas Toifl CERN / EP / MIC

2

IC Command word format

Data Format:

7 6 5 4 3 2 1 0

Bit 7-5 : device select Bit 4-0: delay select

000 signal 1 0-24 : delay (0-24ns)

001 “ 2 25 : 0 (disable output)

010 “ 3 27 : 1

011 “ 4

100 “ CLK

Delay Chip Thomas Toifl CERN / EP / MIC

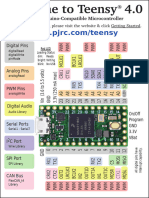

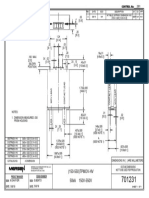

Specifications

Supply voltage: 3.3±0.2 V

Input Clock frequency 40 MHz

SCL

NC

NC

A2

A3

A4

A5

11 10 9 8 7 6 5

GND

PHI2

GND

12

13

4

3

2

VDD

SDA

GND

Signaling Low V CMOS

14

JLCC28

2.6x2.3 mm2

DO1 15 1 DO2

VDD

DO0

16

17

28

27

VDD

DO3

Chip size:

GND 18 26 GND

19 20 21 22 23 24 25

Package: 28 pin J-leaded

DI0

DI1

VDD

PHI1

GND

DI2

DI3

ceramic

Current consumption

DLL only: 3mA

1 Delay channel: 3mA+75µA/Mhz

Delay Chip Thomas Toifl CERN / EP / MIC

Delaychip Layout

I2C and

initialisation

logic

Delay-locked

Loop

Matched delay lines

Delay Chip Thomas Toifl CERN / EP / MIC

Measured Delay vs. programmed delay

25

20

Delay [ns]

15

10

0

0 5 10 15 20 25

Delay tap #

Delay Chip Thomas Toifl CERN / EP / MIC

Jitter as a function of delay tap

60

rms Jitter [ps]

55

50

45

40

35

30

25

0 5 10 15 20 25

Delay tap #

Delay Chip Thomas Toifl CERN / EP / MIC

Differential Nonlinearity

∆ T Distribution

35

30

25

Hits

20

15 σ = 26 ps

10

0

0.92 0.94 0.96 0.98 1 1.02 1.04 1.06 1.08 1.1

∆T [ns]

Delay Chip Thomas Toifl CERN / EP / MIC

Integral Nonlinearity

0.5

0.4

Deviation [ns]

0.3

0.2 Channel 1

0.1

Channel 2

0 CLK

-0.1 Channel 3

-0.2

Channel 4

-0.3

-0.4

-0.5

0 5 10 15 20 25

Delay tap #

Delay Chip Thomas Toifl CERN / EP / MIC

Current consumption / channel

Current consumption [mA]

6

500 Ω load

5

4 No external load

2

Output switched off

0

0 5 10 15 20 25 30 35 40

Frequency [MHz]

Delay Chip Thomas Toifl CERN / EP / MIC

You might also like

- LC89056W-E: Ic InformationDocument2 pagesLC89056W-E: Ic InformationCosta MafraNo ratings yet

- Ak 4399Document41 pagesAk 4399fabiolmtNo ratings yet

- Overview Data Sheets: F 3223: 4 Fold Input ModuleDocument4 pagesOverview Data Sheets: F 3223: 4 Fold Input ModulemohamadziNo ratings yet

- Acer Aspire 3010 5010 (Wistron SNIPE) PDFDocument56 pagesAcer Aspire 3010 5010 (Wistron SNIPE) PDFMustafa AkanNo ratings yet

- SamProRF Graphical Datasheet UpdatedDocument1 pageSamProRF Graphical Datasheet UpdatedYu-feng LinNo ratings yet

- TV/VCR Tuner Ic With DC/DC Converter: FeaturesDocument21 pagesTV/VCR Tuner Ic With DC/DC Converter: FeaturesEdsel SilvaNo ratings yet

- Scard SerialDocument1 pageScard SerialRayed Awad AlsahlaneeNo ratings yet

- Data Sheet: Dual 16-Bit DACDocument12 pagesData Sheet: Dual 16-Bit DACFetrian IvanNo ratings yet

- Advanced Multi-Bit 192Khz 24-Bit: General DescriptionDocument38 pagesAdvanced Multi-Bit 192Khz 24-Bit: General DescriptionPETAR STANICICNo ratings yet

- Wistron K6 IBM R51eDocument71 pagesWistron K6 IBM R51eMario Rodriguez JuradoNo ratings yet

- 2085 Hart MoDem DatasheetDocument8 pages2085 Hart MoDem DatasheetHPC HartNo ratings yet

- Lenovo B460 - V460 Wistron LA46 UMA 09922-1 Rev1 SchematicDocument48 pagesLenovo B460 - V460 Wistron LA46 UMA 09922-1 Rev1 Schematicnasir khan100% (1)

- Acer Aspire 1600 (Wistron Toucan2) PDFDocument47 pagesAcer Aspire 1600 (Wistron Toucan2) PDFMustafa AkanNo ratings yet

- Card10a Rev2 WebDocument1 pageCard10a Rev2 WebPravin NagpureNo ratings yet

- Overview Data Sheets: F 3222: 8 Fold Input ModuleDocument2 pagesOverview Data Sheets: F 3222: 8 Fold Input ModulemohamadziNo ratings yet

- Sony SVF1441V6CW - DA0HKAMB6D0 - Quanta HKA - HKBDocument36 pagesSony SVF1441V6CW - DA0HKAMB6D0 - Quanta HKA - HKBLABORATORIO ACCOMPUTERNo ratings yet

- Op17 PC CableDocument1 pageOp17 PC CablePeter UhuleNo ratings yet

- Puya P24C32C SSH Mir - C2977254Document22 pagesPuya P24C32C SSH Mir - C2977254Jorge Humberto DuqueNo ratings yet

- Lenovo b460 v460 Wistron La46uma Laptop ScheaticsDocument48 pagesLenovo b460 v460 Wistron La46uma Laptop ScheaticsVịnh DemoNo ratings yet

- RTM560 266R RealTekDocument29 pagesRTM560 266R RealTekBillal CosmosNo ratings yet

- AK4386ET - Asahi Kasei Microsystems Co., Ltd. (AKM) - Datasheet - SupportDocument18 pagesAK4386ET - Asahi Kasei Microsystems Co., Ltd. (AKM) - Datasheet - Supporttushar contractorNo ratings yet

- Alcatel Omnipcx Enterprise: Cblv36 CableDocument6 pagesAlcatel Omnipcx Enterprise: Cblv36 CableAriel BecerraNo ratings yet

- Trigorilla PinoutDocument2 pagesTrigorilla PinoutMuhammad YusufNo ratings yet

- ch340g Part 3Document3 pagesch340g Part 3David MoodyNo ratings yet

- Hmc-080 Control BoardDocument51 pagesHmc-080 Control BoardWalid AsyhariNo ratings yet

- CMT2189A Datasheet-EN-V0.8-2020915Document67 pagesCMT2189A Datasheet-EN-V0.8-2020915Rudraksh GandharvaNo ratings yet

- Training Material of MS09A and MS09L ChassisDocument47 pagesTraining Material of MS09A and MS09L Chassisبوند بوندNo ratings yet

- Cmt2150Aw: 240 - 480 MHZ Ook Stand-Alone Transmitter With EncoderDocument31 pagesCmt2150Aw: 240 - 480 MHZ Ook Stand-Alone Transmitter With EncoderLong Trần NhậtNo ratings yet

- NFCDocument8 pagesNFCkorada sai kumarNo ratings yet

- Lenovo Ideapad V360 Wistron LA36 Rev-1 SchematicDocument58 pagesLenovo Ideapad V360 Wistron LA36 Rev-1 SchematicINNOVA20212No ratings yet

- Class 1Document46 pagesClass 1Naureen ButtNo ratings yet

- MT8870DDocument12 pagesMT8870DMUHAMMAD SISWANTORONo ratings yet

- JTAG Connectors and PinoutDocument10 pagesJTAG Connectors and PinoutbalzoniaNo ratings yet

- HTTPSWWW - Micro Semiconductor - Hudatasheet97 AK4628AVQ PDFDocument42 pagesHTTPSWWW - Micro Semiconductor - Hudatasheet97 AK4628AVQ PDFPoon Electronic Training CentreNo ratings yet

- Si3012 FS ModemDocument54 pagesSi3012 FS ModemAnonymous xDBXbk89PNo ratings yet

- Circuit Descriptions: EN 34 QM16.4E LA 7Document3 pagesCircuit Descriptions: EN 34 QM16.4E LA 7avrelec100% (1)

- TDA8444Document16 pagesTDA8444Charbel TadrosNo ratings yet

- RDM 6300Document4 pagesRDM 6300Zeus KhronosNo ratings yet

- CDocument35 pagesCJagopati Jr.No ratings yet

- Coolaudio V4220M DatasheetDocument10 pagesCoolaudio V4220M DatasheetdjraagNo ratings yet

- 2.7V 4-Channel/8-Channel 12-Bit A/D Converters With SPI Serial InterfaceDocument41 pages2.7V 4-Channel/8-Channel 12-Bit A/D Converters With SPI Serial InterfacecutoNo ratings yet

- T6963CDocument28 pagesT6963Capi-19831863No ratings yet

- Atmega 32U4-Arduino Pin Mapping: Main Site Blog Playground Forum Labs Store Help Sign in RegisterDocument4 pagesAtmega 32U4-Arduino Pin Mapping: Main Site Blog Playground Forum Labs Store Help Sign in RegisterManiraj PerumalNo ratings yet

- ms-7255v21 1115Document31 pagesms-7255v21 1115vidboNo ratings yet

- Si5338a A GM PDFDocument170 pagesSi5338a A GM PDFAdeel AbbasNo ratings yet

- Acrosser Technology AR B1673 DatasheetDocument5 pagesAcrosser Technology AR B1673 DatasheetWaleed MareeNo ratings yet

- 98 Ak 4480 EfDocument44 pages98 Ak 4480 EfYurii LembergNo ratings yet

- TLP251 Datasheet en 20170821Document7 pagesTLP251 Datasheet en 20170821Lavissia GreenNo ratings yet

- Da0hk1mb6e0 Rev e MBX-247 PDFDocument39 pagesDa0hk1mb6e0 Rev e MBX-247 PDFmohamadNo ratings yet

- D D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With FifoDocument39 pagesD D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With Fifoapi-3825669No ratings yet

- D D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With FifoDocument38 pagesD D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With FifoArturo PicolinNo ratings yet

- 4 IOports v21Document24 pages4 IOports v21Thao Vo VanNo ratings yet

- PDP (Plasma Display Panel) FA (Factory Automation) High-Speed InterfaceDocument7 pagesPDP (Plasma Display Panel) FA (Factory Automation) High-Speed InterfaceJar TesNo ratings yet

- AK4346Document31 pagesAK4346naeem_aaNo ratings yet

- TLP2372 TLP2372 TLP2372 TLP2372: 1. 1. 1. 1. Applications Applications Applications ApplicationsDocument17 pagesTLP2372 TLP2372 TLP2372 TLP2372: 1. 1. 1. 1. Applications Applications Applications ApplicationsAndresPGUNo ratings yet

- GND GND: Pcint17 Pcint16 Pcint14 Pcint18 Pcint19 Pcint20 Pcint21 Pcint22 Pcint23 Pcint0 Pcint1Document1 pageGND GND: Pcint17 Pcint16 Pcint14 Pcint18 Pcint19 Pcint20 Pcint21 Pcint22 Pcint23 Pcint0 Pcint1dcNo ratings yet

- HA0101EDocument10 pagesHA0101Eessen999No ratings yet

- AN0523EDocument11 pagesAN0523Eessen999No ratings yet

- SLDDRWDocument1 pageSLDDRWessen999No ratings yet

- DWG 02Document1 pageDWG 02essen999No ratings yet

- AN0563ENDocument12 pagesAN0563ENessen999No ratings yet

- Phoenix Contact 2801637 enDocument10 pagesPhoenix Contact 2801637 enessen999No ratings yet

- Datasheet - Live: Agilent 34410A/11A 6 Digit MultimeterDocument152 pagesDatasheet - Live: Agilent 34410A/11A 6 Digit Multimeteressen999No ratings yet

- Pratima EnterprisesDocument3 pagesPratima Enterprisesessen999No ratings yet

- Ada4077 1 - 4077 2 - 4077 4Document25 pagesAda4077 1 - 4077 2 - 4077 4essen999No ratings yet

- Kubara Lamina ProduktkatalogDocument20 pagesKubara Lamina Produktkatalogessen999No ratings yet

- Applications: Radial Solid Polymer Aluminum CapacitorsDocument18 pagesApplications: Radial Solid Polymer Aluminum Capacitorsessen999No ratings yet

- LKD 54SxxxK-1 SpecificationDocument1 pageLKD 54SxxxK-1 Specificationessen999No ratings yet

- Micro PilotDocument4 pagesMicro Pilotessen999No ratings yet

- Unisonic Technologies Co., LTD: Low Voltage Audio Power AmplifierDocument5 pagesUnisonic Technologies Co., LTD: Low Voltage Audio Power Amplifieressen999No ratings yet

- Opa 4197Document50 pagesOpa 4197essen999No ratings yet

- Ultrasonic Pest Repeller: AdjustmentDocument2 pagesUltrasonic Pest Repeller: Adjustmentessen999No ratings yet

- MAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver and Receiver With 15-kV ESD ProtectionDocument30 pagesMAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver and Receiver With 15-kV ESD Protectionessen999No ratings yet

- Mux 508Document43 pagesMux 508essen999No ratings yet

- VP2020L, BSS92: Vishay SiliconixDocument4 pagesVP2020L, BSS92: Vishay Siliconixessen999No ratings yet

- Kpus 25T 16T 487Document10 pagesKpus 25T 16T 487essen999No ratings yet

- Sipmos Small-Signal Transistor BSS 88: V I R VDocument6 pagesSipmos Small-Signal Transistor BSS 88: V I R Vessen999No ratings yet

- Design ChecklistDocument19 pagesDesign Checklistessen999No ratings yet

- Catalogue Multi LayDocument1 pageCatalogue Multi Layessen999No ratings yet

- SPS 1BX XXX XX XXDocument1 pageSPS 1BX XXX XX XXessen999No ratings yet

- Applications: Radial Solid Polymer Aluminum CapacitorsDocument18 pagesApplications: Radial Solid Polymer Aluminum Capacitorsessen999No ratings yet

- Champion Electronics PVT - LTD.: Socket TO Series Machined Pins Tin Plated Sleeves How To Order Code Spr-Xxx-Xxx-Ja-XxDocument1 pageChampion Electronics PVT - LTD.: Socket TO Series Machined Pins Tin Plated Sleeves How To Order Code Spr-Xxx-Xxx-Ja-Xxessen999No ratings yet

- Amphenol: Interconnection Solution GuideDocument1 pageAmphenol: Interconnection Solution Guideessen999No ratings yet

- Energy Audit Report by CPRIDocument247 pagesEnergy Audit Report by CPRImag_ktps20021520100% (2)

- DPP 01 Periodic Table JH Sir-3576 PDFDocument5 pagesDPP 01 Periodic Table JH Sir-3576 PDFChessNo ratings yet

- What Is A Stress Intensification FactorDocument7 pagesWhat Is A Stress Intensification FactorMahendra RathoreNo ratings yet

- Crane Wheels-General InformationDocument3 pagesCrane Wheels-General InformationArvind VaishNo ratings yet

- Basic Electronics (ES-112)Document49 pagesBasic Electronics (ES-112)Bharat LalNo ratings yet

- Performance Evaluation of Existing Sunshine-Based Computing Models For Estimating Global Solar Radiation at Lagos, NigeriaDocument12 pagesPerformance Evaluation of Existing Sunshine-Based Computing Models For Estimating Global Solar Radiation at Lagos, NigeriasamuelNo ratings yet

- Penn State University Press Is Collaborating With JSTOR To Digitize, Preserve and Extend Access To Philosophy & RhetoricDocument16 pagesPenn State University Press Is Collaborating With JSTOR To Digitize, Preserve and Extend Access To Philosophy & RhetoricvanduongNo ratings yet

- SOPRANO TIM SMTP Interface Developers GuideDocument43 pagesSOPRANO TIM SMTP Interface Developers GuidenettellectNo ratings yet

- Atmos S 351 - Service ManualDocument40 pagesAtmos S 351 - Service ManualcuetlaxochitlNo ratings yet

- Astm A106-2002Document13 pagesAstm A106-2002henryNo ratings yet

- Arthashastra: Citation NeededDocument4 pagesArthashastra: Citation NeededtusharNo ratings yet

- Discover Haxeflixel FullDocument182 pagesDiscover Haxeflixel FullKristian Macanga100% (3)

- (John F. Moulder) PHI Handbook of XRay Photoelectron SpectrosDocument192 pages(John F. Moulder) PHI Handbook of XRay Photoelectron SpectrosCamilo CorredorNo ratings yet

- Metron 05 CR DataDocument10 pagesMetron 05 CR DatamkgohNo ratings yet

- E Rich Burn Control System: With Stablesense™ TechnologyDocument4 pagesE Rich Burn Control System: With Stablesense™ TechnologyYasir JamilNo ratings yet

- C 13Document33 pagesC 13rgerwwaaNo ratings yet

- Calcium Ethoxide As A Solid Base Catalyst For The PDFDocument15 pagesCalcium Ethoxide As A Solid Base Catalyst For The PDFHelmi BaharNo ratings yet

- Coding in Communication System: Channel Coding) Will Be AddressedDocument5 pagesCoding in Communication System: Channel Coding) Will Be AddressedDuge PlakolliNo ratings yet

- Cortec, VpCI-371 Application GuideDocument2 pagesCortec, VpCI-371 Application Guidemonserrat PereaNo ratings yet

- Individual Spirituality, Workplace Spirituality and Work Attitudes An Empirical Test of Direct and Interaction EffectsDocument19 pagesIndividual Spirituality, Workplace Spirituality and Work Attitudes An Empirical Test of Direct and Interaction EffectsBasharat NaeemNo ratings yet

- Alarm ListDocument4 pagesAlarm ListMirela Perenda ŠabićNo ratings yet

- Kou2003 PDFDocument6 pagesKou2003 PDFGe EffgenNo ratings yet

- Unit Iv Ce 6405Document13 pagesUnit Iv Ce 6405HanafiahHamzahNo ratings yet

- Mha Mca Cet SyllabusDocument20 pagesMha Mca Cet Syllabusm kumarNo ratings yet

- TH 2100Document67 pagesTH 2100KI TechnologiesNo ratings yet

- Tugas HKSA Deskriptor (Fitriani Choerunnisa (11171013) 3FA1)Document4 pagesTugas HKSA Deskriptor (Fitriani Choerunnisa (11171013) 3FA1)fitriani choerunnisaNo ratings yet

- Thermal Analysis and Compensation of A Double Column Machining CentreDocument9 pagesThermal Analysis and Compensation of A Double Column Machining CentreShamanth CNo ratings yet

- Import Data From Excel To Sap TableDocument11 pagesImport Data From Excel To Sap TableSajjadNo ratings yet

- Python ProgramDocument3 pagesPython ProgramGOKUL BNo ratings yet

- Sheet Pile Analysis Sheet v1.07-18.1Document2 pagesSheet Pile Analysis Sheet v1.07-18.1SES DESIGN100% (1)