Professional Documents

Culture Documents

Irfs7530 7ppbf

Uploaded by

Anidiobi OkwudiliOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Irfs7530 7ppbf

Uploaded by

Anidiobi OkwudiliCopyright:

Available Formats

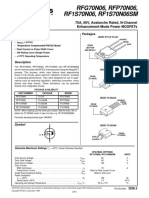

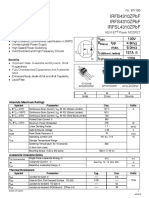

StrongIRFET™

IRFS7530-7PPbF

Application HEXFET® Power MOSFET

Brushed Motor drive applications

BLDC Motor drive applications D

VDSS 60V

Battery powered circuits RDS(on) typ. 1.15m

Half-bridge and full-bridge topologies G

max 1.4m

Synchronous rectifier applications ID (Silicon Limited) 338A

Resonant mode power supplies S

ID (Package Limited) 240A

OR-ing and redundant power switches

Benefits

Improved Gate, Avalanche and Dynamic dV/dt Ruggedness

Fully Characterized Capacitance and Avalanche SOA

Enhanced body diode dV/dt and dI/dt Capability

Lead-Free, RoHS Compliant

G D S

Gate Drain Source

Base Part Number Package Type Standard Pack Complete Part Number

Form Quantity

Tube 50 IRFS7530-7PPbF

IRFS7530-7PPbF D2Pak-7PIN

Tape and Reel Left 800 IRFS7530TRL7PP

( )

6 350

RDS(on), Drain-to -Source On Resistance m

ID = 100A

Limited By Package

5 300

250

ID, Drain Current (A)

200

3

TJ = 125°C

150

2

100

1

TJ = 25°C

50

0

4 8 12 16 20 0

VGS, Gate-to-Source Voltage (V) 25 50 75 100 125 150 175

TC , Case Temperature (°C)

Fig 1. Typical On-Resistance vs. Gate Voltage Fig 2. Maximum Drain Current vs. Case Temperature

1 www.irf.com © 2015 International Rectifier Submit Datasheet Feedback March 5, 2015

IRFS7530-7PPbF

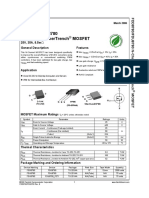

Absolute Maximium Rating

Symbol Parameter Max. Units

ID @ TC = 25°C Continuous Drain Current, VGS @ 10V (Silicon Limited) 338

ID @ TC = 100°C Continuous Drain Current, VGS @ 10V (Silicon Limited) 239

A

ID @ TC = 25°C Continuous Drain Current, VGS @ 10V (Wire Bond Limited) 240

IDM Pulsed Drain Current 1450

PD @TC = 25°C Maximum Power Dissipation 375 W

Linear Derating Factor 2.5 W/°C

VGS Gate-to-Source Voltage ± 20 V

TJ Operating Junction and

-55 to + 175

TSTG Storage Temperature Range °C

Soldering Temperature, for 10 seconds (1.6mm from case) 300

Avalanche Characteristics

EAS (Thermally limited) Single Pulse Avalanche Energy 526

mJ

EAS (Thermally limited) Single Pulse Avalanche Energy 1029

IAR Avalanche Current A

See Fig 14, 15, 23a, 23b

EAR Repetitive Avalanche Energy mJ

Thermal Resistance

Symbol Parameter Typ. Max. Units

RJC Junction-to-Case ––– 0.40 °C/W

RJA Junction-to-Ambient ––– 40

Static @ TJ = 25°C (unless otherwise specified)

Symbol Parameter Min. Typ. Max. Units Conditions

V(BR)DSS Drain-to-Source Breakdown Voltage 60 ––– ––– V VGS = 0V, ID = 250µA

V(BR)DSS/TJ Breakdown Voltage Temp. Coefficient ––– 33 ––– mV/°C Reference to 25°C, ID = 1mA

RDS(on) Static Drain-to-Source On-Resistance ––– 1.15 1.4 m VGS = 10V, ID = 100A

––– 1.4 ––– m VGS = 6.0V, ID = 50A

VGS(th) Gate Threshold Voltage 2.1 ––– 3.7 V VDS = VGS, ID = 250µA

IDSS Drain-to-Source Leakage Current ––– ––– 1.0 µA VDS = 60 V, VGS = 0V

––– ––– 150 VDS = 60V,VGS = 0V,TJ =125°C

IGSS Gate-to-Source Forward Leakage ––– ––– 100 nA VGS = 20V

Gate-to-Source Reverse Leakage ––– ––– -100 VGS = -20V

RG Gate Resistance ––– 2.2 –––

Notes:

Calculated continuous current based on maximum allowable junction temperature. Bond wire current limit is 240A.

Note that current limitations arising from heating of the device leads may occur with some lead mounting

arrangements. (Refer to AN-1140)

Repetitive rating; pulse width limited by max. junction temperature.

Limited by TJmax, starting TJ = 25°C, L = 105µH, RG = 50, IAS = 100A, VGS =10V.

ISD 100A, di/dt 1575A/µs, VDD V(BR)DSS, TJ 175°C.

Pulse width 400µs; duty cycle 2%.

Coss eff. (TR) is a fixed capacitance that gives the same charging time as Coss while VDS is rising from 0 to 80% VDSS.

Coss eff. (ER) is a fixed capacitance that gives the same energy as Coss while VDS is rising from 0 to 80% VDSS.

R is measured at TJ approximately 90°C.

Limited by TJmax, starting TJ = 25°C, L = 1mH, RG = 50, IAS = 45A, VGS =10V.

When mounted on 1" square PCB (FR-4 or G-10 Material). For recommended footprint and soldering techniques

refer to application note #AN-994: http://www.irf.com/technical-info/appnotes/an-994.pdf

2 www.irf.com © 2015 International Rectifier Submit Datasheet Feedback March 5, 2015

IRFS7530-7PPbF

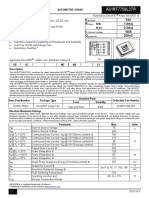

Dynamic Electrical Characteristics @ TJ = 25°C (unless otherwise specified)

Symbol Parameter Min. Typ. Max. Units Conditions

gfs Forward Transconductance 249 ––– ––– S VDS = 10V, ID =100A

Qg Total Gate Charge ––– 236 354 ID = 100A

Qgs Gate-to-Source Charge ––– 62 ––– VDS = 30V

nC

Qgd Gate-to-Drain Charge ––– 73 ––– VGS = 10V

Qsync Total Gate Charge Sync. (Qg - Qgd) ––– 163 –––

td(on) Turn-On Delay Time ––– 24 ––– VDD = 30V

tr Rise Time ––– 102 ––– ID = 100A

ns

td(off) Turn-Off Delay Time ––– 168 ––– RG= 2.7

tf Fall Time ––– 79 ––– VGS = 10V

Ciss Input Capacitance ––– 12960 ––– VGS = 0V

Coss Output Capacitance ––– 1270 ––– VDS = 25V

Crss Reverse Transfer Capacitance ––– 760 ––– pF ƒ = 1.0MHz

Coss eff.(ER) Effective Output Capacitance (Energy Related) ––– 1248 ––– VGS = 0V, VDS = 0V to 48V

Coss eff.(TR) Output Capacitance (Time Related) ––– 1590 ––– VGS = 0V, VDS = 0V to 48V

Diode Characteristics

Symbol Parameter Min. Typ. Max. Units Conditions

Continuous Source Current MOSFET symbol D

IS ––– ––– 338

(Body Diode) showing the

A

Pulsed Source Current integral reverse G

ISM ––– ––– 1450

(Body Diode) p-n junction diode. S

VSD Diode Forward Voltage ––– ––– 1.2 V TJ = 25°C,IS = 100A,VGS = 0V

dv/dt Peak Diode Recovery dv/dt ––– 8.5 ––– V/ns TJ = 175°C,IS =100A,VDS = 60V

––– 48 ––– TJ = 25°C VDD = 51V

trr Reverse Recovery Time ns

––– 50 ––– TJ = 125°C IF = 100A,

––– 72 ––– TJ = 25°C di/dt = 100A/µs

Qrr Reverse Recovery Charge nC

––– 83 ––– TJ = 125°C

IRRM Reverse Recovery Current ––– 2.5 ––– A TJ = 25°C

3 www.irf.com © 2015 International Rectifier Submit Datasheet Feedback March 5, 2015

IRFS7530-7PPbF

10000 10000

VGS VGS

TOP 15V TOP 15V

ID, Drain-to-Source Current (A) 10V 10V

ID, Drain-to-Source Current (A)

8.0V 8.0V

1000 7.0V 7.0V

6.0V 6.0V

5.5V

1000 5.5V

5.0V 5.0V

BOTTOM 4.5V BOTTOM 4.5V

100

100

10 4.5V

4.5V

60µs PULSE WIDTH 60µs PULSE WIDTH

Tj = 25°C Tj = 175°C

1 10

0.1 1 10 100 0.1 1 10 100

VDS, Drain-to-Source Voltage (V) VDS, Drain-to-Source Voltage (V)

Fig 3. Typical Output Characteristics Fig 4. Typical Output Characteristics

10000 2.5

RDS(on) , Drain-to-Source On Resistance

ID = 100A

VGS = 10V

ID, Drain-to-Source Current (A)

1000

2.0

TJ = 175°C

100

(Normalized)

1.5

TJ = 25°C

10

1.0

1

VDS = 25V

60µs PULSE WIDTH

0.1

0.5

2.0 4.0 6.0 8.0

-60 -40 -20 0 20 40 60 80 100 120 140 160 180

VGS, Gate-to-Source Voltage (V)

TJ , Junction Temperature (°C)

Fig 5. Typical Transfer Characteristics Fig 6. Normalized On-Resistance vs. Temperature

1000000 14

VGS = 0V, f = 1 MHZ

C iss = Cgs + C gd , Cds SHORTED ID= 100A VDS= 48V

12

VGS, Gate-to-Source Voltage (V)

C rss = C gd VDS= 30V

100000 C oss = C ds + C gd VDS= 12V

10

C, Capacitance (pF)

8

Ciss

10000

6

Coss 4

1000

Crss

2

0

100

0 50 100 150 200 250 300

1 10 100

QG Total Gate Charge (nC)

VDS, Drain-to-Source Voltage (V)

Fig 8. Typical Gate Charge vs.

Fig 7. Typical Capacitance vs. Gate-to-Source Voltage

4 www.irf.com © 2015 International Rectifier Submit Datasheet Feedback March 5, 2015

IRFS7530-7PPbF

10000

10000

ISD, Reverse Drain Current (A)

ID, Drain-to-Source Current (A)

1000

1000

TJ = 175°C 100µsec

100 100

1msec

Limited by

Package

10 TJ = 25°C

10

OPERATION IN THIS AREA

LIMITED BY R (on)

DS

10msec

1 1 Tc = 25°C

Tj = 175°C

VGS = 0V Single Pulse DC

0.1 0.1

0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 0.1 1 10 100

VSD, Source-to-Drain Voltage (V) VDS, Drain-toSource Voltage (V)

Fig 9. Typical Source-Drain Diode Forward Voltage Fig 10. Maximum Safe Operating Area

V(BR)DSS, Drain-to-Source Breakdown Voltage (V)

80 2.0

Id = 1.0mA

1.5

Energy (µJ)

70 1.0

0.5

60 0.0

0 10 20 30 40 50 60

-60 -40 -20 0 20 40 60 80 100120140160180

TJ , Temperature ( °C ) VDS, Drain-to-Source Voltage (V)

Fig 11. Drain-to-Source Breakdown Voltage Fig 12. Typical Coss Stored Energy

2.2

( )

RDS(on), Drain-to -Source On Resistance m

VGS = 5.5V

VGS = 6.0V

2.0

VGS = 7.0V

VGS = 8.0V

1.8

VGS = 10V

1.6

1.4

1.2

1.0

0 50 100 150 200

ID, Drain Current (A)

Fig 13. Typical On-Resistance vs. Drain Current

5 www.irf.com © 2015 International Rectifier Submit Datasheet Feedback March 5, 2015

IRFS7530-7PPbF

1

Thermal Response ( ZthJC ) °C/W

D = 0.50

0.1

0.20

0.10

0.05

0.01 0.02

0.01

0.001 SINGLE PULSE

( THERMAL RESPONSE ) Notes:

1. Duty Factor D = t1/t2

2. Peak Tj = P dm x Zthjc + Tc

0.0001

1E-006 1E-005 0.0001 0.001 0.01 0.1

t1 , Rectangular Pulse Duration (sec)

Fig 14. Maximum Effective Transient Thermal Impedance, Junction-to-Case

1000

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming Tj = 150°C and

Tstart =25°C (Single Pulse)

Avalanche Current (A)

100

10

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming j = 25°C and

Tstart = 150°C. (Single Pulse)

1

1.0E-06 1.0E-05 1.0E-04 1.0E-03 1.0E-02 1.0E-01

tav (sec)

Fig 15. Avalanche Current vs. Pulse Width

2400

Notes on Repetitive Avalanche Curves , Figures 14, 15:

EAS, Single Pulse Avalanche Energy (mJ)

ID

(For further info, see AN-1005 at www.irf.com)

2000 TOP 21A 1.Avalanche failures assumption:

44A Purely a thermal phenomenon and failure occurs at a

BOTTOM 100A temperature far in excess of Tjmax. This is validated for every

1600 part type.

2. Safe operation in Avalanche is allowed as long asTjmax is not

exceeded.

1200

3. Equation below based on circuit and waveforms shown in Figures

23a, 23b.

800 4. PD (ave) = Average power dissipation per single avalanche pulse.

5. BV = Rated breakdown voltage (1.3 factor accounts for voltage

increase during avalanche).

400 6. Iav = Allowable avalanche current.

7. T = Allowable rise in junction temperature, not to exceed Tjmax

(assumed as 25°C in Figure 14, 15).

0 tav = Average time in avalanche.

25 50 75 100 125 150 175 D = Duty cycle in avalanche = tav ·f

Starting TJ, Junction Temperature (°C) ZthJC(D, tav) = Transient thermal resistance, see Figures 13)

PD (ave) = 1/2 ( 1.3·BV·Iav) = T/ ZthJC

Iav = 2T/ [1.3·BV·Zth]

Fig 16. Maximum Avalanche Energy vs. Temperature EAS (AR) = PD (ave)·tav

6 www.irf.com © 2015 International Rectifier Submit Datasheet Feedback March 5, 2015

IRFS7530-7PPbF

4.0 16

IF = 60A

VGS(th) Gate threshold Voltage (V)

3.5 VR = 51V

12 TJ = 25°C

TJ = 125°C

3.0

IRRM (A)

2.5 ID = 250µA 8

ID = 1.0mA

2.0 ID = 1.0A

4

1.5

1.0 0

-75 -50 -25 0 25 50 75 100 125 150 175 0 200 400 600 800 1000

TJ , Temperature ( °C ) diF /dt (A/µs)

Fig 17. Threshold Voltage vs. Temperature Fig 18. Typical Recovery Current vs. dif/dt

16 500

IF = 100A IF = 60A

VR = 51V VR = 51V

400 TJ = 25°C

12 TJ = 25°C

TJ = 125°C TJ = 125°C

300

QRR (nC)

IRRM (A)

200

4

100

0 0

0 200 400 600 800 1000 0 200 400 600 800 1000

diF /dt (A/µs) diF /dt (A/µs)

Fig 19. Typical Recovery Current vs. dif/dt Fig 20. Typical Stored Charge vs. dif/dt

500

IF = 100A

VR = 51V

400 TJ = 25°C

TJ = 125°C

300

QRR (nC)

200

100

0

0 200 400 600 800 1000

diF /dt (A/µs)

Fig 21. Typical Stored Charge vs. dif/dt

7 www.irf.com © 2015 International Rectifier Submit Datasheet Feedback March 5, 2015

IRFS7530-7PPbF

Fig 22. Peak Diode Recovery dv/dt Test Circuit for N-Channel HEXFET® Power MOSFETs

V(BR)DSS

15V

tp

L DRIVER

VDS

RG D.U.T +

V

- DD

IAS A

20V

tp 0.01 I AS

Fig 23a. Unclamped Inductive Test Circuit Fig 23b. Unclamped Inductive Waveforms

Fig 24a. Switching Time Test Circuit Fig 24b. Switching Time Waveforms

Id

Vds

Vgs

Vgs(th)

Qgs1 Qgs2 Qgd Qgodr

Fig 25a. Gate Charge Test Circuit Fig 25b. Gate Charge Waveform

8 www.irf.com © 2015 International Rectifier Submit Datasheet Feedback March 5, 2015

IRFS7530-7PPbF

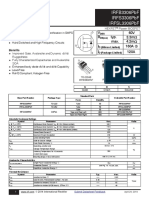

D2Pak-7Pin Package Outline (Dimensions are shown in millimeters (inches))

Note: For the most current drawing please refer to IR website at http://www.irf.com/package/

9 www.irf.com © 2015 International Rectifier Submit Datasheet Feedback March 5, 2015

IRFS7530-7PPbF

D2Pak-7Pin Part Marking Information

D2Pak-7Pin Tape and Reel

Note: For the most current drawing please refer to IR website at http://www.irf.com/package/

10 www.irf.com © 2015 International Rectifier Submit Datasheet Feedback March 5, 2015

IRFS7530-7PPbF

Qualification Information†

Industrial

Qualification Level

(per JEDEC JESD47F) ††

MSL1

Moisture Sensitivity Level D2Pak-7Pin

(per JEDEC J-STD-020D††)

RoHS Compliant Yes

† Qualification standards can be found at International Rectifier’s web site: http://www.irf.com/product-info/reliability/

†† Applicable version of JEDEC standard at the time of product release.

Revision History

Date Comment

Updated EAS (L =1mH) = 1029mJ on page 2

03/05/2015 Updated note 9 “Limited by TJmax, starting TJ = 25°C, L = 1mH, RG = 50, IAS = 45A, VGS =10V” on page 2

Updated package outline on page 9 .

IR WORLD HEADQUARTERS: 101 N. Sepulveda Blvd., El Segundo, California 90245, USA

To contact International Rectifier, please visit http://www.irf.com/whoto-call/

11 www.irf.com © 2015 International Rectifier Submit Datasheet Feedback March 5, 2015

You might also like

- Irfp7530pbf PDFDocument10 pagesIrfp7530pbf PDFPaulo Roberto s freireNo ratings yet

- Irfs7434 7ppbfDocument11 pagesIrfs7434 7ppbfAlecio SilvaNo ratings yet

- Strong Fet™ Irfb7446Pbf: Application V 40V R Typ. 2.6M Max 3.3M I 123A I 120ADocument10 pagesStrong Fet™ Irfb7446Pbf: Application V 40V R Typ. 2.6M Max 3.3M I 123A I 120ANobreak ServiceNo ratings yet

- Irfb 7537Document13 pagesIrfb 7537Cris ducusinNo ratings yet

- Strong Fet™ Irfb7546Pbf: Application V 60V R Typ. 6.0M Max 7.3M I 75ADocument10 pagesStrong Fet™ Irfb7546Pbf: Application V 60V R Typ. 6.0M Max 7.3M I 75AYaraNo ratings yet

- Datasheet PDFDocument10 pagesDatasheet PDFHank SvensonNo ratings yet

- Strong Fet™ Irfb7545Pbf: Application V 60V R Typ. 4.9M Max 5.9M I 95ADocument10 pagesStrong Fet™ Irfb7545Pbf: Application V 60V R Typ. 4.9M Max 5.9M I 95Aejdigger ejNo ratings yet

- Irl40b215 N Mos 40V 140aDocument10 pagesIrl40b215 N Mos 40V 140arem remNo ratings yet

- IRFR7740 DataSheetDocument13 pagesIRFR7740 DataSheetSummer SpringNo ratings yet

- Strong Fet Irfb7430Pbf: V 40V R Typ. 1.0M Max. 1.3M I 409A I 195ADocument10 pagesStrong Fet Irfb7430Pbf: V 40V R Typ. 1.0M Max. 1.3M I 409A I 195AdixonNo ratings yet

- 200v MosfetDocument18 pages200v MosfetshivaramakrishnaNo ratings yet

- Infn S A0004165546 1Document17 pagesInfn S A0004165546 1Bipin VishwakarmaNo ratings yet

- IRL40SC228Document10 pagesIRL40SC228Rafael GuevaraNo ratings yet

- IRFS3207Z DataSheetDocument13 pagesIRFS3207Z DataSheetSummer SpringNo ratings yet

- Strong Fet Irfs7437-7Ppbf: V 40V R Typ. 1.1Mω Max. 1.4M I 295A I 195ADocument11 pagesStrong Fet Irfs7437-7Ppbf: V 40V R Typ. 1.1Mω Max. 1.4M I 295A I 195AAriel Rodrigo MuñozNo ratings yet

- RFD8P05, RFD8P05SM, RFP8P05: Features DescriptionDocument5 pagesRFD8P05, RFD8P05SM, RFP8P05: Features DescriptionRicardo VieiraNo ratings yet

- IRFB3206 Mosfet 30A Solar Charge ControllerDocument12 pagesIRFB3206 Mosfet 30A Solar Charge ControllerLord_JoelNo ratings yet

- Rfg70N06, Rfp70N06, Rf1S70N06, Rf1S70N06Sm: 70A, 60V, Avalanche Rated, N-Channel Enhancement-Mode Power MosfetsDocument6 pagesRfg70N06, Rfp70N06, Rf1S70N06, Rf1S70N06Sm: 70A, 60V, Avalanche Rated, N-Channel Enhancement-Mode Power MosfetsRomário CaribéNo ratings yet

- RFD8P05 Datasheet (PDF) - Intersil CorporationDocument6 pagesRFD8P05 Datasheet (PDF) - Intersil Corporationrcuvgd-1No ratings yet

- Fdd8780 Mosfet Malo de Placa PC MariaDocument6 pagesFdd8780 Mosfet Malo de Placa PC MariadojiligNo ratings yet

- Auirf7759l275v 160A 1.8 mOHm MosfetDocument11 pagesAuirf7759l275v 160A 1.8 mOHm MosfetTomas MullerNo ratings yet

- Sơ Đồ DCT (Dry) - Hyundai ElentraDocument5 pagesSơ Đồ DCT (Dry) - Hyundai Elentranguyendu8315No ratings yet

- Irfb3306Pbf Irfs3306Pbf Irfsl3306Pbf: V 60V R Typ. 3.3M: Max. 4.2M I 160A C I 120ADocument12 pagesIrfb3306Pbf Irfs3306Pbf Irfsl3306Pbf: V 60V R Typ. 3.3M: Max. 4.2M I 160A C I 120ADirson Volmir WilligNo ratings yet

- IRFR9310 VishaySiliconixDocument11 pagesIRFR9310 VishaySiliconixDimas AprlioNo ratings yet

- Features General Description: P-Channel Enhancement Mode Power MOSFETDocument7 pagesFeatures General Description: P-Channel Enhancement Mode Power MOSFETaffes electroniqueNo ratings yet

- Electro-Pneumatic I/P, Ep Transducer: Model T7800 SeriesDocument11 pagesElectro-Pneumatic I/P, Ep Transducer: Model T7800 SeriesGilberto Meneses NavarroNo ratings yet

- AUIRF2804 AUIRF2804S AUIRF2804L: Automotive GradeDocument16 pagesAUIRF2804 AUIRF2804S AUIRF2804L: Automotive Gradegotcha75No ratings yet

- Si7848dp PDFDocument5 pagesSi7848dp PDFДрагиша Небитни ТрифуновићNo ratings yet

- Si7848DP: Vishay SiliconixDocument5 pagesSi7848DP: Vishay SiliconixДрагиша Небитни ТрифуновићNo ratings yet

- Irfb4310Zpbf Irfs4310Zpbf Irfsl4310Zpbf: V 100V R Typ. 4.8M: Max. 6.0M: I 127A C I 120ADocument11 pagesIrfb4310Zpbf Irfs4310Zpbf Irfsl4310Zpbf: V 100V R Typ. 4.8M: Max. 6.0M: I 127A C I 120ALuis FigueroaNo ratings yet

- Irfb3307Zpbf Irfs3307Zpbf Irfsl3307ZpbfDocument11 pagesIrfb3307Zpbf Irfs3307Zpbf Irfsl3307Zpbfejdigger ejNo ratings yet

- AUIRFR5305 AUIRFU5305: DSS DS (On) DDocument12 pagesAUIRFR5305 AUIRFU5305: DSS DS (On) DjairNo ratings yet

- Manual DS-416Document16 pagesManual DS-416alan.correa.oliveiraNo ratings yet

- GT Existing Wire Distance ChartDocument3 pagesGT Existing Wire Distance Chartngocanh11595No ratings yet

- Irfb4110Gpbf: V 100V R Typ. 3.7M Max. 4.5M I 180A I 120ADocument8 pagesIrfb4110Gpbf: V 100V R Typ. 3.7M Max. 4.5M I 180A I 120ALuis FigueroaNo ratings yet

- Features General Description: N-Channel Enhancement Mode Power MOSFETDocument6 pagesFeatures General Description: N-Channel Enhancement Mode Power MOSFETJean GaroniNo ratings yet

- Tda 7292Document22 pagesTda 7292pedro santosNo ratings yet

- 156 O Legato Interlock Foot Block 1600 X 800 X 800Document1 page156 O Legato Interlock Foot Block 1600 X 800 X 800BogdanBNo ratings yet

- RFG50N06, RFP50N06, RF1S50N06SM: 50A, 60V, 0.022 Ohm, N-Channel Power Mosfets FeaturesDocument8 pagesRFG50N06, RFP50N06, RF1S50N06SM: 50A, 60V, 0.022 Ohm, N-Channel Power Mosfets FeaturesRoberto DiazNo ratings yet

- IRFR 420-IRFU 420-SiHFR420-SiHFU420 - MosfetDocument11 pagesIRFR 420-IRFU 420-SiHFR420-SiHFU420 - MosfetTiago LeonhardtNo ratings yet

- 110004774-10 170KV 630dia 1T With CK BaseDocument5 pages110004774-10 170KV 630dia 1T With CK Basetragi oyeNo ratings yet

- Si4835BDY: Vishay SiliconixDocument6 pagesSi4835BDY: Vishay SiliconixAku KudupiknikNo ratings yet

- Differential/Cascode Amplifier For Commercial and Industrial Equipment From DC To 120Mhz FeaturesDocument11 pagesDifferential/Cascode Amplifier For Commercial and Industrial Equipment From DC To 120Mhz FeaturesBenny AlconnNo ratings yet

- IRF540, RF1S540SM: 28A, 100V, 0.077 Ohm, N-Channel Power Mosfets FeaturesDocument7 pagesIRF540, RF1S540SM: 28A, 100V, 0.077 Ohm, N-Channel Power Mosfets FeaturesJuan Pablo Echeverria CockNo ratings yet

- Auirfr 5505 TRDocument13 pagesAuirfr 5505 TRneluNo ratings yet

- Cessna Standard Repair ListDocument44 pagesCessna Standard Repair ListKJ Dhiman100% (1)

- 3827-E10-063 - Modulating Control Valve - EDocument6 pages3827-E10-063 - Modulating Control Valve - EMohamed Elsaid El ShallNo ratings yet

- V V R Q Q V: DirectfetDocument9 pagesV V R Q Q V: DirectfetOrangelin SantaellaNo ratings yet

- RFP30N06LEDocument6 pagesRFP30N06LEfathiNo ratings yet

- Description Features: Ait Semiconductor IncDocument8 pagesDescription Features: Ait Semiconductor Incteranet tbtNo ratings yet

- Irfb 4110 PBFDocument8 pagesIrfb 4110 PBFGabriel SaucedoNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) : STI10NM60NDocument12 pagesObsolete Product(s) - Obsolete Product(s) : STI10NM60N2019 Der CHINO GUTIERREZ EDUARDONo ratings yet

- Vishay Siliconix: FeaturesDocument7 pagesVishay Siliconix: Featuresمركز القدسNo ratings yet

- Infineon IRFB3077 DataSheet v01 - 01 ENDocument9 pagesInfineon IRFB3077 DataSheet v01 - 01 ENimran tahirNo ratings yet

- Three-Phase Motors - Specifications - Hitachi Industrial Equipment SystemsDocument1 pageThree-Phase Motors - Specifications - Hitachi Industrial Equipment SystemsArjun SomaiyaNo ratings yet

- Infineon IRFB4110 DataSheet v01 01 En-1732544Document11 pagesInfineon IRFB4110 DataSheet v01 01 En-1732544Seedfp CelularesNo ratings yet

- DatasheetDocument14 pagesDatasheetJNo ratings yet

- Lâmpada Sinalização - RedobstlightDocument2 pagesLâmpada Sinalização - RedobstlightJulivanNo ratings yet

- SUP/SUB75P05-08: Vishay SiliconixDocument5 pagesSUP/SUB75P05-08: Vishay Siliconixh_878236333No ratings yet

- Isolation Monitor Circuit Generation II LeTourneau EquipmentDocument9 pagesIsolation Monitor Circuit Generation II LeTourneau EquipmentjoseNo ratings yet

- Eetop - CN TN45CLDR001 2 6Document600 pagesEetop - CN TN45CLDR001 2 6zx DNo ratings yet

- LG Bb5430a PDFDocument153 pagesLG Bb5430a PDFboroda241067% (12)

- Two Stage AmplifierDocument23 pagesTwo Stage AmplifierDennis Michael De GuzmanNo ratings yet

- BD HS CodeDocument23 pagesBD HS CodeMN Titas TitasNo ratings yet

- CTC 195 - 197 TrainingDocument174 pagesCTC 195 - 197 TrainingAndres Lecaro JarrinNo ratings yet

- 4.6 Final Aeronautics Avionics - 2Document12 pages4.6 Final Aeronautics Avionics - 2Manish Mishra100% (1)

- SCR Power Control (Watlow)Document28 pagesSCR Power Control (Watlow)nealmalm100% (1)

- Generation of High Voltages & CurrentsDocument46 pagesGeneration of High Voltages & Currentssaikarthick023No ratings yet

- LM741CDocument1 pageLM741CMario ArielNo ratings yet

- Samsung LCD Ltm295wx-1Document89 pagesSamsung LCD Ltm295wx-1Jose Evilio Perez ManzaneroNo ratings yet

- Vlsi System DesignDocument12 pagesVlsi System DesignMahender GoudNo ratings yet

- Static Timing Analysis Facts PDFDocument2 pagesStatic Timing Analysis Facts PDFLalit Gohate100% (3)

- Solar RoadwaysDocument28 pagesSolar Roadwaysswetha82% (11)

- Fpga23000 10 WKBF Rev1Document370 pagesFpga23000 10 WKBF Rev1Doravari LakshmiNo ratings yet

- EDC Practical 1Document6 pagesEDC Practical 1nandkishor joshiNo ratings yet

- Piksi Schematics v2.3.1Document7 pagesPiksi Schematics v2.3.1Danut StanciuNo ratings yet

- RMsE LectureDocument148 pagesRMsE Lectureuplbseles100% (10)

- VIVA-questions Semi ConductorDocument22 pagesVIVA-questions Semi Conductorsirisha715No ratings yet

- TVL ST23 04 Ad0Document9 pagesTVL ST23 04 Ad0coulsonpfilNo ratings yet

- GoTo IndraDrive CsDocument274 pagesGoTo IndraDrive CsShiva Raj C SNo ratings yet

- Snx400, Snx4Ls00, and Snx4S00 Quadruple 2-Input Positive-Nand GatesDocument31 pagesSnx400, Snx4Ls00, and Snx4S00 Quadruple 2-Input Positive-Nand GatesVijayakumar SNo ratings yet

- Chapter04 ExDocument6 pagesChapter04 ExKarthikeya VemparalaNo ratings yet

- Implementation of Pid Trained Artificial Neural Network Controller For Different DC Motor DriveDocument14 pagesImplementation of Pid Trained Artificial Neural Network Controller For Different DC Motor DriveGery VerzaztNo ratings yet

- VinodDocument7 pagesVinodMadaka Vinod KumarNo ratings yet

- Power System ProtectionDocument46 pagesPower System ProtectionRatul MollickNo ratings yet

- Grinding TutorialDocument10 pagesGrinding TutorialJared YairNo ratings yet

- Chapter 2 Introduction To Integrated Circuit FabricationDocument19 pagesChapter 2 Introduction To Integrated Circuit Fabrication李承家No ratings yet

- Amazing All-Band ReceiverDocument8 pagesAmazing All-Band ReceiverjhonkayNo ratings yet

- Sanyo - Avm 1901 Service ManualDocument26 pagesSanyo - Avm 1901 Service ManualJerald D'costaNo ratings yet