Professional Documents

Culture Documents

39 - PDFsam - Escholarship UC Item 5qd0r4ws

39 - PDFsam - Escholarship UC Item 5qd0r4ws

Uploaded by

Mohammad0 ratings0% found this document useful (0 votes)

6 views1 pageOriginal Title

39_PDFsam_eScholarship UC Item 5qd0r4ws

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

6 views1 page39 - PDFsam - Escholarship UC Item 5qd0r4ws

39 - PDFsam - Escholarship UC Item 5qd0r4ws

Uploaded by

MohammadCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

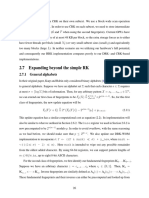

and yn+r−1 by y_new, the updated fingerprint F will be F ← ((F + p - R) 1) +

y_new) % p, where R ← (base * y_old) % p.

For 32-bit registers, if p < 230 , then R and F never overflow (base is itself modulo p).

Originally we should have F-R instead of F+p-R. But since F and R are both positive and less

than p, we add a p value (neutral to modulo operator) to assure the result is positive before

shifting (0 ≤ F + p − R < 2p). The choice of the maximum of 30 bits is required because the

result of both lines must not overflow before the modulo operator. Now, for patterns smaller

than 32 characters we can have F ← ((F & mask) 1) + y_new, where mask ←

∼(1 m). Since we use the binary representation of characters as their fingerprints (exact

hashing with theoretical zero collision), we can mask out the effect of yr by an AND operation

and avoid using an extra subtraction here. mask can be computed once, so on average we have

one bitwise AND, one shift and one summation per character in this case. We refer to this

version as DRK without modulo (DRK-WOM-32bit). With minimal (but non-zero) performance

degradation, we can instead use 64-bit registers and support binary patterns up to 64 characters

(DRK-WOM-64bit).

In DRK (or DRK-WOM), each thread is supposed to process g +m−1 consecutive characters

from the text and verify whether or not there is a match for its g exclusive strings (Section 2.4).

This is not an ideal memory access pattern for high-performance GPU implementation. We would

instead prefer coalesced accesses, where consecutive threads within a warp access consecutive

elements. To alleviate this problem, with NT threads per block, we initially load NT consecutive

subtexts into each block’s shared memory in a coalesced manner (total of gNT + m − 1 characters

per block), and then each thread reads its own subtext locally from much faster shared memory

(where coalescing is less important). In GPUs, memory accesses are in 4B alignments. Therefore

we read elements as char4 vectors (4 consecutive characters) to better exploit the available

memory bandwidth3 .

2.6.3 Hybrid RK

As discussed in Section 2.4, HRK assigns each subtext to a group of processors, where a CRK

method is performed on each subtext. On the GPU, we assign each subtext to a block, and threads

3

char4 is a built-in CUDA vector type with 4B alignment [78, Ch. B.3.].

25

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5813)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- 25 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page25 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 38 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page38 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 45 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page45 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 43 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page43 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 36 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page36 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 34 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page34 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 35 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page35 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 22 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page22 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 24 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page24 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 40 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page40 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 28 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page28 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 9 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page9 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 16 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page16 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 23 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page23 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 8 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page8 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 17 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page17 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 26 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page26 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 12 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page12 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 2 - PDFsam - Beginning Rust - From Novice To Professional (PDFDrive)Document1 page2 - PDFsam - Beginning Rust - From Novice To Professional (PDFDrive)MohammadNo ratings yet

- 13 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page13 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 9.11 Performing Multiple Operations On A List Using FunctorsDocument4 pages9.11 Performing Multiple Operations On A List Using FunctorsMohammadNo ratings yet

- 4 - PDFsam - Escholarship UC Item 5qd0r4wsDocument1 page4 - PDFsam - Escholarship UC Item 5qd0r4wsMohammadNo ratings yet

- 19 - PDFsam - Beginning Rust - From Novice To Professional (PDFDrive)Document1 page19 - PDFsam - Beginning Rust - From Novice To Professional (PDFDrive)MohammadNo ratings yet

- 20 - PDFsam - Beginning Rust - From Novice To Professional (PDFDrive)Document1 page20 - PDFsam - Beginning Rust - From Novice To Professional (PDFDrive)MohammadNo ratings yet

- Deep Learning For Assignment of Protein Secondary Structure Elements From CoordinatesDocument7 pagesDeep Learning For Assignment of Protein Secondary Structure Elements From CoordinatesMohammadNo ratings yet

- 22 - PDFsam - Beginning Rust - From Novice To Professional (PDFDrive)Document1 page22 - PDFsam - Beginning Rust - From Novice To Professional (PDFDrive)MohammadNo ratings yet

- 9.11 Performing Multiple Operations On A List Using FunctorsDocument1 page9.11 Performing Multiple Operations On A List Using FunctorsMohammadNo ratings yet

- 18.4 Being Notified of The Completion of An Asynchronous DelegateDocument3 pages18.4 Being Notified of The Completion of An Asynchronous DelegateMohammadNo ratings yet

- 9.11 Performing Multiple Operations On A List Using FunctorsDocument3 pages9.11 Performing Multiple Operations On A List Using FunctorsMohammadNo ratings yet

- 18.4 Being Notified of The Completion of An Asynchronous DelegateDocument2 pages18.4 Being Notified of The Completion of An Asynchronous DelegateMohammadNo ratings yet