Professional Documents

Culture Documents

1.1.1 Lesson 4 Homework

Uploaded by

Tom O'BrienCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

1.1.1 Lesson 4 Homework

Uploaded by

Tom O'BrienCopyright:

Available Formats

1.

1 System architecture

1.1.1 Architecture of the CPU

Homework

The Fetch–Execute cycle

Time: 15 mins

1 What are the four steps of the fetch phase?

Step 1 Copy PC to MAR

Step 2a Copy data from the RAM addressed by the MAR into the MDR

Step 2b Increment the pc by 1

Step 3 Copy contents of the MDR to the CIR

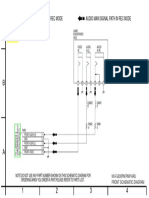

Control

CPU Bus

Arithmetic Logic Control unit RAM

Unit (ALU) (CU) ADDR DATA

00 LDA FF

01 ADD 7

02 SUB 4

ACC CIR MDR

Data

03 STA FE

Bus

FE 2

PC MAR

FF 0

Address

00

Bus

© Hodder & Stoughton Limited 2020 OCR GCSE Computer Science

1.1 System architecture

2 On the attached sheet complete the table to show the steps of the program

shown above. For each instruction you will need to show the steps needed to

complete first the fetch, then the execute phases. The first one has been

completed for you.

The steps for the fetch phase are shown for you and the execute phase for the

first two operations. You need to work out what the steps for the execute phase

will be for the final two instructions.

© Hodder & Stoughton Limited 2020 OCR GCSE Computer Science

1.1 Systems architecture

Program CPU Primary Storage

Instructio

PC ACC CIR MAR MDR 00 01 02 03 --- FE FF

Step

n

00 LDA FE ADD 7 SUB 4 STA FF --- 2 0

Fetch 1 00 00 LDA FF SUB 4 ADD 2 STA FE --- 2 0

Fetch 2a LDA FF ---

LDA FE

Fetch 2b 01 ---

Fetch 3 LDA FF

Operand to

FE

MAR

RAM to MDR 2

MDR to ACC 2 ---

Fetch 1 01 ---

ADD 7

Fetch 2a ADD 7 ---

Fetch 2b 02 ---

Fetch 3 ADD 7

Add operand

to ACC

9 ---

Fetch 1 02 ---

SUB 4

Fetch 2a SUB 4 ---

Fetch 2b 03 ---

Fetch 3 SUB 4

5 ---

Fetch 1 03 ---

Fetch 2a STA FF ---

STA FF

Fetch 2b 04 ---

Fetch 3 STA FF

FF

--- 5

© Hodder & Stoughton Limited 2020 OCR GCSE Computer Science

You might also like

- Computeractive - 27 September 2023Document76 pagesComputeractive - 27 September 20239stm1q96No ratings yet

- LTE L13 Protocols and Procedures: Using Wireshark To View L2Document14 pagesLTE L13 Protocols and Procedures: Using Wireshark To View L2Birckof PearceNo ratings yet

- How to use QXDM terminal software for DT in the fieldDocument5 pagesHow to use QXDM terminal software for DT in the fieldTalent & Tech Global InfotechNo ratings yet

- TS-2000 (B510-01-005) UT-20 InstallationDocument6 pagesTS-2000 (B510-01-005) UT-20 Installationbackup mailNo ratings yet

- Delem: Reference Manual Operation of Version V1Document132 pagesDelem: Reference Manual Operation of Version V1Cash ZebaNo ratings yet

- Weather App Documentation by Vikalp Dubey (66) and Ankit MishraDocument24 pagesWeather App Documentation by Vikalp Dubey (66) and Ankit MishraVikalp Dubey100% (2)

- Samsung AR12Document103 pagesSamsung AR12PauloNo ratings yet

- Annex I - SIL - Verification - ReportDocument8 pagesAnnex I - SIL - Verification - ReportRabah AmidiNo ratings yet

- 1.1.1 Lesson 4 Going DeeperDocument2 pages1.1.1 Lesson 4 Going DeeperTom O'BrienNo ratings yet

- Hisp-3774 - Fes11089-12 - Advanced Centric Systems 1Document12 pagesHisp-3774 - Fes11089-12 - Advanced Centric Systems 1aadil svmelectromechNo ratings yet

- Voltage Regulator Soc Periferials Rf-Soc PartDocument5 pagesVoltage Regulator Soc Periferials Rf-Soc PartMd Kamruzzaman KhanNo ratings yet

- Lecture04 DynamicSchedulingDocument81 pagesLecture04 DynamicSchedulingNikitasNo ratings yet

- Softwired ExampDocument61 pagesSoftwired ExampAKSHAT GARGNo ratings yet

- 04-A6115 Chap4 IO Modified-01Document26 pages04-A6115 Chap4 IO Modified-01sarim baigNo ratings yet

- Ali M3101 DVB-T Demo Board DesignDocument8 pagesAli M3101 DVB-T Demo Board DesignshingoragabashNo ratings yet

- Tap Lenh PLC Delta Day DuDocument487 pagesTap Lenh PLC Delta Day DuĐức An ĐậuNo ratings yet

- Logo Inserter Dvbt3 Jakarta: Out DA Rcti Encoder 1Document1 pageLogo Inserter Dvbt3 Jakarta: Out DA Rcti Encoder 1atara sindiNo ratings yet

- L12 TomasuloDocument28 pagesL12 TomasuloNida CHNo ratings yet

- List Drawing - Uip ViiDocument47 pagesList Drawing - Uip Viizainalabidin3388No ratings yet

- 3BHS832702 E20 RevB TroubleshootingGuide ACS 5k INU LKAI20xxDocument151 pages3BHS832702 E20 RevB TroubleshootingGuide ACS 5k INU LKAI20xxPrafulla SupekarNo ratings yet

- Canadian Solar Projeto Solar Lavras Smartacu2000D Esquemático ElétricoDocument2 pagesCanadian Solar Projeto Solar Lavras Smartacu2000D Esquemático ElétricoCarlos JuniorNo ratings yet

- TV5725 Register Map PDFDocument1 pageTV5725 Register Map PDFFernando PilatoNo ratings yet

- AN8885SBE1V Servo AmpDocument3 pagesAN8885SBE1V Servo AmpEddy Francisco Castellanos PolancoNo ratings yet

- Lecture-11 Dynamic Scheduling ADocument18 pagesLecture-11 Dynamic Scheduling AYumna ShahzadNo ratings yet

- Lawrence 6050A2477601-M0C PVT 20111005Document28 pagesLawrence 6050A2477601-M0C PVT 20111005Ismael BaroneNo ratings yet

- Basic Design PDFDocument26 pagesBasic Design PDFLeTung95No ratings yet

- Lenovo - T - I C340 6050A2497501-AX2-cktDocument49 pagesLenovo - T - I C340 6050A2497501-AX2-cktOman SomantriNo ratings yet

- ConectorDocument4 pagesConectorSamuel SouzaNo ratings yet

- CH 08 FRTDocument1 pageCH 08 FRTRUBEN DARIO SandovalNo ratings yet

- Schematic Diagrams: Compact Component SystemDocument18 pagesSchematic Diagrams: Compact Component SystemEnriqueNo ratings yet

- PCB 3 14 22Document9 pagesPCB 3 14 22kolwin .chindwinNo ratings yet

- M XszzwyDocument8 pagesM XszzwyRADON electronicsNo ratings yet

- Physical OSPF (Sub-Interface) : SW1 SW1Document1 pagePhysical OSPF (Sub-Interface) : SW1 SW1ras aNo ratings yet

- L3Out - 1Document1 pageL3Out - 1Sidhoum SidNo ratings yet

- Dell Latitude E4310 Compal LA-5691P SchematicsDocument51 pagesDell Latitude E4310 Compal LA-5691P SchematicsCarlos ZarateNo ratings yet

- 2021 F150 Audio System - Navigation - SYNC 18 Speaker System 2Document1 page2021 F150 Audio System - Navigation - SYNC 18 Speaker System 2Jason RobertsNo ratings yet

- Aircond System ConnectionDocument7 pagesAircond System Connectionmuhammad farisNo ratings yet

- Eng BizhubProC6500 ICP ListDocument6 pagesEng BizhubProC6500 ICP ListDävïď ËmänüëľNo ratings yet

- KRC 165Document16 pagesKRC 165Kenneth SuzonNo ratings yet

- Genta Permata Putra 2001022018 Tugas Portal Sap 2000 Kelas 2A.Sdb SAP2000 v14.0.0 - License # 15 December 2021Document3 pagesGenta Permata Putra 2001022018 Tugas Portal Sap 2000 Kelas 2A.Sdb SAP2000 v14.0.0 - License # 15 December 2021Genta PermataNo ratings yet

- Block Diagrams: This Document Can Not Be Used Without Samsung's Authorization. Samsung Electronics 8-1Document8 pagesBlock Diagrams: This Document Can Not Be Used Without Samsung's Authorization. Samsung Electronics 8-1Nei Vinicius Hercules Rodrigues MirandaNo ratings yet

- COMPAL CONFIDENTIAL MODEL NAME : NAL60Document51 pagesCOMPAL CONFIDENTIAL MODEL NAME : NAL60Ion PetruscaNo ratings yet

- Assignment 2Document2 pagesAssignment 2Fateh Ali AlimNo ratings yet

- A5-01 Schedule of Finishes-A5-01 PDFDocument1 pageA5-01 Schedule of Finishes-A5-01 PDFDipin Nediya ParambathNo ratings yet

- Um8250 Umc PDFDocument2 pagesUm8250 Umc PDFsaid sakićNo ratings yet

- 21088sch PDFDocument30 pages21088sch PDFpaco37No ratings yet

- Compaq All and One TPV ARROYO PVT Ellsworth 715G4788M0G 6050A2447401 REV M0GDocument27 pagesCompaq All and One TPV ARROYO PVT Ellsworth 715G4788M0G 6050A2447401 REV M0GCarlos Yuvini HernandezNo ratings yet

- Pages From JVC CH-X470 - SMDocument4 pagesPages From JVC CH-X470 - SMpepejoakiNo ratings yet

- JVC KD r430 PDFDocument13 pagesJVC KD r430 PDFAleksNo ratings yet

- ATX-BART BoardDocument8 pagesATX-BART BoardnunocoitoNo ratings yet

- Alfred Sitompil - UtsDocument3 pagesAlfred Sitompil - UtsJunedy Sio SianturiNo ratings yet

- TC-42PX34X: 42 Inch Class 720p Plasma HDTVDocument7 pagesTC-42PX34X: 42 Inch Class 720p Plasma HDTVPedro SandovalNo ratings yet

- 1 - SSDACPart E GGTronicsDocument16 pages1 - SSDACPart E GGTronicsaditya_vyas_13No ratings yet

- Dell Inspiron 15 5567 5767 Compall LA-D801P R1.0-OutputDocument61 pagesDell Inspiron 15 5567 5767 Compall LA-D801P R1.0-OutputriyasNo ratings yet

- Activity 2 - 2022 HpcaDocument3 pagesActivity 2 - 2022 HpcavenuNo ratings yet

- High Performance Power Combi Controller TDA 16888: PFC SectionDocument39 pagesHigh Performance Power Combi Controller TDA 16888: PFC SectionaaaaaNo ratings yet

- Document Submittal NumberingDocument1 pageDocument Submittal NumberingJose Ricky FalcasantosNo ratings yet

- Column A-C 1-8Document1 pageColumn A-C 1-8Rahmatur RidhaNo ratings yet

- Section 3B Advisory/Status Procedures: SubjectDocument6 pagesSection 3B Advisory/Status Procedures: SubjectDhinesh BalasubrmaniNo ratings yet

- Arroyo DVT Schematics PCB Version and Component ListingDocument27 pagesArroyo DVT Schematics PCB Version and Component ListingElves Mattos100% (1)

- JARINGAN LAN FORTUNA FARMINDODocument6 pagesJARINGAN LAN FORTUNA FARMINDOFortuna Lancar AdimakmurNo ratings yet

- FT-2200 Serv F6DBL 1993Document125 pagesFT-2200 Serv F6DBL 1993Marcos DanilaviciusNo ratings yet

- TP BTN LS 6743Document2 pagesTP BTN LS 6743Ricardo MeloNo ratings yet

- CloudComputing600A AssignmentDocument21 pagesCloudComputing600A AssignmentThuto DintweNo ratings yet

- WT UNIT 1 Lecture 1.6 The Internet and Its ServicesDocument7 pagesWT UNIT 1 Lecture 1.6 The Internet and Its ServicesSACHIDANAND CHATURVEDINo ratings yet

- 14-Apr-2022 Engr. Majid Kaleem 1Document20 pages14-Apr-2022 Engr. Majid Kaleem 1Mobile MentorNo ratings yet

- Aryldo Russo - Safety Certification Considering Processes Around The World1Document29 pagesAryldo Russo - Safety Certification Considering Processes Around The World1Ron HemNo ratings yet

- السيرة الذاتيةDocument1 pageالسيرة الذاتيةYounesNo ratings yet

- Hypergraph Convolutional Neural Network-Based Clustering TechniqueDocument9 pagesHypergraph Convolutional Neural Network-Based Clustering TechniqueIAES IJAINo ratings yet

- Urn Uvci 01 Ro W10dmyl82pkjp0o7ppoz6or37gev9x#2Document2 pagesUrn Uvci 01 Ro W10dmyl82pkjp0o7ppoz6or37gev9x#2Codrin CodrinNo ratings yet

- OFFICE MANAGEMENT-noteDocument53 pagesOFFICE MANAGEMENT-notereem mazeeNo ratings yet

- Printlink5-ID - IV DICOM 3.0 Conformance StatementDocument20 pagesPrintlink5-ID - IV DICOM 3.0 Conformance StatementjamesNo ratings yet

- STL Cheat Sheet by AlphabetDocument2 pagesSTL Cheat Sheet by Alphabet-DaNn1EeLL -No ratings yet

- Fas 22Document15 pagesFas 22sam tariqNo ratings yet

- Automatic Cutting Machine: Powercut 3700Document118 pagesAutomatic Cutting Machine: Powercut 3700Dionisio M. RiveraNo ratings yet

- Context-Free Grammar: CSE 211 (Theory of Computation)Document18 pagesContext-Free Grammar: CSE 211 (Theory of Computation)Ovi Poddar AntorNo ratings yet

- Isr 4400 SWCFGDocument332 pagesIsr 4400 SWCFGHuy Truong GiaNo ratings yet

- ChatcryptoDocument16 pagesChatcryptoKashif JameelNo ratings yet

- Lecture3 Chapter4 - Design 4-Bit Ripple Carry Binary Adder-Subtractor CircuitDocument32 pagesLecture3 Chapter4 - Design 4-Bit Ripple Carry Binary Adder-Subtractor CircuitAyesha HussainNo ratings yet

- Fs2311001 Autopulse AP 4001 Product Overview Us DigitalDocument2 pagesFs2311001 Autopulse AP 4001 Product Overview Us DigitalengrjameschanNo ratings yet

- Research Article: A Comparative Analysis of The Top Ott Platforms in India Liya RajeshDocument18 pagesResearch Article: A Comparative Analysis of The Top Ott Platforms in India Liya RajeshPrathamesh DivekarNo ratings yet

- Service Manual: Home Audio SystemDocument38 pagesService Manual: Home Audio SystemSergio Hernandez GNo ratings yet

- Circus Charlie - 1984 - Parker BrothersDocument4 pagesCircus Charlie - 1984 - Parker BrothersJuan CarlosNo ratings yet

- BD243/A/B/C: NPN Epitaxial Silicon TransistorDocument10 pagesBD243/A/B/C: NPN Epitaxial Silicon TransistorTimothy MartinNo ratings yet

- How To Use SAP Activate Content in SAP Solution Manager 7.2: DraftDocument17 pagesHow To Use SAP Activate Content in SAP Solution Manager 7.2: Draftخليل الكرامةNo ratings yet

- RFID Based Library Management SystemDocument85 pagesRFID Based Library Management SystemRamesh kNo ratings yet

- Data Resource Management: Reporter: Cabantoc, Mariannne & Caranzo, Mel RoseDocument24 pagesData Resource Management: Reporter: Cabantoc, Mariannne & Caranzo, Mel RoseArt Robin NagpacanNo ratings yet

- Lab 05 - Boolean Function ImplementationDocument10 pagesLab 05 - Boolean Function ImplementationNashowan Gamal AlhadrmiNo ratings yet