Professional Documents

Culture Documents

Problem 12

Problem 12

Uploaded by

Abdi JoteOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Problem 12

Problem 12

Uploaded by

Abdi JoteCopyright:

Available Formats

Digital Electronics

Tutorial Sheet 12

1.* Show that a binary down-counter can be implemented using a binary up-

counter. To do this, draw the transition table for a 4-bit up-counter and for a 4-

bit down counter and then consider the relationship between corresponding

bits in the two tables.

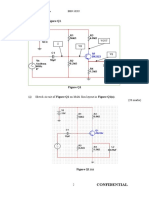

2.** A 3-bit synchronous counter with a synchronous CLEAR input is connected as

shown below in Figure 1. Draw a state diagram for the circuit. Draw also the

modified state diagram if the CLEAR input were asynchronous? Finally, draw

the modified logic symbol.

3.** The circuit below in Figure 2 uses a 4-bit synchronous binary counter with a

synchronous LOAD input. The signal TC is high whenever the contents of the

counter equal 15. The frequency of CLOCK is 16 kHz.

a) If N3:0 = 5, draw a state diagram for the counter.

b) If N3:0 = 5, what is the frequency of the signal OUT?

c) Derive a general formula giving the frequency of OUT in terms of the value N.

d) What is the frequency of the signal OUT if N=15?

CLOCK OUT

CTR3 C1

Q0

{

CLOCK 0

Q1 1D

C1+ CT CTR4

Q2 1

2 M2 CT=15

1 1CT=0

C1/2+

N0 Q0

1,2D

N1 Q1

N2 Q2

N3 Q3 (MSB)

Figure 1 Figure 2

You might also like

- Eco Intern Exercise SuddenStopDocument2 pagesEco Intern Exercise SuddenStopBetoNo ratings yet

- Mnemonic Function Program Steps Controllers: X0 C20 CNT K100Document3 pagesMnemonic Function Program Steps Controllers: X0 C20 CNT K100Christenes AlvesNo ratings yet

- Noncompartmental Analysis: Deficiencies of Compartmental AnalysisDocument49 pagesNoncompartmental Analysis: Deficiencies of Compartmental AnalysisSamehabdulla AbdullaNo ratings yet

- Chapter 04c Frequency Filtering (Circulant Matrices) 2Document48 pagesChapter 04c Frequency Filtering (Circulant Matrices) 2Manu PrasadNo ratings yet

- CounterDocument9 pagesCounterrmangaiNo ratings yet

- Chapter 09Document52 pagesChapter 09gudxor85741031No ratings yet

- Mics Telys Kohler Dec4000Document101 pagesMics Telys Kohler Dec4000ohe985No ratings yet

- Mics Telys Kohler Dec4000Document101 pagesMics Telys Kohler Dec4000ohe985No ratings yet

- Telys 2 - Master t100 - Revfev09Document101 pagesTelys 2 - Master t100 - Revfev09RickNo ratings yet

- Part1 Asynchronous CountersDocument9 pagesPart1 Asynchronous CountersLilya OuarabNo ratings yet

- Study and Evaluation of Performances of The Digital MultimeterDocument10 pagesStudy and Evaluation of Performances of The Digital Multimetermihaela0chiorescuNo ratings yet

- MultivibratorsDocument9 pagesMultivibratorsPadanam MaathramNo ratings yet

- Lab Report 5 - The Triangular Waveform Generator and The Astable MultivibratorDocument5 pagesLab Report 5 - The Triangular Waveform Generator and The Astable MultivibratorYasmim de SouzaNo ratings yet

- MPTA 6 (Sol)Document12 pagesMPTA 6 (Sol)pauldebtanu5No ratings yet

- Frequency Filtering (Circulant Matrices)Document48 pagesFrequency Filtering (Circulant Matrices)anaNo ratings yet

- Counters and Decoders: PurposeDocument7 pagesCounters and Decoders: Purposepraritlamba25No ratings yet

- What's Next : - Combinational Circuit ExamplesDocument17 pagesWhat's Next : - Combinational Circuit ExamplesvipulugaleNo ratings yet

- 6 CountersDocument52 pages6 CountersBiniam TeferiNo ratings yet

- Physics DPP SolutionDocument10 pagesPhysics DPP SolutionAyush GuptaNo ratings yet

- CS212 Counters Timers and DMMDocument57 pagesCS212 Counters Timers and DMMMtoi TvNo ratings yet

- Tutorial of Non-Isolated DC-DC Converter in Continuous Mode (Benny Yeung)Document3 pagesTutorial of Non-Isolated DC-DC Converter in Continuous Mode (Benny Yeung)Farhan Malik100% (1)

- Mariano Marcos State University: College of EngineeringDocument8 pagesMariano Marcos State University: College of EngineeringLyka Jane Tapia OpeñaNo ratings yet

- DSP ch08 S2.3 2.7P PDFDocument57 pagesDSP ch08 S2.3 2.7P PDFBelaliaNo ratings yet

- Vector Excersice PDFDocument5 pagesVector Excersice PDFSiti Haja'sNo ratings yet

- DF ch09 S2.3 2.7PDocument57 pagesDF ch09 S2.3 2.7PVamshidhar ReddyNo ratings yet

- Counter 163Document7 pagesCounter 163Carla BarbosaNo ratings yet

- Heat LossDocument4 pagesHeat LossCham SurendNo ratings yet

- Power Electronics Tutorial DC-DC Converter - CCm-1Document3 pagesPower Electronics Tutorial DC-DC Converter - CCm-1Hasnain JamilNo ratings yet

- Updated Question1Document2 pagesUpdated Question1azqa khalidNo ratings yet

- Dec4000 - Master T100 070207Document80 pagesDec4000 - Master T100 070207kyaw myo lwinNo ratings yet

- Digital Logic Design: CountersDocument44 pagesDigital Logic Design: CountersZelalem MeskiNo ratings yet

- Microsoft Word - MA3004 - Tutorial 5 (FEM) Solutions - AY2022-23Document15 pagesMicrosoft Word - MA3004 - Tutorial 5 (FEM) Solutions - AY2022-23Luna OpalNo ratings yet

- CEG 2136 - Fall 2014 - Midterm PDFDocument7 pagesCEG 2136 - Fall 2014 - Midterm PDFAmin DhouibNo ratings yet

- CEG 2136 - Fall 2016 - MidtermDocument9 pagesCEG 2136 - Fall 2016 - MidtermAmin DhouibNo ratings yet

- Setup and Hold Time CalculationsDocument33 pagesSetup and Hold Time CalculationsRashmi Periwal100% (11)

- Formulario Exa Final Cam FFCCDocument1 pageFormulario Exa Final Cam FFCCIsaaNo ratings yet

- Tutorial of Non-Isolated DC/DC Converters in Continuous ModeDocument15 pagesTutorial of Non-Isolated DC/DC Converters in Continuous ModeSudip MondalNo ratings yet

- CounterDocument33 pagesCounterAMIT KUMAR SINGHNo ratings yet

- Cs EmpireDocument4 pagesCs Empireayoubalam52No ratings yet

- P Q y T X T P y Q X y T: Visit Us At: WWW - Nodia.co - inDocument1 pageP Q y T X T P y Q X y T: Visit Us At: WWW - Nodia.co - inSameerChauhanNo ratings yet

- Chapter2 2Document39 pagesChapter2 2hailegebreselassie24No ratings yet

- Bezier Curves and SurfacesDocument10 pagesBezier Curves and SurfacesAniruddho RayNo ratings yet

- Counters 1Document11 pagesCounters 1Jenifer StalinNo ratings yet

- 2.D.3d. Exercise2.2Document1 page2.D.3d. Exercise2.2Prayash MangerNo ratings yet

- Seq 4 ExercicesDocument4 pagesSeq 4 ExercicesKįlwâ ZöüldîkNo ratings yet

- MPSI Quiz2 SolutionDocument2 pagesMPSI Quiz2 SolutionIman HayatNo ratings yet

- Lab Test 1 BBN 10205Document4 pagesLab Test 1 BBN 10205Zhamir ZhakwanNo ratings yet

- COMM 2 NotesDocument9 pagesCOMM 2 NotesGeorges ChouchaniNo ratings yet

- CountersDocument19 pagesCounterslakraniNo ratings yet

- 35 - PDFsam - 03 - 1261 - Technical Description 3460aroMA AA83346-07Document1 page35 - PDFsam - 03 - 1261 - Technical Description 3460aroMA AA83346-07Anonymous glDF4cfqgNo ratings yet

- EXP No 9Document5 pagesEXP No 9P B SavithaNo ratings yet

- We Have Following Equilibrium PointsDocument6 pagesWe Have Following Equilibrium PointsvishalkingsingNo ratings yet

- Binomial Theorem - DPP 03 (Of Lec 04) - (Prayas 2.0 2023 PW Star)Document3 pagesBinomial Theorem - DPP 03 (Of Lec 04) - (Prayas 2.0 2023 PW Star)Deep SarkarNo ratings yet

- Civil Engineering Department de La Salle University-ManilaDocument3 pagesCivil Engineering Department de La Salle University-ManilaHillary CanlasNo ratings yet

- Digital Logic CounterDocument12 pagesDigital Logic CounterRaziya SultanaNo ratings yet

- Formula Sheet: KT Q N NDocument2 pagesFormula Sheet: KT Q N NMarinaNo ratings yet

- Clinical Audity-22Document44 pagesClinical Audity-22Abdi JoteNo ratings yet

- Big Fast Results - by Dr. Daniel GebremichaelDocument31 pagesBig Fast Results - by Dr. Daniel GebremichaelAbdi JoteNo ratings yet

- Problem 7Document2 pagesProblem 7Abdi JoteNo ratings yet

- Problem 1Document1 pageProblem 1Abdi JoteNo ratings yet

- Chapter 1Document32 pagesChapter 1Abdi JoteNo ratings yet

- Problem 2Document1 pageProblem 2Abdi JoteNo ratings yet

- Chapter 3 Two Port Netw All in OneDocument53 pagesChapter 3 Two Port Netw All in OneAbdi Jote100% (1)

- Chapter 2 For TeachingDocument55 pagesChapter 2 For TeachingAbdi JoteNo ratings yet