Professional Documents

Culture Documents

MIL-STD-1553 3.3V Dual Transceivers With Integrated Encoder / Decoders

Uploaded by

conan-kidachiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MIL-STD-1553 3.3V Dual Transceivers With Integrated Encoder / Decoders

Uploaded by

conan-kidachiCopyright:

Available Formats

HI-1575

MIL-STD-1553 3.3V Dual Transceivers

August 2020

with Integrated Encoder / Decoders

DESCRIPTION PIN CONFIGURATIONS

38 CHA/CHB

39 ERROR

The HI-1575 is a low power CMOS dual transceiver with

37 CLK

on-chip Manchester II Encoder and dual Decoder

36 D0

35 D1

34 D2

33 D3

32 D4

40 -

31 -

designed to meet the requirements of the MIL-STD-1553

specification. The part acts as a "Smart Transceiver", - 1 30 -

allowing users to transmit and receive properly encoded RCVA 2 29 D5

BUSA 3 28 D6

MIL-STD-1553 Command and Data words between a BUSA 4 27 D7

16-bit host processor and dual MIL-STD-1553 data VDD 5 1575PCI 26 GND

BUSB 6 25 D8

buses. BUSB 7 1575PCT 24 D9

RCVB 8 23 D10

REG 9 22 D11

A single write cycle is used to transfer a word to the - 10 21 -

HI-1575, which encodes the data, adds the selected Sync

11

12

13

14

15

16

17

18

19

20

and Parity bits, and transmits the word on the chosen

STRB

MR

SYNC

D15

D14

D13

D12

-

R/W

-

MIL-STD-1553 data bus. Complete MIL-STD-1553

messages may be transmitted by executing multiple write

cycles to the device.

Activity on both MIL-STD-1553 data buses is continuously 40 Pin Plastic 6mm x 6mm

monitored. When the HI-1575 detects a properly encoded Chip-scale package

word, a hardware interrupt is generated and the

information is decoded and stored in one of two internal

registers, which may then be read by the host processor.

Bits in the internal Status & Mode Register indicate on

which bus the word was received and whether the word 31 - CHA/CHB

32 - ERROR

had a Data or Command Sync. 30 - CLK

29 - D0

28 - D1

27 - D2

26 - D3

25 - D4

FEATURES

RCVA - 1 24 - D5

! Compliant to MIL-STD-1553A & B BUSA - 2

BUSA - 3

23 - D6

22 - D7

HI-1575PQI

! 3.3V single supply operation VDD - 4

BUSB - 5

&

HI-1575PQT

21 - GND

20 - D8

BUSB - 6 19 - D9

! On-chip Encoder and Dual Decoder RCVB - 7

REG - 8

18 - D10

17 - D11

! Small footprint available in 32-pin plastic

STRB - 10

SYNC - 12

D15 - 13

D14 - 14

D13 - 15

D12 - 16

MR - 11

R/W - 9

TQFP package

! Less than 0.5W maximum power dissipation

! 6 mm x 6 mm 40-pin plastic chip-scale 32 Pin TQFP package

package option

HOLT INTEGRATED CIRCUITS

(DS1575 Rev. F) www.holtic.com 08/20

HI-1575

PIN DESCRIPTIONS

PULL-UP

PIN SYMBOL FUNCTION PULL-DOWN DESCRIPTION

(TQFP)

1 RCVA Digital output - Goes high when MIL-STD-1553 word received on Bus A

2 BUSA Analog I/O - MIL-STD-1533 bus driver A, negative signal

3 BUSA Analog I/O - MIL-STD-1553 bus driver A, positive signal

4 VDD Power supply - +3.3 VDC

5, BUSB Analog I/O - MIL-STD-1533 bus driver B, negative signal

6 BUSB Analog I/O - MIL-STD-1553 bus driver B, positive signal

7 RCVB Digital output - Goes high when MIL-STD-1553 word received on Bus B

8 REG Digital input 12K pull-down Selects Status & Mode Register when high, or Data registers when low

9 R/W Digital input 12K pull-up Controls data and sync direction during read or write operations

10 STRB Digital input 12K pull-up Strobe. Timing input to control register read and write operations

11 MR Digital input 12K pull-down Pulse high to reset the HI-1575

12 SYNC Digital I/O 12K pull-down Selects transmit sync type on write, indicates received sync type on read.

13-20, 22-29 D15:D0 Digital I/O 12K pull-down Data bus. D15 (MSB) corresponds to MIL-STD-1553 bit 4

21 GND Power supply - Ground

30 CLK Digital input - 12 MHz clock

31 CHA/CHB Digital Input 12K pull-down Selects MIL-STD-1553 Bus A or Bus B

32 ERROR Digital output - Goes high when a received MIL-STD-1553 word has an encoding error

FUNCTIONAL DESCRIPTION

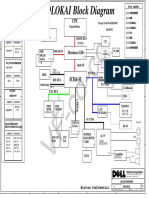

Figure 1 shows a simplified block diagram of the HI-1575. Similarly, the SYNC I/O pin may be left open-circuit al-

lowing the transmitter sync to be programmed into SAM

The MR (Master Reset) input should be pulsed high to bit 4, or SAM bit 4 can be set to zero and the SYNC pin

initialize the Manchester II Encoder and Decoders. MR used to set the transmitted SYNC type. Note that SYNC

also clears the Receive Data registers, RXA and RXB, is an I/O pin. It is an input when writing data to the

and sets the Status & Mode register to its default state HI-1575 transmit data register (TX), and an output when

as described in figure 2. reading data from the HI-1575 receivers (RXA and RXB).

The SYNC pin must not be shorted directly to VDD or

The CLK input requires a 12.0 MHz clock signal. CLK is GND. An internal pull-down resistor allow the SYNC pin

used to derive the 1.0 us bit period for MIL-STD-1553 to be left open-circuit if the user opts for purely software

data transmission, as well to provide the master clock for control.

the Manchester II encoder and the decoder's receiver

sampling logic. TRANSMITTER

STATUS & MODE REGISTER Data words to be transmitted on the MIL-STD-1553 data

bus are written to the TX register by pulsing STRB low

The HI-1575 is configured by writing bits 0 - 5 of the Sta- while R/W is low and REG is low. The logical OR of the

tus & Mode (SAM) register. Refer to figure 2 for a com- CHA/CHB input pin and SAM bit 5 (CHAN) during the

plete description. SAM bits 0 - 5 are read/write allowing write cycle determines whether the word is output on

the user to verify the chip's configuration at any time by MIL-STD-1553 bus A or B. Setting CHA/CHB OR CHAN

reading the SAM. SAM is accessed by performing a read to a zero selects bus A, and a one selects bus B. The log-

or write cycle with the REG input high. ical OR of the SYNC pin and SAM bit 4 (TXSYNC) dur-

ing the write cycle defines whether the transmitted word

SAM bits 6 - 15 are read-only and are used to provide is a MIL-STD-1553 Command or Data word. Setting

status information. SYNC to a one causes a Command (or Status) sync to

be generated. Setting SYNC to zero selects a Data sync.

To minimize the number of hardware control inputs, SAM Note that the SYNC pin is bidirectional. It should be

bit 5 (Channel A/B select) is logically 'OR'ed with the treated as an extension to the 16-bit bidirectional

CHA/CHB input pin. To select between MIL-STD-1553 databus (D15:D0) in terms of I/O switching and timing.

bus A or B, the user may either tie the CHA/CHB pin low

and select buses using SAM bit 5 (software control), or The HI-1575 automatically calculates and appends the cor-

program SAM bit 5 to a zero and use the CHA/CHB pin rect parity bit to the transmitted word. Each word is as-

to select the active bus (hardware control). signed odd parity as required by MIL-STD-1553.

HOLT INTEGRATED CIRCUITS

2

HI-1575

4 VDD

30

CLK

10

STRB

9

R/W 2

8 BUSA

REG Encoder 3

11 BUSA

MR

SHIFT

TX

5

31 BUSB

CHA/CHB 6

BUSB

13-20, SHIFT

RXA

22-29

DATABUS

12

SYNC Decoder A

1

RCVA

SHIFT

RXB

Decoder B

7

RCVB

STATUS & MODE

10

32

ERROR

21 GND Note: Pin numbers reflect QFP package

FIGURE 1. HI-1575 BLOCK DIAGRAM

To transmit contiguous words, a second write to the TX RECEIVER

register must occur no earlier than 3.5 µs and no later

than 18.5 µs after the first TX write. SAM bit 15 The HI-1575's two receivers continuously monitor both

(SENDDATA) is high during this period and may be used MIL-STD-1553 data busses. Bi-phase differential data

as a flag to indicate when the HI-1575 is ready to accept words are accepted from the MIL-STD-1553 bus through

the next data write for contiguous transmission. When the same direct or transformer coupled interface as the

transmitting a message of three or more words, the third transmitter. Each receiver’s differential input stage drives

and subsequent write operations should occur every 20.0 a filter and threshold comparator that presents data to the

us so as to avoid over-writing the previous data before it is decoders.

transferred to the transmitter's shift register.

The decoder logic checks the incoming word for correct

Figure 3 shows a timing diagram for transmit operations. encoding, bit count and parity. If a valid MIL-STD-1553

word is received, the RCVA or RCVB output goes high

The transmitter outputs are either direct or transformer and the 16-bit received word is transferred to the RXA or

coupled to the MIL-STD-1553 data bus. Both coupling RXB register. The HI-1575 ERROR output goes high

methods produce a nominal voltage on the main whenever an encoding error is detected on either bus. If

MIL-STD-1553 bus of 7.5 volts peak-to-peak, line-to-line. a received word has an encoding error, then SAM bits 10

Figure 6 shows bus coupling examples. or 14 (ERRORA, ERRORB) are set high, and the

corresponding RCVA or RCVB pin is not asserted.

One or both transmitters may be disabled by writing a '1'

into SAM register bits 0 or 1 (TXDISA, TXDISB). When dis- To minimize the number of pins necessary to interface the

abled, the host interface works as normal, but there is no HI-1575, the state of RCVA and RCVB can also be read

output from the BUSA and BUSA (BUSB and BUSB) pins. from SAM bits 7 and 11.

HOLT INTEGRATED CIRCUITS

3

HI-1575

G OR A

R AT

AP B

AP A

C B

C A

EN C

H d

G OR

TX ISB

A

ER DD

R NC

R NC

C se

R YN

IS

AN

R B

ER B

R B

TX A

R A

N A

u

V

R

EN

N

SY

SY

D

D

S

ot

SE

TX

STATUS & MODE REGISTER (SAM) 0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

MSB LSB

Bit Name R/W Default Description

0 TXDISA R/W 0 Writing TXDISA to a '1' disables the transmitter for MIL-STD-1553 bus A

1 TXDISB R/W 0 Writing TXDISB to a '1' disables the transmitter for MIL-STD-1553 bus B

2 RENA R/W 1 Setting RENA to a '1' enables the receiver for MIL-STD-1553 bus A. A '0' disables the

receiver causing the HI-1575 to ignore all activity on bus A.

3 RENB R/W 1 Setting RENB to a '1' enables the receiver for MIL-STD-1553 bus B. A '0' disables the

receiver causing the HI-1575 to ignore all activity on bus B.

4 TXSYNC R/W 0 The TXSYNC bit is logically ORed with the SYNC input pin during host write cycles to the

Transmit Data Register (TX). If TXSYNC OR SYNC is a '1' the transmitter prefixes the

transmitted word with a MIL-STD-1553 Command Sync. If TXSYNC OR SYNC is a '0'

during a write to TX, then the transmitted word has a MIL-STD-1553 Data Sync.

5 CHAN R/W 0 The CHAN bit is logically ORed with the CHA/CHB input pin and the result used to Select

between MIL-STD-1553 bus A or B during write transfers to the TX register, or reading data

from the RX registers. When CHAN OR CHA/CHB is a '0' during a transmit operation,

data is transmitted on MIL-STD-1553 bus A. When the result is a '1', MIL-STD-1553

bus B is selected. During HI-1575 data read cycles, if CHAN OR CHA/CHB is a '0', the RXA

register is accessed, and if CHAN OR CHA/CHB is a '1' then the data is read from RXB.

6 - Read-only 0 Not used. Internally set to '0'.

7 RCVA Read-only 0 This bit reflects the state of the RCVA output pin. RCVA goes high whenever a new word is

received on MIL-STD-1553 bus A. The received word may be read by the host from the RXA

register. RCVA is reset on reading RXA or if the HI-1575 detects a new word arriving on bus A.

If the data words are contiguous, then RCVA will be high for about 3 us before the new word

resets it. The data is still available in the RXA register and may be retreived any time up until

the RCVA flag goes high again. If the user does not read the data, the word is lost when

the RCVA flag goes high on reception of the next word.

8 RSYNCA Read-only 0 RSYNCA indicates the Sync of the last MIL-STD-1553 word received on bus A. RSYNCA is a

'0' for a Data sync, and a '1' for a Command Sync. When the RXA register is read, the

RSYNCA value is also output on the SYNC I/O pin.

9 GAPA Read-only 0 GAPA is a '1' when there is no activity detected on MIL-STD-1553 bus A, for example during an

inter-message gap. GAPA is a '0' whenever the HI-1575 detects bus traffic.

10 ERRORA Read-only 0 ERRORA goes high when the HI-1575 Manchester decoder receives an incorrectly encoded

word on MIL-STD-1553 bus A

11 RCVB Read-only 0 Same function as RCVA but for MIL-STD-1553 bus B.

12 RSYNCB Read-only 0 Same function as RSYNCA but for MIL-STD-1553 bus B.

13 GAPB Read-only 0 Same function as GAPA but for MIL-STD-1553 bus B.

14 ERRORB Read-only 0 Same function as ERRORA but for MIL-STD-1553 bus B.

15 SENDDATA Read-only 1 SENDDATA goes high approximately 3.5 us after the start of a MIL-STD-1553 word

transmission. SENDATA goes low approximately 18.5 us after the start of a MIL-STD-1553

word transmission. If new a new data word is written to the TX register while SENDDATA is

high, that word will be transmitted contiguously after the currently transmitting word.

FIGURE 2. STATUS AND MODE REGISTER

HOLT INTEGRATED CIRCUITS

4

HI-1575

Write TX, Write TX,

(MIL-STD-1553 Status word) (MIL-STD-1553 Data word)

Read SAM,

check SENDDATA=1

D15 - D0 TXDATA DON’T CARE SAM TXDATA

R/W DON’T CARE

CHA/CHB VALID DON’T CARE VALID

SYNC DON’T CARE

REG DON’T CARE

STRB

BUSA (B) SYNC SYNC 15 14 13 3 3 2 1 0 P SYNC SYNC 15

FIGURE 3. EXAMPLE TRANSMIT OPERATION

Read RXA or RXB,

(MIL-STD-1553 Data word)

Read SAM

BUSA (B) SYNC SYNC 15 14 13 12 2 1 0 P SYNC SYNC 15 14 13 12

RCVA (B)

R/W DON’T CARE

CHA/CHB DON’T CARE VALID

REG DON’T CARE

STRB

D15 - D0 SAM RXA (B)

SYNC SYNC

FIGURE 4. EXAMPLE RECEIVE OPERATION

CHAN OR CHA/CHB REG Register

0 0 Receiver A Data (RXA)

1 0 Receiver B Data (RXB)

X 1 Status & Mode Register (SAM)

FIGURE 5. HI-1575 REGISTER MAP

HOLT INTEGRATED CIRCUITS

5

HI-1575

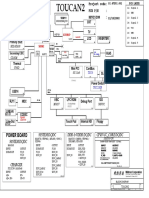

The host reads the received word from the HI-1575 RXA or MIL-STD-1553 BUS CONNECTION

RXB register. The data word is read by pulsing STRB low,

while R/W is high and REG is low. Figure 4 shows an The HI-1575 includes on-chip MIL-STD-1553 analog

example receive operation. The SYNC output indicates transceivers which are designed to drive the primary

whether the word had a Command Sync (SYNC=1) or winding of a 1:2.5 turns-ratio MIL-STD-1553 isolation

Data Sync (SYNC=0). SAM register bits 8 and 12 transformer. Figure 6 shows how the HI-1575 may be

(RSYNCA and RSYNCB) retain the Sync values for the connected to the MIL-STD-1553 data bus as either a

last word received on each bus. direct coupled stub (Bus A example), or a transformer

coupled stub (Bus B example). Holt Integrated Circuits

SAM bits 2 or 3 (RENA, RENB) can be used to offers a wide range of single-core and dual-core coupling

independently enable or disable each receiver. Writing a transformers suitable for use with the HI-1575.

'1' to RENA enables receiver A. A '0' disables the receiver.

RENB performs the same function for the MIL-STD-1553

bus B.

Note that because each receiver is internally connected to

its transmitter, when a MIL-STD-1553 word is transmitted

by the HI-1575 it will also be received on the same

channel. This feature allows the terminal to self-monitor

data transmitted to the MIL-STD-1553 data bus.

3.3 V

VDD

12.0 MHz CLK

55 Ohms

BUSA

STRB MIL-STD-1553

BUS A

R/W (Direct Coupled)

55 Ohms

CHA/CHB BUSA

REG 1:2.5

Host CPU

D15:D0

SYNC

HI-1575

RCVA

RCVB 52.5 Ohms

BUSB MIL-STD-1553

ERROR BUS B

MR (Transformer Coupled)

52.5 Ohms

BUSB

1:2.5 1:1.4

GND

FIGURE 6. MIL-STD-1553 BUS CONNECTION

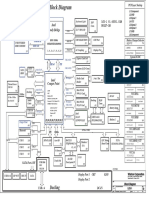

Bit Period 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

SYNC TERMINAL ADDRESS R/T SUBADDRESS DATA WORD P

Command Word SYNC

/ MODE COUNT

SYNC DATA WORD P

Data Word SYNC

SYNC TERMINAL ADDRESS ME CODE FOR FAILURE MODES TF P

Status Word SYNC

FIGURE 7. MIL-STD-1553 WORD FORMATS

HOLT INTEGRATED CIRCUITS

6

HI-1575

TIMING DIAGRAMS

BIT PERIOD BIT PERIOD BIT PERIOD

t R1

BUSA - BUSA

(BUSB - BUSB) t R1

COMMAND SYNC

t R1

BUSA - BUSA

(BUSB - BUSB) t R1

DATA SYNC

t R3 t R2

BUSA - BUSA

(BUSB - BUSB) t R2 t R3 t R2

ONE ZERO ONE

FIGURE 8. MIL-STD-1553 BUS RECEIVER TIMING

MID-SYNC MID-SYNC MID-PARITY MID-SYNC MID-PARITY

MID-PARITY

1553 COMMAND DATA WORD WITH ERROR

BUS

tFH tFH tFH

RCVA(B)

tFR tFR

ERROR

tFR

tRF tRF tRF

STRB

(Read RXA) (Read RXA) (Read SAM)

FIGURE 9. HI-1575 RECEIVER TIMING

REG VALID REG VALID

tRWS tRWH tRRH

tRRS

tSTR tSTR

STRB STRB

tDWS

tDRV

tDWH tDRT

D15:0

SYNC VALID D15:0 VALID

SYNC

tCHWS tCHRS

tCHWH tCHRH

CHA/CHB CHA/CHB

tRWWS tRWRS

tRWWH tRWRH

R/W R/W

Figure 10. DATABUS TIMING - WRITE. Figure 11. DATABUS TIMING - READ

HOLT INTEGRATED CIRCUITS

7

HI-1575

ABSOLUTE MAXIMUM RATINGS RECOMMENDED OPERATING CONDITIONS

Supply voltage (VDD) -0.3 V to +5 V Supply Voltage

Logic input voltage range -0.3 V DC to +3.6 V VDD....................................... 3.3V... ±5%

Receiver differential voltage 50 Vp-p Temperature Range

Driver peak output current +1.0 A Industrial Screening.........-40°C to +85°C

Solder Temperature (reflow) 260°C Hi-Temp Screening........-55°C to +125°C

Junction Temperature 175°C

NOTE: Stresses above absolute maximum

Storage Temperature -65°C to +150°C ratings or outside recommended operating

conditions may cause permanent damage to the

device. These are stress ratings only. Operation

at the limits is not recommended.

DC ELECTRICAL CHARACTERISTICS

VDD = 3.3 V, GND = 0V, TA = Operating Temperature Range (unless otherwise specified).

PARAMETER SYMBOL CONDITION MIN TYP MAX UNITS

Operating Voltage VDD 3.15 3.30 3.45 V

Total Supply Current ICC1 Not Transmitting 4 10 mA

ICC2 Transmit one channel @ 225 250 mA

50% duty cycle

ICC3 Transmit one channel @ 425 500 mA

100% duty cycle

Power Dissipation PD1 Not Transmitting 0.06 W

PD2 Transmit one channel @ 0.3 0.5 W

100% duty cycle

Min. Input Voltage (HI) VIH Digital inputs 70% VDD

Max. Input Voltage (LO) VIL Digital inputs 30% VDD

Min. Input Current (HI) IIH Digital inputs (without pull-down) 20 µA

Max. Input Current (LO) IIL Digital inputs (without pull-up) -20 µA

Pull-up / Pull-down current IPUD Digital inputs and data bus 275 µA

Min. Output Voltage (HI) VOH IOUT = -1.0mA, Digital outputs 90% VDD

Max. Output Voltage (LO) VOL IOUT = 1.0mA, Digital outputs 10% VDD

RECEIVER (Measured at Point “AD“ in Figure 12 unless otherwise specified)

Input resistance RIN Differential 2 Kohm

Input capacitance CIN Differential 5 pF

Common mode rejection ratio CMRR 40 dB

Input common mode voltage VICM -10.0 +10.0 V-pk

Threshold Voltage - Direct-coupled Detect VTHD 1 Mhz Sine Wave 1.15 Vp-p

No Detect VTHND (Measured at Point “AD“ in Figure 12) 0.28 Vp-p

Theshold Voltage - Transformer-coupled Detect VTHD 1 MHz Sine Wave 0.86 Vp-p

No Detect VTHND (Measured at Point “AT“ in Figure 13) 0.20 Vp-p

TRANSMITTER(Measured at Point “AD” in Figure 12 unless otherwise specified)

Output Voltage 35 ohm load

Direct coupled VOUT 6.0 9.0 Vp-p

(Measured at Point “AD“ in Figure 12)

70 ohm load

Transformer coupled VOUT 18.0 27.0 Vp-p

(Measured at Point “AT“ in Figure 13)

Output Noise VON Differential, inhibited 10.0 mVp-p

Output Dynamic Offset Voltage 35 ohm load

Direct coupled VDYN -90 90 mV

(Measured at Point “AD“ in Figure 12)

70 ohm load

Transformer coupled VDYN -250 250 mV

(Measured at Point “AT“ in Figure 13)

HOLT INTEGRATED CIRCUITS

8

HI-1575

AC ELECTRICAL CHARACTERISTICS

VDD = 3.3 V, GND = 0V, TA =Operating Temperature Range (unless otherwise specified)

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

TRANSMITTER (Measured at Point “AD” in Figure 12)

RiseTtime tr 35 ohm load 100 300 ns

Fall Time tf 35 ohm load 100 300 ns

RECEIVER (See figures 8 and 9)

Sync Transition Span tR1 1500 ns

Short Data Transition Span tR2 500 ns

Long Data Transition Span tR3 1000 ns

Delay Mid-Parity to Flag Set tFH 2500 ns

Flag Setup Time to Read tFR 0 ns

Flag Reset Delay tRF 60 ns

DATA BUS TIMING - WRITE (See figure 10)

Strobe STRB Pulse Width tSTR 50 ns

REG Write Setup Time tRWS 50 ns

REG Write Hold Time tRWH 10 ns

Databus / SYNC Write Setup Time tDWS 50 ns

Databus / SYNC Write Hold Time tDWH 10 ns

CHA/CHB Write Setup Time tCHWS 50 ns

CHA/CHB Write Hold Time tCHWH 10 ns

R/W Write Setup Time tRWWS 50 ns

R/W Write Hold Time tRWWH 10 ns

DATA BUS TIMING - READ (See figure 11)

Strobe STRB Pulse Width tSTR 50 ns

REG Read Setup Time tRRS 50 ns

REG Read Hold Time tRRH 10 ns

Data Read to Databus Valid tDRV 60 ns

Data Read to Databus Tri-state tDRT 0 60 ns

CHA/CHB Read Setup Time tCHRS 50 ns

CHA/CHB Read Hold Time tCHRH 10 ns

R/W Read Setup Time tRWRS 50 ns

R/W Read Hold Time tRWRH 10 ns

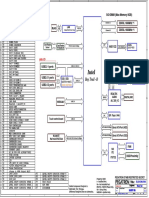

VDD

Isolation

Transformer 55W

BUS A (B)

Host CPU 35W

55W

BUS A (B)

1:2.5

HI-1575 Point

“AD”

GND

FIGURE 12. DIRECT COUPLED TEST CIRCUIT

HOLT INTEGRATED CIRCUITS

9

HI-1575

VDD

Isolation

Transformer

BUS A (B)

Host CPU 70W

BUS A (B)

1:2.5

HI-1575 Point

“AT”

GND

FIGURE 13. TRANSFORMER COUPLED TEST CIRCUIT

HEAT SINKING THE LEADLESS PLASTIC APPLICATIONS NOTE

CHIP CARRIER PACKAGE Holt Applications Note AN-500 provides circuit design

The HI-1575PCI/T is packaged in a 40 pin leadless plastic notes regarding the use of Holt MIL-STD-1553 data

chip carrier (QFN). This package has a metal heat sink communications devices. Layout considerations, as well

pad on its bottom surface, which should be soldered to as recommended interface and protection components

the printed circuit board for optimum thermal dissipation. are included.

The package heat sink is electrically isolated and may be

soldered to any convenient power plane or ground plane.

Redundant "vias" between the exposed board surface

and buried power or ground plane will enhance thermal

conductivity.

RECOMMENDED TRANSFORMERS

The HI-1575 transceiver have been characterized for Holt recommends Premier Magnetics parts as offering

compliance with the electrical requirements of MIL-STD- the best combination of electrical performance, low cost

1553 when used with the following transformers. and small footprint.

MANUFACTURER PART NUMBER APPLICATION TURNS RATIO DIMENSIONS

Premier Magnetics PM-DB2791S Isolation Single 1:2.5 .400 x .400 x .185 inches

Premier Magnetics PM-DB2762 Isolation Dual 1:2.5 .400 x .400 x .320 inches

Premier Magnetics PM-DB2756 Isolation Dual 1:2.5 .930 x .575 x .185 inches

Premier Magnetics PM-DB2702 Stub coupling 1:1.4 .625 x .625 x .250 inches

HOLT INTEGRATED CIRCUITS

10

HI-1575

ORDERING INFORMATION

HI - 1575 PQ x x

PART LEAD

NUMBER FINISH

Blank Tin / Lead (Sn / Pb) Solder

F 100% Matte Tin (Pb-free, RoHS compliant)

PART TEMPERATURE FLOW BURN

NUMBER RANGE IN

I -40°C TO +85°C I NO

T -55°C TO +125°C T NO

M -55°C TO +125°C M YES

PART PACKAGE

NUMBER DESCRIPTION

PQ 32 PIN PLASTIC PQFP (32PQS)

HI - 1575 PC x x

PART LEAD

NUMBER FINISH

Blank NiPdAu

F NiPdAu (Pb-free, RoHS compliant)

PART TEMPERATURE FLOW BURN

NUMBER RANGE IN

I -40°C TO +85°C I NO

T -55°C TO +125°C T NO

PART PACKAGE

NUMBER DESCRIPTION

PC 40 PIN CHIP SCALE PACKAGE (40PCS)

HOLT INTEGRATED CIRCUITS

11

HI-1575

REVISION HISTORY

P/N Rev Date Description of Change

DS1575 D 04/20/11 Added REG input to block diagram. Corrected D.C. Electrical Characteristics Table

and package thickness dimension for the 32PTQS.

E 02/13/17 Update Direct and Transformer Coupled test circuits. Remove Thermal

Characteristics Table. Add Recommended Transformers Table. Update Solder

Temperature (reflow). Update 32PQS package drawing.

F 08/31/2020 Correct typo in DC Electrical Characteristics Table; VOL incorrectly labeled as VIH.

Remove Power Dissipation from Absolute Maximum Ratings Table. Update QFN

package lead finish to NiPdAu.

HOLT INTEGRATED CIRCUITS

12

PACKAGE DIMENSIONS

32 PIN PLASTIC QUAD FLAT PACK (PQFP) millimeters (inches)

Package Type: 32PQS

0.145 ± 0.055

(0.006 ± 0.002)

0.80

BSC

(0.031)

9.00 7.00

BSC sq. BSC sq.

(0.354) (0.276) 0.375 ± 0.075

(0.015 ± 0.003)

0.60 ± 0.150

(0.024 ± 0.006)

1.00 ± 0.05

(0.039 ± 0.002) 0.20 R

(0.008) max

See Detail A

1.20 0° £ Q £ 7°

max

(0.047)

0.08

0.004 ± 0.002 R

(0.003) min

(0.10 ± 0.05)

BSC = “Basic Spacing between Centers” Detail A

is theoretical true position dimension and

has no tolerance. (JEDEC Standard 95)

40-PIN PLASTIC CHIP-SCALE PACKAGE

millimeters

Electrically isolated heat sink

pad on bottom of package.

Package Type: 40PCS

Connect to any ground or

power plane for optimum

6.00 BSC thermal dissipation. 4.15 ± .15

0.50 BSC

6.00 BSC Top View 4.15 ± .15 Bottom

View

0.25 typ

0.55 ± .10

See Detail A

1.00 max

0.2 typ

0.90 ± .10

BSC = “Basic Spacing between Centers” 0.02 typ

is theoretical true position dimension and

has no tolerance. (JEDEC Standard 95) Detail A

HOLT INTEGRATED CIRCUITS

13

You might also like

- Esquema Eletrico ECS G41T-R3Document29 pagesEsquema Eletrico ECS G41T-R3bentogil75% (4)

- Final MCPA NE Guide and Sample QuesionDocument21 pagesFinal MCPA NE Guide and Sample Quesionna_s75% (4)

- MIL-STD-1553 / 1760 3.3V Dual Transceiver With Integrated IP Security ModuleDocument13 pagesMIL-STD-1553 / 1760 3.3V Dual Transceiver With Integrated IP Security ModuleShashank MuthaNo ratings yet

- ths5661 PDFDocument29 pagesths5661 PDFIqbal AchmadiNo ratings yet

- HI-1573, HI-1574: MIL-STD-1553 3.3V Monolithic Dual TransceiversDocument11 pagesHI-1573, HI-1574: MIL-STD-1553 3.3V Monolithic Dual TransceiverscetibegizNo ratings yet

- MOLOKAI Block Diagram: VF-co-ccDocument39 pagesMOLOKAI Block Diagram: VF-co-ccWILLPC369No ratings yet

- HI-1579, HI-1581: MIL-STD-1553 / 1760 3.3V Monolithic Dual TransceiversDocument11 pagesHI-1579, HI-1581: MIL-STD-1553 / 1760 3.3V Monolithic Dual TransceiversPradeep KumarNo ratings yet

- Acer Aspire 1600 (Wistron Toucan2) PDFDocument47 pagesAcer Aspire 1600 (Wistron Toucan2) PDFMustafa AkanNo ratings yet

- MIL-STD-1553 / MIL-STD-1760 3.3V Single Transceiver: Description Pin Configurations Pin ConfigurationsDocument11 pagesMIL-STD-1553 / MIL-STD-1760 3.3V Single Transceiver: Description Pin Configurations Pin ConfigurationsPradeep KumarNo ratings yet

- 10-Bit, 40Msps, 3.0V, Low-Power ADC With Internal Reference: General Description FeaturesDocument20 pages10-Bit, 40Msps, 3.0V, Low-Power ADC With Internal Reference: General Description FeaturesRobNo ratings yet

- 5 Volt Only Driver/Receiver: RS232 EIA-232-E and CCITT V.28Document9 pages5 Volt Only Driver/Receiver: RS232 EIA-232-E and CCITT V.28Mauro Miranda CoutoNo ratings yet

- Mitsubishi : 8-Bit 8-Ch Multiplying D-A Converter With Buffer AmplifiersDocument6 pagesMitsubishi : 8-Bit 8-Ch Multiplying D-A Converter With Buffer AmplifiersquinquinoNo ratings yet

- CS8411 CS8412: Digital Audio Interface ReceiverDocument36 pagesCS8411 CS8412: Digital Audio Interface Receivertinears02No ratings yet

- Pos Ecig41bs (Diagramas - Com.br)Document29 pagesPos Ecig41bs (Diagramas - Com.br)José FrançaNo ratings yet

- Wistron Je70-Cp (91.4HN01.001, 48.4HN01.0SD, 09923-1M, 2010-02-02)Document67 pagesWistron Je70-Cp (91.4HN01.001, 48.4HN01.0SD, 09923-1M, 2010-02-02)ruslancikdurbalaNo ratings yet

- Banan Pi BPI-R1 MP Schematic-SD - V3-20140922Document14 pagesBanan Pi BPI-R1 MP Schematic-SD - V3-20140922Tuan AnhNo ratings yet

- TravelMate 370Document42 pagesTravelMate 370Syukri AlhamdiNo ratings yet

- x230 Schematics PDFDocument101 pagesx230 Schematics PDFEmmanuel MoreauNo ratings yet

- App Arm JtagDocument34 pagesApp Arm JtagbalzoniaNo ratings yet

- Important Notes About This Schematic: PCB StackDocument29 pagesImportant Notes About This Schematic: PCB Stackanh_sao_dem_92No ratings yet

- G41T M7 PDFDocument30 pagesG41T M7 PDFAlex Melo50% (2)

- 4.4 HOST Auto-Filming Connection I/F Cable Connection DiagramDocument3 pages4.4 HOST Auto-Filming Connection I/F Cable Connection DiagramGhulam MurtazaNo ratings yet

- Lenovo Thinkpad X230 Wistron DASHER-2 LBD-2 112321-1 SchematicDocument101 pagesLenovo Thinkpad X230 Wistron DASHER-2 LBD-2 112321-1 SchematicLuis Alberto ArizaNo ratings yet

- Usb To TTLDocument1 pageUsb To TTLKARTIK FALDUNo ratings yet

- D D D D D D D D D D D D D D D D: SN75ALS170, SN75ALS170A Triple Differential Bus TransceiverDocument22 pagesD D D D D D D D D D D D D D D D: SN75ALS170, SN75ALS170A Triple Differential Bus TransceiverDedii KurniawanNo ratings yet

- QM - Artix7 - Xc7A35T DB: User ManualDocument19 pagesQM - Artix7 - Xc7A35T DB: User ManualNgoc AnhNo ratings yet

- IT66121FNDocument39 pagesIT66121FNCarlos ChuekeNo ratings yet

- Arctic Tern Module Schematic v1.01Document27 pagesArctic Tern Module Schematic v1.01Foo BarNo ratings yet

- CS8412Document38 pagesCS8412ricardosdiotiNo ratings yet

- Si3012 FS ModemDocument54 pagesSi3012 FS ModemAnonymous xDBXbk89PNo ratings yet

- ch340g Part 3Document3 pagesch340g Part 3David MoodyNo ratings yet

- Skema Thinkpad X230Document101 pagesSkema Thinkpad X230Tukang ITNo ratings yet

- Comet 1 PDFDocument101 pagesComet 1 PDFRaju KhajjidoniNo ratings yet

- 170 3 092971 MB40528Document14 pages170 3 092971 MB40528Umum Cupang CupangNo ratings yet

- Mainboard 845eiclientDocument35 pagesMainboard 845eiclientHo Thanh Binh100% (1)

- IBM Thinkpad R31 SchematicsDocument37 pagesIBM Thinkpad R31 Schematicsحسن علي نوفلNo ratings yet

- Real Rs232 For Laptop PCS: Small CircuitscollectionDocument1 pageReal Rs232 For Laptop PCS: Small CircuitscollectionTariq ZuhlufNo ratings yet

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocument7 pagesHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataDimon SergeevichNo ratings yet

- HI-15530 / HI-1567 Example Circuit Applications Note: August 2009Document2 pagesHI-15530 / HI-1567 Example Circuit Applications Note: August 2009wdrrr wdrrrNo ratings yet

- Lenovo B460 - V460 Wistron LA46 UMA 09922-1 Rev1 SchematicDocument48 pagesLenovo B460 - V460 Wistron LA46 UMA 09922-1 Rev1 Schematicnasir khan100% (1)

- Ecs g41t-m Rev. 7.1Document30 pagesEcs g41t-m Rev. 7.1Zidan YasrahNo ratings yet

- 96 KHZ Digital Audio Receiver: Cs8413 Cs8414Document38 pages96 KHZ Digital Audio Receiver: Cs8413 Cs8414moocomNo ratings yet

- Z61Ae Schematic V2.0: System Page Ref. Power Page RefDocument57 pagesZ61Ae Schematic V2.0: System Page Ref. Power Page RefAnubys 365No ratings yet

- Pegatron Iaxbt-Bl Rev Rev. 1.01 Acer Aspire Zc-606Document67 pagesPegatron Iaxbt-Bl Rev Rev. 1.01 Acer Aspire Zc-606Ban NeoNo ratings yet

- HI-2579, HI-2581: 3.3V MIL-STD-1553/1760 Dual Transceiver With Low Profile Integrated TransformersDocument14 pagesHI-2579, HI-2581: 3.3V MIL-STD-1553/1760 Dual Transceiver With Low Profile Integrated TransformersPradeep KumarNo ratings yet

- Modem Ótico ShadowDocument3 pagesModem Ótico ShadowKennedy TavaresNo ratings yet

- PD16732A, 16732B: Mos Integrated CircuitDocument24 pagesPD16732A, 16732B: Mos Integrated CircuitAnika HernandezNo ratings yet

- I2C Serial InterfaceDocument11 pagesI2C Serial InterfaceBobyNo ratings yet

- REN Cdp1802ac-3 DST 20020117Document27 pagesREN Cdp1802ac-3 DST 20020117darkstar314No ratings yet

- TLC 7225Document21 pagesTLC 7225tajpan77No ratings yet

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocument8 pagesHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataGonzaloGaldamesNo ratings yet

- GFK0682EDocument2 pagesGFK0682EsabasthianNo ratings yet

- Block Diagram 1381743Document1 pageBlock Diagram 1381743Andrzej GomulaNo ratings yet

- 711e9psDocument1 page711e9psElvis LinaresNo ratings yet

- Ecs - VS - G41t-M2.rev.1.0Document30 pagesEcs - VS - G41t-M2.rev.1.0Gilberto GomesNo ratings yet

- Msi - 87956 - MS-7328Document40 pagesMsi - 87956 - MS-7328Débo OrellanoNo ratings yet

- LoooDocument56 pagesLoooLim Aaron KusmadiNo ratings yet

- Email KorespondensiDocument4 pagesEmail KorespondensiJamil MisbahNo ratings yet

- 04-WCDMA RNP LinkBudget - 20051214Document63 pages04-WCDMA RNP LinkBudget - 20051214NguyenPhuocNo ratings yet

- 04A - Working With Datastores - Jupyter Notebook PDFDocument11 pages04A - Working With Datastores - Jupyter Notebook PDFjhNo ratings yet

- Animatronics: Submitted By: Istuti Gupta 0723931021 E.c.-Iv YearDocument17 pagesAnimatronics: Submitted By: Istuti Gupta 0723931021 E.c.-Iv YearIstuti GuptaNo ratings yet

- Computer Grade 8 Solved 100 MCQs For Preparation of Competitive ExamDocument20 pagesComputer Grade 8 Solved 100 MCQs For Preparation of Competitive ExamAli hamzaNo ratings yet

- BBA 1ST SEM Bachelor of Business Administration - Tourism and TravelDocument11 pagesBBA 1ST SEM Bachelor of Business Administration - Tourism and TravelAakash SinghNo ratings yet

- Surigao State College of TechnologyDocument106 pagesSurigao State College of Technologyraymond baliteNo ratings yet

- REST UdemyDocument47 pagesREST UdemyAHOUALAKOUNNo ratings yet

- January 30, 2024 Mechanical Engineering Team Daily Report.Document4 pagesJanuary 30, 2024 Mechanical Engineering Team Daily Report.kenasa jirataNo ratings yet

- Anne Mette Jonassen Hass Guide To Software Testing - Ejemplo PDFDocument7 pagesAnne Mette Jonassen Hass Guide To Software Testing - Ejemplo PDFurielNo ratings yet

- MODUL 3 - Creating An Interconnected IP NetworkDocument28 pagesMODUL 3 - Creating An Interconnected IP NetworkThe MasterNo ratings yet

- SafetyToolkit 5whysDocument4 pagesSafetyToolkit 5whysFaisal AbdoNo ratings yet

- D1-160 - LEWA Dosing Pump TechnicalDocument38 pagesD1-160 - LEWA Dosing Pump Technicalraji357No ratings yet

- CATALOGO BOMBA INYECCION STA ItaliaDocument54 pagesCATALOGO BOMBA INYECCION STA ItaliaKata CardonaNo ratings yet

- Bicotest T625 TDRDocument3 pagesBicotest T625 TDRBen's IvanNo ratings yet

- Resume (Suraj)Document4 pagesResume (Suraj)Suraj s ShetsanadiNo ratings yet

- MNL23-0082 Econ Global Builders Corp. (Final)Document8 pagesMNL23-0082 Econ Global Builders Corp. (Final)Rhen CarlonNo ratings yet

- 4D-F9 GPS Version User S ManualDocument16 pages4D-F9 GPS Version User S Manualangelica.mirosaNo ratings yet

- Letter of Complaint (Zadania-Seminarky - SK)Document2 pagesLetter of Complaint (Zadania-Seminarky - SK)patrikbenko2000No ratings yet

- Nvidia DGX h100 DatasheetDocument2 pagesNvidia DGX h100 DatasheetNum NumtrexNo ratings yet

- Drager Savina 2.0 Maintenance PDFDocument25 pagesDrager Savina 2.0 Maintenance PDFAhmerShehzadNo ratings yet

- The Console Wars: An Online HindsightDocument4 pagesThe Console Wars: An Online HindsightNico AtaizaNo ratings yet

- Hfe Yamaha RX E410 E810 ServiceDocument57 pagesHfe Yamaha RX E410 E810 Serviceanthony leonardNo ratings yet

- Mysore District ProfileDocument16 pagesMysore District ProfilenarayankoppalNo ratings yet

- Maintenance Journal 174Document95 pagesMaintenance Journal 174Jorge MartinezNo ratings yet

- LC320DXN SFR2 LGDocument35 pagesLC320DXN SFR2 LGAbcd EfghNo ratings yet

- Information System Midterm Flashcards - QuizletDocument9 pagesInformation System Midterm Flashcards - Quizletbusiness docNo ratings yet

- Categorising MaterialsDocument31 pagesCategorising MaterialsHassan OuchenNo ratings yet