Professional Documents

Culture Documents

RYCHIP Semiconductor Inc RY9120 - C2930864

Uploaded by

vs674584Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

RYCHIP Semiconductor Inc RY9120 - C2930864

Uploaded by

vs674584Copyright:

Available Formats

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

Features

• Wide 4.5V to 17V Operating Input Range • 110mΩ/70mΩ Low RDS(ON) Internal Power

• 2A Continuous Output Current MOSFETs

• 500KHz Switching Frequency • Output Adjustable from 0.6V

• ECOT Mode Control with Fast Transient • No Schottky Diode Required

Response • Short Protection with Hiccup-Mode

• Built-in Over Current Limit • Integrated internal compensation

• Built-in Over Voltage Protection • Thermal Shutdown

• PFM Mode for High Efficiency in Light Load • Available in SOT23-6 Package

• Internal Soft-Start • -40°C to +85°C Temperature Range

Applications

• Digital Set-top Box (STB) • Digital Video Recorder (DVR)

• Tablet Personal Computer (Pad) • Portable Media Player (PMP)

• Flat-Panel Television and Monitor • Cable Modem / XDSL

• Wi-Fi Router / AP • General Purposes

General Description

The RY9120 is a high frequency, synchronous, rectified, step-down, switch-mode converter with internal power

MOSFETs. It offers a very compact solution to provide a 2A continuous output current over a wide input supply

range, with excellent load and line regulation. ECOT control operation provides very fast transient response and

easy loop design as well as very tight output regulation.

The RY9120 requires a minimal number of readily available, external components and is available in a space saving

SOT23-6 package.

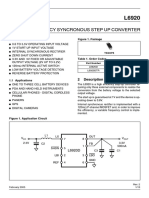

Typical Application Circuit

C1

VIN BS L1 VOUT

IN SW

R1 CFF COUT

ON/

CIN EN FB

OFF

GND

R2

Basic Application Circuit

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 1 / 13

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

Pin Description

Pin Configuration

TOP VIEW

BS 1 6 SW

GND 2 5 IN

FB 3 4 EN

SOT23-6

Top Marking: CCYLL (device code: CC, Y=year code, LL= lot number code)

Pin Description

Pin Name Function

Bootstrap. A capacitor connected between SW and BST pins is required to form a

1 BS

floating supply across the high-side switch driver.

2 GND GROUND Pin

Adjustable Version Feedback input. Connect FB to the center point of the external

3 FB

resistor divider

Drive this pin to a logic-high to enable the IC. Drive to a logic-low to disable the

4 EN

IC and enter micro-power shutdown mode.

5 IN Power Supply Pin

6 SW Switching Pin

Order Information (1)

Marking Part No. Model Description Package T/R Qty

RY9120 ECOT Buck, 4.5-17V, 2A,

CCYLL 70301120 RY9120 SOT23-6 3000PCS

500KHz, VFB 0.6V, SOT23-6

Note (1): All RYCHIP parts are Pb-Free and adhere to the RoHS directive.

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 2 / 13

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

Specifications

Absolute Maximum Ratings (1) (2)

Item Min Max Unit

VIN voltage -0.3 18 V

EN voltage -0.3 18 V

SW voltage -3 19 V

SW voltage (<10 ns transient) -5 19 V

BS voltage (to SW) -0.3 6.5 V

FB voltage -0.3 6 V

(3)

Power dissipation Internally Limited

Operating junction temperature, TJ -40 150 °C

Storage temperature, Tstg -55 150 °C

Lead Temperature (Soldering, 10sec.) 260 °C

Note (1): Exceeding these ratings may damage the device.

Note (2): The device is not guaranteed to function outside of its operating conditions.

Note (3): The maximum allowable power dissipation is a function of the maximum junction temperature, T J(MAX),

the junction-to-ambient thermal resistance, RθJA, and the ambient temperature, TA. The maximum allowable power

dissipation at any ambient temperature is calculated using: PD (MAX) = (TJ(MAX) − TA)/RθJA. Exceeding the maximum

allowable power dissipation causes excessive die temperature, and the regulator goes into thermal shutdown.

Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at

TJ=160°C (typical) and disengages at TJ= 130°C (typical).

ESD Ratings

Item Description Value Unit

Human Body Model (HBM)

V(ESD-HBM) ANSI/ESDA/JEDEC JS-001-2014 ±2000 V

Classification, Class: 2

Charged Device Mode (CDM)

V(ESD-CDM) ANSI/ESDA/JEDEC JS-002-2014 ±200 V

Classification, Class: C0b

JEDEC STANDARD NO.78E APRIL 2016

ILATCH-UP Temperature Classification, ±150 mA

Class: I

Recommended Operating Conditions

Item Min Max Unit

(1)

Operating junction temperature –40 125 °C

Operating temperature range -40 85 °C

Input voltage VIN 4.5 17 V

Output current 0 2 A

Note (1): All limits specified at room temperature (TA = 25°C) unless otherwise specified. All room temperature

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 3 / 13

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

limits are 100% production tested. All limits at temperature extremes are ensured through correlation using standard

Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

Thermal Information

Item Description Value Unit

(1)(2)

RθJA Junction-to-ambient thermal resistance 105 °C/W

RθJC(top) Junction-to-case (top) thermal resistance 55 °C/W

RθJB Junction-to-board thermal resistance 17.5 °C/W

ψJT Junction-to-top characterization parameter 3.5 °C/W

ψJB Junction-to-board characterization parameter 17.5 °C/W

Note (1): The package thermal impedance is calculated in accordance to JESD 51-7.

Note (2): Thermal Resistances were simulated on a 4-layer, JEDEC board.

Electrical Characteristics (1) (2)

VIN=12V, TA=25°C, unless otherwise specified.

Parameter Test Conditions Min Typ. Max Unit

Input Voltage Range 4.5 17 V

Supply Current (Quiescent) VEN =3.0V 0.6 0.8 mA

Supply Current (Shutdown) VEN =0 or EN = GND 4 uA

Feedback Voltage 0.585 0.6 0.615 V

High-Side Switch On-Resistance ISW=100mA 110 mΩ

Low-Side Switch On-Resistance ISW=-100mA 70 mΩ

Valley Switch Current Limit 2 A

Over Voltage Protection Threshold 18 V

Switching Frequency 500 KHz

Maximum Duty Cycle VFB=90% 94 %

Minimum Off-Time 89 nS

EN Rising Threshold 1.4 V

EN Falling Threshold 0.8 V

Wake up VIN Voltage 4.3 4.5 V

Under-Voltage Lockout Threshold Shutdown VIN Voltage 3.6 3.8 V

Hysteresis VIN voltage 500 mV

Soft Start 1.5 mS

Thermal Shutdown 160 ℃

Thermal Hysteresis 30 ℃

Note (1): MOSFET on-resistance specifications are guaranteed by correlation to wafer level measurements.

Note (2): Thermal shutdown specifications are guaranteed by correlation to the design and characteristics analysis.

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 4 / 13

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

Typical Performance Characteristics (1) (2)

Note (1): Performance waveforms are tested on the evaluation board.

Note (2): VIN =12V, VOUT=3.3V, TA = +25ºC, unless otherwise noted.

Efficiency vs Load Current Load Regulation Line Regulation

VOUT=5V, 3.3V, 1.2V VOUT=5V, 3.3V, 1.2V VOUT=3.3V

Output Ripple Voltage Output Ripple Voltage Output Ripple Voltage

VIN=12V, VOUT=3.3V, IOUT=0A VIN=12V, VOUT=3.3V, IOUT=1A VIN=12V, VOUT=3.3V, IOUT=2A

Loop Response Output Short Short Circuit Entry

VIN=12V, VOUT=3.3V, IOUT=1A-2A VIN=12V, VOUT=3.3V VIN=12V, VOUT=3.3V

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 5 / 13

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

Short Circuit Recovery Enable Startup at No Load Enable Shutdown at No Load

VIN=12V, VOUT=3.3V VIN=12V, VOUT=3.3V, IOUT=0A VIN=12V, VOUT=3.3V, IOUT=0A

Enable Startup at Full Load Enable Shutdown at Full Load Power Up at No Load

VIN=12V, VOUT=3.3V, IOUT=2A VIN=12V, VOUT=3.3V, IOUT=2A VIN=12V, VOUT=3.3V, IOUT=0A

Power Up at Full Load PFM Mode at No Load Switching Point

VIN=12V, VOUT=3.3V, IOUT=2A VIN=12V, VOUT=3.3V, IOUT=0A VIN=12V, VOUT=3.3V, IOUT=1.08A

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 6 / 13

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

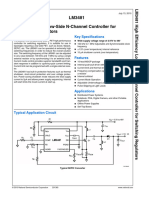

Functional Block Diagram

IN

Internal VCC

EN Regulator BS

UVLO On-Time

Bias&Voltage

Reference

HICCUP

Control Driver SW

VSHORT

Reference

FB

PWM OC

Reference OCL

Ripple Gen

Reference

SW

GND

Block Diagram

Functions Description

Internal Regulator

The RY9120 is an ECOT mode step down DC/DC converter that provides excellent transient response with no extra

external compensation components. This device contains an internal, low resistance, high voltage power MOSFET,

and operates at a high 500KHz operating frequency to ensure a compact, high efficiency design with excellent AC

and DC performance.

Error Amplifier

The error amplifier compares the FB pin voltage with the internal FB reference (V FB) and outputs a current

proportional to the difference between the two. This output current is then used to charge or discharge the internal

compensation network, which is used to control the power MOSFET current. The optimized internal compensation

network minimizes the external component counts and simplifies the control loop design.

Under-Voltage Lockout (UVLO)

Under-voltage lockout (UVLO) protects the chip from operating at an insufficient supply voltage. UVLO protection

monitors the internal regulator voltage. When the voltage is lower than UVLO threshold voltage, the device is shut

off. When the voltage is higher than UVLO threshold voltage, the device is enabled again.

Thermal Shutdown

Thermal shutdown prevents the chip from operating at exceedingly high temperatures. When the silicon die

temperature exceeds 160°C, it shuts down the whole chip. When the temperature falls below its lower threshold

(Typ. 130°C) the chip is enabled again.

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 7 / 13

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

Internal Soft-Start

The soft-start is implemented to prevent the converter output voltage from overshooting during startup. When the

chip starts, the internal circuitry generates a soft-start voltage (SS) ramping up from 0V to 0.6V. When it is lower

than the internal reference (REF), SS overrides REF so the error amplifier uses SS as the reference. When SS is

higher than REF, REF regains control. The SS time is internally max to 1.5ms.

Over Current Protection and Hiccup

The RY9120 has cycle-by-cycle over current limit when the inductor current valley value exceeds the set current

limit threshold. Meanwhile, output voltage starts to drop until FB is below the Under-Voltage (UV) threshold. Once

a UV is triggered, the RY9120 enters hiccup mode to periodically restart the part. This protection mode is especially

useful when the output is dead-short to ground. The average short circuit current is greatly reduced to alleviate the

thermal issue and to protect the regulator. The RY9120 exits the hiccup mode once the over current condition is

removed.

Startup and Shutdown

If both VIN and EN are higher than their appropriate thresholds, the chip starts. The reference block starts first,

generating stable reference voltage and currents, and then the internal regulator is enabled. The regulator provides

stable supply for the remaining circuitries. Three events can shut down the chip: EN low, V IN low and thermal

shutdown. In the shutdown procedure, the signaling path is first blocked to avoid any fault triggering. The comp

voltage and the internal supply rail are then pulled down. The floating driver is not subject to this shutdown

command.

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 8 / 13

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

Applications Information

Setting the Output Voltage

RY9120 require an input capacitor, an output capacitor and an inductor. These components are critical to the

performance of the device. RY9120 are internally compensated and do not require external components to achieve

stable operation. The output voltage can be programmed by resistor divider.

𝑅1 + 𝑅2

𝑉𝑂𝑈𝑇 = 𝑉𝐹𝐵 ×

𝑅2

VOUT(V) R1(KΩ) R2(KΩ) RT(KΩ) L1(μH) C1(nF) CIN(μF) COUT(μF) CFF (pF) Opt.

1.0 6.67 10 Non or 0 1.5 100 22 22×2 CFF Chapter

1.05 7.5 10 Non or 0 1.5 100 22 22×2 CFF Chapter

1.2 10 10 Non or 0 1.5 100 22 22×2 CFF Chapter

1.5 15 10 Non or 0 2.2 100 22 22×2 CFF Chapter

1.8 20 10 Non or 0 2.2 100 22 22×2 CFF Chapter

2.5 31.67 10 Non or 0 2.2 100 22 22×2 CFF Chapter

3.3 45 10 Non or 0 2.2 100 22 22×2 CFF Chapter

5.0 73.33 10 Non or 0 2.2 100 22 22×2 CFF Chapter

All the external components are the suggested values, the final values are based on the application testing results.

Selecting the Inductor

The recommended inductor values are shown in the Application Diagram. It is important to guarantee the inductor

core does not saturate during any foreseeable operational situation. The inductor should be rated to handle the

maximum inductor peak current: Care should be taken when reviewing the different saturation current ratings that

are specified by different manufacturers. Saturation current ratings are typically specified at 25°C, so ratings at

maximum ambient temperature of the application should be requested from the manufacturer. The inductor value

can be calculated with:

𝑉𝑂𝑈𝑇 × (𝑉𝐼𝑁 − 𝑉𝑂𝑈𝑇 )

𝐿=

𝑉𝐼𝑁 × ∆𝐼𝐿 × 𝐹𝑂𝑆𝐶

Where ΔIL is the inductor ripple current. Choose inductor ripple current to be approximately 30% to 40% of the

maximum load current. The maximum inductor peak current can be estimated as:

∆𝐼𝐿

𝐼𝐿(𝑀𝐴𝑋) = 𝐼𝐿𝑂𝐴𝐷 +

2

Under light load conditions below 100mA, larger inductance is recommended for improved efficiency. Larger

inductances lead to smaller ripple currents and voltages, but they also have larger physical dimensions, lower

saturation currents and higher linear impedance. Therefore, the choice of inductance should be compromised

according to the specific application.

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 9 / 13

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

Selecting the Input Capacitor

The input current to the step-down converter is discontinuous and therefore requires a capacitor to supply AC current

to the step-down converter while maintaining the DC input voltage. For a better performance, use ceramic capacitors

placed as close to VIN as possible and a 0.1µF input capacitor to filter out high frequency interference is

recommended. Capacitors with X5R and X7R ceramic dielectrics are recommended because they are stable with

temperature fluctuations.

The capacitors must also have a ripple current rating greater than the maximum input ripple current of the converter.

The input ripple current can be estimated with Equation:

𝑉𝑂𝑈𝑇 𝑉𝑂𝑈𝑇

𝐼𝐶𝐼𝑁 = 𝐼𝑂𝑈𝑇 × √ × (1 − )

𝑉𝐼𝑁 𝑉𝐼𝑁

From the above equation, it can be concluded that the input ripple current reaches its maximum at VIN=2VOUT where

𝐼

I𝐶𝐼𝑁 = 𝑂𝑈𝑇

2

. For simplification, choose an input capacitor with an RMS current rating greater than half of the

maximum load current.

The input capacitance value determines the input voltage ripple of the converter. If there is an input voltage ripple

requirement in the system, choose the input capacitor that meets the specification. The input voltage ripple can be

estimate with Equation:

𝐼𝑂𝑈𝑇 𝑉𝑂𝑈𝑇 𝑉𝑂𝑈𝑇

∆𝑉𝐼𝑁 = × × (1 − )

𝐹𝑂𝑆𝐶 × 𝐶𝐼𝑁 𝑉𝐼𝑁 𝑉𝐼𝑁

1 𝐼𝑂𝑈𝑇

Similarly, when VIN=2VOUT, input voltage ripple reaches its maximum of ∆𝑉𝐼𝑁 = ×𝐹 .

4 𝑂𝑆𝐶 ×𝐶𝐼𝑁

Selecting the Output Capacitor

An output capacitor is required to maintain the DC output voltage. The output voltage ripple can be estimated with

Equation:

𝑉𝑂𝑈𝑇 𝑉𝑂𝑈𝑇 1

∆𝑉𝑂𝑈𝑇 = × (1 − ) × (𝑅𝐸𝑆𝑅 + )

𝐹𝑂𝑆𝐶 × 𝐿 𝑉𝐼𝑁 8 × 𝐹𝑂𝑆𝐶 × 𝐶𝑂𝑈𝑇

There are some differences between different types of capacitors. In the case of ceramic capacitors, the impedance

at the switching frequency is dominated by the capacitance. The output voltage ripple is mainly caused by the

capacitance. For simplification, the output voltage ripple can be estimated with Equation:

𝑉𝑂𝑈𝑇 𝑉𝑂𝑈𝑇

∆𝑉𝑂𝑈𝑇 = 2 × (1 − )

8 × 𝐹𝑂𝑆𝐶 × 𝐿 × 𝐶𝑂𝑈𝑇 𝑉𝐼𝑁

A larger output capacitor can achieve a better load transient response, but the maximum output capacitor limitation

should also be considered in the design application. If the output capacitor value is too high, the output voltage will

not be able to reach the design value during the soft-start time and will fail to regulate. The maximum output

capacitor value (COUT_MAX) can be limited approximately with Equation:

𝐶𝑂𝑈𝑇_𝑀𝐴𝑋 = (𝐼𝐿𝐼𝑀_𝐴𝑉𝐺 − 𝐼𝑂𝑈𝑇 ) × 𝑇𝑆𝑆 /𝑉𝑂𝑈𝑇

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 10 / 13

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

Where LLIM_AVG is the average start-up current during the soft-start period, and TSS is the soft- start time.

On the other hand, special attention should be paid when selecting these components. The DC bias of these

capacitors can result in a capacitance value that falls below the minimum value given in the recommended capacitor

specifications table.

The ceramic capacitor’s actual capacitance can vary with temperature. The capacitor type X7R, which operates over

a temperature range of −55°C to +125°C, will only vary the capacitance to within ±15%. The capacitor type X5R

has a similar tolerance over a reduced temperature range of −55°C to +85°C. Many large value ceramic capacitors,

larger than 1uF are manufactured with Z5U or Y5V temperature characteristics. Their capacitance can drop by more

than 50% as the temperature varies from 25°C to 85°C. Therefore, X5R or X7R is recommended over Z5U and

Y5V in applications where the ambient temperature will change significantly above or below 25°C.

Feed-Forward Capacitor (CFF)

RY9120 has internal loop compensation, so adding CFF is optional. Specifically, for specific applications, if

necessary, consider whether to add feed-forward capacitors according to the situation.

The use of a feed-forward capacitor (CFF) in the feedback network is to improve the transient response or higher

phase margin. For optimizing the feed-forward capacitor, knowing the cross frequency is the first thing. The cross

frequency (or the converter bandwidth) can be determined by using a network analyzer. When getting the cross

frequency with no feed-forward capacitor identified, the value of feed-forward capacitor (CFF) can be calculated

with the following equation:

1 1 1 1

𝐶𝐹𝐹 = ×√ ×( + )

2𝜋 × 𝐹𝐶𝑅𝑂𝑆𝑆 𝑅1 𝑅1 𝑅2

Where FCROSS is the cross frequency.

To reduce transient ripple, the feed-forward capacitor value can be increased to push the cross frequency to higher

region. Although this can improve transient response, it also decreases phase margin and cause more ringing. In the

other hand, if more phase margin is desired, the feed-forward capacitor value can be decreased to push the cross

frequency to lower region.

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 11 / 13

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

PC Board Layout Consideration

PCB layout is very important to achieve stable operation. It is highly recommended to duplicate EVB layout for

optimum performance. If change is necessary, please follow these guidelines for reference.

1. Keep the path of switching current short and minimize the loop area formed by Input capacitor, high-side

MOSFET and low-side MOSFET.

2. Bypass ceramic capacitors are suggested to be put close to the VIN Pin.

3. Ensure all feedback connections are short and direct. Place the feedback resistors and compensation

components as close to the chip as possible.

4. VOUT, SW away from sensitive analog areas such as FB.

5. Connect IN, SW, and especially GND respectively to a large copper area to cool the chip to improve thermal

performance and long-term reliability.

Top Layer Bottom Layer

Sample Board Layout

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 12 / 13

RY9120

17V 2A 500KHz ECOT Sync Step-Down Regulator

Package Description

SOT23-6

0.95

2.80 BSC

0.60

3.00

TYP

1.20

EXAMPLE TYP

TOP MARK

AAAAA 1.50

1.70

2.60

3.00

2.60

TYP

PIN 1

TOP VIEW RECOMMENDED PAD LAYOUT

GAUGE PLANE

0.90 0.25 BSC

1.30 1.45 MAX

SEATING PLANE

0.30 0.00 0.09

0.95 BSC 0.30

0.50 0.15 0°~8° 0.20

0.55

FRONT VIEW SIDE VIEW

NOTE:

1. CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

2. PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

3. PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

4. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

5. DRAWING CONFORMS TO JEDEC MS-012, VARIATION BA.

6. DRAWING IS NOT TO SCALE.

Email: support@rychip.com http://www.rychip.com

©RYCHIP Semiconductor Inc. Page 13 / 13

You might also like

- 36V/3A 500Khz Synchronous Step-Down Converter: FeaturesDocument10 pages36V/3A 500Khz Synchronous Step-Down Converter: FeaturesDmitrNo ratings yet

- STI3470 600KHz - 18V 2.0A Synchronous Step - Down ConverterDocument10 pagesSTI3470 600KHz - 18V 2.0A Synchronous Step - Down ConverterHoson AkNo ratings yet

- AP3502Document11 pagesAP3502nassimNo ratings yet

- AOZ3015AIDocument14 pagesAOZ3015AIIcomNo ratings yet

- AOZ2023PIDocument11 pagesAOZ2023PIjuliocunachiNo ratings yet

- Ap 3502 em Regulador DCDC s1005Document11 pagesAp 3502 em Regulador DCDC s1005gerson evandro hanauerNo ratings yet

- RP108J Series: Low Input Voltage 3A LDO Regulator OutlineDocument29 pagesRP108J Series: Low Input Voltage 3A LDO Regulator OutlineArie DinataNo ratings yet

- Shouding: Features General DescriptionDocument7 pagesShouding: Features General DescriptionJuan SenatoriNo ratings yet

- Sy8008A/Sy8008B/Sy8008C: High Efficiency 1.5Mhz, 0.6A/1A/1.2A Synchronous Step Down RegulatorDocument5 pagesSy8008A/Sy8008B/Sy8008C: High Efficiency 1.5Mhz, 0.6A/1A/1.2A Synchronous Step Down RegulatorAnil BpsNo ratings yet

- 2.5A, 18V, 500Khz Acot Synchronous Step-Down Converter: General Description FeaturesDocument14 pages2.5A, 18V, 500Khz Acot Synchronous Step-Down Converter: General Description FeaturesMaxNo ratings yet

- AOZ6604PI Regulador de VoltajeDocument16 pagesAOZ6604PI Regulador de VoltajeDaiverJuarezNo ratings yet

- AOZ6623DI Regulador de VoltajeDocument15 pagesAOZ6623DI Regulador de VoltajeDaiverJuarezNo ratings yet

- 3A, 18V, 700Khz Acot Synchronous Step-Down Converter: Features General DescriptionDocument14 pages3A, 18V, 700Khz Acot Synchronous Step-Down Converter: Features General DescriptionVasil StoyanovNo ratings yet

- AN SY8063 SilergyDocument13 pagesAN SY8063 Silergyzigmund zigmundNo ratings yet

- RYCHIP Semiconductor Inc RY3408 - C370750Document9 pagesRYCHIP Semiconductor Inc RY3408 - C370750Maikol DominguezNo ratings yet

- C90691 - LM2596R 12 - 2016 12 17Document8 pagesC90691 - LM2596R 12 - 2016 12 17Nabla HarryNo ratings yet

- Datasheet - Aoz1280 Simple Buck RegulatorDocument13 pagesDatasheet - Aoz1280 Simple Buck RegulatorCesar ServidoneNo ratings yet

- 2.5A Switch Step Down Switching Regulator: DescriptionDocument10 pages2.5A Switch Step Down Switching Regulator: DescriptionVictor CuaicalNo ratings yet

- AOZ3013PI: General Description FeaturesDocument14 pagesAOZ3013PI: General Description FeaturesJohn KleinNo ratings yet

- 1.5A Switch Step Down Switching Regulator: 1 General FeaturesDocument11 pages1.5A Switch Step Down Switching Regulator: 1 General FeaturesRene gNo ratings yet

- 4.5V To 18V Input, 5.0A Integrated MOSFET Single Synchronous Buck DC/DC ConverterDocument23 pages4.5V To 18V Input, 5.0A Integrated MOSFET Single Synchronous Buck DC/DC ConverterRamonAngelNo ratings yet

- 1V High Efficiency Syncronous Step Up Converter: 1 FeaturesDocument13 pages1V High Efficiency Syncronous Step Up Converter: 1 FeaturesGuillaume RIVARDNo ratings yet

- LED Step-Up Converter Drives Up to Five White LEDsDocument9 pagesLED Step-Up Converter Drives Up to Five White LEDsBudi PrayitnoNo ratings yet

- DatasheetDocument14 pagesDatasheetsamaya egNo ratings yet

- Aerosemi MT1470Document10 pagesAerosemi MT1470StephieNo ratings yet

- Silergy Corp SY8213FCC - C178246Document9 pagesSilergy Corp SY8213FCC - C178246Thai LamNo ratings yet

- AOZ3018PIDocument14 pagesAOZ3018PIpravin jadavNo ratings yet

- RT7296F 0.1Document96 pagesRT7296F 0.1Chiapin LeeNo ratings yet

- 300ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatorDocument11 pages300ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatordinhdtdNo ratings yet

- 1.2A 1.5MHz 7V Synchronous Buck Converter with 96% EfficiencyDocument7 pages1.2A 1.5MHz 7V Synchronous Buck Converter with 96% EfficiencyGeovanny SanJuanNo ratings yet

- Out Products: Monolithic IC MM192x SeriesDocument16 pagesOut Products: Monolithic IC MM192x SeriesIbrain MoranNo ratings yet

- AP3211Document11 pagesAP3211miteshNo ratings yet

- Off-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Document13 pagesOff-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Renato Luther escalanteNo ratings yet

- Sti 3470Document12 pagesSti 3470marcio moratesNo ratings yet

- 300Ma Cmos Ldo Regulator With 15: Μμμμμa Quiescent CurrentDocument14 pages300Ma Cmos Ldo Regulator With 15: Μμμμμa Quiescent CurrentGABRIEL ALFONSONo ratings yet

- Aoz1212ai PDFDocument18 pagesAoz1212ai PDF060279No ratings yet

- Bit 3269Document6 pagesBit 3269zubiNo ratings yet

- SP1232FDocument11 pagesSP1232Fnazala fikri nugrahaNo ratings yet

- Sy6288c20 D20Document6 pagesSy6288c20 D20Sahid Cota CamachoNo ratings yet

- LP3211 LowpowersemiDocument6 pagesLP3211 LowpowersemiRafael BrunoNo ratings yet

- 500ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatorDocument13 pages500ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatoreugeneNo ratings yet

- LWNMNP : General Description FeaturesDocument16 pagesLWNMNP : General Description FeaturesArturo ArmuellesNo ratings yet

- str-x6768n Ds en PDFDocument9 pagesstr-x6768n Ds en PDFCarlNo ratings yet

- 1ch Buck Converter Integrated FET: 12V To 76V Input Voltage Range 3A Output CurrentDocument29 pages1ch Buck Converter Integrated FET: 12V To 76V Input Voltage Range 3A Output CurrentDuc VoquangNo ratings yet

- FP6321A FitiDocument14 pagesFP6321A FitiJob GarciaNo ratings yet

- BUK209-50Y Philips Elenota - PLDocument8 pagesBUK209-50Y Philips Elenota - PLSandra Krzysiek KaduczkaNo ratings yet

- Infineon IR2153 DataSheet v01 00 enDocument9 pagesInfineon IR2153 DataSheet v01 00 enApexAudio BpnNo ratings yet

- Infineon IR2153 DataSheet v01 00 enDocument9 pagesInfineon IR2153 DataSheet v01 00 enApexAudio BpnNo ratings yet

- AOZ1282CIDocument13 pagesAOZ1282CIBelalang TempurNo ratings yet

- CR6848 Chip RailDocument3 pagesCR6848 Chip Railadamz74No ratings yet

- High Speed Low Dropout Middle Current Voltage Regulators: General Description FeaturesDocument13 pagesHigh Speed Low Dropout Middle Current Voltage Regulators: General Description FeaturesВадим МкртчянNo ratings yet

- bm2scq12xt LBZ eDocument33 pagesbm2scq12xt LBZ eBD MNNo ratings yet

- Self-Oscillating Half-Bridge Driver: Ir2153 (D) (S) & (PBF)Document9 pagesSelf-Oscillating Half-Bridge Driver: Ir2153 (D) (S) & (PBF)Javier ParedesNo ratings yet

- LWNMNM : General Description FeaturesDocument16 pagesLWNMNM : General Description FeaturesSergio BarbozaNo ratings yet

- BD8160AEFV DatasheetDocument21 pagesBD8160AEFV Datasheetjose peresNo ratings yet

- 1F - Sot 23 6Document14 pages1F - Sot 23 6freddyNo ratings yet

- Half-Bridge Driver: Features Product SummaryDocument18 pagesHalf-Bridge Driver: Features Product SummaryPE TruNo ratings yet

- Application Note: AN - SY8881: General Description FeaturesDocument9 pagesApplication Note: AN - SY8881: General Description Featuressluz2000No ratings yet

- LM3481MM NOPB National SemiconductorDocument22 pagesLM3481MM NOPB National Semiconductorvs674584No ratings yet

- Internal Photos 1740521Document4 pagesInternal Photos 1740521vs674584No ratings yet

- TPA3116D2 15-W, 30-W, 50-W Filter-Free Class-D Stereo Amplifier Family With AM AvoidanceDocument44 pagesTPA3116D2 15-W, 30-W, 50-W Filter-Free Class-D Stereo Amplifier Family With AM Avoidancekishore_bulli6666No ratings yet

- PDFDocument11 pagesPDFFernando Sobrino-Manzanares MasNo ratings yet

- Model Manual 3960695Document10 pagesModel Manual 3960695vs674584No ratings yet

- Oil Well Drilling Methods: University of Karbala College of Engineering Petroleum Eng. DepDocument8 pagesOil Well Drilling Methods: University of Karbala College of Engineering Petroleum Eng. DepAli MahmoudNo ratings yet

- Slogan Goes Here: Local Store Importing CompanyDocument1 pageSlogan Goes Here: Local Store Importing Company5gt6kdfdqhNo ratings yet

- Analysis of A Refrigeration Cycle With Coolprop PDFDocument6 pagesAnalysis of A Refrigeration Cycle With Coolprop PDFewan_73No ratings yet

- TM Journal Class 5 Pharma Trademarks 2018Document1,192 pagesTM Journal Class 5 Pharma Trademarks 2018Tahir LabbeNo ratings yet

- Clay Brick Making Machine Mew CB 3000Document5 pagesClay Brick Making Machine Mew CB 3000Aakansh NigamNo ratings yet

- Ken Jennings' Junior Genius Guides: Maps and Geography (Excerpt)Document24 pagesKen Jennings' Junior Genius Guides: Maps and Geography (Excerpt)Simon and Schuster100% (2)

- Mental Health Awareness and PFA Training ReportDocument4 pagesMental Health Awareness and PFA Training ReportSHEILA MAE PERTIMOS100% (14)

- Festivals WorksheetDocument8 pagesFestivals WorksheetlurdesNo ratings yet

- Sap GlossaryDocument324 pagesSap GlossaryNikos TataliasNo ratings yet

- BIG-IP Access Policy Manager CustomizationDocument118 pagesBIG-IP Access Policy Manager CustomizationDhananjai SinghNo ratings yet

- GYROSCOPE ManualDocument8 pagesGYROSCOPE ManualAman BansalNo ratings yet

- PAPD Cable glands for hazardous areasDocument2 pagesPAPD Cable glands for hazardous areasGulf Trans PowerNo ratings yet

- CustomizingDocument5 pagesCustomizingEduardo Padilla Lozano100% (1)

- Woody Plant Seed Manual - CompleteDocument1,241 pagesWoody Plant Seed Manual - CompleteJonas Sandell100% (1)

- ATPL theory summary formulas and guidelines (40 charactersDocument60 pagesATPL theory summary formulas and guidelines (40 charactersJonas Norvidas50% (2)

- 4 McdonaldizationDocument17 pages4 McdonaldizationAngelica AlejandroNo ratings yet

- Cardio Fitt Pin PostersDocument5 pagesCardio Fitt Pin Postersapi-385952225No ratings yet

- Roke TsanDocument53 pagesRoke Tsanhittaf_05No ratings yet

- Galloway 1989 Genetic Stratigraphic Sequence Basin Analysis IDocument18 pagesGalloway 1989 Genetic Stratigraphic Sequence Basin Analysis IMitreNo ratings yet

- Knowledge, Attitudes and Practices of Nursing Students on Dengue FeverDocument9 pagesKnowledge, Attitudes and Practices of Nursing Students on Dengue FeverElinNo ratings yet

- Aquilion ONE GENESIS Edition Transforming CTDocument40 pagesAquilion ONE GENESIS Edition Transforming CTSemeeeJuniorNo ratings yet

- Underwater vessels, sensors, weapons and control systemsDocument1 pageUnderwater vessels, sensors, weapons and control systemsNguyễn ThaoNo ratings yet

- PHL Ad 17 01 Operationalguidance 2017 Eng Ops Manual Adolescent Health Development ProgramDocument111 pagesPHL Ad 17 01 Operationalguidance 2017 Eng Ops Manual Adolescent Health Development ProgramJoanne G Haw GetidaNo ratings yet

- Detailed CET ListDocument11 pagesDetailed CET ListBhagya H SNo ratings yet

- BS 0812-114 - 1989Document12 pagesBS 0812-114 - 1989عمر عمرNo ratings yet

- Human Resource Reforms in Public Administration: The Importance of The Reward SystemDocument10 pagesHuman Resource Reforms in Public Administration: The Importance of The Reward SystemElena BejanNo ratings yet

- Abstract & Concrete NounsDocument2 pagesAbstract & Concrete NounsSitifatimah92No ratings yet

- Demolition and excavation worksDocument30 pagesDemolition and excavation worksHafizan Hanafiah100% (3)

- Hotel Training ReportDocument14 pagesHotel Training ReportButchick Concepcion Malasa100% (1)

- The Impact of Interest Rates On Economic Growth in KenyaDocument41 pagesThe Impact of Interest Rates On Economic Growth in KenyaSAMUEL KIMANINo ratings yet