Professional Documents

Culture Documents

Xapp 137

Uploaded by

guezaki6636Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Xapp 137

Uploaded by

guezaki6636Copyright:

Available Formats

APPLICATION NOTE

Configuring Virtex FPGAs from

Parallel EPROMs with a CPLD

XAPP 137 March 1, 1999 (Version 1.0) Application Note by Carl Carmichael

Summary

Previous generations of Xilinx FPGAs supported a Master Parallel Configuration Mode which allowed the FPGA to configure

itself directly from a parallel (byte wide) PROM. The Virtex family of Xilinx FPGAs does not utilize a Master Parallel mode.

This appnote describes a simple interface design to configure a Virtex device from a parallel EPROM using the SelectMAP

configuration mode.

Xilinx Family

Virtex & XC9500

Introduction

Many FPGA users prefer to store configuration data on par- DONE

allel EPROMs because they are available in greater stor-

The DONE output indicates the completion of configuration

age capacities than serial PROMs. A parallel PROM stores

and the beginning of the Startup sequence.

data as an addressed byte which is accessed by an

address bus. INIT

Configuring a Virtex FPGA through the SelectMAP mode is The bidirectional open-drain INIT pin is used to hold off

8 times faster than bit-serial mode. The SelectMAP config- configuration initialization, and it indicates when CRC

uration mode utilizes an 8 bit configuration bus and 7 con- errors occur in the configuration data.

trol signals for synchronization and handshaking of data. WRITE

Combining larger memory capacities with an 8 bit interface The WRITE input is a write strobe that must be asserted

results in a faster configuration scheme that requires fewer and held throughout the loading of data.

storage elements thus reducing board utilization and nec-

essary time for system initialization. This is made possible BUSY

by the addition of a small interface design to provide the The BUSY open-drain output indicates whether the current

address bus for the parallel PROM and the necessary con- byte is being loaded or ignored.

trol signals for SelectMAP configuration.

CS

SelectMAP in Virtex The CS input is the Chip Select signal used to enable the

FPGA to be sensible of the SelectMAP interface.

SelectMAP uses a byte wide bidirectional access port for

reading and writing the configuration data of a Virtex M2 M1 M0

FPGA. As a configuration mode it is very similar to the The MODE pins M<2:0> must be set to indicate which con-

Express mode used by XC4000XLA and SpartanXL figuration mode will be used. For SelectMAP configuration

FPGAs. To use the SelectMAP mode the following signals these must be <110>.

are used.

D7...D0 Configuration Process Steps

The D7 through D0 pins comprise the 8 bit bidirectional The following are the steps for performing a Virtex Select-

data bus. MAP configuration.

CCLK Reset the Configuration Logic

The CCLK is the configuration clock input signal used by If configuration is to follow power-up, or a recycling of the

the internal configuration logic. power source, then the configuration logic will become

active already initialized. However, if the FPGA is to be

PROG reconfigured without the recycling of power, then the PROG

The PROG input signal resets the internal configuration input must be asserted Low for at least 300ns to reset the

logic and re-initializes the internal configuration memory. configuration logic.

XAPP 137 March 1, 1999 (Version 1.0) 1

Time-out Start of Configuration End of Configuration

After the release of the PROG input, or the powering up of The DONE output transitions High to indicate the end of

the FPGA, the INIT output stays Low while the internal con- configuration and the beginning of the startup sequence.

figuration memory is automatically cleared. During the startup sequence the D7...D0, WRITE, BUSY,

Unlike previous generations of FPGAs, Virtex does not INIT, and CS pins all become user IO. If any of these pins

require an additional time-out period following initialization. are used by the configured design, then any driving source

Configuration may begin as soon as INIT has gone High. used only for configuration purposes must be disabled so

The FPGA may ignore as much as the first three clock as not to contend.

cycles of data; however, a Virtex Bit-Stream is padded with Depending on the startup options selected in BitGen, com-

8 dummy bytes at the beginning of the data stream to pleting the startup phase will require as much as 8 CCLK

account for this. cycles after DONE has transitioned High. However, since

Loading Configuration Data the example shown below uses a free running oscillator,

this is not a concern. The Virtex FPGA will complete the

To begin configuration, the WRITE and CS inputs must be startup phase even if the CS signal is de-asserted.

asserted Low and held. Each byte is loaded on the rising

edge of CCLK. If BUSY was Low during the CCLK transi- Interface Design

tion then the byte was accepted. If it was High then the byte

was ignored and must be reloaded on the next clock cycle. To configure the Virtex FPGA from a parallel PROM, a

BUSY is a synchronous signal; Therefore, CCLK can not small interface is needed to generate the PROM addresses

be suspended until the BUSY is de-asserted. For configu- and load the data into the FPGA. Although any one of sev-

ration clocks below 50MHz the BUSY can be ignored eral technologies might be used, a Xilinx CPLD is a simple

entirely, and removed from the interface design.* and cost effective implementation, as shown in Figure 1.

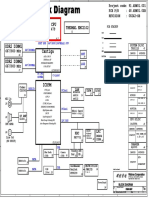

VPU VPU

D(7:0) D(7:0) VCCO 3.3 V

OE DONE VCORE 2.5 V

CE INIT

*Only needed when oscillator is greater than 50 MHz.

BUSY

EPROM

VIRTEX

or CPLD FPGA

FLASH DONE CS CS

INIT WRITE WRITE

BUSY PROG PROG

A(19:0) A(19:0) CCLK CCLK

Oscillator M2 M1 M0

VPU

NC NC

Control Signal

Figure 1: SelectMAP and EPROM Interface Circuit Diagram

2 XAPP 137 March 1, 1999 (Version 1.0)

Voltage Supplies and Pullups Mbyte (8 Mbit) PROM is shown which requires a 20 bit

The Virtex FPGA was designed for mixed voltage environ- address bus. If less than half of the PROM was to be used,

ments. The internal voltage (VCORE) requires a 2.5 V sup- or a smaller PROM in its place, then the address counter

ply. During configuration, the IO are automatically set to the could be decreased. For connecting multiple PROMs see

LVTTL standard which requires a VCCO of 3.3 V. If this is “Interfacing Multiple PROMs” on page 4.

incompatible with the IO standard to be used after configu- Write Control Register

ration, VCCO may be left disabled during configuration and

The CS and WRITE input signals to the FPGA must be

all the configuration pins (VCCO_2, DONE, INIT, and asserted and held Low for configuration. If only one FPGA

BUSY) can be pulled up to VPU. Even if the VCCO is is being targeted for configuration these two signals may be

driven, the Pullups should remain on DONE and INIT. The derived from the same source. For targeting multiple

VPU refers to the needed IO voltage for the CPLD and

FPGAs see “Daisy Chaining Multiple FPGAs” on page 5.

PROM. Most likely this will either be 3.3 or 5.0 V. Either is

acceptable to the Virtex FPGA. No translation is needed. Configuration must be delayed until the INIT signal has

The recommended pullup value is 4.7K ohm. This value is transitioned High indicating that FPGA initialization has

not critical. Smaller pullup resistors will of course increase completed.

current draw when that node is driven to a logic Low. Oscillator

The PromMAP Design The Virtex configuration logic was designed to work with a

free-running oscillator. The maximum input oscillator fre-

The CPLD design promMAP, shown in Figure 2, consists of quency for a Virtex FPGA is 66 MHz; however, in this case

an address counter, a write control register, some tristate the maximum frequency for the oscillator is determined by

buffers and random logic. The PROG input acts as a global the access time of the PROM (tACC) plus the setup time for

reset. The DONE acts as a global tristate. The INIT and the SelectMAP data inputs (tSMDCC).

BUSY hold off the address counter from incrementing while

the FPGA initializes or processes data.

1

Oscillator Frequency =

Address Counter

tACC + tSMDCC

The address counter needs to be large enough to accom-

modate the address bus width of the PROM. In Figure 1 a 1

INIT Address Counter

CE Q(19:0) A19..A0

BUSY

C

CLR

DONE

Write Control

D Q CS/

WRITE

CCLK C

CLR

PROG

Figure 2: PromMAP Interface Design

XAPP 137 March 1, 1999 (Version 1.0) 3

The tSMDCC for a Virtex FPGA is 2.0ns. A typical tACC for an The output enable (OE) input pins of the PROMs can be

EPROM (e.g. AT27c080) is 100ns. Using these values the driven by an address decode of the most significant bits of

maximum frequency of the oscillator is 9.6MHz (76.8 MBit/ the address counter in the promMAP design as shown in

s). This is far below the CCLK frequency capabilities of the Figure 4.

Virtex (66 MHz) and CPLD (66.6 MHz in a XC9536-10). For the example shown in Figure 3, the 8 MBit PROM has

Therefore, a faster PROM would allow for faster configura- been replaced with two 4 MBit PROMs. The common

tion speeds up to 66 MHz (528 MBit/s). address bus is now only 19 bits wide and the MSB A(19) is

used to select between the PROMs, see Table 1.

PromMAP Design Files

Table 1: Address decode for two PROM

The promMAP design was built in an XC9536VQ44-10 and

selection

tested with an XCV300BG432 and an AT27c080. The

VHDL, Verilog, source code and Foundation project for the A(19) OE0 OE1

design can be downloaded from the XIlinx website at ftp:// 0 0 1

ftp.xilinx.com/pub/applications/xapp/xapp137.zip 1 1 0

Interfacing Multiple PROMs The CE outputs are just a binary decode of an additional

If the needed memory storage capacity requires the use of MSB of the address counter. To add more PROMs simply

multiple PROMs then the interface design can be altered to increase the size of the counter and binary decoder.

accommodate PROM daisy-chaining as shown in Figure 3.

VPU VPU

D(7:0) D(7:0) D(7:0)

D(7:0

CE CE DONE

INIT

BUSY

EPROM EPROM

or or

DONE CS CS

FLASH FLASH

INIT WRITE WRITE

BUSY VIRTEX

A(18:0) A(18:0) A(18:0) CPLD

PROG PROG

OE OE OE0

OE1 CCLK CCLK

VPU

Control Signal

Figure 3: Connecting Multiple PROMs in daisy-chain

4 XAPP 137 March 1, 1999 (Version 1.0)

Decoder Daisy Chaining Multiple FPGAs

OE0

SelectMAP configuration does not support a standard

A19

daisy-chain configuration like the bit-serial modes do. How-

OE1 ever, in an application such as this, where there are multi-

ple FPGAs to be configured, the PromMAP design may be

altered to accommodate a parallel daisy-chain so that mul-

tiple interface chips are not necessary. As shown in

Figure 5, the daisy-chaining of multiple FPGAs in parallel is

similar to daisy-chaining multiple PROMs.

Address Counter For each FPGA the DONE and CS signals must be con-

A18..A0

nected to the interface design separately. The BUSY and

CE Q(19:0) WRITE signals can be a common line between the FPGAs.

When the first FPGA raises it’s DONE signal the interface

C should disable that FPGA’s CS input and enable the next

CLR one in the chain, and so on until all DONEs are high. An

example of this is shown in Figure 6.

Using this method will cause each FPGA to become active

after its DONE transitions High. Therefore, it is important

Figure 4: Selecting multiple PROMs that none of the configuration pins used for SelectMAP con-

figuration be used as IOs in the FPGA designs. Otherwise

contention could result when one or more FPGAs are con-

figured and active, but others are not yet configured.

VPU VPU

D(7:0) D(7:0

D(7:0) D(7:0

D(7:0)

DONE DONE

INIT INIT

BUSY BUSY

EPROM

or VIRTEX VIRTEX

FLASH CPLD FPGA FPGA

(1M x 8) CS0 CS CS

DONE0

DONE1 CS1

INIT WRITE WRITE WRITE

BUSY PROG PROG PROG

A(19:0) A(19:0) CCLK CCLK CCLK

M2 M1 M0 M2 M1 M0

OE/CE OE/CE

NC NC NC NC

VPU

Control

Oscillator

Figure 5: Connecting multiple FPGAs for parallel daisy-chaining

XAPP 137 March 1, 1999 (Version 1.0) 5

DONE_ALL

DONE0 Q CS0

D

DONE1

CS1

D PRE Q

DONE(n-1) DONE_ALL

DONE(n)

CSn

D PRE Q

Figure 6: Daisy-chain of FPGA Chip Selects

Alternatively, if it is desired to use these pins after configu- previous ordered DONE signal transitions High, the PRE-

ration, then the common WRITE signal input for each set is released and the register loads the value of the asso-

FPGA could be connected to the GTS and GSR (or other ciated DONE signal on each clock cycle. When the

reset signal) in the FPGA design so that these pins will not associated DONE transitions High, the corresponding CS

be driven by the active FPGAs while others are still config- output will transition High disabling the configuration for

uring. that FPGA in the chain. This removes the PREset of the

Figure 6 shows how the CS outputs are cascaded accord- next segment and allows configuration of the next FPGA in

ingly with the DONE inputs. In the single FPGA example the chain. The first segment does not make use of a PRE-

the DONE input is the global tristate control for all outputs. set. When all DONE signals are High all outputs will dis-

For multiple FPGAs the global tristate signal (DONE_ALL) able.

is generated by ANDing together all the DONE lines from The WRITE signal need only be held Low throughout the

the separate FPGAs. entire configuration process and disabled when DONE

goes High. Since the CS selects will not assert and the

The dotted extension in Figure 6 demonstrates that more

FPGAs may be added to the chain by adding to the chain of address counter will not increment until INIT is High, the

chip select registers. For each segment, the register is held WRITE signal input to the output tristate buffer may simply

asynchronously PREset when the previous ordered DONE be a GND connection (a true Open-Drain style output).

(n-1) and the associated DONE (n) are both Low. When the

6 XAPP 137 March 1, 1999 (Version 1.0)

Synchronizing Startup Cascading PROM Files

An alternative method to activating the FPGAs sequentially PromGen must be run on each FPGA design separately

would be to synchronize the startup of all the FPGAs by and the resulting prom files concatenated together. Care

combining all the DONE lines into one signal. Virtex auto- must be taken to assure that the prom files are in the

matically synchronizes the startup sequence to wait for desired order. Do not use PromGen to create a single prom

DONE to be externally released. It is, however, important file as would be done for bit-serial daisy-chaining. This

that the BitGen option to “DriveDone” is not selected. By would result in an incorrect bit stream for this configuration

default this is not the case. Unless otherwise specified, the scheme.

DONE pin will be an open-drain output. The PROM files for each of the FPGAs in the daisy-chain

Combining the DONE signals means they cannot be used must be simply concatenated together. This may be

to indicate when configuration must transition to the next accomplished in a variety of ways depending on the pro-

FPGA in the chain. Instead address decoding would be grammer used.

used to disable and enable the individual CS outputs. If your programmer can use HEX files then a simple concat-

In Figure 7, decoding logic PREsets the CS control register enation of hex files is all that’s needed. The PromGen utility

at Address 0 (set all CS registers High in the beginning) has a switch option to create HEX files.

and Toggles the register at the starting address and ending If your PROM Programmer’s software has edit ability, then it

address for the desired configuration data. Set the starting may allow you to read in each of the PROM files individually

address of the first register to 1h. Otherwise, the register

and specify which address to load up from.

will not toggle. The decode of the starting address for one

stage can also serve as the ending address decode of the If the programmer requires a single PROM file in addressed

previous stage. format (mcs, tek, exo), then some manual editing may be

required. It should be noted that a daisy chain of Virtex

Synchronizing Startup in this manner simplifies the board PROM files will typically be too big for the MCS and TEK

connections and worries of contention during configuration. formats. EXO is usually the better choice and easier to

However, this also increases the size of the PromMAP work with.

design. The starting and ending address values for each

stage is easily determined after generating the final PROM To concatenate EXO files together, first generate the EXO

file. for the first bit file in the chain with PromGen loading up

from address 0h. View the EXO file. The very last line

should be deleted. The second to last line should also be

deleted, but first note the starting address for that line. For

example if the last 2 lines read:

DONE

S208035760000000003D

Decode

S804000000FB

Address What you see here is that the data 00000000 is loaded in

00000h

starting at address 35760h. This line is only 4 bytes, a par-

tial line (a full line is 16 bytes), this line should be deleted

and the next prom file generated should start at address

Decode

Starting-

35760h. Then the two files may be concatenated together.

Address CS(n) For more stages to the daisy chain, simply continue with

& T PRE Q this same process.

Ending-

Address The 4 bytes of data that is being removed from the PROM

C file are at the end of a 16 byte section of dummy data that

merely represents needed clock cycles to complete the

startup sequence (actually, only 8 clock cycles are

needed). Since a free running oscillator is being used in

this case, the unwanted dummy bits may be discarded.

Address Bus

Figure 7: CS Address Decoding

XAPP 137 March 1, 1999 (Version 1.0) 7

You might also like

- MSX Bios - Listing Part1 - BúsquedaDocument285 pagesMSX Bios - Listing Part1 - BúsquedaAndyNo ratings yet

- Network with Practical Labs Configuration: Step by Step configuration of Router and Switch configurationFrom EverandNetwork with Practical Labs Configuration: Step by Step configuration of Router and Switch configurationNo ratings yet

- 1 車用 CAN Bus 網路技術探討Document72 pages1 車用 CAN Bus 網路技術探討Wan Tak SiNo ratings yet

- Digital Logic Design ProjectsDocument23 pagesDigital Logic Design ProjectsMychon KanNo ratings yet

- Fpga & It's ArchitectureDocument39 pagesFpga & It's Architectureeeshgarg100% (6)

- Basic Config Guide For OCLAN Switch Ver 3 0Document11 pagesBasic Config Guide For OCLAN Switch Ver 3 0anoop.ashu9376No ratings yet

- Ccnpv7.1 Switch Lab6-2 Hsrpv6 InstructorDocument23 pagesCcnpv7.1 Switch Lab6-2 Hsrpv6 InstructorAustin GriffithNo ratings yet

- Customizable Embedded Processors PDFDocument527 pagesCustomizable Embedded Processors PDFEfraín HerreraNo ratings yet

- TN65CLDR001 2 3Document674 pagesTN65CLDR001 2 3Naveed Ahmed100% (3)

- MCBSTM32C Lab PDFDocument30 pagesMCBSTM32C Lab PDFguezaki6636No ratings yet

- Fpga TutorialDocument10 pagesFpga Tutorialgsavithri_4017No ratings yet

- Fpga Interview QuestionDocument35 pagesFpga Interview QuestionRAGUL RAJ S100% (1)

- FPGA Selection: LTC2387-18 S.No Pin - Name Pin - No. - ADC Mode PurposeDocument6 pagesFPGA Selection: LTC2387-18 S.No Pin - Name Pin - No. - ADC Mode PurposeGurinder Pal SinghNo ratings yet

- How Does FPGA Work: OutlineDocument17 pagesHow Does FPGA Work: OutlinehariharankalyanNo ratings yet

- FPGA Architecture and ImplementationDocument59 pagesFPGA Architecture and ImplementationManas BhattNo ratings yet

- Ccnpv7.1 Switch Lab6-3 GLBP StudentDocument18 pagesCcnpv7.1 Switch Lab6-3 GLBP StudentSebastian CorredorNo ratings yet

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkFrom EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkNo ratings yet

- 3.1.2 Lab - Implement Advanced STP Modifications and Mechanisms - ILMDocument30 pages3.1.2 Lab - Implement Advanced STP Modifications and Mechanisms - ILMDemon Boy0% (1)

- Brksec 3055Document190 pagesBrksec 3055Majnu SmNo ratings yet

- An63620 001-63620Document11 pagesAn63620 001-63620अमरेश झाNo ratings yet

- Xue 2014Document4 pagesXue 2014jose.borjaNo ratings yet

- Acer Emachines d725 - Wistron Hm40-MvDocument51 pagesAcer Emachines d725 - Wistron Hm40-MvNguyễn Công CườngNo ratings yet

- FPGA TechnologyDocument26 pagesFPGA TechnologyvinaypantraNo ratings yet

- XC 18 V00 PromsDocument20 pagesXC 18 V00 PromsJuan CarlosNo ratings yet

- Delivered By.. Love Jain P08ec907Document24 pagesDelivered By.. Love Jain P08ec907api-19772070100% (1)

- Cyc c51013 33-37Document5 pagesCyc c51013 33-37Huascar Anavi loayzaNo ratings yet

- Cs295: Modern Systems What Are Fpgas and Why Should You CareDocument22 pagesCs295: Modern Systems What Are Fpgas and Why Should You CareGiovanni OrsariNo ratings yet

- High Speed Data Acquisition System Using FpslicDocument4 pagesHigh Speed Data Acquisition System Using Fpslictkpriya76No ratings yet

- Product Obsolete or Under Obsolescence: Xc1700E, Xc1700El, and Xc1700L Series Configuration PromsDocument13 pagesProduct Obsolete or Under Obsolescence: Xc1700E, Xc1700El, and Xc1700L Series Configuration PromsLaboratorio GTO Perú S.A.C.No ratings yet

- Escuela de Ciencias Básicas, Tecnología e Ingeniería: Universidad Nacional Abierta Y A DistanciaDocument36 pagesEscuela de Ciencias Básicas, Tecnología e Ingeniería: Universidad Nacional Abierta Y A DistancialeoNo ratings yet

- Machxo3 Programming and Configuration Usage Guide: August 2017 Technical Note Tn1279Document64 pagesMachxo3 Programming and Configuration Usage Guide: August 2017 Technical Note Tn1279Horacio DorantesNo ratings yet

- Ksj Ethercat Fpga Master 【Introduction】Document4 pagesKsj Ethercat Fpga Master 【Introduction】Andres LNo ratings yet

- Microcontroller-Based Spartan-3 Generation Fpga ConfiguratorDocument6 pagesMicrocontroller-Based Spartan-3 Generation Fpga ConfiguratorMaicherNo ratings yet

- FpgaDocument6 pagesFpgaÁryâñ SinghNo ratings yet

- Yeferson Sierra Ccnpv7.1 Switch Lab6-3 GLBP StudentDocument28 pagesYeferson Sierra Ccnpv7.1 Switch Lab6-3 GLBP StudentSebastianBarreraNo ratings yet

- Lecture 22Document47 pagesLecture 22Piyush ParasharNo ratings yet

- Wistron HOMA (TM15''), GW51, 07245-1 PDFDocument57 pagesWistron HOMA (TM15''), GW51, 07245-1 PDFtorlamenNo ratings yet

- VHDL Module2 Rev BDocument14 pagesVHDL Module2 Rev BVishal PalNo ratings yet

- CPLD and Fpga - Unit3Document107 pagesCPLD and Fpga - Unit3shriyaNo ratings yet

- Design and Implementation of FPGA Based High Speed Data Acquisition Systems For Embedded ApplicationsDocument52 pagesDesign and Implementation of FPGA Based High Speed Data Acquisition Systems For Embedded ApplicationsachakracuNo ratings yet

- 3.1.2 Lab - Implement Advanced STP Modifications and MechanismsDocument20 pages3.1.2 Lab - Implement Advanced STP Modifications and MechanismsSolange LuzNo ratings yet

- Cyc c51013 1-6Document6 pagesCyc c51013 1-6Huascar Anavi loayzaNo ratings yet

- Xilinx Xc7k160t-2ffg676i Fpga PriceDocument6 pagesXilinx Xc7k160t-2ffg676i Fpga PricejackNo ratings yet

- SpaceWire-to-GigabitEther UesrGuide 20100930Document19 pagesSpaceWire-to-GigabitEther UesrGuide 20100930Isaac LopezNo ratings yet

- AT17C65Document10 pagesAT17C65meroka2000No ratings yet

- Realtek Single Chip Fast Ethernet Controller With Power Management RTL8139C (L)Document60 pagesRealtek Single Chip Fast Ethernet Controller With Power Management RTL8139C (L)vinh_electronicsNo ratings yet

- Wistron Petra UMA, 11324-1Document60 pagesWistron Petra UMA, 11324-1marusvNo ratings yet

- Slaa 115Document4 pagesSlaa 115api-3744762No ratings yet

- Picoblaze TutorialDocument6 pagesPicoblaze TutorialHamid Reza Mehtari TaheriNo ratings yet

- Lec06 FPGACircuitDesignDocument25 pagesLec06 FPGACircuitDesign0106062007No ratings yet

- Iecon2018 v2Document6 pagesIecon2018 v2sergioNo ratings yet

- Stepper Motor Implementation On FPGA (1) With 1.5 FinalDocument61 pagesStepper Motor Implementation On FPGA (1) With 1.5 Finalswati sakhare100% (1)

- 24.1.4 Lab - Implement Flexible Netflow - ILMDocument22 pages24.1.4 Lab - Implement Flexible Netflow - ILMTRYST CHAMANo ratings yet

- 1670 Petra UMA MB-Aspire V5-531 V5-571-11324Document103 pages1670 Petra UMA MB-Aspire V5-531 V5-571-11324juan carlosNo ratings yet

- Basys2 Reference ManualDocument12 pagesBasys2 Reference ManualOsman SinanoğluNo ratings yet

- Introduction To Cplds and Fpgas: by N.ChandrasekharanDocument21 pagesIntroduction To Cplds and Fpgas: by N.ChandrasekharanWilliam Arief WengNo ratings yet

- Implement Flexible NetflowDocument21 pagesImplement Flexible NetflowTI CursosNo ratings yet

- Acer Aspire 5930GDocument50 pagesAcer Aspire 5930Gperaja12No ratings yet

- The Low-Cost, Efficient Serial Configuration of Spartan FpgasDocument9 pagesThe Low-Cost, Efficient Serial Configuration of Spartan FpgasSal ManNo ratings yet

- SPI Flash Config Xilinx FPGAsDocument14 pagesSPI Flash Config Xilinx FPGAsalaki1000No ratings yet

- All About Xilinx Xc4020xl-09ht176c FpgaDocument5 pagesAll About Xilinx Xc4020xl-09ht176c FpgajackNo ratings yet

- Fpga1 - What IsDocument25 pagesFpga1 - What IsThy NguyễnNo ratings yet

- How To Implement DSP Algorithms Using The Xilinx Spartan 3E Starter BoardDocument7 pagesHow To Implement DSP Algorithms Using The Xilinx Spartan 3E Starter BoardShahzad SaleemNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- LEARN MPLS FROM SCRATCH PART-B: A Beginners guide to next level of networkingFrom EverandLEARN MPLS FROM SCRATCH PART-B: A Beginners guide to next level of networkingNo ratings yet

- Curiosity PIC32MZ EF 2.0 Development Board FeaturesDocument41 pagesCuriosity PIC32MZ EF 2.0 Development Board Featuresguezaki6636No ratings yet

- Medical Electrical Equipment - Part 2-41: Particular Requirements For Basic Safety and Essential Performance of Surgical Luminaires and Luminaires For DiagnosisDocument23 pagesMedical Electrical Equipment - Part 2-41: Particular Requirements For Basic Safety and Essential Performance of Surgical Luminaires and Luminaires For Diagnosisguezaki6636No ratings yet

- Pi CameraDocument213 pagesPi Cameraguezaki6636100% (1)

- CAT4016 16-Channel Constant Current LED Driver: DescriptionDocument14 pagesCAT4016 16-Channel Constant Current LED Driver: DescriptionLucilia Dos SantosNo ratings yet

- AMD Functional Data Sheet, 939-Pin Package: Advanced Micro DevicesDocument87 pagesAMD Functional Data Sheet, 939-Pin Package: Advanced Micro DevicesamdatiNo ratings yet

- Temperature Sensor With Buffer-Chain Based Time-To-Digital Converter For Ultralow Voltage OperationDocument14 pagesTemperature Sensor With Buffer-Chain Based Time-To-Digital Converter For Ultralow Voltage OperationJames MorenoNo ratings yet

- S32K DSDocument85 pagesS32K DSResham ParmarNo ratings yet

- Beckhoff Products 2020 PDFDocument98 pagesBeckhoff Products 2020 PDFenriconoveNo ratings yet

- Supermicro C2SBX, C2SBX+ (User Manual)Document92 pagesSupermicro C2SBX, C2SBX+ (User Manual)MechDRNo ratings yet

- AutoChips MCU Selection GuideDocument10 pagesAutoChips MCU Selection Guidesunhua1983No ratings yet

- Italy SKL Price ListDocument5 pagesItaly SKL Price ListPatrick GeorgeNo ratings yet

- DC Expert CsDocument2 pagesDC Expert CsvasanthmahadevNo ratings yet

- PLC Based Laser Control UnitDocument24 pagesPLC Based Laser Control UnitBrahmanandareddy ReddyNo ratings yet

- Spek Acer Aspire Az1650 18Document9 pagesSpek Acer Aspire Az1650 18Nebula OriomNo ratings yet

- Design of 8: 1 Multiplexer Using When-Else Concurrent Statement (Data Flow Modeling Style)Document2 pagesDesign of 8: 1 Multiplexer Using When-Else Concurrent Statement (Data Flow Modeling Style)dineshvhavalNo ratings yet

- Am27c256 AmdDocument12 pagesAm27c256 AmdRafaelNo ratings yet

- DECKELDocument2 pagesDECKELOmar LeonNo ratings yet

- PIC Microcontrollers: Chapter 5: Branch, Call, and Time Delay LoopDocument31 pagesPIC Microcontrollers: Chapter 5: Branch, Call, and Time Delay LoopBernard Maacaron100% (1)

- c02 En4442en00enDocument14 pagesc02 En4442en00enAgnes EcsekiNo ratings yet

- DpcoDocument58 pagesDpcovarshavarsha3690No ratings yet

- xr21V1410 131 072513Document28 pagesxr21V1410 131 072513kokantNo ratings yet

- Ibm x3400Document230 pagesIbm x3400al_babaNo ratings yet

- An Overview of Motorola DSP563XX ProcessorsDocument17 pagesAn Overview of Motorola DSP563XX ProcessorsS G ShivaPrasad YadavNo ratings yet

- Designing Secure USB-Based DonglesDocument7 pagesDesigning Secure USB-Based DonglesManoj Kumar MauryaNo ratings yet

- Advance Computer Architecture - CS501 Spring 2013 QuizDocument4 pagesAdvance Computer Architecture - CS501 Spring 2013 QuizAkram KhanNo ratings yet

- Chapter 04 Computer Architecture CH04-COA9e Upto MidDocument8 pagesChapter 04 Computer Architecture CH04-COA9e Upto MidFasih DawoodNo ratings yet

- Dasar Teknik Digital: Mata KuliahDocument14 pagesDasar Teknik Digital: Mata KuliahAnnysa UtamiNo ratings yet