Professional Documents

Culture Documents

Placement Test

Uploaded by

Vasudevareddy ThalamatiOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Placement Test

Uploaded by

Vasudevareddy ThalamatiCopyright:

Available Formats

VLSI Training Services

Setting standards in VLSI Design

Final Test

Time: 3 Hrs. Total Marks: 100

Part – A

Marks: 15

Digital (15 Marks)

1. Use minimum no. of 4-bit ring counters, 5-bit Johnson counters & mod 8 counters to

generate clocks with frequencies of 1Mhz, 2Mhz & 10Mhz from a source clock with a

frequency of 320Mhz. 8M

2. Draw a Moore model FSM for a sequential circuit whose output will be toggled with the

occurrence of ‘11’ sequence in an overlapping manner. 7M

PART – B

Verilog (15 Marks) Marks: 15

1. Find the hardware inferred by the following code. 4M

module test(input [3:0]a,

input [3:0]b,

input clk, rst_n,

output reg [4:0] sum);

always @(posedge clk)

begin

if(!rst_n)

sum <= 5'b0;

else

sum <= a+b;

end

endmodule

2. Write an RTL code to design a sequence detector in MOORE non-overlapping

manner to detect 1010 with MSB first. 7M

Copyright © 2023 Maven Silicon

www.maven-silicon.com

VLSI Training Services

Setting standards in VLSI Design

3. Predict the output of the following Verilog program 4M

module test();

integer a = 0;

initial

begin

#2 a = #2 2;

a <= #3 3;

#2 a = 4;

#2 a <= 5;

#2 a = #2 6;

a = #2 7;

a <= #2 8;

#2 a <= #2 9;

#3 a = 10;

end

initial

$monitor ("at time t = %0t, a = %0d", $time, a);

endmodule

PART – C

Physical Design Marks : 60

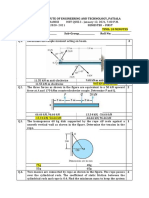

1. Calculate Va , Vb, Vc and Vo for given the circuit using the Pass transistor logic. 4M

(Vt =0.8)

2. Consider the AND gate shown below: 6M

The delay and the output slew of different arcs are shown below:

Copyright © 2023 Maven Silicon

www.maven-silicon.com

VLSI Training Services

Setting standards in VLSI Design

The arrival time at different input pins are as follows:

a. What will be the arrival time and the output slew at the pin Z when Graph Based

Analysis (GBA) is performed for the setup check or late-mode check?

b. What will be the arrival time and the output slew at the pin Z when Path Based

Analysis (PBA) is performed for the setup check or late-mode check through the arc

B→Z?

3. Consider the following synchronous circuit. 6M

The following attributes are valid for the flip-flops FF1 and FF2: setup time=45

ps, hold time=10 ps, and CLK-to-Q delay=20 ps. The delay of each inverter is

50 ps. Ignore the wire delay.

Assume that the period of the clock is 1000 ps.

a. What is the setup slack at the timing end-point FF2/D?

b. What is the hold slack at the timing end-point FF2/D?

4. What is floor planning? Explain the different parameters w.r.t floor planning 4M

5. What is partitioning? What are the goals of floor planning? 4M

6. What are Macros? Explain the different types of Macros. 4M

7. What are the Sanity checks need to be done before and After CTS? 4M

8. What do you mean by logical mapping during logical synthesis? What kind of

violations (Setup/Hold) are solved during Synthesis? And Why 3M

9. What is SDC? Explain the following SDC command with an example. 5M

(i) Set_input_delay

(ii) Set_output_delay

(iii) Set_max_delay

(iv) Set_max_transition

Copyright © 2023 Maven Silicon

www.maven-silicon.com

VLSI Training Services

Setting standards in VLSI Design

10. What is slew, skew,latency,jitter and uncertainity? Mention how you are going to set

these values in the SDC file. 5M

11. What is signoff? Explain the signoff steps 5M

12. What is DMM? Explain the significance of DMM in Fusion Compiler tool 5M

13. Explain the Synthesis flow and What will be the synthesis result of the following

piece of Verilog code: 5M

Part – D (Basic Electronics, Networks and Aptitude) Marks: 10

1. For the following specifications, check the circuit for any violations & fix them if any. 4M

2. Calculate the output voltage for this circuit when V1 = 2.5 V and V2 = 2.25 V.

4M

3. A can lay railway track between two given stations in 16 days and B can do the same job in

12 days. With help of C, they did the job in 4 days only. Then, C alone can do the job in:2M

************ ALL THE BEST *********

Copyright © 2023 Maven Silicon

www.maven-silicon.com

You might also like

- MATH 10-3 Lesson 3 Rational ExpressionsDocument38 pagesMATH 10-3 Lesson 3 Rational ExpressionsRalph100% (1)

- Supafirefly 1Document8 pagesSupafirefly 1api-356919224No ratings yet

- FOS User Guide PDFDocument96 pagesFOS User Guide PDFadsrjmNo ratings yet

- Exercises Problems Answers Chapter 5Document5 pagesExercises Problems Answers Chapter 5A Sibiescu100% (1)

- Verilog Interview QuestionsDocument7 pagesVerilog Interview QuestionsVishal K SrivastavaNo ratings yet

- 2023-1509 TopSolid'Design TutorialDocument53 pages2023-1509 TopSolid'Design TutorialMáy TiệnNo ratings yet

- Specification 33 KV LineDocument18 pagesSpecification 33 KV LineSatyaprasad NimmakayalaNo ratings yet

- CCNP 350-401 Encor 28 Januari 2022Document98 pagesCCNP 350-401 Encor 28 Januari 2022Nurwan Reza Fachrur RoziNo ratings yet

- VLSI Interview QuestionsDocument7 pagesVLSI Interview QuestionsVlsi GuruNo ratings yet

- CCNA Questions July 2019Document294 pagesCCNA Questions July 2019Emmanuel Teixeira de SousaNo ratings yet

- Systemverilog - CodingDocument39 pagesSystemverilog - CodingV SharmaNo ratings yet

- EVE EVE48100 User ManualDocument29 pagesEVE EVE48100 User ManualHoàng HiếuNo ratings yet

- Final Test: Part - ADocument5 pagesFinal Test: Part - Akavya devulapalliNo ratings yet

- Be Winter 2022Document2 pagesBe Winter 2022kaushal.21beect008No ratings yet

- QuestionsDocument5 pagesQuestionsgirishdsk2002No ratings yet

- BIT103 Digital LogicDocument1 pageBIT103 Digital LogicBishalNo ratings yet

- Manual - Lab 2Document6 pagesManual - Lab 22017 Koh Guan TsinNo ratings yet

- Spos Lab ManualDocument63 pagesSpos Lab ManualishikaNo ratings yet

- Information TechnologyDocument7 pagesInformation TechnologyDEVANAND ANo ratings yet

- Advanced Digital VLSI Design (ECE 521) (Makeup) PDFDocument2 pagesAdvanced Digital VLSI Design (ECE 521) (Makeup) PDFRahul PinnamaneniNo ratings yet

- L-4rr-lI/CSE Date: 27/0312023: Section-ADocument35 pagesL-4rr-lI/CSE Date: 27/0312023: Section-AQuazi Hasnat IrfanNo ratings yet

- Midterm1 Soln Fall09 PDFDocument6 pagesMidterm1 Soln Fall09 PDFbsudheertecNo ratings yet

- Set 1Document3 pagesSet 1heisenberg1975.12No ratings yet

- Set 1Document3 pagesSet 1heisenberg1975.12No ratings yet

- Questions 4 1Document95 pagesQuestions 4 1Anik PaulNo ratings yet

- CSE 331 - Final - Assignment - v2Document5 pagesCSE 331 - Final - Assignment - v2S.M. Imam Jahed Hossain 1511500642No ratings yet

- 15ecsc704 576 Kle54-Ecsc704Document5 pages15ecsc704 576 Kle54-Ecsc704Aniket AmbekarNo ratings yet

- Lab No 2 (VLSI Design)Document4 pagesLab No 2 (VLSI Design)Zahid Ul HassanNo ratings yet

- Summer 2023Document2 pagesSummer 2023khushalee.chavadaNo ratings yet

- S, R Are All STD - LogicDocument7 pagesS, R Are All STD - LogicMuhammad Moin100% (1)

- MATH49111/69111: Scientific Computing: 26th October 2017Document29 pagesMATH49111/69111: Scientific Computing: 26th October 2017Pedro Luis CarroNo ratings yet

- DLP Lab ManualDocument72 pagesDLP Lab ManualPoorna chand Evuru100% (1)

- TMS320F28335 DSP Programming Using MATLAB Simulink Embedded Coder: Techniques and AdvancementsDocument7 pagesTMS320F28335 DSP Programming Using MATLAB Simulink Embedded Coder: Techniques and AdvancementsSaid MerengueNo ratings yet

- (Common To Cse, It, Ai&Ml, DS) : Computer Networ Web Technology Laboratory ManualDocument138 pages(Common To Cse, It, Ai&Ml, DS) : Computer Networ Web Technology Laboratory ManualchintuNo ratings yet

- VLSI DesignDocument7 pagesVLSI DesignVarun ThejNo ratings yet

- B2 Ece2003 50333 50077 50428Document2 pagesB2 Ece2003 50333 50077 50428NanduNo ratings yet

- Ccna Training Ccnav3 - New Questions 3Document38 pagesCcna Training Ccnav3 - New Questions 3Remi PaternackNo ratings yet

- MCS 012 Previous Year Question Papers by IgnouassignmentguruDocument96 pagesMCS 012 Previous Year Question Papers by IgnouassignmentguruMayank ChoudharyNo ratings yet

- CSE3035-Principles of Coud Computing Lab Assignment-4Document41 pagesCSE3035-Principles of Coud Computing Lab Assignment-4ShadowNo ratings yet

- VLSI Record 2022-23Document77 pagesVLSI Record 2022-23MANOJNo ratings yet

- RT 22022042017Document8 pagesRT 22022042017YasyrNo ratings yet

- JAMES College of Engineering and Technology JAMES College of Engineering and TechnologyDocument1 pageJAMES College of Engineering and Technology JAMES College of Engineering and TechnologyepregithaNo ratings yet

- 6th SEM EC Lab Manual (17EC67)Document79 pages6th SEM EC Lab Manual (17EC67)Swetha Rani MunirajuNo ratings yet

- VLSI Print SharadDocument48 pagesVLSI Print SharadSHARAD FADADUNo ratings yet

- Chapter 7 - Testbench VerificationDocument36 pagesChapter 7 - Testbench VerificationĐức NguyễnNo ratings yet

- Testing of Vlsi Circuits: Answer All Questions Each Question Carries 25 MarksDocument2 pagesTesting of Vlsi Circuits: Answer All Questions Each Question Carries 25 MarksAnonymous gwdxvOcoqNo ratings yet

- S.V. National Institute of Technology, Surat: EC306: Embedded SystemsDocument2 pagesS.V. National Institute of Technology, Surat: EC306: Embedded SystemsBittu GoswamiNo ratings yet

- CCNAquestions July 2019 PDFDocument294 pagesCCNAquestions July 2019 PDFAlbertoNo ratings yet

- Name: Student Id:: Difficulty: Easy LevelDocument11 pagesName: Student Id:: Difficulty: Easy LevelSyed Shahriar Zaman ShibleeyNo ratings yet

- Electrical Engineering Department Academic SessionDocument17 pagesElectrical Engineering Department Academic SessionShavitra 30No ratings yet

- In Semester (Individual) AssignmentDocument10 pagesIn Semester (Individual) AssignmentmuhammadNo ratings yet

- VL7301 Testing of VLSI CircuitsDocument8 pagesVL7301 Testing of VLSI Circuitsmanojece80100% (1)

- Advantage Pro Ccna Skill Assessment Test: Answer Any Five of The Following Questions: (5x10 50marks)Document6 pagesAdvantage Pro Ccna Skill Assessment Test: Answer Any Five of The Following Questions: (5x10 50marks)Madavan RajNo ratings yet

- 523 BA19 Ad 01Document5 pages523 BA19 Ad 01ramesh1926No ratings yet

- Chapter 9 - Testbench VerificationDocument36 pagesChapter 9 - Testbench VerificationPhạm Gia LongNo ratings yet

- 16ec250 21Document2 pages16ec250 21AswiniSamantrayNo ratings yet

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDocument3 pagesEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYANo ratings yet

- Ii Ece B I SemDocument52 pagesIi Ece B I SemElectronics & communication engineering AstcNo ratings yet

- TMS320F28335 DSP Programming Using MATLAB Simulink Embedded Coder: Techniques and AdvancementsDocument8 pagesTMS320F28335 DSP Programming Using MATLAB Simulink Embedded Coder: Techniques and AdvancementsSaid MerengueNo ratings yet

- Indian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Document4 pagesIndian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Utkarsh PatelNo ratings yet

- EC6302 Digital ElectronicsDocument12 pagesEC6302 Digital ElectronicsJabeen BanuNo ratings yet

- Part-ADocument16 pagesPart-AOmkar RaneNo ratings yet

- CCNA 200-125 V3.0 2018.4.17 Chinese DumpDocument164 pagesCCNA 200-125 V3.0 2018.4.17 Chinese DumpAmine BoubakeurNo ratings yet

- Question Bank For Mid-2 r13 (Vlsi) .Document6 pagesQuestion Bank For Mid-2 r13 (Vlsi) .rppvchNo ratings yet

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksFrom EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNo ratings yet

- Alinhamento+SuperStar+3900 3Document4 pagesAlinhamento+SuperStar+3900 3Robson Roberto InomataNo ratings yet

- 7650-8550-DS-500-6105 DoneDocument91 pages7650-8550-DS-500-6105 DoneKhan Akhtar HusainNo ratings yet

- Opps TaskDocument2 pagesOpps Taskvenkata akhilNo ratings yet

- Manual - Manitou 1740 PDocument5 pagesManual - Manitou 1740 PMichel GonçalvesNo ratings yet

- Ch2 Signals PDFDocument23 pagesCh2 Signals PDFChetna MalhotraNo ratings yet

- Chapter3 PDFDocument9 pagesChapter3 PDFAdithyan GowthamNo ratings yet

- ATF VI en FR Motul 19280 20221103Document6 pagesATF VI en FR Motul 19280 20221103larconeNo ratings yet

- HHE-VL-Recip-Compressor-Flyer-June-2021-pdf - Original FileDocument2 pagesHHE-VL-Recip-Compressor-Flyer-June-2021-pdf - Original Fileaatishsehgal94No ratings yet

- ps242 Smoke DetectorDocument2 pagesps242 Smoke DetectorrafaelNo ratings yet

- Expt 6 PresentationDocument27 pagesExpt 6 PresentationTj DacalanioNo ratings yet

- Body Mass Index - Wikipedia, The Free EncyclopediaDocument10 pagesBody Mass Index - Wikipedia, The Free EncyclopediaRupam DasNo ratings yet

- Nonlintools: GUI Tool For Analysis and Design of Nonlinear Control SystemDocument4 pagesNonlintools: GUI Tool For Analysis and Design of Nonlinear Control SystemBayeNo ratings yet

- Introducing The 3L Small Form FactorDocument15 pagesIntroducing The 3L Small Form FactorzdjulicgmailcomNo ratings yet

- Export SocialDocument45 pagesExport SocialM-IENTIST GamingNo ratings yet

- High Precision Spectroradiometer Integrating Sphere SystemDocument11 pagesHigh Precision Spectroradiometer Integrating Sphere SystemLISUN GROUPNo ratings yet

- Service ManualDocument144 pagesService ManualMariusBelecciuNo ratings yet

- MST Quiz 2 AnswersDocument4 pagesMST Quiz 2 AnswersWilleyNo ratings yet

- Excel Chart Trendline FormulasDocument3 pagesExcel Chart Trendline FormulasSZaungg NauuNo ratings yet

- Empowerment Tech LessonsDocument34 pagesEmpowerment Tech LessonsAlyanna De LeonNo ratings yet

- Building PDF in Rails Using Prawn LibraryDocument5 pagesBuilding PDF in Rails Using Prawn LibrarySandip RansingNo ratings yet

- Unit 1Document67 pagesUnit 1sophieee19No ratings yet

- Drilling of Composite MaterialsDocument17 pagesDrilling of Composite Materialsrinu248No ratings yet

- Music Theory Sem 2 Rbu Class 4Document1 pageMusic Theory Sem 2 Rbu Class 4Awtar singhNo ratings yet