Professional Documents

Culture Documents

Architecture of 8085 Microprocessor

Architecture of 8085 Microprocessor

Uploaded by

Snehardra0 ratings0% found this document useful (0 votes)

6 views22 pagesOriginal Title

Architecture of 8085 microprocessor

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

6 views22 pagesArchitecture of 8085 Microprocessor

Architecture of 8085 Microprocessor

Uploaded by

SnehardraCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 22

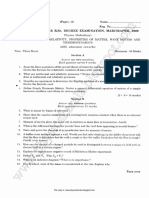

rr CT

CHAPTER

Architecture and Organization of

Microprocessor

INTRODUCTION

‘A microprocessor is a semiconductor chip designed by using VLSI technology. It implements

the central processing unit of a microcomputer. It consists of an_arithmetic_and logic unit,

register unit and control unit. These three units are fabricated on a single chip. The

microprocessors aré generally characterized by speed, word length, architecture and instruction

set.

In this chapter we will study architecture and organization of microprocessor,

microprocessor operations, internal architecture of a microprocessor, internal architecture of

8085, 8085 pin description, 8085 functional description, demultiplexing of buses, generation of

control signals and how a program is executed.

3.1. MICROCOMPUTER SYSTEM

As the technology moved from SSI to VLSI, the face of the computer changed. Initially,

computers were built with discrete logic gates. As more and more logic circuits were built on

one chip using LSI technology, it became possible to build the whole CPU with its related

timing function on a single chip. The central processing unit of a digital computer, built into

a single IC is called microprocessor unit (MPU). A simple example of a microcomputer is

Shown in Figure 3.1. The various components of this system are:

35

36 + Microprocessor 8085 and Its Interfacing

Tapat =

aapeer| 4 6 s,

ALU ney ‘System bus

AWM

Control unit ROM

Figure 3.1 Microcomputer system.

3.1.1 Arithmetic and Logic Unit

kn this area of the microprocessor the computing functions are performed on the ee as atu

performs arithmetic operations such as addition and subtraction and logic operations 5

AND, OR and XOR results are stored in the registers or in memory unit or send to output unit.

3.1.2 Register Unit

This area of the microprocessor consists of various registers. The registers are used for

temporary storage of data during execution of a Program. Some of the registers are accessible

to the users through various instructions

3.1.3 Control Unit

The control unit provides necessary timing and control signals to all the operations in the

microprocessor and peripherals, including memory.

3.1.5 System Bus -

‘The system bus is a communication path between the microprocessoy

nothing but a group of wires that carries data in the form of bits,

3.2 MICROPROCESSOR OPERATIONS

Microprocessor is a complex IC of sequential circuits. It is a

designed with registers, flip-flops and timing elements. It hac

‘manipulate data and communicate with peripherals. The p

Architecture and Organization of Microprocessor + 37

communication with peripherals is determined by the logic design or the microprocessor, the

logic design is called architecture.

All of the operations of the microprocessor can be classified into one of three types

1. Microprocessor initiated operations

2. Internal operations

3. Peripheral initiated operations

3.2.1. Microprocessor Initiated Operations

These are the operations which are initiated by the microprocessor itself and the peripheral

devices will execute these operations. These are usually one of the following operations:

1, Memory read: Reads data from memory.

2. Memory write: Writes data into the memory.

3. IOR: Accepts data from input devices.

4. IOW: Sends data to output devices.

All these operations are part of the communication process between microprocessor and

Peripheral devices or memory. To perform these communication operations, MPU executes the

following steps:

1. Identify the address of memory location or the peripheral device.

2. Provide timing or synchronization signals.

3. Transfer the data.

The microprocessor performs the given three functions through the communication lines

called system bus (bunch of wires). As there are three types of information that are

communicated, hence there are three types of buses. These buses are:

Address bus: It carries the address of a memory location or I/O devices that the MPU wants

to access, It is a unidirectional bus (from MPU to peripheral) generally denoted by Ag to Aye.

In MP 8085, it is 16-bit wide.

Data bus: It is used to transfer data between the processor and memory and I/O devices. It

's bi-directional in nature, In microprocessor 8085, there are 8 data lines denoted by Dp to Dy.

Control bus: It is used to carry control signals between MPU and various devices connected

{0 it.I also carries synchronization and timing signals. The bus is Somewhat a confusing term

for it. In fact, these are individual lines that provide signals to the devices connected to the

microprocessor.

Figure 3.2 shows the bus system of 8085.

3.22 Internal Data Operations

These are the operations which are internally performed by the microprocessor. The internal

Architecture of microprocessor determines how and what operations can be performed with the

‘ata. The internal operations performed by the microprocessor are classified into five groups:

38 + Microprocessor 8085 and Its Interfacing

Input unit Output unit

¥ ¥

ons] [| 4 | iP

Register ‘Address bus

ALU | ney

’

Controt unit aon aa

MPU 8085

Figure 3.2 Bus system of 8085.

1. Store 8-bit data.

2. Perform arithmetic and logic operations.

3. Test for the conditions.

4. Sequence the execution of instructions.

5. Store data temporarily during the execution in the defined R/W memory locations called

the stack.

To perform these five operations we require registers, ALU and control logic and path for

communication, i.e., bus system

First operation

To store 8-bit data, microprocessor has the register unit.

Register unit: Microprocessor 8085 has six 8-bit general purpose data registers. During

Program execution, these registers are used to store 8- or 16-bit data. These registers are

identified as B, C, D, E, H and L. If during some operation microprocessor has to deal with 16-

bit data, then these registers can be paired. This register pairing is fixed, ie, register B will pat

with register C, D with E and H with L. The higher byte of the 16-bit data will go to either B,

D and H registers, whereas lower byte will go to C, E and L.

These registers are programmable, i-e., the user can use them to load, copy and move data

from the registers by using instructions such as MOV B, C. These registers can be considered

as memory locations which are situated inside the microprocessor and are referred by alphabets

for the user’s convenience. Some microprocessors do not have these registers so they use

memory locations for this purpose.

Second operation

To perform arithmetic and logic operations, micro

A lator A. processor has ALU and a register called

ccumulator A.

Accumulator: The accumulator is an 8-bit general

; Purpose register that is part of ALU. This

register is used to store 8-bit data to perform arith 8 at is par

metic and logical operations. Accumulato!

Architecture and Organization of Microprocessor + 39

participates in all the arithmetic and logical operations, After the operation the result is stored

in the accumulator, Accumulator is the only register which communicates with IO. Accumulator

is also identified as register A.

Third operation

To test the condition, if any, microprocessor has another 8-

it register called the flag register

Flag register: The flag register is an 8-bit register. These 8-bits of the register are

independent bits. Out of these 8-bits, five are used to represent five different data conditions.

‘These are:

Carry flag If after an arithmetic operation the result in the accumulator is greater than 8-bits,

then the carry flag is set, ie., CY = 1, otherwise it is 0.

Zero flag If after an arithmetic operation the result in the accumulator is zero, then zero flag

is set, ie., Z = 1, otherwise it is 0.

‘Sign flag If after an arithmetic operation the MSB of the result in the accumulator is 1, then

sign flag is set, iLe., S = 1, otherwise it is 0.

Parity flag If after an arithmetic operation the result contains even number of 1s, then parity

flag is set, ic., P = 1, otherwise it is 0.

Auxiliary flag This status flag is set if there is a carry when there is a carry from bits 3 to 4.

‘These five flip-flops or status flags are set or reset according to the result of operation. The

microprocessor uses them to perform the testing or setting for data conditions.

Fourth operation

To perform this operation, microprocessor 8085 has another register called program counter.

Program counter: This is a 16-bit register that deals with the fourth operation of the list, i.e.,

sequencing the execution of instructions. This register is a memory pointer. The function of the

Program counter is to point the memory address from which the next byte is to be fetched,

When one bit is being fetched the contents of the program counter is increased by 1 to point

the next memory location. Memory locations have 16-bit address that is why this register is of

16 bit.

Fifth operation

To perform this operation of the microprocessor internal operations, microprocessor 8085 has

another register called stack pointer (SP)

Stack pointer: The stack pointer is also a 16-bit register used as a memory pointer. It points

to a memory location in R/W memory, called the stack. The beginning of the stack is defined

by loading a 16-bit address in the stack pointer.

3.2.3 Peripheral or Externally Initiated Operations

External devices can initiate the following operations, for which individual pins on the

microprocessor chip are assigned. These operations are:

40 + Microprocessor 8085 and Its Interfacing

Reset: When reset pin is activated all internal operations are stopped and the program counter

is reset to 0000. Program execution again begins from zero memory address.

Interrupt: The microprocessor’s current operation is suspended and the microprocessor

executes some emergency task called Interrupt Service Routine (ISR). After the execution of

the ISR, the microprocessor returns to its previous operations and continues.

Ready: The 8085 has a pin called READY. This pin is used by external devices to synchronize

the speed of microprocessor with the slower peripherals. As long as the READY pin is low, the

microprocessor will be in a ‘wait’ state.

Hold: The 8085 has a pin called HOLD. This pin is used by external devices to gain control

of the buses. When the HOLD signal is activated by an external device, the 8085 suspend

current execution and stops using the buses. This would allow external devices to control the

information on the buses, such as, direct memory access (DMA).

3.3. 8085 FUNCTIONAL DESCRIPTION

The 8085A is a complete 8-bit parallel central processor. It requires a single +5 volt supply. Its

basic clock speed is 3 MHz, thus, improving on the present 8080's performance with higher

system speed. Also it is designed to fit into a minimum system of three ICs: The CPU, a RAM/

10 and a ROM or PROMAIO chip.

The 8085A uses a multiplexed data bus. The address is split between the higher 8-bit

address bus and the lower 8-bit address/data bus. During the first cycle the address is sent out.

‘The lower 8-bits are latched into the peripherals by the address latch enable (ALE). During the

rest of the machine cycle, the data bus is used for memory or I/O data.

The 8085A provides RD", WR and IO/M™ signals for bus control. An interrupt

acknowledge signal (INTA) is also provided. Hold, ready and all interrupts are synchronized.

The 8085A also provides serial input data (SID) and serial output data (SOD) lines for simple

serial interface.

In addition to these features, the 8085A has three maskable, restart interrupts and one non-

maskable trap interrupt. The 8085A provides RD", WR” and IO/M” signals for bus control.

Status information is directly available from the 8085A. ALE serves as a status strobe. The

status is partially encoded and provides the user with advanced timing of the type of bus transfer

that is being done. IO/M cycle status signal is provided directly. Decoded Sp, S; carries the

following status information: HALT, WRITE, READ, FETCH S; that can be interpreted as R/

W in all bus transfers. In the 8085A the 8 LSB of address are multiplexed with the data instead

of status. The ALE line is used as a strobe to enter the lower half of the address into the memory

or peripheral address latch. This also frees extra pins for expanded interrupt capability.

The 8085A has 5 interrupt inputs: INTR, RST5.5, RST6.5, RST7.5, and TRAP. Each of the

three RESTART inputs, RSTS.5, RST6.5 and RST7.5, has a programmable mask. TRAP is also

a RESTART interrupt except it is non-maskable. The three RESTART interrupts cause the

internal execution of RST if the interrupts are enabled and if the interrupt mask is not set. The

non-maskable TRAP causes the internal execution of a RST independent of the state of the

interrupt enable or masks. The interrupts are arranged in a fixed priority that determines which

Architecture and Organization of Microprocessor + 41

interrupt is to be recognized if more than one is pending as follows: TRAP highest priority,

RST7.5, RST6.5, RSTS.5; INTR lowest priority This priority scheme does not take into account

the priority of a routine that was started by a higher priority interrupt. RSTS.5 can interrupt a

RST7.5 routine if the interrupts were re-enabled before the end of the RST7.5 routine. The

TRAP interrupt is useful for catastrophic errors such as power failure or bus error. The TRAP

input is recognized just as any other interrupt but has the highest priority. It is not affected by

any flag or mask. The TRAP input is both edge and level sensitive.

3.4 INTERNAL ARCHITECTURE OF 8085

The internal architecture of microprocessor 8085 can be divided into five parts as follows:

1. Register unit

2. Control unit

3. Arithmetic and logical unit

4, Interrupt unit

5. Serial 10 unit

These five units consist of other internal parts. The following section gives a detailed over-

view of these parts.

3.4.1 Register Unit

As shown in Figure 3.3, the register unit consists of six general purpose data registers B, C, D,

E, H and L, two internal registers W and Z, two 16-bit address registers PC and SP, one

increment/decrement counter register and one MUX/DEMUX.

‘Accumulator Av Flag register

Bo Se

Dey Ew

He Ley

Stack pointer (SP)j5

Pros counter (PC);

Figure 3.3 Registers of 8085.

General purpose data register

The 8085/8080A has six general-purpose data registers to store 8-bit data. These registers are

named as B, C, D, E, H, and L as shown in Figure 3.4. The user can use these registers to store

of copy a data temporarily during the execution of a program by using data transfer instructions.

Though these registers are of 8 bits but whenever the microprocessor has to harldle 16-bit data,

these registers can be combined as register pairs—BC, DE, and HL.

Apart from these six general purpose data registers, the 8085 microprocessor also has

-bit internal data registers. These registers are named as W and Z. These registers are only

ternal operation of the microprocessor and not available to the user. Microprocessor uses

these registers internally for example in the case of CALL and XCHG instructions

two 8.

for in

“$808 Jo eunjosyyoue jeuss,U)

42. + Microprocessor 8085 and Its Interfacing

ve aunBiy

103 ano

aR He 4as3u vaIH _WIOI 's5 % av ay =

4 ‘e T 4 uasay fee t 3 t te f Aare

- + t tt

[Denna eveasseippy Jeyng Sselppy yesoy vwa ‘smeig you09 NaD 2

ori Je—'x

wun jonuoo pue Bulwi,

TWHIeT Sseuppe LI

queweio@p Tapoous

Quewsesouy @j049,

dS J2UIod yoRIS: Ey »| suIueW -|

3 pue a

[Oa 491uN0o wesBora] * | | aoe

a Hs uononsisuy

3 a |3| Lt

ie

ts fi art

(6a,

a vononasul [| wee

[Lienuoo tenes} jonues \dnvveWUL

Pett

| wats | sedsu

ais dos

LVANI yin}

s91se

vel

Architecture and Organization of Microprocessor + 43,

Program counter (PC)

This 16-bit register deals with sequencing the execution of instructior 8 This Tegister is a

memory pointer. Memory locations have 16-bit addresses which is why this is a 16-bit register.

‘The microprocessor uses this register to sequence the execution of the instructions. The function

of the program counter is to point to the memory address from which the next byte is to be

fetched. When a byte (machine code) is being fetched, the program counter is incremented by

one to point to the next memory location.

Stack pointer (SP)

The stack pointer is also a 16-bit register used as a memory pointer. It points to a memory

location in R/W memory, called the stack. The beginning of the stack is defined by loading 16-

bit address in the stack pointer. The stack concept is explained in the chapter Stack and

Subroutines.

Increment/Decrement counter

This counter register is used to increment or decrement the contents of the various registers

available in the register unit, For instance, everytime microprocessor accesses a memory, its PC

register is incremented.

MUX/DEMUX unit

This unit is used to select a register out of all the available registers. This unit (shown in

Figure 3.5) behaves as a MUX when data is going from the register to the internal data bus.

It behaves as a DEMUX when data is coming to a register from the internal data bus of the

microprocessor. The register select will behave as the function selection lines of the MUX/

DEMUX.

To registers

From registers

NeErxrmooo

xce

To internal data bus

From internal data bus

Neer rmooga

a

Register

select

Register

select

Figure 3.5 Multiplexer unit

4 + Microprocessor 8085 and Its Interfacing

Address buffer register and data/address buffer register

‘These registers hold the address/data, received from PCyinternal data bus and then loads the

external address and data buses. These registers actually behave as the buffer stage between the

microprocessor and external system buses.

3.4.2. Control Unit

The control unit generates signals within microprocessor to carry out the instruction, which has

been decoded. In reality it causes certain connections between blocks of the microprocessor to

be opened or closed, so that the data goes where it is required and the ALU operations occur,

The control unit itself consists of three parts; the instructions register (IR), instruction decoder

and machine cycle encoder and control and timing unit.

Instruction register

This register holds the machine code of the instruction. When microprocessor executes a

program it reads the opcode from the memory, this opcode is stored in the instruction register.

Instruction decoder and machine cycle encoder

The IR sends the machine code to this unit. This unit, as its name suggests, decodes the opcode

and finds out what is to be done in response of the coming opcode and how many machine

cycles are required to execute this instruction.

Control and timing unit

The control unit generates signals within microprocessor to carry out the instruction, which has

been decoded. In reality, it causes certain connections between blocks of the microprocessor to

be opened or closed, so that the data goes where it is required and the ALU operations occur.

3.4.3 Arithmetic and Logical Unit

‘The ALU performs the actual numerical and logical operation such as ‘add’, ‘subtract’, ‘AND’,

‘OR’, ete. ALU uses data from memory and from accumulator to perform the arithmetic

operations and always stores the result of the operation in accumulator. The ALU consists of

accumulator, flag register and temporary register

Accumulator

The accumulator is an 8-bit register that is a part of arithmetic/logic unit (ALU). This register

is used to store 8-bit data and perform arithmetical and logical operations. The result of an

operation is stored in the accumulator. The accumulator is also identified as register A.

Flags

The ALU includes five flip-flops, which are set or reset after an operation according to the data

conditions of the result in the accumulator and other registers. They are called zero (Z), carry

(CY), sign (S), parity (P) and auxiliary carry (AC) flags; their bit positions in the flag register

are shown in Figure 3.6. The microprocessor uses these flags to set and test data conditions. For

Architecture and Organization of Microprocessor » 45,

example, after an addition of two numbers, if the sum in the accumulator is larger than 8-bits,

the flip-flop indicates a carry—called the carry flag (CY}—to set to one. When an arithmetic

operation results in zero, the flip-flop called the zero (Z) flag is set to one.

Figure 3.6 shows this 8-bit flag register, adjacent to the accumulator.

D, | Ds Ds Dy D; D> Di Do

Ss Zz x AC at P x cy

X = Not specified

Figure 3.6 Format of the flag register.

The flags are stored in the 8-bit register so that the programmer can examine these flags

(data conditions) by accessing the register through an instruction. These flags have critical

importance in the decision-making process of the microprocessor. The conditions (set or reset)

of the flags are tested through the software instructions. For instance, the instruction JC (jump

on carry) is implemented to change the sequence of a program when CY flag is set. The

thorough understanding of flag is essential in writing assembly language programs.

Z (Zero) flag: This flag indicates whether the result of a mathematical or logical operation

is zero or not. If the result of the current operation is zero, then this flag will be set, otherwise

reset.

CY (Carry) flag: This flag indicates whether, during an addition or subtraction operation,

carry or borrow is generated or not, if generated then this flag bit will be set. (This flag may

also be set before a mathematical operation as an extra operand to certain instructions).

AC (Auxiliary carry) flag: It shows carry propagation from Ds position to Dg position. To

understand it better, consider Figure 3.7.

De Ds Dy Ds D, D Do

1 0 0 0 1 1 0 0

0 1 0 1 0 1 1

1 0 Ley Fi 0 1 1 1

Figure 3.7 Auxiliary carry flag,

Here, a carry generates from Ds bit position and propagates to the D, position. This carry

is called auxiliary carry. This flag is never used for setting or testing a condition.

S (Sign) flag: Sign flag indicates whether the result of a mathematical operation is negative

or positive. If the result is positive, then this flag will reset and if the result is negative this flag

will be set. This bit, in fact, is a replica of the Dy bit.

P (Parity) flag: Parity is the number of 1’s in a number. If the number of 1’s in a number

seven, then that number is known as even parity number. If the number of 1’s in a number

'S odd then that number is known as an odd parity number. This flag indicates whether the

Current result is of even parity (1) or of odd parity (0).

46 + Microprocessor 8085 and Its Interfacing

3.5 8085 SYSTEM BUS

Typical system uses a number of buses which are nothing but collection of wires, which

transmit binary numbers, one bit per wire. A typical microprocessor communicates with

memory and other devices (input and output) using three buses: address bus, data bus ang

control bus.

Address bus

Address bus is a unidirectional group of lines, i.e., numbers only sent from microprocessor to

memory, not the other way. Microprocessor 8085 has 16 address lines, one wire for each bit,

therefore, 16-bits = 16 wires. With the help of 16-bits we can generate 2'° combinations, if one

combination is allotted to a single memory location as an address, that means, 64 K memory

locations can be addressed by 8085 microprocessor.

Data bus

Data bus carries ‘data’, in binary form, between microprocessor and other external units, such

as memory. Data bus is used to transmit “data”, i.e., information, results of arithmetic, etc,

between memory and the microprocessor. Data bus is bi-directional. Size of the data bus

determines what arithmetic can be done. If it is only 8-bits wide, then the largest number is

11111111 (255 in decimal). Therefore, larger number has to be broken down into chunks of

255. This slows the microprocessor. Data bus also carries instructions from memory to the

microprocessor. Size of the bus, therefore, limits the number of possible instructions to 256,

each specified by a separate number. The data bus in 8085 typically consists of 8 wires.

Control bus

Control bus consists of various lines which have specific functions for coordinating and

controlling microprocessor operations, e.g. read line and write line. These lines control whether

memory is being ‘written to’ (data stored in memory) or ‘read from’ (data taken out of

memory). Control bus may also include clock line(s) for timing/synchronizing, interrupts, reset,

etc. The control bus carries control signals partly unidirectional, partly bi-directional. Control

signals are things like “read or write”. This tells the memory that we are reading from a

location, specified on the address bus, or writing to a specified location. Various other control

signals also float on these lines to control and coordinate the operation of the system.

3.6 8085 PIN DESCRIPTION

Microprocessor 8085 is a 40-pin IC which operates on +5'V power supply and 3 MHz

frequency. These 40 pins are divided into six groups according to their functions. These groups

are:

1, Frequency and power supply signals

2. Higher order address bus

3. Multiplexed address/data bus

4. Control and status signals

ee

Architecture and Organization of Microprocessor + 47

5. Serial 10 signals

6. Externally or peripheral initiated signals.

The pin configuration of microprocessor 8085 is shown in Figure 3.8.

Veo Vos

x1 40 Ve. Aa

xe 99 FHola sop «|

Reset out] 3 38 CHLDA Ap

soot] 4 87 [CLK (ouT)

sioc]s 36D RESET in’ AST75 ———+|

rape ssfaReady ——-RST8s ——*] K-aDEmDE>

Rst7.5C|7 34 Dione

RST6.5C]8 33s, WB

RstssCl9 = 8 a2 RD NT, 8085 fF

radio «=O at we re

wad 8 soa HOLD ——+| 7

anti 5 ahs, oat i

a,C13 28D Ay Patan OM

ADC] 14 27D Ag RESET in. + t——> s

a0.C]15 26 Ay Reset out ~——

AD, 16 25 Ay coeee. |

ap,C117 240A, aif

AD,C] 18 23 Aw

eee ee TT

Vys] 20 21 FA, X,X, CLK out

Figure 3.8 Pin configuration of 8085.

3.6.1. Group 1: Power Supply and Frequency Signals

X, Xz (Input)

These are the two input lines across which a Crystal or R/C oscillator circuit is connected to

provide the required clock frequency to the microprocessor. The frequency generated by the

oscillator is divided by 2 to give the internal operating frequency of the microprocessor.

The input frequency is divided by 2 because the frequency is applied to the system through a

T flip-flop which divides the incoming frequency by 2 (as shown in Figure 3.9).

Vee

+5 volt supply.

Ves

Ground reference.

‘CLK OUT

Xe

Figure 3.9 Internal clock

3.6.2 Group 2: Higher Order Address Bus (Output) (Ag-A\s)

Instead of having 24 pins for address and data lines, 8085 has only 16 pins. Out of the 16 ping

8 pins are used to carry the higher order address and the other 8 pins are multiplexed to carry

the address as well as the data. This multiplexing is done to keep the number of pin as minimum

as possible. The most significant 8 bits of the memory address or the 8 bits of the I/O address

is carried by these lines. These lines are tri-stated during Hold and Halt modes.

3.6.3 Group 3: Multiplexed Address/Data Bus (AD,-AD;)

‘The 808SA uses a multiplexed data bus. These lines are time multiplexed with the lower 8-lines

of the address bus. Lower 8-bits of the memory address or I/O address appear on the bus during

the T, state of a machine cycle. It then becomes the data bus during the second and the third

clock cycles. These lines are tristated during Hold and Halt modes.

3.6.4 Group 4: Control and Status Signal

ALE (Address latch enable) (output)

ALE ‘as its name suggest, enables the address latch to store the address during the

demultiplexing operation. It occurs during the first T state of every machine cycle, Whenever

microprocessor sends a valid address on the multiplexed lines, it also make the ALE signal high.

ALE can also be used to strobe the status information. ALE is never tristated,

RD” (read) (output)

Read is an active low output control signal. When this signal is low, it indicates that the

microprocessor wants to read a data either from memory or IO device. Microprocessor activates

this signal during the T> state of the machine cycle as in this T state, the data bus is ready to

carry the data. The read signal is tristated during Hold and Halt modes,

WR™ (write) (output)

_=_=__-_- i

Architecture and Organization of Microprocessor + 49

10/M~ (output)

‘The Read and Write signals indicates that the microprocessor wants to read or write @ data but

do not specify from where this read or write operation will take place. This is indicated by the

1O/M signal. When this signal is low, it means a read or write operation will take place

from/to memory. When this signal is high, it means the operation is with reference to 10. This

signal is tristated during Hold and Halt modes.

So S; (status signal) (output)

These are the two data bus status signals. The four combinations of these signals give the

information of what the microprocessor is doing or the encoded status of the bus cycle

(Figure 3.10).

5: Si Operation

0 0 Halt

0 1 Write

1 0 Read

1 1 Fetch

Figure 3.10 Encoding of status signal

S, can be used as an advanced R/W status.

3.6.5 Group 5: Serial 10 Signal

SID (input)

Serial input data line. This line is used in serial data communication. Through this pin, the serial

data is received by the processor. The data on this line is loaded into accumulator bit 7,

whenever a RIM instruction is executed. Figure 3.11 shows the SID operation.

siD

+

D, Ds 0; D, D, D, Dy Dy

‘Accumulator

Figure 3.11 SID operation.

SOD (output)

Serial output data line. This line is used in serial data communication. Through this pin, the

serial data is transmitted by the processor. The output SOD is set or reset as specified by. the

SIM instruction. Figure 3.12 shows the SOD operation.

50 + Microprocessor 8085 and

sop

t

0, Dp 0; 0, D, DB, dD, Dy

Accumulator

Figure 312 SOD operation

3.6.6 Group 6: Externally or Peripheral Initiated Signals

TRAP (Input)

Trap is a nonmaskable interrupt which have the highest priority. It is recognized at the same

time as INTR. This interrupt cannot be masked or disabled. This is a vectored interrupt. It is

edge as well as level triggered

RST 5.5, RST 6.5, RST 7.5: RESTART interrupt (inputs)

These three inputs have the same timing as INTR except they cause an internal RESTART to

be automatically inserted. These interrupts are maskable. The mask can be set to any of these

interrupts by SIM instruction

RST7.S has the highest priority and it is edge triggered.

RST6.5 is level triggered

RSTS.5 has the lowest priority and it is edge triggered.

The priority of these interrupts is ordered as shown. These interrupts have a higher priority

than the INTR.

INTR (interrupt request) (input)

INTR is used as a general purpose interrupt. It is sampled only during the next to the last clock

cycle of an instruction cycle. When itis active, the Program Counter (PC) will stop incremented

INTA™ (interrupt acknowledge) (output)

This signal is generated by microprocessor in response to the INTR. When microprocessor

accepts the INTR, it executes an INTA machine cycle. This cycle is exactly same as that of read

cycle except that instead of RD” signal, microprocessor sends the INTA” in the T, and T; state.

It can be used to activate 8259 Interrupt chip or some other interrupt port.

Pee ee ee ee a,

Architecture and Organization of Microprocessor + 51

READY (input) : -

This signal is used to synchronize the slower peripherals with microprocessor. If sae ie high

during a read or write cycle, it indicates that the memory or peripheral is ready i send or

receive data. If ‘Ready’ is low, the CPU will wait for ‘Ready’ to go high before completing the

read or write cycle. For example, if microprocessor is interfaced with a slower output peripheral

device, the device will send logic 1 on the READY pin. On receiving the READY signal,

microprocessor will release the data and then enter into the wait state till the next time

microprocessor receive the signal on READY.

HOLD (hold request) (input)

HOLD is bus request from a competent bus master. Whenever a competent bus master like

DMAC (Direct memory access controller) wants to transfer data between memory and the IO,

it sends a request on the HOLD pin of the microprocessor. On receiving the Hold request signal,

the microprocessor suspends its current operation and relinquishes the buses as soon as the

completion of the current machine cycle, Internal processing can continue. The processor

regains the control of the buses when the Hold request is dropped by the DMAC. When the

Hold is acknowledged, the Address, Data, RD", WR”, and IO/M" lines are tristated. This signal

is polled by the microprocessor in the last T state of every machine cycle. Figure 3.13 shows

the HOLD operation.

EDA Other

master

8 Data bus

Q pit DMA

8 ‘Address bus controller

HOLD

Figure 3.13 HOLD operation.

HLDA: HOLD acknowledge (output)

On receiving the HOLD request, the microprocessor completes the current machine cycle and

then suspends its operation, release the buses and sends a HOLD acknowledge signal to the

DMAC. HLDA goes low after the Hold request is dropped. The microprocessor takes the buses

one half clock cycle after HLDA goes low.

RESET” IN (input)

This signal is used to reset the processor. When microprocessor receives a signal on this pin

it clears the Program Counter and resets the Interrupt Enable and HLDA Flip-flop. Except the

Instruction register, all the general purpose data registers and the flag register remain unaffected

by the Reset signal. The microprocessor is held in the reset condition as long as Reset is applied.

7

52

* Microprocessor 8085 and Its Interfacing

RESET our (output)

This signal is used by the microprocessor to reset its ee eee It can be used as ic

system RESET. The signal is synchronized to the processor clock.

CLK (output)

Clock output is used as a system clock when a crystal or R/C network is used as an input tp

the CPU. The period of CLK is twice the Xj, X> input period.

3.7 DEMULTIPLEXING OF AD,-AD,

12 8085 the higher order address lines are dedicated to carry the higher order address but the

lower order address lies are multiplexed with data bus. This multiplexing is done to keep the

mgeeet Of Pins as minimum as possible. These lines are demultiplexed to generate the

independent address as well as data bus nee

76 ge ‘tis demultiplexing first we see how long multiplexed addressdata is available on

qr APr. During T; state of every machine cycle AD,-ADy lines carry the address part. In

this Tr-state ALE signal is also high to indicate address on these lines. Afte. Tr-state

mmiropeecessor 8085 will remove the address contents from AD,_AD, lines and ae hae, lines

anion Oat Clock cycle onwards. The demultiplexing of these lines is done by using

ici evn in Figure 3.14) along with the ALE signal as shown in Figure 3.12

‘is hig gidress signals will get latched in 8-bit latch and the output of latch will

ide AGA; ade ntents. When ALE is low for data, it will disable the latch from

sonnei @Do- AD, lines and the same lines can be used as data lines.

Here, inthe'eircui

ie D-FF(Flip Flop) are triggered by the ALE signal. When these FFs

are triggered Me pu tut. becomes equal to the input which is nothing but address at this

moment. Now ‘©vengif the ALE signal goes down these FF retain the address component

a there output for. peripheral addressing. The tri-stated butte are used just to increase the

driving capabilitia buses.

Io,

00,

[—>D0,

+00,

[—>o,

+0,

Strobe -

(sTB) OE Output enable

Figure 3.14 Pin diagram of D-latch 8282.

Architecture and Organization of Microprocessor » 53

74LS373,

AD {0 0 > a

FF

pe{ClK

AD, DQ +A,

belcux

AD, >

ADy: >

AD, >

AD,- >

ADs: >

AD, >a 2 A

p>cik

ALE =

Do

b,

Figure 3.15 Demultiplexing of ADy-AD;.

3.8 GENERATION OF CONTROL SIGNALS

Microprocessor 8085 does not give the four control signals, i.c., IOR’, TOW" MEMR’ and

MEMW-’ directly. These four control signals are generated from the three control signals RD”,

WR° and IO/M” as shown in Figure 3.16.

ao2oo

lor

RD-

wr

Figure 3.16 Generation of control signals.

54.

Microprocessor 8085 and Its Intertacing

From De-Morgan theorem, a bubbled NAND gate is equal to an OR gate so here in this

logic circuit the bubbled NAND gates can also be replaced by OR gates.

Figure 3.17 shows the complete diagram of a microprocessor 8085 with its control signals

and demultiplexed bus system.

Asse AisAg

ALE

AD,-ADs| Ary

DD,

MEMR™

MEMW-

tor”

tow

Figure 3.17 Microprocessor system

3.9 HOW A PROGRAM IS EXECUTED

Intel Microprocessors work on the stored program concept, i.e., instructions or programs are

stored in memory. To execute a program, microprocessor fetches the instructions one by one

and executes them in the same sequence and then executes them. The flow of signal for the

execution of a stored instruction is shown in Figure 3.18. Microprocessor performs the

following steps to execute the stored program.

1. First the Program counter loads the 16-bit memory address of the instruction on the

address bus.

2. The Control unit sends the MEMR’ signal to tell the memory that the microprocessor

wants to read the memory and thereby memory enable the addressed memory location.

The addressed memory location then placed the 8-bit instruction code on the data bus

and transferred this code to the instruction register (IR)

Architecture and Organization of Microprocessor + 55

8085 uh

Microprocessor Data bus

Internal data Bus a

Flag %

lAccumulator| | fip- |} | Instruction |. Bi C) 2005 [“orooTT TT

flops|| | decoder [*]0 E

H| L

‘Arithmetic logic unit SP.

aye PC.

Control Lt

‘unit 005.

Address bu t ‘| :

Control signal =

rol signals — E

Figure 3.18 Flow of signal for the execution of a stored instruction.

4, The opcode is then transferred to the instruction decoder and machine cycle encoder

from instruction register. The instruction decoder and machine cycle encoder decoded

the meaning of the opcode and the number of machine cycles required to execute the

complete instruction.

5. The decoded opcode information is sent to the control unit so that the control unit can

generate the appropriate control signal to execute the instruction.

EXERCISES

3.1 Give the order of priority of the following instructions with reason.

(a) HOLD (b) RESET (¢) INTERRUPT

3.2. What is stack memory? How is it implemented in an 8085 system? Discuss LIFO and

FIFO type of operations in stack registers.

3.3 Draw a schematic diagram to generate four control signals (using OR gates and using

decoder circuit) related to read and write operation of 8085.

3.4 Explain the block diagram of 8085 in detail.

3.5. Discuss the functions of the address bus and direction of the information flow on the

address bus, How many address lines are necessary to address two megabytes (2048 K)

of memory?

3.6 The instruction code 01001111 (4 FH) is stored in memory location 2005 H. Illustrate

the data flow and list the sequence of events when the instruction code is fetched by the

MPU.

3.7 Calculate the address lines for an 8K byte memory.

3.8 Why a 16-bit address (data) is stored in memory in the reversed order the low-order byte

first, followed by the high-order bytes?

56 -

39

3.1

S

3.

3.12

3.13

3.14

3.15

3.16

3.17

3.18

3.19

3.20

3.21

3.2.

a

3.24

3.25

3.26

Microprocessor 8085 and Its Interfacing '

Explain the functions of (a) HLDA (b) READY (c) SOD (4) ALE (e) RESET (f) Hoy,

pins of the 8085 microprocessor.

List the sequence of events that occurs when the 8085 microprocessor reads from the

memory.

What are the various status flags provided in 8085? Discuss their roles.

Explain the requirement of a program counter, stack pointer and instruction register in

the architecture of Intel 8085 microprocessor.

Why the program counter and the stack pointer are 16-bit registers? While executing

Program, when the 8085 microprocessor completes the fetching of the machine code

located at the memory address 2057 H, what is the content of the counter?

Explain the need to demultiplex the bus AD;-ADp. How is demultiplexing done?

How does the microprocessor know what operation to perform first (read/write memory

or read/write 1/0)?

How does the microprocessor differentiate between data and instruction?

Write the procedure to communicate with memory by a microprocessor.

Explain the functions of flag, program counter and accumulator in the architecture of

8085 microprocessor.

Explain the functions of the following signals of 8085 microprocessor:

(a) HLDA (6) S;, Sy (c) IO/M™ (4) INTR

Sketch and explain the signal diagram of 8085.

Mention the list of registers of 8085 that are accessible to the programmer. Explain what

each of these registers is generally used for.

Explain with schematic diagram how separate address, data signals can be generated

from 8085 common address data lines.

Explain the schematic which decodes IO/M", RD", WR’ into four active low signals

MEMR’, MEMW’, IOR™ and IOW-.

List the status signals in 8085. Explain their functions.

List the control signals in 8085. Explain their functions.

What are RAMs and ROMs? Why should both of these be used in an 8085 system?

MULTIPLE CHOICE QUESTIONS

What is clock frequency for 8085?

(@) 3 MHz (b) 2 MHz

(©) 4 MHz (@) 5 MHz

. How many hardware interrupts are there in 8085?

(a) 5 (b) 6

(c) 7 @) 8

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5807)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (842)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- 8085 MicroprocessorDocument32 pages8085 MicroprocessorSnehardraNo ratings yet

- Introduction To Plasma Physics FF Chen - Equilibrium and Stability Lecture NotesDocument23 pagesIntroduction To Plasma Physics FF Chen - Equilibrium and Stability Lecture NotesSnehardraNo ratings yet

- Plasma As Fluid and Waves in Plasma NotesDocument19 pagesPlasma As Fluid and Waves in Plasma NotesSnehardraNo ratings yet

- Dielectric Properties and Magnetic PropertiesDocument66 pagesDielectric Properties and Magnetic PropertiesSnehardraNo ratings yet

- Instruction Set of 8085Document53 pagesInstruction Set of 8085SnehardraNo ratings yet

- MScPythonPracts 231020 223819Document39 pagesMScPythonPracts 231020 223819SnehardraNo ratings yet

- Mechanics Relativity Properties of Matter ThermodynamicsDocument2 pagesMechanics Relativity Properties of Matter ThermodynamicsSnehardraNo ratings yet

- LASERS PolarisationDocument35 pagesLASERS PolarisationSnehardraNo ratings yet

- Quantam Dynamics (From Semiclassical Apprx)Document26 pagesQuantam Dynamics (From Semiclassical Apprx)SnehardraNo ratings yet

- 1.microprocessor and Assembly Language ProgrammingDocument34 pages1.microprocessor and Assembly Language ProgrammingSnehardraNo ratings yet

- Nanoscience and Technology 2017Document3 pagesNanoscience and Technology 2017SnehardraNo ratings yet

- Materials Science 2019 c60060Document3 pagesMaterials Science 2019 c60060SnehardraNo ratings yet

- Nanoscience and NanotechnologyDocument134 pagesNanoscience and NanotechnologySnehardraNo ratings yet

- Thermal and Statistical Physics 2019Document3 pagesThermal and Statistical Physics 2019SnehardraNo ratings yet

- Kerala Class 6 First Term Onam Exam Question Paper 2019 Social Science (MM)Document3 pagesKerala Class 6 First Term Onam Exam Question Paper 2019 Social Science (MM)SnehardraNo ratings yet

- Application of NanotechnologyDocument19 pagesApplication of NanotechnologySnehardraNo ratings yet

- Solid State Physics Spectroscopy and Laser Physics 2017Document3 pagesSolid State Physics Spectroscopy and Laser Physics 2017SnehardraNo ratings yet

- Python For EducationDocument85 pagesPython For EducationSnehardraNo ratings yet

- Nuclear-Particleand AstrophysicsDocument3 pagesNuclear-Particleand AstrophysicsSnehardraNo ratings yet