Professional Documents

Culture Documents

PIC16F87XA: 4.5 PORTE and TRISE Register

Uploaded by

vitor valeOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PIC16F87XA: 4.5 PORTE and TRISE Register

Uploaded by

vitor valeCopyright:

Available Formats

PIC16F87XA

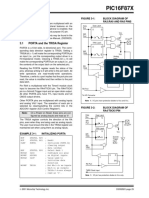

4.5 PORTE and TRISE Register FIGURE 4-9: PORTE BLOCK DIAGRAM

(IN I/O PORT MODE)

Note: PORTE and TRISE are not implemented

on the 28-pin devices. Data Data Latch

Bus D Q

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6

and RE2/CS/AN7) which are individually configurable WR

I/O pin(1)

Port

as inputs or outputs. These pins have Schmitt Trigger CK

input buffers.

TRIS Latch

The PORTE pins become the I/O control inputs for the D Q

microprocessor port when bit PSPMODE (TRISE<4>) is WR

set. In this mode, the user must make certain that the TRIS

CK Schmitt

TRISE<2:0> bits are set and that the pins are configured Trigger

Input

as digital inputs. Also, ensure that ADCON1 is config- Buffer

ured for digital I/O. In this mode, the input buffers are

RD

TTL. TRIS

Register 4-1 shows the TRISE register which also

controls the Parallel Slave Port operation.

Q D

PORTE pins are multiplexed with analog inputs. When

selected for analog input, these pins will read as ‘0’s. ENEN

TRISE controls the direction of the RE pins, even when RD Port

they are being used as analog inputs. The user must

make sure to keep the pins configured as inputs when

using them as analog inputs. Note 1: I/O pins have protection diodes to VDD and VSS.

Note: On a Power-on Reset, these pins are

configured as analog inputs and read as ‘0’.

TABLE 4-9: PORTE FUNCTIONS

Name Bit# Buffer Type Function

I/O port pin or read control input in Parallel Slave Port mode or analog input:

RD

RE0/RD/AN5 bit 0 ST/TTL(1) 1 = Idle

0 = Read operation. Contents of PORTD register are output to PORTD

I/O pins (if chip selected).

I/O port pin or write control input in Parallel Slave Port mode or analog input:

WR

RE1/WR/AN6 bit 1 ST/TTL(1) 1 = Idle

0 = Write operation. Value of PORTD I/O pins is latched into PORTD

register (if chip selected).

I/O port pin or chip select control input in Parallel Slave Port mode or analog input:

CS

RE2/CS/AN7 bit 2 ST/TTL(1)

1 = Device is not selected

0 = Device is selected

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

2003 Microchip Technology Inc. DS39582B-page 49

PIC16F87XA

TABLE 4-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Value on

Value on:

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 all other

POR, BOR

Resets

09h PORTE — — — — — RE2 RE1 RE0 ---- -xxx ---- -uuu

89h TRISE IBF OBF IBOV PSPMODE — PORTE Data Direction bits 0000 -111 0000 -111

9Fh ADCON1 ADFM ADCS2 — — PCFG3 PCFG2 PCFG1 PCFG0 00-- 0000 00-- 0000

Legend: x = unknown, u = unchanged, - = unimplemented, read as ‘0’. Shaded cells are not used by PORTE.

REGISTER 4-1: TRISE REGISTER (ADDRESS 89h)

R-0 R-0 R/W-0 R/W-0 U-0 R/W-1 R/W-1 R/W-1

IBF OBF IBOV PSPMODE — Bit 2 Bit 1 Bit 0

bit 7 bit 0

Parallel Slave Port Status/Control Bits:

bit 7 IBF: Input Buffer Full Status bit

1 = A word has been received and is waiting to be read by the CPU

0 = No word has been received

bit 6 OBF: Output Buffer Full Status bit

1 = The output buffer still holds a previously written word

0 = The output buffer has been read

bit 5 IBOV: Input Buffer Overflow Detect bit (in Microprocessor mode)

1 = A write occurred when a previously input word has not been read (must be cleared in

software)

0 = No overflow occurred

bit 4 PSPMODE: Parallel Slave Port Mode Select bit

1 = PORTD functions in Parallel Slave Port mode

0 = PORTD functions in general purpose I/O mode

bit 3 Unimplemented: Read as ‘0’

PORTE Data Direction Bits:

bit 2 Bit 2: Direction Control bit for pin RE2/CS/AN7

1 = Input

0 = Output

bit 1 Bit 1: Direction Control bit for pin RE1/WR/AN6

1 = Input

0 = Output

bit 0 Bit 0: Direction Control bit for pin RE0/RD/AN5

1 = Input

0 = Output

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS39582B-page 50 2003 Microchip Technology Inc.

PIC16F87XA

4.6 Parallel Slave Port When not in PSP mode, the IBF and OBF bits are held

clear. However, if flag bit IBOV was previously set, it

The Parallel Slave Port (PSP) is not implemented on must be cleared in firmware.

the PIC16F873A or PIC16F876A.

An interrupt is generated and latched into flag bit

PORTD operates as an 8-bit wide Parallel Slave Port, PSPIF when a read or write operation is completed.

or microprocessor port, when control bit PSPMODE PSPIF must be cleared by the user in firmware and the

(TRISE<4>) is set. In Slave mode, it is asynchronously interrupt can be disabled by clearing the interrupt

readable and writable by the external world through RD enable bit PSPIE (PIE1<7>).

control input pin, RE0/RD/AN5, and WR control input

pin, RE1/WR/AN6.

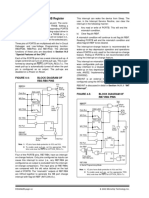

FIGURE 4-10: PORTD AND PORTE

The PSP can directly interface to an 8-bit BLOCK DIAGRAM

microprocessor data bus. The external microprocessor (PARALLEL SLAVE PORT)

can read or write the PORTD latch as an 8-bit latch.

Setting bit PSPMODE enables port pin RE0/RD/AN5 to

be the RD input, RE1/WR/AN6 to be the WR input and Data Bus

D Q

RE2/CS/AN7 to be the CS (Chip Select) input. For this

functionality, the corresponding data direction bits of WR RDx pin

Port

the TRISE register (TRISE<2:0>) must be configured CK

as inputs (set). The A/D port configuration bits, TTL

PCFG3:PCFG0 (ADCON1<3:0>), must be set to

Q D

configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches: one for data output RD Port ENEN

and one for data input. The user writes 8-bit data to the

PORTD data latch and reads data from the port pin

One bit of PORTD

latch (note that they have the same address). In this

mode, the TRISD register is ignored since the external Set Interrupt Flag

device is controlling the direction of data flow. PSPIF (PIR1<7>)

A write to the PSP occurs when both the CS and WR

lines are first detected low. When either the CS or WR

lines become high (level triggered), the Input Buffer Full

(IBF) status flag bit (TRISE<7>) is set on the Q4 clock Read

TTL RD

cycle, following the next Q2 cycle, to signal the write is

complete (Figure 4-11). The interrupt flag bit, PSPIF Chip Select

TTL CS

(PIR1<7>), is also set on the same Q4 clock cycle. IBF

can only be cleared by reading the PORTD input latch. Write

The Input Buffer Overflow (IBOV) status flag bit TTL WR

(TRISE<5>) is set if a second write to the PSP is

attempted when the previous byte has not been read Note 1: I/O pins have protection diodes to VDD and VSS.

out of the buffer.

A read from the PSP occurs when both the CS and RD

lines are first detected low. The Output Buffer Full

(OBF) status flag bit (TRISE<6>) is cleared

immediately (Figure 4-12), indicating that the PORTD

latch is waiting to be read by the external bus. When

either the CS or RD pin becomes high (level triggered),

the interrupt flag bit PSPIF is set on the Q4 clock cycle,

following the next Q2 cycle, indicating that the read is

complete. OBF remains low until data is written to

PORTD by the user firmware.

2003 Microchip Technology Inc. DS39582B-page 51

PIC16F87XA

FIGURE 4-11: PARALLEL SLAVE PORT WRITE WAVEFORMS

Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

CS

WR

RD

PORTD<7:0>

IBF

OBF

PSPIF

FIGURE 4-12: PARALLEL SLAVE PORT READ WAVEFORMS

Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

CS

WR

RD

PORTD<7:0>

IBF

OBF

PSPIF

TABLE 4-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

Value on

Value on:

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 all other

POR, BOR

Resets

08h PORTD Port Data Latch when written; Port pins when read xxxx xxxx uuuu uuuu

09h PORTE — — — — — RE2 RE1 RE0 ---- -xxx ---- -uuu

89h TRISE IBF OBF IBOV PSPMODE — PORTE Data Direction bits 0000 -111 0000 -111

0Ch PIR1 PSPIF(1) ADIF RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF 0000 0000 0000 0000

8Ch PIE1 PSPIE(1) ADIE RCIE TXIE SSPIE CCP1IE TMR2IE TMR1IE 0000 0000 0000 0000

9Fh ADCON1 ADFM ADCS2 — — PCFG3 PCFG2 PCFG1 PCFG0 00-- 0000 00-- 0000

Legend: x = unknown, u = unchanged, - = unimplemented, read as ‘0’. Shaded cells are not used by the Parallel Slave Port.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873A/876A; always maintain these bits clear.

DS39582B-page 52 2003 Microchip Technology Inc.

PIC16F87XA

5.0 TIMER0 MODULE Counter mode is selected by setting bit T0CS

(OPTION_REG<5>). In Counter mode, Timer0 will

The Timer0 module timer/counter has the following increment either on every rising or falling edge of pin

features: RA4/T0CKI. The incrementing edge is determined by

• 8-bit timer/counter the Timer0 Source Edge Select bit, T0SE

• Readable and writable (OPTION_REG<4>). Clearing bit T0SE selects the ris-

ing edge. Restrictions on the external clock input are

• 8-bit software programmable prescaler

discussed in detail in Section 5.2 “Using Timer0 with

• Internal or external clock select an External Clock”.

• Interrupt on overflow from FFh to 00h

The prescaler is mutually exclusively shared between

• Edge select for external clock the Timer0 module and the Watchdog Timer. The

Figure 5-1 is a block diagram of the Timer0 module and prescaler is not readable or writable. Section 5.3

the prescaler shared with the WDT. “Prescaler” details the operation of the prescaler.

Additional information on the Timer0 module is

available in the PICmicro® Mid-Range MCU Family 5.1 Timer0 Interrupt

Reference Manual (DS33023). The TMR0 interrupt is generated when the TMR0

Timer mode is selected by clearing bit T0CS register overflows from FFh to 00h. This overflow sets

(OPTION_REG<5>). In Timer mode, the Timer0 bit TMR0IF (INTCON<2>). The interrupt can be

module will increment every instruction cycle (without masked by clearing bit TMR0IE (INTCON<5>). Bit

prescaler). If the TMR0 register is written, the incre- TMR0IF must be cleared in software by the Timer0

ment is inhibited for the following two instruction cycles. module Interrupt Service Routine before re-enabling

The user can work around this by writing an adjusted this interrupt. The TMR0 interrupt cannot awaken the

value to the TMR0 register. processor from Sleep since the timer is shut-off during

Sleep.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

CLKO (= FOSC/4)

Data Bus

8

M 1

0

RA4/T0CKI U M Sync

pin X U

1 0 2 TMR0 Reg

X Cycles

T0SE

T0CS

PSA Set Flag bit TMR0IF

on Overflow

PRESCALER

0

M 8-bit Prescaler

U

Watchdog 1 X 8

Timer

8-to-1 MUX PS2:PS0

PSA

0 1

WDT Enable bit

MUX PSA

WDT

Time-out

Note: T0CS, T0SE, PSA, PS2:PS0 are (OPTION_REG<5:0>).

2003 Microchip Technology Inc. DS39582B-page 53

You might also like

- Unit IIDocument23 pagesUnit IIomgunjal85No ratings yet

- PIC PortsDocument4 pagesPIC PortsPranav vigneshNo ratings yet

- 04 I - o Ports On Pic16f877Document14 pages04 I - o Ports On Pic16f877Allen AlaskaNo ratings yet

- Port DetailsDocument2 pagesPort DetailsJaya LukyNo ratings yet

- Objecttves: Upon Completion Chapte4 You ToDocument22 pagesObjecttves: Upon Completion Chapte4 You ToFaizan AliNo ratings yet

- Parallel Port I/ODocument41 pagesParallel Port I/OvestereverNo ratings yet

- Atmega128 I/O Ports: VersusDocument16 pagesAtmega128 I/O Ports: VersusZoranNo ratings yet

- Topic 10 - AVR IO in C (ISMAIL - FKEUTM 2018)Document93 pagesTopic 10 - AVR IO in C (ISMAIL - FKEUTM 2018)Aya AmirNo ratings yet

- Spark V Exp 2Document7 pagesSpark V Exp 2yogeshNo ratings yet

- PIC16F87X: 3.0 I/O PortsDocument6 pagesPIC16F87X: 3.0 I/O PortsMenad SalahNo ratings yet

- PIC16 Digital and Analog Input Output ProgrammingDocument35 pagesPIC16 Digital and Analog Input Output ProgrammingMostafa AbdulmalekNo ratings yet

- PIC16F628Document30 pagesPIC16F628Prince YehyaNo ratings yet

- Subroutines: Nithin S. EEE DeptDocument33 pagesSubroutines: Nithin S. EEE DeptabcdefgNo ratings yet

- Ports and Pins Configuration of PIC MicrocontrollersDocument33 pagesPorts and Pins Configuration of PIC Microcontrollersyug varshneyNo ratings yet

- 8255A Programmable Peripheral InterfaceDocument5 pages8255A Programmable Peripheral InterfaceSahil .S.PawarNo ratings yet

- PIC16F87XA: 3.7 Protection Against Spurious Write 3.8 Operation During Code-ProtectDocument5 pagesPIC16F87XA: 3.7 Protection Against Spurious Write 3.8 Operation During Code-Protectvitor valeNo ratings yet

- Hardware RequirementsDocument36 pagesHardware RequirementsAnuraag HiremathNo ratings yet

- PIC16F87XA: 4.2 PORTB and The TRISB RegisterDocument5 pagesPIC16F87XA: 4.2 PORTB and The TRISB Registervitor valeNo ratings yet

- MPMC Unit4Document61 pagesMPMC Unit4Nandhini ShreeNo ratings yet

- Chapter 3 IoDocument17 pagesChapter 3 IoShanker KalaivaniNo ratings yet

- Chapter 4 IoDocument17 pagesChapter 4 IoAmzar ShukriNo ratings yet

- AVR I/O ports configurationDocument67 pagesAVR I/O ports configurationJanice TiongNo ratings yet

- Experiment No: 1: TheoryDocument28 pagesExperiment No: 1: TheorychitranganNo ratings yet

- Unit - III InterfacingDocument53 pagesUnit - III InterfacingPavan ParthikNo ratings yet

- Lab Assignment 2Document26 pagesLab Assignment 2Pandu KNo ratings yet

- 8255 Ppi ExamplesDocument10 pages8255 Ppi Examplesvenky258100% (1)

- Ppi 8255Document163 pagesPpi 8255Taufik Mage3No ratings yet

- 8155 - Siddharth ChauhanDocument42 pages8155 - Siddharth ChauhanSiddharth Chauhan100% (3)

- Ees06 MSP430 GpioDocument20 pagesEes06 MSP430 GpioasdsdNo ratings yet

- STATUS Register (RAM Memory Address 03h, 83h)Document4 pagesSTATUS Register (RAM Memory Address 03h, 83h)KanoNo ratings yet

- Unit 1 MaDocument29 pagesUnit 1 MaEljameely JamaleldeenNo ratings yet

- LPC2148 IntroDocument47 pagesLPC2148 IntroNavami SunilNo ratings yet

- 8255 PPI - Ppi Programmable Peripheral InterfaceDocument62 pages8255 PPI - Ppi Programmable Peripheral InterfaceVport PortNo ratings yet

- Im&a Unit-1 PartDocument10 pagesIm&a Unit-1 PartAmrutha VarshaNo ratings yet

- 8255 Programmable Peripheral Interface ModesDocument54 pages8255 Programmable Peripheral Interface Modesmariyal eceNo ratings yet

- 8255 NewDocument13 pages8255 Newmohit mishraNo ratings yet

- Microcontroller & Embedded Systems Lab Manual Exp.1,2,3Document11 pagesMicrocontroller & Embedded Systems Lab Manual Exp.1,2,3Akanksha DixitNo ratings yet

- Port Programming Assembly 8086Document15 pagesPort Programming Assembly 8086avmapNo ratings yet

- PIC16F87XA: 2.2.2.3 INTCON RegisterDocument5 pagesPIC16F87XA: 2.2.2.3 INTCON Registervitor valeNo ratings yet

- Pin Diagram PortsDocument22 pagesPin Diagram PortsAkarsh R SharmaNo ratings yet

- Pinout Diagram of Atmega16Document7 pagesPinout Diagram of Atmega16Harshit VermaNo ratings yet

- 80C51 Family Hardware Description 80C51 FamilyDocument24 pages80C51 Family Hardware Description 80C51 FamilyABDElrahmanJamalMohaNo ratings yet

- Chapter3-Input Output Ports ProgrammingDocument26 pagesChapter3-Input Output Ports Programmingadamwaiz100% (1)

- CH 3 PpiDocument12 pagesCH 3 PpiAnisSamyNo ratings yet

- The Programmable Peripheral Interface DeviceDocument25 pagesThe Programmable Peripheral Interface Devicenskpatnaik100% (10)

- Pin ConfigurationDocument27 pagesPin ConfigurationShanmukh SudheendraNo ratings yet

- PROJECT USING MICROCONTROLLER ATMEGA16Document34 pagesPROJECT USING MICROCONTROLLER ATMEGA16KARTHIK S SNo ratings yet

- Pen Gen AlanDocument16 pagesPen Gen AlanAin Syamimi KhairuddinNo ratings yet

- AVR Course Day4Document33 pagesAVR Course Day4Cristhian TapiaNo ratings yet

- General Purpose Input/Output: All Rights ReservedDocument20 pagesGeneral Purpose Input/Output: All Rights ReservedAlexgriNo ratings yet

- Ppi 8255Document16 pagesPpi 8255Md Rasheduzzaman RashedNo ratings yet

- I-O PortsDocument20 pagesI-O PortsPradeep V DevNo ratings yet

- 8255 Um CommonDocument55 pages8255 Um CommonChaitanya KommuNo ratings yet

- Chapter 5 interfacing to 8086Document71 pagesChapter 5 interfacing to 8086haileasrat4No ratings yet

- Lecture 8255 Ppi Upto ADC InterfacingDocument26 pagesLecture 8255 Ppi Upto ADC InterfacingAnadiKashyapNo ratings yet

- Data Transfer InstructionsDocument13 pagesData Transfer Instructionsrajeev kumarsharmaNo ratings yet

- Status Registers (Address 03h, 83h, 103h, and 183h) R/W - 0 R/W-0 R/W-0 R-1 R-1 R/W-X R/W-X R/W-X IRP RP1 RP0 TO PD Z DC CDocument9 pagesStatus Registers (Address 03h, 83h, 103h, and 183h) R/W - 0 R/W-0 R/W-0 R-1 R-1 R/W-X R/W-X R/W-X IRP RP1 RP0 TO PD Z DC Criyasudeen786No ratings yet

- Submitted To: Submitted By: Prof. A.K.Baliga Suraj Bora B.Tech (C.S.E)Document21 pagesSubmitted To: Submitted By: Prof. A.K.Baliga Suraj Bora B.Tech (C.S.E)putriNo ratings yet

- Exam Unit 1 Out and About 1º BachilleratoDocument5 pagesExam Unit 1 Out and About 1º Bachilleratolisikratis1980No ratings yet

- Guidelines SLCM BWDocument60 pagesGuidelines SLCM BWpnaarayanNo ratings yet

- User Manual: Rider 320Document46 pagesUser Manual: Rider 320SarahNo ratings yet

- 2011 Mena Annual Reportv1Document73 pages2011 Mena Annual Reportv1Yasmeen LayallieNo ratings yet

- DownloadDocument2 pagesDownloadAmit KumarNo ratings yet

- OlayDocument36 pagesOlayrachit.chaudharyNo ratings yet

- Robotics Process AutomationDocument21 pagesRobotics Process Automationbhaskarkiran.pNo ratings yet

- Mark Dyczkowski and Trika Journal March 2015 Vol.1.No.1.Document10 pagesMark Dyczkowski and Trika Journal March 2015 Vol.1.No.1.Mark Dyczkoswki and Trika Journal100% (2)

- Building Lean Supply ChainsDocument33 pagesBuilding Lean Supply ChainsJefri MustaphaNo ratings yet

- DS-RTCD905 H6W4Document2 pagesDS-RTCD905 H6W4david fonsecaNo ratings yet

- Anxiety, Depression and Self-Esteem in Children With Well-Controlled AsthmaDocument6 pagesAnxiety, Depression and Self-Esteem in Children With Well-Controlled AsthmaAbdallah H. KamelNo ratings yet

- 1 Catalyst FundamentalsDocument17 pages1 Catalyst FundamentalsSam AnuNo ratings yet

- The Separation of Coherent and Incoherent Compton X-Ray ScatteringDocument8 pagesThe Separation of Coherent and Incoherent Compton X-Ray ScatteringFaisal AmirNo ratings yet

- Toyota Genuine ATF WSDocument14 pagesToyota Genuine ATF WSKirillNo ratings yet

- Challenges Faced by Irregular StudentsDocument13 pagesChallenges Faced by Irregular StudentsTicag Teo80% (5)

- Mental Status Examination FormatDocument7 pagesMental Status Examination FormatMala Rasaily100% (3)

- Ethylene Yield From Pyrolysis Cracking in Olefin PDocument6 pagesEthylene Yield From Pyrolysis Cracking in Olefin PALL2WINNo ratings yet

- Islamic Center Design With Islamic ArchiDocument11 pagesIslamic Center Design With Islamic ArchiMuhammad Sufiyan SharafudeenNo ratings yet

- Critical Buckling Load of Pile in Liquefied SoilDocument8 pagesCritical Buckling Load of Pile in Liquefied SoilKefas JanuarNo ratings yet

- Coaching, Mentoring & OnboardingDocument43 pagesCoaching, Mentoring & OnboardingosvehNo ratings yet

- Integrated Marketing Communication PlanDocument5 pagesIntegrated Marketing Communication Planprojectwork185No ratings yet

- Pcit Brochure TemplateDocument2 pagesPcit Brochure Templateapi-370829251No ratings yet

- 17a03g - Mosfet - DualDocument5 pages17a03g - Mosfet - DualEletronica01 - BLUEVIXNo ratings yet

- New Ss 8 OutlineDocument3 pagesNew Ss 8 Outlineapi-251874206No ratings yet

- R4850G2 Rectifier Data Sheet 05Document2 pagesR4850G2 Rectifier Data Sheet 05PP CharlyNo ratings yet

- ISO 13485 Version 2016 Requirements NotesDocument24 pagesISO 13485 Version 2016 Requirements Notesda_reaper_dasNo ratings yet

- (Jean Oliver and Alison Middleditch (Auth.) ) Funct (B-Ok - CC)Document332 pages(Jean Oliver and Alison Middleditch (Auth.) ) Funct (B-Ok - CC)Lorena BurdujocNo ratings yet

- Chakra System of Animals FACT SHEETDocument4 pagesChakra System of Animals FACT SHEETNiko Diamesis75% (4)

- Sapamine CSN Textile Softener: Technical Data SheetDocument5 pagesSapamine CSN Textile Softener: Technical Data SheetsaskoNo ratings yet

- SHSHA Report PresentationDocument27 pagesSHSHA Report PresentationPatrick JohnsonNo ratings yet