Professional Documents

Culture Documents

PIC16F87X: 3.0 I/O Ports

Uploaded by

Menad SalahOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PIC16F87X: 3.0 I/O Ports

Uploaded by

Menad SalahCopyright:

Available Formats

PIC16F87X

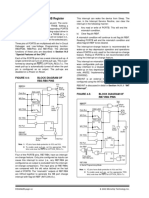

3.0 I/O PORTS FIGURE 3-1: BLOCK DIAGRAM OF

RA3:RA0 AND RA5 PINS

Some pins for these I/O ports are multiplexed with an

alternate function for the peripheral features on the Data Data Latch

Bus

device. In general, when a peripheral is enabled, that D Q

pin may not be used as a general purpose I/O pin.

VDD

WR

Additional information on I/O ports may be found in the Port

PICmicro™ Mid-Range Reference Manual, (DS33023). CK Q

P I/O pin(1)

3.1 PORTA and the TRISA Register TRIS Latch

N

D Q

PORTA is a 6-bit wide, bi-directional port. The corre-

sponding data direction register is TRISA. Setting a WR

TRISA bit (= 1) will make the corresponding PORTA pin TRIS VSS

CK Q

an input (i.e., put the corresponding output driver in a Analog

Hi-Impedance mode). Clearing a TRISA bit (= 0) will Input

Mode

make the corresponding PORTA pin an output (i.e., put

the contents of the output latch on the selected pin).

RD

Reading the PORTA register reads the status of the TRIS TTL

pins, whereas writing to it will write to the port latch. All Input

Buffer

write operations are read-modify-write operations. Q D

Therefore, a write to a port implies that the port pins are

read, the value is modified and then written to the port

data latch. EN

Pin RA4 is multiplexed with the Timer0 module clock

input to become the RA4/T0CKI pin. The RA4/T0CKI RD Port

pin is a Schmitt Trigger input and an open drain output.

All other PORTA pins have TTL input levels and full

To A/D Converter

CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs Note 1: I/O pins have protection diodes to VDD and VSS.

and analog VREF input. The operation of each pin is

selected by clearing/setting the control bits in the

ADCON1 register (A/D Control Register1). FIGURE 3-2: BLOCK DIAGRAM OF

RA4/T0CKI PIN

Note: On a Power-on Reset, these pins are con-

figured as analog inputs and read as '0'. Data Data Latch

Bus D Q

The TRISA register controls the direction of the RA WR

pins, even when they are being used as analog inputs. Port

CK Q

The user must ensure the bits in the TRISA register are N I/O pin(1)

maintained set when using them as analog inputs. TRIS Latch

D Q VSS

EXAMPLE 3-1: INITIALIZING PORTA WR

TRIS Schmitt

BCF STATUS, RP0 ; CK Q

Trigger

BCF STATUS, RP1 ; Bank0 Input

CLRF PORTA ; Initialize PORTA by Buffer

; clearing output RD

; data latches TRIS

BSF STATUS, RP0 ; Select Bank 1

MOVLW 0x06 ; Configure all pins

MOVWF ADCON1 ; as digital inputs Q D

MOVLW 0xCF ; Value used to

; initialize data ENEN

; direction

RD Port

MOVWF TRISA ; Set RA<3:0> as inputs

; RA<5:4> as outputs

; TRISA<7:6>are always TMR0 Clock Input

; read as ’0’.

Note 1: I/O pin has protection diodes to VSS only.

2001 Microchip Technology Inc. DS30292C-page 29

PIC16F87X

3.2 PORTB and the TRISB Register This interrupt can wake the device from SLEEP. The

user, in the Interrupt Service Routine, can clear the

PORTB is an 8-bit wide, bi-directional port. The corre- interrupt in the following manner:

sponding data direction register is TRISB. Setting a

TRISB bit (= 1) will make the corresponding PORTB pin a) Any read or write of PORTB. This will end the

an input (i.e., put the corresponding output driver in a mismatch condition.

Hi-Impedance mode). Clearing a TRISB bit (= 0) will b) Clear flag bit RBIF.

make the corresponding PORTB pin an output (i.e., put A mismatch condition will continue to set flag bit RBIF.

the contents of the output latch on the selected pin). Reading PORTB will end the mismatch condition and

Three pins of PORTB are multiplexed with the Low allow flag bit RBIF to be cleared.

Voltage Programming function: RB3/PGM, RB6/PGC The interrupt-on-change feature is recommended for

and RB7/PGD. The alternate functions of these pins wake-up on key depression operation and operations

are described in the Special Features Section. where PORTB is only used for the interrupt-on-change

Each of the PORTB pins has a weak internal pull-up. A feature. Polling of PORTB is not recommended while

single control bit can turn on all the pull-ups. This is per- using the interrupt-on-change feature.

formed by clearing bit RBPU (OPTION_REG<7>). The This interrupt-on-mismatch feature, together with soft-

weak pull-up is automatically turned off when the port ware configureable pull-ups on these four pins, allow

pin is configured as an output. The pull-ups are dis- easy interface to a keypad and make it possible for

abled on a Power-on Reset. wake-up on key depression. Refer to the Embedded

Control Handbook, “Implementing Wake-up on Key

FIGURE 3-3: BLOCK DIAGRAM OF Strokes” (AN552).

RB3:RB0 PINS RB0/INT is an external interrupt input pin and is config-

VDD ured using the INTEDG bit (OPTION_REG<6>).

RBPU(2)

Weak RB0/INT is discussed in detail in Section 12.10.1.

P Pull-up

Data Latch

Data Bus

D Q FIGURE 3-4: BLOCK DIAGRAM OF

WR Port

I/O RB7:RB4 PINS

CK pin(1)

VDD

TRIS Latch

RBPU(2)

D Q Weak

P Pull-up

TTL

WR TRIS Input Data Latch

CK Buffer Data Bus

D Q

I/O

WR Port CK pin(1)

RD TRIS

TRIS Latch

D Q

Q D

RD Port WR TRIS TTL

CK Input

EN

Buffer ST

Buffer

RB0/INT

RB3/PGM

RD TRIS

Latch

Schmitt Trigger RD Port

Buffer Q D

RD Port

Note 1: I/O pins have diode protection to VDD and VSS. EN Q1

2: To enable weak pull-ups, set the appropriate TRIS Set RBIF

bit(s) and clear the RBPU bit (OPTION_REG<7>).

Q D

Four of the PORTB pins, RB7:RB4, have an interrupt- RD Port

From other

on-change feature. Only pins configured as inputs can RB7:RB4 pins EN

cause this interrupt to occur (i.e., any RB7:RB4 pin Q3

configured as an output is excluded from the interrupt- RB7:RB6

on-change comparison). The input pins (of RB7:RB4) In Serial Programming Mode

are compared with the old value latched on the last Note 1: I/O pins have diode protection to VDD and VSS.

read of PORTB. The “mismatch” outputs of RB7:RB4 2: To enable weak pull-ups, set the appropriate TRIS

are OR’ed together to generate the RB Port Change bit(s) and clear the RBPU bit (OPTION_REG<7>).

Interrupt with flag bit RBIF (INTCON<0>).

2001 Microchip Technology Inc. DS30292C-page 31

PIC16F87X

3.3 PORTC and the TRISC Register FIGURE 3-6: PORTC BLOCK DIAGRAM

(PERIPHERAL OUTPUT

PORTC is an 8-bit wide, bi-directional port. The corre-

OVERRIDE) RC<4:3>

sponding data direction register is TRISC. Setting a

TRISC bit (= 1) will make the corresponding PORTC Port/Peripheral Select(2)

pin an input (i.e., put the corresponding output driver in

a Hi-Impedance mode). Clearing a TRISC bit (= 0) will Peripheral Data Out

0

make the corresponding PORTC pin an output (i.e., put VDD

Data Bus

the contents of the output latch on the selected pin). WR

D Q P I/O

Port 1 pin(1)

PORTC is multiplexed with several peripheral functions CK Q

(Table 3-5). PORTC pins have Schmitt Trigger input Data Latch

buffers.

D Q

When the I2C module is enabled, the PORTC<4:3> WR

TRIS

pins can be configured with normal I2C levels, or with CK Q N

SMBus levels by using the CKE bit (SSPSTAT<6>). TRIS Latch

Vss

When enabling peripheral functions, care should be RD

taken in defining TRIS bits for each PORTC pin. Some TRIS

Schmitt

peripherals override the TRIS bit to make a pin an out- Trigger

put, while other peripherals override the TRIS bit to Peripheral

OE(3) Q D

make a pin an input. Since the TRIS bit override is in Schmitt

Trigger

effect while the peripheral is enabled, read-modify- EN with

write instructions (BSF, BCF, XORWF) with TRISC as RD SMBus

Port 0 levels

destination, should be avoided. The user should refer SSPl Input

to the corresponding peripheral section for the correct

TRIS bit settings. 1

CKE

FIGURE 3-5: PORTC BLOCK DIAGRAM SSPSTAT<6>

(PERIPHERAL OUTPUT

Note 1: I/O pins have diode protection to VDD and VSS.

OVERRIDE) RC<2:0>, 2: Port/Peripheral select signal selects between port data

RC<7:5> and peripheral output.

3: Peripheral OE (output enable) is only activated if

peripheral select is active.

Port/Peripheral Select(2)

Peripheral Data Out

0 VDD

Data Bus

D Q

WR P I/O

Port CK Q 1 pin(1)

Data Latch

D Q

WR

TRIS CK Q

N

TRIS Latch

VSS

RD

TRIS

Schmitt

Trigger

Peripheral

OE(3) Q D

RD EN

Port

Peripheral Input

Note 1: I/O pins have diode protection to VDD and VSS.

2: Port/Peripheral select signal selects between port

data and peripheral output.

3: Peripheral OE (output enable) is only activated if

peripheral select is active.

2001 Microchip Technology Inc. DS30292C-page 33

PIC16F87X

3.4 PORTD and TRISD Registers FIGURE 3-7: PORTD BLOCK DIAGRAM

(IN I/O PORT MODE)

PORTD and TRISD are not implemented on the

PIC16F873 or PIC16F876. Data I/O pin(1)

Data Latch

Bus D Q

PORTD is an 8-bit port with Schmitt Trigger input buff-

ers. Each pin is individually configureable as an input or WR

Port

output. CK

PORTD can be configured as an 8-bit wide micropro- TRIS Latch

cessor port (parallel slave port) by setting control bit D Q

PSPMODE (TRISE<4>). In this mode, the input buffers WR

are TTL. TRIS Schmitt

CK

Trigger

Input

Buffer

RD

TRIS

Q D

ENEN

RD Port

Note 1: I/O pins have protection diodes to VDD and VSS.

TABLE 3-7: PORTD FUNCTIONS

Name Bit# Buffer Type Function

RD0/PSP0 bit0 ST/TTL(1) Input/output port pin or parallel slave port bit0.

RD1/PSP1 bit1 ST/TTL(1) Input/output port pin or parallel slave port bit1.

RD2/PSP2 bit2 ST/TTL(1) Input/output port pin or parallel slave port bit2.

(1)

RD3/PSP3 bit3 ST/TTL Input/output port pin or parallel slave port bit3.

RD4/PSP4 bit4 ST/TTL(1) Input/output port pin or parallel slave port bit4.

(1)

RD5/PSP5 bit5 ST/TTL Input/output port pin or parallel slave port bit5.

RD6/PSP6 bit6 ST/TTL(1) Input/output port pin or parallel slave port bit6.

RD7/PSP7 bit7 ST/TTL(1) Input/output port pin or parallel slave port bit7.

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

TABLE 3-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

Value on: Value on

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 POR, all other

BOR RESETS

08h PORTD RD7 RD6 RD5 RD4 RD3 RD2 RD1 RD0 xxxx xxxx uuuu uuuu

88h TRISD PORTD Data Direction Register 1111 1111 1111 1111

89h TRISE IBF OBF IBOV PSPMODE — PORTE Data Direction Bits 0000 -111 0000 -111

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

2001 Microchip Technology Inc. DS30292C-page 35

PIC16F87X

3.5 PORTE and TRISE Register FIGURE 3-8: PORTE BLOCK DIAGRAM

(IN I/O PORT MODE)

PORTE and TRISE are not implemented on the

PIC16F873 or PIC16F876. I/O pin(1)

Data Data Latch

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6, Bus D Q

and RE2/CS/AN7) which are individually configureable WR

as inputs or outputs. These pins have Schmitt Trigger Port

CK

input buffers.

TRIS Latch

The PORTE pins become the I/O control inputs for the

D Q

microprocessor port when bit PSPMODE (TRISE<4>) is

WR

set. In this mode, the user must make certain that the TRIS

CK Schmitt

TRISE<2:0> bits are set, and that the pins are configured Trigger

as digital inputs. Also ensure that ADCON1 is configured Input

for digital I/O. In this mode, the input buffers are TTL. Buffer

RD

Register 3-1 shows the TRISE register, which also con- TRIS

trols the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When

Q D

selected for analog input, these pins will read as ’0’s.

TRISE controls the direction of the RE pins, even when ENEN

they are being used as analog inputs. The user must RD Port

make sure to keep the pins configured as inputs when

using them as analog inputs.

Note 1: I/O pins have protection diodes to VDD and VSS.

Note: On a Power-on Reset, these pins are con-

figured as analog inputs, and read as ‘0’.

TABLE 3-9: PORTE FUNCTIONS

Name Bit# Buffer Type Function

I/O port pin or read control input in Parallel Slave Port mode or analog input:

RD

RE0/RD/AN5 bit0 ST/TTL(1) 1 = Idle

0 = Read operation. Contents of PORTD register are output to PORTD

I/O pins (if chip selected)

I/O port pin or write control input in Parallel Slave Port mode or analog input:

WR

RE1/WR/AN6 bit1 ST/TTL(1) 1 = Idle

0 = Write operation. Value of PORTD I/O pins is latched into PORTD

register (if chip selected)

I/O port pin or chip select control input in Parallel Slave Port mode or analog input:

CS

RE2/CS/AN7 bit2 ST/TTL(1)

1 = Device is not selected

0 = Device is selected

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

TABLE 3-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Value on

Value on:

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 all other

POR, BOR

RESETS

09h PORTE — — — — — RE2 RE1 RE0 ---- -xxx ---- -uuu

89h TRISE IBF OBF IBOV PSPMODE — PORTE Data Direction Bits 0000 -111 0000 -111

9Fh ADCON1 ADFM — — — PCFG3 PCFG2 PCFG1 PCFG0 --0- 0000 --0- 0000

Legend: x = unknown, u = unchanged, - = unimplemented, read as ’0’. Shaded cells are not used by PORTE.

DS30292C-page 36 2001 Microchip Technology Inc.

PIC16F87X

11.5 A/D Operation During SLEEP Turning off the A/D places the A/D module in its lowest

current consumption state.

The A/D module can operate during SLEEP mode. This

requires that the A/D clock source be set to RC Note: For the A/D module to operate in SLEEP,

(ADCS1:ADCS0 = 11). When the RC clock source is the A/D clock source must be set to RC

selected, the A/D module waits one instruction cycle (ADCS1:ADCS0 = 11). To allow the con-

before starting the conversion. This allows the SLEEP version to occur during SLEEP, ensure the

instruction to be executed, which eliminates all digital SLEEP instruction immediately follows the

switching noise from the conversion. When the conver- instruction that sets the GO/DONE bit.

sion is completed, the GO/DONE bit will be cleared and

the result loaded into the ADRES register. If the A/D 11.6 Effects of a RESET

interrupt is enabled, the device will wake-up from A device RESET forces all registers to their RESET

SLEEP. If the A/D interrupt is not enabled, the A/D state. This forces the A/D module to be turned off, and

module will then be turned off, although the ADON bit any conversion is aborted. All A/D input pins are con-

will remain set. figured as analog inputs.

When the A/D clock source is another clock option (not The value that is in the ADRESH:ADRESL registers is

RC), a SLEEP instruction will cause the present conver- not modified for a Power-on Reset. The

sion to be aborted and the A/D module to be turned off, ADRESH:ADRESL registers will contain unknown data

though the ADON bit will remain set. after a Power-on Reset.

TABLE 11-2: REGISTERS/BITS ASSOCIATED WITH A/D

Value on Value on

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 POR, MCLR,

BOR WDT

0Bh,8Bh, INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

10Bh,18Bh

0Ch PIR1 PSPIF(1) ADIF RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF 0000 0000 0000 0000

8Ch PIE1 PSPIE(1) ADIE RCIE TXIE SSPIE CCP1IE TMR2IE TMR1IE 0000 0000 0000 0000

1Eh ADRESH A/D Result Register High Byte xxxx xxxx uuuu uuuu

9Eh ADRESL A/D Result Register Low Byte xxxx xxxx uuuu uuuu

1Fh ADCON0 ADCS1 ADCS0 CHS2 CHS1 CHS0 GO/DONE — ADON 0000 00-0 0000 00-0

9Fh ADCON1 ADFM — — — PCFG3 PCFG2 PCFG1 PCFG0 --0- 0000 --0- 0000

85h TRISA — — PORTA Data Direction Register --11 1111 --11 1111

05h PORTA — — PORTA Data Latch when written: PORTA pins when read --0x 0000 --0u 0000

89h(1) TRISE IBF OBF IBOV PSPMODE — PORTE Data Direction bits 0000 -111 0000 -111

09h(1) PORTE — — — — — RE2 RE1 RE0 ---- -xxx ---- -uuu

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These registers/bits are not available on the 28-pin devices.

2001 Microchip Technology Inc. DS30292C-page 117

You might also like

- PIC16F87XA: 4.2 PORTB and The TRISB RegisterDocument5 pagesPIC16F87XA: 4.2 PORTB and The TRISB Registervitor valeNo ratings yet

- PIC16F87XA: 3.7 Protection Against Spurious Write 3.8 Operation During Code-ProtectDocument5 pagesPIC16F87XA: 3.7 Protection Against Spurious Write 3.8 Operation During Code-Protectvitor valeNo ratings yet

- PIC16F87XA: 4.5 PORTE and TRISE RegisterDocument5 pagesPIC16F87XA: 4.5 PORTE and TRISE Registervitor valeNo ratings yet

- Parallel Port I/ODocument41 pagesParallel Port I/OvestereverNo ratings yet

- 24fj PPSApNoteDocument26 pages24fj PPSApNoteLuis Di PintoNo ratings yet

- Port DetailsDocument2 pagesPort DetailsJaya LukyNo ratings yet

- Microcontroller & Embedded Systems Lab Manual Exp.1,2,3Document11 pagesMicrocontroller & Embedded Systems Lab Manual Exp.1,2,3Akanksha DixitNo ratings yet

- 8051 ArchitectureDocument13 pages8051 ArchitectureKabilanNo ratings yet

- Mcu - Pic24fv32ka304 - Microchip - Section 12. Io Ports With Pps - 39711bDocument24 pagesMcu - Pic24fv32ka304 - Microchip - Section 12. Io Ports With Pps - 39711bLudwig SchmidtNo ratings yet

- Delta DVPDocument3 pagesDelta DVPKerolos MekhaelNo ratings yet

- S7 GpioDocument14 pagesS7 GpioAhmed JemaiiNo ratings yet

- 04 I - o Ports On Pic16f877Document14 pages04 I - o Ports On Pic16f877Allen AlaskaNo ratings yet

- Unit IIDocument23 pagesUnit IIomgunjal85No ratings yet

- The Concise LCD Data Sheet.: RS T TDocument1 pageThe Concise LCD Data Sheet.: RS T TgcbilalNo ratings yet

- PIC PortsDocument4 pagesPIC PortsPranav vigneshNo ratings yet

- 8155 - Siddharth ChauhanDocument42 pages8155 - Siddharth ChauhanSiddharth Chauhan100% (3)

- Sigals 8086Document31 pagesSigals 8086RajaRaman.GNo ratings yet

- Spark V Exp 2Document7 pagesSpark V Exp 2yogeshNo ratings yet

- Hardware RequirementsDocument36 pagesHardware RequirementsAnuraag HiremathNo ratings yet

- Industrial Automation Using MicrocontrollerDocument43 pagesIndustrial Automation Using MicrocontrollerArduino UniNo ratings yet

- I/O Ports: Code ExampleDocument2 pagesI/O Ports: Code ExamplepawanNo ratings yet

- UNIT VI - Uart - Adc - SpiDocument55 pagesUNIT VI - Uart - Adc - SpiShubham MadneNo ratings yet

- The One With I - o Port ProgrammingDocument33 pagesThe One With I - o Port Programmingyug varshneyNo ratings yet

- Test 1Document56 pagesTest 1Satyam LalaNo ratings yet

- Section 10. I - O PortsDocument24 pagesSection 10. I - O PortsVlad MizeffNo ratings yet

- Co 1Document43 pagesCo 1Akula Lakshmi SreenivasuluNo ratings yet

- #Tutorialspoint Programmable Peripheral Interface 8255: Block DiagramDocument13 pages#Tutorialspoint Programmable Peripheral Interface 8255: Block DiagramHasib PeyalNo ratings yet

- #Tutorialspoint Programmable Peripheral Interface 8255: Block DiagramDocument26 pages#Tutorialspoint Programmable Peripheral Interface 8255: Block DiagramHasib PeyalNo ratings yet

- Topic 10 - AVR IO in C (ISMAIL - FKEUTM 2018)Document93 pagesTopic 10 - AVR IO in C (ISMAIL - FKEUTM 2018)Aya AmirNo ratings yet

- CH 3 PpiDocument12 pagesCH 3 PpiAnisSamyNo ratings yet

- RS232 Communication Bus, RS485, I2C, SPI, CAN, JTAG PDFDocument20 pagesRS232 Communication Bus, RS485, I2C, SPI, CAN, JTAG PDFndcongNo ratings yet

- Objecttves: Upon Completion Chapte4 You ToDocument22 pagesObjecttves: Upon Completion Chapte4 You ToFaizan AliNo ratings yet

- Advanced Microprocessors: Date: 16/11/2005 Prof. S. JagannathanDocument39 pagesAdvanced Microprocessors: Date: 16/11/2005 Prof. S. JagannathanVinoda DhayanitheNo ratings yet

- First Design: Key BoardDocument39 pagesFirst Design: Key BoardkkumkumNo ratings yet

- The 8051 MicrocontrollerDocument142 pagesThe 8051 MicrocontrollerRahul RaushanNo ratings yet

- ModbusDocument6 pagesModbusCésar YagüeNo ratings yet

- 8051 PresentationDocument40 pages8051 PresentationJain Philip UthupNo ratings yet

- Pin ConfigurationDocument27 pagesPin ConfigurationShanmukh SudheendraNo ratings yet

- Experiment No.: 5Document6 pagesExperiment No.: 5Dhrumil ManiyarNo ratings yet

- RAM/Peripheral Interfacing Device For 8085 and 8088: Hitesh PatelDocument28 pagesRAM/Peripheral Interfacing Device For 8085 and 8088: Hitesh Patelhitesh_maxi100% (1)

- Unit IIIDocument42 pagesUnit IIISoundarrajan RajanNo ratings yet

- PIC - IO PortsDocument43 pagesPIC - IO PortsElena Gilbert100% (2)

- BFM3333 Course: Microcontroller SystemDocument35 pagesBFM3333 Course: Microcontroller SystemMostafa AbdulmalekNo ratings yet

- Chapter3-Input Output Ports ProgrammingDocument26 pagesChapter3-Input Output Ports Programmingadamwaiz100% (1)

- IO PortsDocument45 pagesIO PortsAshwin S SivanNo ratings yet

- 06,250 (-1), 260 To 240 RS-232 Communications Wiring Diagram: TechnotesDocument1 page06,250 (-1), 260 To 240 RS-232 Communications Wiring Diagram: TechnoteswarwarNo ratings yet

- Chapter 3 IoDocument17 pagesChapter 3 IoShanker KalaivaniNo ratings yet

- Programmable Peripheral Interface 8255Document6 pagesProgrammable Peripheral Interface 8255AnkurNo ratings yet

- CH353DS1Document17 pagesCH353DS1zambare100% (1)

- Project Using Microcontroller-Atmega16: Pushparaj Mani PathakDocument34 pagesProject Using Microcontroller-Atmega16: Pushparaj Mani PathakKARTHIK S SNo ratings yet

- Presentation AviDocument29 pagesPresentation AvipoonamshallyNo ratings yet

- Unit Iii I/O Part A: InterfacingDocument54 pagesUnit Iii I/O Part A: Interfacingmariyal eceNo ratings yet

- Microcontroller 8051Document42 pagesMicrocontroller 8051om18sahuNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 1 s2.0 S1877042813032916 MainDocument5 pages1 s2.0 S1877042813032916 MainMenad SalahNo ratings yet

- Coca Cola قياس استجابة المستهلك والكلام الشفهيDocument25 pagesCoca Cola قياس استجابة المستهلك والكلام الشفهيMenad SalahNo ratings yet

- Ems AccessDocument25 pagesEms AccessMenad SalahNo ratings yet

- Effect of Post Weld Heat Treatment On Corrosion Resistance of Austenitic Stainless SteeDocument10 pagesEffect of Post Weld Heat Treatment On Corrosion Resistance of Austenitic Stainless SteeMenad SalahNo ratings yet

- Failure Pressure Analysis of The Pipe With Inner CorrosionDocument17 pagesFailure Pressure Analysis of The Pipe With Inner CorrosionMenad SalahNo ratings yet

- Nash DH Effect of Different Tip Angles Witht Tilted Torch in Stationary Gas Tungsten Arc Welding A 3D Simulation Aug 2013Document10 pagesNash DH Effect of Different Tip Angles Witht Tilted Torch in Stationary Gas Tungsten Arc Welding A 3D Simulation Aug 2013Menad SalahNo ratings yet

- The Effect of Successive Repairs On The 20150412101851 431297Document7 pagesThe Effect of Successive Repairs On The 20150412101851 431297Menad SalahNo ratings yet

- SAW Welding Effect of Welding Parameters On Penetration and Bead WidthDocument7 pagesSAW Welding Effect of Welding Parameters On Penetration and Bead WidthMenad SalahNo ratings yet

- List of Items Not Covered by EN 1090:2009+A1:2011Document3 pagesList of Items Not Covered by EN 1090:2009+A1:2011Menad SalahNo ratings yet

- Effects of Torch Configuration and Welding Current On Weld Bead Formation WeldDocument10 pagesEffects of Torch Configuration and Welding Current On Weld Bead Formation WeldMenad SalahNo ratings yet

- Quality Assuarance in WeldingDocument150 pagesQuality Assuarance in WeldingMenad SalahNo ratings yet

- C100 Cryomodule Supply/Return Header Design Per ASME B31.3: An Addendum To JLAB-TN-07-051Document5 pagesC100 Cryomodule Supply/Return Header Design Per ASME B31.3: An Addendum To JLAB-TN-07-051Menad SalahNo ratings yet

- Caracterisation Des Defauts Par UltrasonDocument17 pagesCaracterisation Des Defauts Par UltrasonMenad SalahNo ratings yet

- 01 Access Pipeline Fact Sheet ONE FINALDocument2 pages01 Access Pipeline Fact Sheet ONE FINALMenad SalahNo ratings yet

- 031 Building Management System UP CE ING TN 120 0Document41 pages031 Building Management System UP CE ING TN 120 0Đức Huấn ĐỗNo ratings yet

- Quasaruk Remote Control SystemsDocument3 pagesQuasaruk Remote Control SystemsMike SmithNo ratings yet

- Full Thesis Print 04.07Document65 pagesFull Thesis Print 04.07Gaurav KukadeNo ratings yet

- Using A GMR Effect Sensor To Measure The Current in A Wire by Means of Its Magnetic FieldDocument6 pagesUsing A GMR Effect Sensor To Measure The Current in A Wire by Means of Its Magnetic FieldManeesha WijesingheNo ratings yet

- Lab 1: Diode I-V CharacteristicsDocument4 pagesLab 1: Diode I-V CharacteristicsDa Harlequin GalNo ratings yet

- IndxDocument2 pagesIndxJUAN CARLOS SILVESTRENo ratings yet

- LCM CodesDocument4 pagesLCM CodesŁukasz KrzyżanekNo ratings yet

- Power Supply Systems Spds Type 2: Dehnguard® Modular Dgmtt275Document2 pagesPower Supply Systems Spds Type 2: Dehnguard® Modular Dgmtt275amaliadabookNo ratings yet

- 29-48 Delco RemyDocument184 pages29-48 Delco Remybigjl71100% (3)

- Serratron 100 IDocument4 pagesSerratron 100 IOvidiu Si Roxana IvascuNo ratings yet

- InteliVision 12touch DatasheetDocument4 pagesInteliVision 12touch DatasheetMaylen RivasNo ratings yet

- Ut 621024Document14 pagesUt 621024DarleiDuarteNo ratings yet

- Our Own High School, Al Warqa'A Grade: Xii E Worksheet - PhysicsDocument2 pagesOur Own High School, Al Warqa'A Grade: Xii E Worksheet - PhysicsAniruddha KadamNo ratings yet

- Comp EX 1Document120 pagesComp EX 1Vignesh Madhavan100% (3)

- Microprocessor 8086Document231 pagesMicroprocessor 8086Smarak LenkaNo ratings yet

- The Ultraviolet Detection of Corona Discharge in Power Transmission LinesDocument5 pagesThe Ultraviolet Detection of Corona Discharge in Power Transmission LinesleivajNo ratings yet

- 3.5.4. Directional Definite Time Overcurrent Protection (Dircurrentdt)Document7 pages3.5.4. Directional Definite Time Overcurrent Protection (Dircurrentdt)Alex asherNo ratings yet

- Signals and Systems.60 Q.PDocument9 pagesSignals and Systems.60 Q.Prubiniravichandran100% (1)

- Jaquar Lighting-Technical Catalogue For Jaquar Lighting 2021Document399 pagesJaquar Lighting-Technical Catalogue For Jaquar Lighting 2021Ar Mohammed HamzaNo ratings yet

- RTK 725B Basic InformationDocument4 pagesRTK 725B Basic Informationm khNo ratings yet

- Gayatri Physics ProjectDocument27 pagesGayatri Physics ProjectHardik PatilNo ratings yet

- Chapter 3Document33 pagesChapter 3Pratik KumarNo ratings yet

- FQPF10N60CDocument10 pagesFQPF10N60Cmiloud1911No ratings yet

- 473 04Document22 pages473 04Amine AbdelNo ratings yet

- Heidenhain Ik 121v ManualDocument116 pagesHeidenhain Ik 121v ManualmasinemaNo ratings yet

- User Manual CA8335Document116 pagesUser Manual CA8335Achraf ChtibiNo ratings yet

- Watts CleverDocument4 pagesWatts Cleverrowanhains0% (1)

- Lesson Plan - DemoDocument5 pagesLesson Plan - Demomarvin agubanNo ratings yet

- Rectangular Waveguide ResonatorDocument18 pagesRectangular Waveguide ResonatorMilan MakwanaNo ratings yet

- Arc-164 ManualDocument140 pagesArc-164 Manualj.wennikNo ratings yet