Professional Documents

Culture Documents

PIC16F87XA: 4.2 PORTB and The TRISB Register

Uploaded by

vitor valeOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PIC16F87XA: 4.2 PORTB and The TRISB Register

Uploaded by

vitor valeCopyright:

Available Formats

PIC16F87XA

4.2 PORTB and the TRISB Register This interrupt can wake the device from Sleep. The

user, in the Interrupt Service Routine, can clear the

PORTB is an 8-bit wide, bidirectional port. The corre- interrupt in the following manner:

sponding data direction register is TRISB. Setting a

TRISB bit (= 1) will make the corresponding PORTB a) Any read or write of PORTB. This will end the

pin an input (i.e., put the corresponding output driver in mismatch condition.

a High-Impedance mode). Clearing a TRISB bit (= 0) b) Clear flag bit RBIF.

will make the corresponding PORTB pin an output (i.e., A mismatch condition will continue to set flag bit RBIF.

put the contents of the output latch on the selected pin). Reading PORTB will end the mismatch condition and

Three pins of PORTB are multiplexed with the In-Circuit allow flag bit RBIF to be cleared.

Debugger and Low-Voltage Programming function: The interrupt-on-change feature is recommended for

RB3/PGM, RB6/PGC and RB7/PGD. The alternate wake-up on key depression operation and operations

functions of these pins are described in Section 14.0 where PORTB is only used for the interrupt-on-change

“Special Features of the CPU”. feature. Polling of PORTB is not recommended while

Each of the PORTB pins has a weak internal pull-up. A using the interrupt-on-change feature.

single control bit can turn on all the pull-ups. This is per- This interrupt-on-mismatch feature, together with soft-

formed by clearing bit RBPU (OPTION_REG<7>). The ware configurable pull-ups on these four pins, allow

weak pull-up is automatically turned off when the port easy interface to a keypad and make it possible for

pin is configured as an output. The pull-ups are wake-up on key depression. Refer to the application

disabled on a Power-on Reset. note, AN552, “Implementing Wake-up on Key Stroke”

(DS00552).

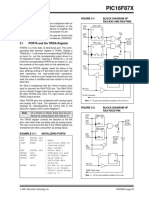

FIGURE 4-4: BLOCK DIAGRAM OF RB0/INT is an external interrupt input pin and is

RB3:RB0 PINS configured using the INTEDG bit (OPTION_REG<6>).

VDD

RBPU(2)

RB0/INT is discussed in detail in Section 14.11.1 “INT

Weak Interrupt”.

P Pull-up

Data Latch

Data Bus

D Q FIGURE 4-5: BLOCK DIAGRAM OF

WR Port

I/O pin(1) RB7:RB4 PINS

CK

VDD

TRIS Latch

RBPU(2) Weak

D Q P Pull-up

TTL

WR TRIS Input Data Latch

CK Buffer Data Bus

D Q

I/O pin(1)

WR Port CK

RD TRIS

TRIS Latch

Q D D Q

RD Port WR TRIS TTL

EN CK Input

Buffer ST

RB0/INT Buffer

RB3/PGM

RD TRIS

Latch

Schmitt Trigger RD Port

Buffer Q D

RD Port

Note 1: I/O pins have diode protection to VDD and VSS. EN Q1

2: To enable weak pull-ups, set the appropriate TRIS Set RBIF

bit(s) and clear the RBPU bit (OPTION_REG<7>).

Q D

Four of the PORTB pins, RB7:RB4, have an interrupt- RD Port

From other

on-change feature. Only pins configured as inputs can RB7:RB4 pins EN

cause this interrupt to occur (i.e., any RB7:RB4 pin Q3

configured as an output is excluded from the interrupt- RB7:RB6

on-change comparison). The input pins (of RB7:RB4) In Serial Programming Mode

are compared with the old value latched on the last Note 1: I/O pins have diode protection to VDD and VSS.

read of PORTB. The “mismatch” outputs of RB7:RB4 2: To enable weak pull-ups, set the appropriate TRIS

are OR’ed together to generate the RB port change bit(s) and clear the RBPU bit (OPTION_REG<7>).

interrupt with flag bit RBIF (INTCON<0>).

DS39582B-page 44 2003 Microchip Technology Inc.

PIC16F87XA

TABLE 4-3: PORTB FUNCTIONS

Name Bit# Buffer Function

RB0/INT bit 0 TTL/ST(1) Input/output pin or external interrupt input. Internal software programmable

weak pull-up.

RB1 bit 1 TTL Input/output pin. Internal software programmable weak pull-up.

RB2 bit 2 TTL Input/output pin. Internal software programmable weak pull-up.

(3)

RB3/PGM bit 3 TTL Input/output pin or programming pin in LVP mode. Internal software

programmable weak pull-up.

RB4 bit 4 TTL Input/output pin (with interrupt-on-change). Internal software programmable

weak pull-up.

RB5 bit 5 TTL Input/output pin (with interrupt-on-change). Internal software programmable

weak pull-up.

RB6/PGC bit 6 TTL/ST(2) Input/output pin (with interrupt-on-change) or in-circuit debugger pin.

Internal software programmable weak pull-up. Serial programming clock.

RB7/PGD bit 7 TTL/ST(2) Input/output pin (with interrupt-on-change) or in-circuit debugger pin.

Internal software programmable weak pull-up. Serial programming data.

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode or in-circuit debugger.

3: Low-Voltage ICSP Programming (LVP) is enabled by default which disables the RB3 I/O function. LVP

must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 28-pin and

40-pin mid-range devices.

TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Value on

Value on:

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 all other

POR, BOR

Resets

06h, 106h PORTB RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 xxxx xxxx uuuu uuuu

86h, 186h TRISB PORTB Data Direction Register 1111 1111 1111 1111

81h, 181h OPTION_REG RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

2003 Microchip Technology Inc. DS39582B-page 45

PIC16F87XA

4.3 PORTC and the TRISC Register FIGURE 4-7: PORTC BLOCK DIAGRAM

(PERIPHERAL OUTPUT

PORTC is an 8-bit wide, bidirectional port. The corre-

OVERRIDE) RC<4:3>

sponding data direction register is TRISC. Setting a

TRISC bit (= 1) will make the corresponding PORTC Port/Peripheral Select(2)

pin an input (i.e., put the corresponding output driver in

a High-Impedance mode). Clearing a TRISC bit (= 0) Peripheral Data Out

0

will make the corresponding PORTC pin an output (i.e., VDD

Data Bus

put the contents of the output latch on the selected pin). D Q P

WR Port 1

PORTC is multiplexed with several peripheral functions CK Q

(Table 4-5). PORTC pins have Schmitt Trigger input Data Latch

buffers. I/O

D Q pin(1)

When the I2C module is enabled, the PORTC<4:3>

WR TRIS

pins can be configured with normal I2C levels, or with CK Q N

SMBus levels, by using the CKE bit (SSPSTAT<6>). TRIS Latch

VSS

When enabling peripheral functions, care should be

taken in defining TRIS bits for each PORTC pin. Some RD TRIS

Schmitt

peripherals override the TRIS bit to make a pin an Trigger

output, while other peripherals override the TRIS bit to Peripheral

OE(3) Q D

make a pin an input. Since the TRIS bit override is in Schmitt

Trigger

effect while the peripheral is enabled, read-modify- EN with

write instructions (BSF, BCF, XORWF) with TRISC as the RD Port

SMBus

0 Levels

destination, should be avoided. The user should refer SSP Input

to the corresponding peripheral section for the correct

TRIS bit settings. 1

CKE

FIGURE 4-6: PORTC BLOCK DIAGRAM SSPSTAT<6>

(PERIPHERAL OUTPUT

Note 1: I/O pins have diode protection to VDD and VSS.

OVERRIDE) RC<2:0>, 2: Port/Peripheral Select signal selects between port data

RC<7:5> and peripheral output.

3: Peripheral OE (Output Enable) is only activated if

Peripheral Select is active.

Port/Peripheral Select(2)

Peripheral Data Out

0 VDD

Data Bus

D Q

P

WR Port CK Q 1

Data Latch

I/O

D Q pin(1)

WR TRIS CK Q N

TRIS Latch

VSS

RD TRIS

Schmitt

Trigger

Peripheral

OE(3) Q D

EN

RD Port

Peripheral Input

Note 1: I/O pins have diode protection to VDD and VSS.

2: Port/Peripheral Select signal selects between port

data and peripheral output.

3: Peripheral OE (Output Enable) is only activated if

Peripheral Select is active.

DS39582B-page 46 2003 Microchip Technology Inc.

PIC16F87XA

TABLE 4-5: PORTC FUNCTIONS

Name Bit# Buffer Type Function

RC0/T1OSO/T1CKI bit 0 ST Input/output port pin or Timer1 oscillator output/Timer1 clock input.

RC1/T1OSI/CCP2 bit 1 ST Input/output port pin or Timer1 oscillator input or Capture2 input/

Compare2 output/PWM2 output.

RC2/CCP1 bit 2 ST Input/output port pin or Capture1 input/Compare1 output/

PWM1 output.

RC3/SCK/SCL bit 3 ST RC3 can also be the synchronous serial clock for both SPI and

I2C modes.

RC4/SDI/SDA bit 4 ST RC4 can also be the SPI data in (SPI mode) or data I/O (I2C mode).

RC5/SDO bit 5 ST Input/output port pin or Synchronous Serial Port data output.

RC6/TX/CK bit 6 ST Input/output port pin or USART asynchronous transmit or

synchronous clock.

RC7/RX/DT bit 7 ST Input/output port pin or USART asynchronous receive or

synchronous data.

Legend: ST = Schmitt Trigger input

TABLE 4-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

Value on

Value on:

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 all other

POR, BOR

Resets

07h PORTC RC7 RC6 RC5 RC4 RC3 RC2 RC1 RC0 xxxx xxxx uuuu uuuu

87h TRISC PORTC Data Direction Register 1111 1111 1111 1111

Legend: x = unknown, u = unchanged

2003 Microchip Technology Inc. DS39582B-page 47

PIC16F87XA

4.4 PORTD and TRISD Registers FIGURE 4-8: PORTD BLOCK DIAGRAM

(IN I/O PORT MODE)

Note: PORTD and TRISD are not implemented

on the 28-pin devices. Data Data Latch

Bus D Q

PORTD is an 8-bit port with Schmitt Trigger input

WR I/O pin(1)

buffers. Each pin is individually configurable as an input Port

CK

or output.

PORTD can be configured as an 8-bit wide TRIS Latch

microprocessor port (Parallel Slave Port) by setting D Q

control bit, PSPMODE (TRISE<4>). In this mode, the WR

input buffers are TTL. TRIS Schmitt

CK

Trigger

Input

Buffer

RD

TRIS

Q D

ENEN

RD Port

Note 1: I/O pins have protection diodes to VDD and VSS.

TABLE 4-7: PORTD FUNCTIONS

Name Bit# Buffer Type Function

RD0/PSP0 bit 0 ST/TTL(1) Input/output port pin or Parallel Slave Port bit 0.

RD1/PSP1 bit 1 ST/TTL(1) Input/output port pin or Parallel Slave Port bit 1.

RD2/PSP2 bit2 ST/TTL(1) Input/output port pin or Parallel Slave Port bit 2.

RD3/PSP3 bit 3 ST/TTL(1) Input/output port pin or Parallel Slave Port bit 3.

RD4/PSP4 bit 4 ST/TTL(1) Input/output port pin or Parallel Slave Port bit 4.

RD5/PSP5 bit 5 ST/TTL(1) Input/output port pin or Parallel Slave Port bit 5.

(1)

RD6/PSP6 bit 6 ST/TTL Input/output port pin or Parallel Slave Port bit 6.

RD7/PSP7 bit 7 ST/TTL(1) Input/output port pin or Parallel Slave Port bit 7.

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

TABLE 4-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

Value on

Value on:

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 all other

POR, BOR

Resets

08h PORTD RD7 RD6 RD5 RD4 RD3 RD2 RD1 RD0 xxxx xxxx uuuu uuuu

88h TRISD PORTD Data Direction Register 1111 1111 1111 1111

89h TRISE IBF OBF IBOV PSPMODE — PORTE Data Direction Bits 0000 -111 0000 -111

Legend: x = unknown, u = unchanged, - = unimplemented, read as ‘0’. Shaded cells are not used by PORTD.

DS39582B-page 48 2003 Microchip Technology Inc.

You might also like

- Apple Macbook Pro A1286 (820-2850, K18) PDFDocument101 pagesApple Macbook Pro A1286 (820-2850, K18) PDFPKGR100% (4)

- AC 310 Service Manual-V1.0Document65 pagesAC 310 Service Manual-V1.0Martín OsorioNo ratings yet

- PIC16F87X: 3.0 I/O PortsDocument6 pagesPIC16F87X: 3.0 I/O PortsMenad SalahNo ratings yet

- PIC16F87XA: 4.5 PORTE and TRISE RegisterDocument5 pagesPIC16F87XA: 4.5 PORTE and TRISE Registervitor valeNo ratings yet

- PIC PortsDocument4 pagesPIC PortsPranav vigneshNo ratings yet

- Unit IIDocument23 pagesUnit IIomgunjal85No ratings yet

- 1F - Sot 23 6Document14 pages1F - Sot 23 6freddyNo ratings yet

- MDT2051Document13 pagesMDT2051Tarzan JoeNo ratings yet

- TelemeterDocument5 pagesTelemeterpursito pursitoNo ratings yet

- w65c21 661Document21 pagesw65c21 661hiren parikhNo ratings yet

- Parallel Port I/ODocument41 pagesParallel Port I/OvestereverNo ratings yet

- DatasheetDocument24 pagesDatasheetcho1989No ratings yet

- B Cahua, SN Power, 2013-06-04, G1, 50111027, C-INST - En.Document1 pageB Cahua, SN Power, 2013-06-04, G1, 50111027, C-INST - En.Alberto VegaNo ratings yet

- Microcontroller & Embedded Systems Lab Manual Exp.1,2,3Document11 pagesMicrocontroller & Embedded Systems Lab Manual Exp.1,2,3Akanksha DixitNo ratings yet

- IC200ACC415 DS RS232 RS485 Interface Adapter VersaMaxMicroNano GFK1834 2002Document1 pageIC200ACC415 DS RS232 RS485 Interface Adapter VersaMaxMicroNano GFK1834 2002jav_08No ratings yet

- GE Fanuc CMMDocument6 pagesGE Fanuc CMMmarcosNo ratings yet

- Páginas Extraídas de Manual - MX2Document8 pagesPáginas Extraídas de Manual - MX2Anonymous 97JlpvN4No ratings yet

- RT9088ADocument11 pagesRT9088AБахтиёр БехбудовNo ratings yet

- General Description: P. 1 2003/5 Ver. 1.7Document14 pagesGeneral Description: P. 1 2003/5 Ver. 1.7yeni biriNo ratings yet

- 06,250 (-1), 260 To 240 RS-232 Communications Wiring Diagram: TechnotesDocument1 page06,250 (-1), 260 To 240 RS-232 Communications Wiring Diagram: TechnoteswarwarNo ratings yet

- Programmable Peripheral Interface 8255Document6 pagesProgrammable Peripheral Interface 8255AnkurNo ratings yet

- TDI TDO ISP Connector Target Device Target SystemDocument2 pagesTDI TDO ISP Connector Target Device Target SystembrahimNo ratings yet

- Data SheetDocument22 pagesData SheetJoel Bbc SangPengembala KambingNo ratings yet

- 8-Bit Microcontroller With 20K Bytes Flash AT89LV55: FeaturesDocument24 pages8-Bit Microcontroller With 20K Bytes Flash AT89LV55: FeaturesRenato HernandezNo ratings yet

- Irl530Nspbf Irl530Nlpbf: Lead-FreeDocument11 pagesIrl530Nspbf Irl530Nlpbf: Lead-FreePaulo SilvaNo ratings yet

- Industrial DIN Rail Mounted Optically Isolated RS-232 To RS-422/485 ConverterDocument3 pagesIndustrial DIN Rail Mounted Optically Isolated RS-232 To RS-422/485 ConverterÁgost VitaNo ratings yet

- HCF4538B: Dual Monostable MultivibratorDocument10 pagesHCF4538B: Dual Monostable MultivibratorHector Rafael MirandaNo ratings yet

- R2S15901SP: Digital Delay IC For "Lip Sync"Document8 pagesR2S15901SP: Digital Delay IC For "Lip Sync"ahmedNo ratings yet

- PORTBDocument1 pagePORTBkihobod876No ratings yet

- Mitsubishi FX5U: HMI SettingDocument5 pagesMitsubishi FX5U: HMI SettingmbgprsmsNo ratings yet

- Keyence KV/KZ Series Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualDocument3 pagesKeyence KV/KZ Series Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualryoNo ratings yet

- MDT10P72: 1. General DescriptionDocument21 pagesMDT10P72: 1. General DescriptioniukhanNo ratings yet

- General Description: 8bit M Icrocontroller With ADCDocument50 pagesGeneral Description: 8bit M Icrocontroller With ADCcesar monasterioNo ratings yet

- Area13-IO LIST-R2Document33 pagesArea13-IO LIST-R2Hân TiênNo ratings yet

- More PIC Programming: Serial and Parallel Data Transfer External Busses Analog To Digital ConversionDocument28 pagesMore PIC Programming: Serial and Parallel Data Transfer External Busses Analog To Digital ConversionLuckyBlueNo ratings yet

- I/O Ports in AVR Microcontrollers: Sepehr NaimiDocument49 pagesI/O Ports in AVR Microcontrollers: Sepehr NaimiAbdulla AshoorNo ratings yet

- PIC16F628Document30 pagesPIC16F628Prince YehyaNo ratings yet

- Adf4113 Ic PDFDocument28 pagesAdf4113 Ic PDFSuresh SolletiiNo ratings yet

- PIC16F87XA: 3.7 Protection Against Spurious Write 3.8 Operation During Code-ProtectDocument5 pagesPIC16F87XA: 3.7 Protection Against Spurious Write 3.8 Operation During Code-Protectvitor valeNo ratings yet

- Toshiba T SeriesDocument4 pagesToshiba T Seriesthomi dhiaNo ratings yet

- Uc3863 Utc U863 PDFDocument9 pagesUc3863 Utc U863 PDFShailesh VajaNo ratings yet

- VL393T2863M E6sDocument10 pagesVL393T2863M E6sNguyễn Công CườngNo ratings yet

- Gw1102-2di (3in1) QigDocument3 pagesGw1102-2di (3in1) QigTam DuongNo ratings yet

- PIC16F87XA: TABLE 1-2: Pic16F873A/876A Pinout Description (Continued)Document5 pagesPIC16F87XA: TABLE 1-2: Pic16F873A/876A Pinout Description (Continued)vitor valeNo ratings yet

- RT8202AGQWDocument20 pagesRT8202AGQWandi FalikNo ratings yet

- 3 V/5 V, Rail-to-Rail Quad, 8-Bit DAC AD7304/AD7305: Features Functional Block DiagramsDocument20 pages3 V/5 V, Rail-to-Rail Quad, 8-Bit DAC AD7304/AD7305: Features Functional Block DiagramsAvs ElectronNo ratings yet

- Mitsubishi FX5UDocument5 pagesMitsubishi FX5UmarioNo ratings yet

- CV512H-U42 Service ManualDocument41 pagesCV512H-U42 Service Manualعاطف شعلانNo ratings yet

- Peak 3A Bus Termination RegulatorDocument12 pagesPeak 3A Bus Termination RegulatormkubawatNo ratings yet

- Digi-Log Reverb Module (Btdr-2) : A Great Digital Reverb Sound That Easily Replaces A Spring Reverberation UnitDocument3 pagesDigi-Log Reverb Module (Btdr-2) : A Great Digital Reverb Sound That Easily Replaces A Spring Reverberation UnitCristobalzqNo ratings yet

- Omron CJ CS CPDocument4 pagesOmron CJ CS CPVu MinhNo ratings yet

- RF Switcher Block Diagram (Dae100929)Document3 pagesRF Switcher Block Diagram (Dae100929)DavidKNo ratings yet

- Rt9008ge Apl5611aci-Trg Apl5611 9008ge 9008 La04 La12 La13 La14 La15 La16 La17 La0 La1Document9 pagesRt9008ge Apl5611aci-Trg Apl5611 9008ge 9008 La04 La12 La13 La14 La15 La16 La17 La0 La1laptophaianhNo ratings yet

- 81r PDFDocument29 pages81r PDFDjalma MotaNo ratings yet

- MDT10P57: 1. General DescriptionDocument13 pagesMDT10P57: 1. General DescriptionJuan Carlos Ramírez LeónNo ratings yet

- Facon FB Series PLC Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualDocument2 pagesFacon FB Series PLC Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualryoNo ratings yet

- Rp130X Series: Low Noise 150ma Ldo RegulatorDocument33 pagesRp130X Series: Low Noise 150ma Ldo RegulatorСергей БрегедаNo ratings yet

- AD009-041 Remote Controller: 1. General DescriptionsDocument14 pagesAD009-041 Remote Controller: 1. General DescriptionsSuchitel DelmondeNo ratings yet

- TL3842PDocument18 pagesTL3842PjoelpalzaNo ratings yet

- Rt913a RichtekDocument11 pagesRt913a RichtekRagavan RagavanNo ratings yet

- Ma Tech StandardsDocument32 pagesMa Tech StandardskareyabrauNo ratings yet

- Case Study:: Why Is Apple Successful?Document1 pageCase Study:: Why Is Apple Successful?AG Atc UumNo ratings yet

- BioTime 8.0Document2 pagesBioTime 8.0Sky ManNo ratings yet

- Circuit Operation: The Combinational Logic Circuitry of The 74181 Integrated Circuit, Which Is A Simple Four-Bit ALUDocument5 pagesCircuit Operation: The Combinational Logic Circuitry of The 74181 Integrated Circuit, Which Is A Simple Four-Bit ALUammarNo ratings yet

- Thread SchedulingDocument38 pagesThread SchedulingmatijahNo ratings yet

- AWS TCO WorkSpacesDocument16 pagesAWS TCO WorkSpacessantuchetuNo ratings yet

- AP Recovery ProcedureDocument2 pagesAP Recovery ProcedureCasandra EdwardsNo ratings yet

- Fujitsu ESPRIMO-Q920Document8 pagesFujitsu ESPRIMO-Q920AlbarianNo ratings yet

- MITSUBISHI QL Structured Mode IEC Programming Manual Common InstructionsDocument942 pagesMITSUBISHI QL Structured Mode IEC Programming Manual Common InstructionsJose Javier PereiraNo ratings yet

- Client 3 - Tech Symposia - Heterogeneous AI On Arm (Taiwan Version v2)Document27 pagesClient 3 - Tech Symposia - Heterogeneous AI On Arm (Taiwan Version v2)Andy WuNo ratings yet

- Excel, One Page, For B2C E-Shops, ZIP 12-02-2017 07-14Document275 pagesExcel, One Page, For B2C E-Shops, ZIP 12-02-2017 07-14Adrian SuciuNo ratings yet

- 48x8 Scrolling Matrix Led Display Using Arduino CoDocument6 pages48x8 Scrolling Matrix Led Display Using Arduino CoJeeva NandhamNo ratings yet

- Lab 31Document13 pagesLab 31ansarirahim1No ratings yet

- UltraSharp 2405FPWDocument2 pagesUltraSharp 2405FPWAlan HannanNo ratings yet

- ALP-Embedded LabDocument5 pagesALP-Embedded LabRuthvik ThumuluriNo ratings yet

- 6TH Semester MP Lab Manual 2017 - 3 PDFDocument85 pages6TH Semester MP Lab Manual 2017 - 3 PDFAman SrivastavNo ratings yet

- Pegatron H24Z (Asus F82)Document58 pagesPegatron H24Z (Asus F82)franlc1No ratings yet

- LTO3Document46 pagesLTO3Marius Iulian RosuNo ratings yet

- The Intel Microprocessors Barry B Brey Some Problems With AnswersDocument3 pagesThe Intel Microprocessors Barry B Brey Some Problems With Answersfoggybluue67% (3)

- DEXcam 3 SpecsDocument2 pagesDEXcam 3 SpecsHenryScheinDentalNo ratings yet

- Features:: All-in-One Biometric Security Advanced SolutionsDocument3 pagesFeatures:: All-in-One Biometric Security Advanced SolutionsAlbert Hauw CeNo ratings yet

- Guide UART Flash SKR V1.3 or SKR V1.4 or SKR V1.4 TURBO Using USB To TTL Adapter Using Windows 10Document4 pagesGuide UART Flash SKR V1.3 or SKR V1.4 or SKR V1.4 TURBO Using USB To TTL Adapter Using Windows 10nestor parianiNo ratings yet

- Aspire 5745 PDFDocument233 pagesAspire 5745 PDFRoberto Rodriguez PinedaNo ratings yet

- Journal 0144Document20 pagesJournal 0144Nacer KhoulaleneNo ratings yet

- Ipmiutil User GuideDocument127 pagesIpmiutil User Guidesatish_pup3177No ratings yet

- M-Audio ProFire 2626Document51 pagesM-Audio ProFire 2626Katy FonsecaNo ratings yet

- CPU Suppor List H110Document2 pagesCPU Suppor List H110readersNo ratings yet

- Activity 2 Computer SpecificationsDocument5 pagesActivity 2 Computer Specificationsloraine jenn rososNo ratings yet