0% found this document useful (0 votes)

52 views22 pagesSimple Processor Design with J Component

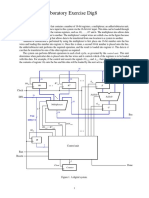

The document describes the design of a simple processor with Verilog code. It includes the design of a multiplexer, control unit and other submodules. Block diagrams and Verilog code for the submodules like multiplexer, adder/subtractor and registers are provided. The main module integrates these submodules according to the control signals from the control unit finite state machine.

Uploaded by

AMIT VERMACopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

52 views22 pagesSimple Processor Design with J Component

The document describes the design of a simple processor with Verilog code. It includes the design of a multiplexer, control unit and other submodules. Block diagrams and Verilog code for the submodules like multiplexer, adder/subtractor and registers are provided. The main module integrates these submodules according to the control signals from the control unit finite state machine.

Uploaded by

AMIT VERMACopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd