Professional Documents

Culture Documents

01-EE001-3-2-AE-FE-QP

Uploaded by

Mohamed AltijaniCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

01-EE001-3-2-AE-FE-QP

Uploaded by

Mohamed AltijaniCopyright:

Available Formats

EE001-3-2-AE Final Exam Page 1 of 5

MODULE DESCRIPTOR VERSION: VE1

No. Course Learning Outcomes Assessments

1 Interpret the design of analogue circuits. (C3, PLO2) Final Exam

2 Investigate the characteristics of analogue circuits. (C4, Group Assignment

PLO4)

3 Exemplify the ability to work effectively in a group on Group Assignment

analogue circuit design problems. (A5, PLO9)

No. Asses Question vs. Taxonomy

sment Cognitive Level Psychomotor Affective

Quest Level Level

ion

1 2 3 4 5 6 1 2 3 4 5 6 7 1 2 3 4 5

Q1 a) 8m c) 6m

b) 3m e) 5m

d) 3m

Q2 a) 2m b) 6m

c) 5m d) 6m

e) 6m

Q3 a)i) 5m b)iii)

LO1

a)ii) 4m 2m

b)i) 11m

b)ii) 3m

Q4 a)ii) 2m a)i) 8m

b)i) 10m

b)ii) 5m

POM 61% 19% 2% 18%

APU Level 2 Asia Pacific University of Technology and Innovation YYYYMMDD

EE001-3-2-AE Final Exam Page 2 of 5

This paper contains 4 questions.

Answer ALL questions.

This paper carries 100 marks.

1.

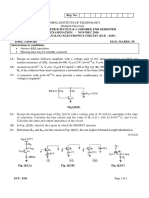

Figure Q1 shows a common-emitter amplifier. The gain of the transistor Q1 is given by β =

100, the resistances are given by RS = 500 Ω, R1 = 1 MΩ, R2 = 1 MΩ, RC = 10 kΩ, RE = 10 kΩ

and RL = 1 kΩ, and the internal capacitances are given by Cμ = 2 pF and Cπ = 20 pF.

Assume that the internal resistances rb = 10 Ω, rμ = ∞, ro = ∞ and the external capacitances CS,

CE and CL are large.

Figure Q1

a) If the supply voltage, VCC, is 12 V, compute the collector current, IC, hybrid-π parameters,

gm and rπ for the transistor Q1. [8 Marks]

b) Sketch the small-signal equivalent circuit in a form suitable for high frequency analysis.

[3 Marks]

c) By using Miller’s theorem, calculate the internal capacitances C1 and C2. [6 Marks]

d) Sketch the small-signal equivalent circuit again which includes the capacitances C1 and C2.

[3 Marks]

e) Using open-circuit time constant method, calculate the 3dB upper corner frequency, fH.

[5 Marks]

APU Level 2 Asia Pacific University of Technology and Innovation YYYYMMDD

EE001-3-2-AE Final Exam Page 3 of 5

2.

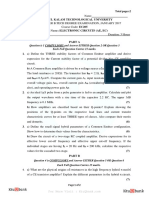

Figure Q2 shows a multi-stage common-emitter amplifier with feedback. Each transistor has a

forward current gain, β = 100. Assume that the hybrid-π resistances rb = 0, rµ = ∞ and ro = ∞.

At signal frequency, the coupling capacitances and bypass capacitances have zero reactance.

Figure Q2

a) Interpret the type of feedback topology used in the circuit shown in Figure Q2.

[2 Marks]

b) Using the appropriate two-port parameters, develop the expressions for the feedback factor

and loading impedances or admittances of the feedback network. [6 Marks]

c) Sketch the small-signal equivalent circuit of the amplifier in a form suitable for

determining the mid-band open loop gain. Include the loading effects of the feedback

network. [5 Marks]

d) Based on the circuit in (c), develop an expression for the mid-band open loop gain.

[6 Marks]

e) Given that the loop gain, βA of the amplifier is large, develop the expressions for the closed-

loop gain and closed-loop input impedance of the amplifier. [6 Marks]

APU Level 2 Asia Pacific University of Technology and Innovation YYYYMMDD

EE001-3-2-AE Final Exam Page 4 of 5

3.

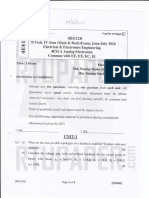

a) Consider a basic inverting op-amp with closed-loop gain of ACL = -10, power supply of

±15V and the input voltage, vs(t) = 2cos(5t).

i) Sketch the expected output voltage, vo (t ) , waveform. [5 Marks]

ii) Interpret the issue faced by this type of op-amp and calculate the maximum input

voltage for the op-amp. [4 Marks]

b) Figure Q3 shows a difference amplifier where the resistor values are given by R1 = 50 kΩ,

R2 = 100 kΩ and R3 = 50 kΩ. In the non-ideal case the op-amp has the following DC

imperfections:

Input bias current : IB = 100 nA

Input offset current : Iio = ±20 nA

Input offset voltage : Vio = ±8 mV

Figure Q3

i) Produce the expressions for the output offset voltage VOS due to the input offset

currents IB+, IB- and input offset voltage Vio. [11 Marks]

ii) Compute the worst-case output offset voltage. [3 Marks]

iii) Explain the reasons for which causes the DC imperfections as mentioned above in

an op-amp. [2 Marks]

APU Level 2 Asia Pacific University of Technology and Innovation YYYYMMDD

EE001-3-2-AE Final Exam Page 5 of 5

4.

a) Figure Q4(a) shows the realisation of a Schmitt trigger. Assume that the saturation voltages

of the op-amp to be Vout = ±Vm.

Figure Q4(a)

i) With aid of equations, outline the transfer characteristics (Vout as a function of Vin).

[8 Marks]

ii) Produce the expression for hysteresis voltage, VH. [2 Marks]

b) By adding a RC feedback circuit between the inverting input and the output of the Schmitt

trigger, a square-wave generator can be formed as shown in Figure Q4(b).

i) With aid of diagrams, interpret the operation of the square-wave generator.

[10 Marks]

ii) Produce the equations for charging intervals (T1) and discharging intervals (T2),

showing the generated square waves are symmetrical. [5 Marks]

Figure Q4(b)

END OF FINAL EXAM

APU Level 2 Asia Pacific University of Technology and Innovation YYYYMMDD

You might also like

- Assignment 3Document1 pageAssignment 3Robert Tatenda ZataNo ratings yet

- Wireless Communications - T. L. Singal PDFDocument69 pagesWireless Communications - T. L. Singal PDFSatya Narayana43% (7)

- Answer Any Two Full Questions, Each Carries 15 Marks.: Reg No.: - NameDocument2 pagesAnswer Any Two Full Questions, Each Carries 15 Marks.: Reg No.: - Namesheena mNo ratings yet

- I C Systems (ECE-2202) RCS (Makeup)Document2 pagesI C Systems (ECE-2202) RCS (Makeup)1x1pNo ratings yet

- EEE 2202 ANALOGUE ELECTRONICS I - July17 - ExamDocument5 pagesEEE 2202 ANALOGUE ELECTRONICS I - July17 - Exameric wahomeNo ratings yet

- SE 2008 Electronics E&TCDocument63 pagesSE 2008 Electronics E&TCManish kumar 50No ratings yet

- R.D. Enggineering College, Duhai, GZB: Deptt. of Electronics & Communication EnggDocument3 pagesR.D. Enggineering College, Duhai, GZB: Deptt. of Electronics & Communication EnggMohan SinghNo ratings yet

- Linear Ic ApplicationsDocument4 pagesLinear Ic ApplicationsChinnu Cutiee28No ratings yet

- Enggzc112 May05 An PDFDocument3 pagesEnggzc112 May05 An PDFdharmendra_kanthariaNo ratings yet

- r05210404 Electronic Circuit Analysis November 2008Document8 pagesr05210404 Electronic Circuit Analysis November 2008Tamire santhosh mohanNo ratings yet

- Electronic Devices and Circuits Oct-Nov 2019Document7 pagesElectronic Devices and Circuits Oct-Nov 2019Venkata LalithaNo ratings yet

- rr12302 Electrical and Electronics EngineeringDocument12 pagesrr12302 Electrical and Electronics EngineeringSRINIVASA RAO GANTANo ratings yet

- Digital Pulse and Circuits Exam QuestionsDocument8 pagesDigital Pulse and Circuits Exam QuestionsKota divyasreeNo ratings yet

- 07a3ec14 Electronic Circuit AnalysisDocument8 pages07a3ec14 Electronic Circuit AnalysisTamire santhosh mohan100% (1)

- Analog Electronic Circuits (ECE - 2101) RCSDocument3 pagesAnalog Electronic Circuits (ECE - 2101) RCSdeevNo ratings yet

- EEE 207 Final Summer 2015Document3 pagesEEE 207 Final Summer 2015rj OpuNo ratings yet

- Basic Electronics (ECE 1051)Document2 pagesBasic Electronics (ECE 1051)aryansorout1612No ratings yet

- Network Analysis Exam QuestionsDocument8 pagesNetwork Analysis Exam Questionschandra sekharNo ratings yet

- Analog Electronics Circuit (ECE - 2101) (Make Up) RCSDocument2 pagesAnalog Electronics Circuit (ECE - 2101) (Make Up) RCSdeevNo ratings yet

- Kbhilai School of Engineering, DurgDocument4 pagesKbhilai School of Engineering, DurgBhupatimtechNo ratings yet

- ELECTRICAL CIRCUIT ANALYSIS-II Oct-Nov 2020Document2 pagesELECTRICAL CIRCUIT ANALYSIS-II Oct-Nov 2020Vedula SudhakarNo ratings yet

- WWW Manaresults Co inDocument8 pagesWWW Manaresults Co inhidhanaaNo ratings yet

- WWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, MCT)Document2 pagesWWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, MCT)pramodNo ratings yet

- IC Design and Applications Exam GuideDocument2 pagesIC Design and Applications Exam GuidevijaykumarNo ratings yet

- 2020 FinalDocument3 pages2020 FinalBen ChouNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument4 pages3 Hours / 70 Marks: Seat No58 EX Ramawat PankajNo ratings yet

- Campusexpress - Co.in: Set No. 1Document8 pagesCampusexpress - Co.in: Set No. 1skssush100% (1)

- UOM Electrical Engineering ExamDocument7 pagesUOM Electrical Engineering ExamchetsNo ratings yet

- KTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedDocument16 pagesKTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedsunNo ratings yet

- B.Tech 3rd Sem Analog Circuits ECEN 2101 NotesDocument4 pagesB.Tech 3rd Sem Analog Circuits ECEN 2101 NotesVikash KumarNo ratings yet

- Pulse and Digital CircuitsDocument8 pagesPulse and Digital CircuitsLalith KumarNo ratings yet

- Analog Circuits (Ecen 2101)Document5 pagesAnalog Circuits (Ecen 2101)sumitbhuia10No ratings yet

- Sample Question Paper Applied ElectronicsDocument4 pagesSample Question Paper Applied Electronicssachin barge100% (1)

- Semester-1 - Chemistry Stream - Mid+end PaperDocument15 pagesSemester-1 - Chemistry Stream - Mid+end PaperGopiNo ratings yet

- Linear and Digital Ic Applications RRDocument8 pagesLinear and Digital Ic Applications RRNizam Institute of Engineering and Technology LibraryNo ratings yet

- ELEC2001 Analogue II April2013Document6 pagesELEC2001 Analogue II April2013Christian PatriceNo ratings yet

- Answer Answer All Questions, Each Carries 3 MarksDocument2 pagesAnswer Answer All Questions, Each Carries 3 MarksAjayShankarNo ratings yet

- EE402 Jan2006Document4 pagesEE402 Jan2006Amazing ElectricalNo ratings yet

- SINGAPORE POLYTECHNIC 2018/2019 MID-SEMESTER TWO TEST ELECTRICAL PRINCIPLES (ELPDocument8 pagesSINGAPORE POLYTECHNIC 2018/2019 MID-SEMESTER TWO TEST ELECTRICAL PRINCIPLES (ELPLimNo ratings yet

- r05221101 Pulse and Digital CircuitsDocument9 pagesr05221101 Pulse and Digital CircuitssridiviNo ratings yet

- Analog Electronic Circuit DesignDocument2 pagesAnalog Electronic Circuit DesignSPANDANNo ratings yet

- APR2013P21Document63 pagesAPR2013P21qsashutoshNo ratings yet

- Ae53 Ac53 At53Document4 pagesAe53 Ac53 At53M Taher BamyaniNo ratings yet

- Analogue ElectronicsDocument7 pagesAnalogue ElectronicsrizwanahbNo ratings yet

- eca Q 2Document1 pageeca Q 2Shiva GlennNo ratings yet

- Basic Electronics Engineering I SemDocument3 pagesBasic Electronics Engineering I Semshubhambani45No ratings yet

- WWW - Manaresults.co - In: Linear Ic ApplicationsDocument1 pageWWW - Manaresults.co - In: Linear Ic Applicationst chinnaNo ratings yet

- USN 16EC32 - Analog Electronics Exam QuestionsDocument3 pagesUSN 16EC32 - Analog Electronics Exam Questionssantosh sarafNo ratings yet

- Analysis of Electrical Circuit ExamsDocument8 pagesAnalysis of Electrical Circuit ExamsSd KhadarNo ratings yet

- Total Pages: Total Pages: 3: Answer Answer Any Two Full Questions, Each Carries 15 Marks MarksDocument3 pagesTotal Pages: Total Pages: 3: Answer Answer Any Two Full Questions, Each Carries 15 Marks MarksanuNo ratings yet

- Birla Institute Electrical Exam QuestionsDocument3 pagesBirla Institute Electrical Exam Questionsdharmendra_kanthariaNo ratings yet

- Edc 7Document8 pagesEdc 729viswa12100% (1)

- Eet205 Analog Electronics, December 2021Document3 pagesEet205 Analog Electronics, December 2021Midun RamkumarNo ratings yet

- Analog Electronics exam questionsDocument4 pagesAnalog Electronics exam questionsrishabh jhalaniNo ratings yet

- WWW - Manaresults.Co - In: Code No: R161208Document15 pagesWWW - Manaresults.Co - In: Code No: R161208NVS TejaswiNo ratings yet

- Electric Circuit Exam INIESATDocument2 pagesElectric Circuit Exam INIESATMBIEDA NGOMEGNI FRANK GAETANNo ratings yet

- WWW - Manaresults.Co - In: Linear Ic ApplicationsDocument1 pageWWW - Manaresults.Co - In: Linear Ic Applicationst chinnaNo ratings yet

- Phy3622 11 Nor 2018Document5 pagesPhy3622 11 Nor 2018Jay KayyNo ratings yet

- EC-401 Theory Exam QuestionsDocument19 pagesEC-401 Theory Exam QuestionsDeepak SahuNo ratings yet

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesFrom EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNo ratings yet

- Electromagnetic Compatibility (EMC) Design and Test Case AnalysisFrom EverandElectromagnetic Compatibility (EMC) Design and Test Case AnalysisNo ratings yet

- 02-EE044-3-3-THT-IA-MSDocument4 pages02-EE044-3-3-THT-IA-MSMohamed AltijaniNo ratings yet

- 1. IntroductionDocument9 pages1. IntroductionMohamed AltijaniNo ratings yet

- 1. IntroductionDocument9 pages1. IntroductionMohamed AltijaniNo ratings yet

- 1. IntroductionDocument9 pages1. IntroductionMohamed AltijaniNo ratings yet

- Ale Gpon Nokia Ont G 010s A Datasheet enDocument3 pagesAle Gpon Nokia Ont G 010s A Datasheet enMukesh VermaNo ratings yet

- Slewing Controller SpecificationDocument7 pagesSlewing Controller SpecificationMohamed ElsayedNo ratings yet

- Quotation for Networking EquipmentDocument3 pagesQuotation for Networking EquipmentMom SovanNo ratings yet

- Unit 2: Electronic Measurement For Measuring Basic ParametersDocument16 pagesUnit 2: Electronic Measurement For Measuring Basic ParametersSiva Sai Ram100% (1)

- Mitigation of Power Quality Problems Using Unified Power Quality Conditioner in Paper Industries. A Case of Mufindi Paper Mills IJERTV6IS050103 PDFDocument6 pagesMitigation of Power Quality Problems Using Unified Power Quality Conditioner in Paper Industries. A Case of Mufindi Paper Mills IJERTV6IS050103 PDFGazal100% (1)

- Minor ProjectDocument34 pagesMinor ProjectDiksha SharmaNo ratings yet

- Easergy P3 Protection Relays - REL52009Document6 pagesEasergy P3 Protection Relays - REL52009Selva SugumaranNo ratings yet

- Control commands for Panasonic projectorsDocument1 pageControl commands for Panasonic projectors1015646541610312No ratings yet

- EtherWAN EX17162A User ManualDocument2 pagesEtherWAN EX17162A User ManualJMAC SupplyNo ratings yet

- EE402 Answers Jan06Document12 pagesEE402 Answers Jan06ankurgoel1975No ratings yet

- commandsBUC AppnoteDocument48 pagescommandsBUC AppnoteradamNo ratings yet

- SpecDocument318 pagesSpechomelessghostNo ratings yet

- Your Electric Vehicle: Charging Solutions For Electric Vehicles or Plug-In HybridsDocument12 pagesYour Electric Vehicle: Charging Solutions For Electric Vehicles or Plug-In HybridsBhanu PandeyNo ratings yet

- 10 October 1962Document100 pages10 October 1962Paul GrahamNo ratings yet

- Design and Development of PCB Milling MachineDocument6 pagesDesign and Development of PCB Milling Machinesjcit.bracNo ratings yet

- Peter B. Aronhime, F. William Stephenson (Auth.) - Analog Signal Processing-Springer US (1994) PDFDocument97 pagesPeter B. Aronhime, F. William Stephenson (Auth.) - Analog Signal Processing-Springer US (1994) PDFRazvan CaldararuNo ratings yet

- RX8900SA - en Application ManualDocument57 pagesRX8900SA - en Application ManualYong Jian ShenNo ratings yet

- MQTT & IOT Based Control and Monitoring of Smart Green HouseDocument6 pagesMQTT & IOT Based Control and Monitoring of Smart Green HousebassbngNo ratings yet

- Unit Test - I B.Tech. - ECE: School of Electrical & Communication Department of EceDocument1 pageUnit Test - I B.Tech. - ECE: School of Electrical & Communication Department of EceNithya VelamNo ratings yet

- 190-00356-30 Displays Addendum PDFDocument50 pages190-00356-30 Displays Addendum PDFkirito asunameNo ratings yet

- Lesson 4 - Coding of Text, Voice, Image, and VideoDocument11 pagesLesson 4 - Coding of Text, Voice, Image, and VideoLee Heng YewNo ratings yet

- Using Practical Examples in Teaching Digital Logic Design v5 PDFDocument14 pagesUsing Practical Examples in Teaching Digital Logic Design v5 PDFprashantvlsiNo ratings yet

- 27012472-MIMO Wall Mount Antenna DatasheetDocument1 page27012472-MIMO Wall Mount Antenna DatasheetСергей МирошниченкоNo ratings yet

- SIMULIA EM EMC For Electonics DatasheetDocument3 pagesSIMULIA EM EMC For Electonics Datasheetkutlu küçükvuralNo ratings yet

- DCFMDocument8 pagesDCFMKavi S.KNo ratings yet

- 5G Deployment Options Keysight May19Document8 pages5G Deployment Options Keysight May19Muhammad KaleemNo ratings yet

- Motion Sensor Using PirDocument10 pagesMotion Sensor Using PirSHRUTI MOONNo ratings yet

- LTspice tutorial - Basic circuits analysis and RC time constantsDocument22 pagesLTspice tutorial - Basic circuits analysis and RC time constantsSmit PrajapatiNo ratings yet