Professional Documents

Culture Documents

BCS302 Unit-3 (Part-III)

Uploaded by

dp06vnsCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BCS302 Unit-3 (Part-III)

Uploaded by

dp06vnsCopyright:

Available Formats

PSIT, Kanpur

Computer Organization and Architecture (BCS302)

Unit - 3 (Part – III)

Horizontal & Vertical Microprogramming

Pipelining

Horizontal & Vertical Microprogramming

Relative differences between Horizontal & Vertical Microprogramming are listed below:

Compiled by- Durgesh Pandey (CSED)

PSIT, Kanpur

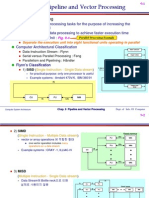

Pipelining

To improve the performance of CPU, we have two options:

1. Improve the hardware by introducing faster circuits

2. Arrange the hardware such that more than one operation can be performed at the same time.

Pipelining is a technique of decomposing a sequential process into suboperations, with each sub-process being executed

in a special dedicated segment that operates concurrently with all other segments.

Pipelining is a process of arrangement of hardware elements of the CPU such that its overall performance is increased by

the simultaneous execution of more than one instruction.

For example, suppose that we want to perform the combined multiply and add operations with a stream of numbers.

Ai * B i + Ci for i = 1, 2, 3, . . . , 7

Each suboperation is to be implemented in a segment within a pipeline. Each segment has one or two registers and a

combinational circuit as shown in Fig. 9-2. The multiplier and adder are combinational circuits. The suboperations performed in

each segment of the pipeline are as follows:

R1 ← Ai, R2 ← Bi Input Ai and Bi

R3 ← R1 * R2, R4 ← Ci Multiply and input Ci

R5 ← R3 + R4 Add Ci to product

Figure 9-2 Example of pipeline processing

Ai Bi Ci

NOTE: The five registers are loaded with new data every clock pulse. The effect of each clock is shown in the following table

(*MM Table 9-1).

TABLE 9-1 Content of Registers in Pipeline (Example)

The first clock pulse transfers A1 and B1 into R1 and R2.

The second clock pulse transfers the product of R1 and R2 into R3 and C1 into R4. The same clock pulse transfers A2 and B2

into R1 and R2.

The third clock pulse operates on all three segments simultaneously i.e. it takes three clock pulses to fill up the pipe and

retrieve the first output from R5.

From there on, each clock produces a new output and moves the data one step down the pipeline; as long as new input data

flow into the system.

When no more input data are available, the clock must continue until the last output emerges out of the pipeline.

Compiled by- Durgesh Pandey (CSED)

PSIT, Kanpur

The general structure of a four-segment pipeline is illustrated in *MM Fig. 9-3. Each segment consists of:

A combinational circuit Si that performs a suboperation over the data stream flowing through the pipe and

Separated by registers Ri that holds the intermediate results between the stages.

Figure 9-3 Four-segment pipeline

Information flows between adjacent stages under the control of a common clock applied to all the registers simultaneously.

The behavior of a pipeline can be illustrated with a space-time diagram that shows the segment utilization as a function of

time.

The space-time diagram of a four-segment pipeline is demonstrated in the following figure (*MM Fig. 9-4).

Figure 9-4 Space-time diagram for pipeline

NOTE: Horizontal axis displays the time in clock cycles and the vertical axis gives the segment number.

We define a task as the total operation performed going through all the segments in the pipeline.

So, the first task T1 is completed after the fourth clock cycle. From then on, the pipe completes a task every clock cycle.

No matter how many segments are there in the system, once the pipeline is full, it takes only one clock period to obtain an

output.

Performance measure

For pipelined architecture,

Consider the case where a k-segment pipeline with a clock cycle time tp is used to execute n tasks.

The first task T1 requires a time = k.tp to complete its operation since there are k segments in the pipe.

The remaining n - 1 tasks, completed after a time = (n - 1).tp (emerge from the pipe at the rate of one task per clock

cycle).

Therefore, to complete n tasks using a k-segment pipeline requires:

Total execution time = [k + (n - 1)].tp

For example, the diagram of *MM Fig. 9-4 shows four segments and six tasks.

The time required to complete all the operations is 4 + (6 - 1) = 9 clock cycles, as indicated in the diagram.

For non-pipelined architecture,

For the same case with a clock cycle time tn

We have,

Total execution time

= Total number of instructions * Time taken to execute one instruction = n.tn

Compiled by- Durgesh Pandey (CSED)

PSIT, Kanpur

Speedup

The speedup of a pipeline processing over an equivalent non-pipeline processing is defined by the ratio

S = n.tn / (k + n - 1).tp

As the number of tasks increases, n becomes much larger than k - 1, and k + n - 1 approaches the value of n.

Under this condition, the speedup becomes S = tn / tp

If we assume that the time it takes to process a task is the same in the pipeline and non-pipeline circuits, we will have

tn = k.tp

Including this assumption, the speedup reduces to

S = k.tp / tp = k

This shows that the theoretical “maximum speedup that a pipeline can provide is k, where k is the number of segments in

the pipeline”.

To clarify the meaning of the speedup ratio, consider the following numerical example.

Question:

A pipeline has 4 segments and executes 100 tasks in sequence with a clock cycle time 20 ns.

1. The pipeline system will take how much total time to complete the execution?

2. What will be the speedup if the time it takes to process the task is the same in the pipeline and non-pipeline

circuits?

Solution:

Given that the time it takes to process a suboperation in each segment be equal to tp = 20 ns. The pipeline has k = 4 segments and

executes n = 100 tasks in sequence.

The pipeline system will take (k + n - 1).tp = (4 + 99) * 20 = 2060 ns to complete.

Answer.

Assuming that tn = k.tp = 4 * 20 = 80 ns,

a non-pipelined system requires n * k.tp = 100 * 80 = 8000 ns to complete the 100 tasks.

The speedup ratio is equal to 8000/2060 = 3 .88. Answer.

As the number of tasks increases, the speedup will approach 4, which is equal to the number of segments in the pipeline.

~~~~~~*****{Ӂ۞Ӂ}*****~~~~~~

Compiled by- Durgesh Pandey (CSED)

You might also like

- Digital Spectral Analysis MATLAB® Software User GuideFrom EverandDigital Spectral Analysis MATLAB® Software User GuideNo ratings yet

- 2.2 Pipelining: AsynchronousDocument24 pages2.2 Pipelining: Asynchronouseshankapur25% (4)

- Practical Guides to Testing and Commissioning of Mechanical, Electrical and Plumbing (Mep) InstallationsFrom EverandPractical Guides to Testing and Commissioning of Mechanical, Electrical and Plumbing (Mep) InstallationsRating: 3.5 out of 5 stars3.5/5 (3)

- Microcontrollers For Embedded Systems Nec022r PDFDocument2 pagesMicrocontrollers For Embedded Systems Nec022r PDFSudhir GoswamiNo ratings yet

- Aca Module 2Document35 pagesAca Module 2Shiva prasad100% (1)

- Pipelining: Improving CPU Performance Through Simultaneous Instruction ExecutionDocument12 pagesPipelining: Improving CPU Performance Through Simultaneous Instruction ExecutionAradhyaNo ratings yet

- Pipeline and Vector ProcessingDocument28 pagesPipeline and Vector ProcessingTerror BladeNo ratings yet

- CAO-II Module 2 CompleteDocument32 pagesCAO-II Module 2 CompleteAsim Arunava Sahoo100% (1)

- Chapter 5 - CO - BIM - IIIDocument7 pagesChapter 5 - CO - BIM - IIIAnkit ShresthaNo ratings yet

- Module 4Document12 pagesModule 4Bijay NagNo ratings yet

- Unit-4 Pipelinie and Vector ProcessingDocument33 pagesUnit-4 Pipelinie and Vector ProcessingMandeepNo ratings yet

- Instruction-Level Parallelism and Its Exploitation: Sources: H&P Appendix C H&P Chapter 3 Previous CS 5375 MaterialDocument104 pagesInstruction-Level Parallelism and Its Exploitation: Sources: H&P Appendix C H&P Chapter 3 Previous CS 5375 Materialharry.cheersNo ratings yet

- Pipeline and Vector Processing ExplainedDocument19 pagesPipeline and Vector Processing ExplainedriyazpashaNo ratings yet

- Ca 6Document19 pagesCa 6SUMAN BROONo ratings yet

- The Optimum Pipeline Depth For A Microprocessor: A. Hartstein and Thomas R. PuzakDocument7 pagesThe Optimum Pipeline Depth For A Microprocessor: A. Hartstein and Thomas R. PuzakSiddharth SinghNo ratings yet

- Pipelining (DSP Implementation) - Wikipedia, The Free EncyclopediaDocument5 pagesPipelining (DSP Implementation) - Wikipedia, The Free EncyclopediaSubanth WiiliamsNo ratings yet

- Pipeline ProcessingDocument28 pagesPipeline Processinganismitaray14No ratings yet

- Uni1-2 PipeliningDocument12 pagesUni1-2 PipeliningAditi VermaNo ratings yet

- ch09 Morris ManoDocument15 pagesch09 Morris ManoYogita Negi RawatNo ratings yet

- Advance Electronics: UnacademyDocument38 pagesAdvance Electronics: UnacademyhemuNo ratings yet

- Pipeline Modeling and Performance AnalysisDocument29 pagesPipeline Modeling and Performance AnalysisalethareeNo ratings yet

- Introduction To MIPS ArchitectureDocument10 pagesIntroduction To MIPS ArchitectureJahanzaib AwanNo ratings yet

- Unit-5 (Coa) NotesDocument33 pagesUnit-5 (Coa) NotesyashNo ratings yet

- CS-421 Parallel Processing Pipeline AnalysisDocument2 pagesCS-421 Parallel Processing Pipeline AnalysisJaweria SiddiquiNo ratings yet

- Unit 4 - P 2Document13 pagesUnit 4 - P 2Sanju SanjayNo ratings yet

- CO Module 5 NotesDocument16 pagesCO Module 5 NotesVarsha S LalapuraNo ratings yet

- CS211 Pipeline Performance ExampleDocument82 pagesCS211 Pipeline Performance ExampleElizabeth AliazNo ratings yet

- UNIT-5: Pipeline and Vector ProcessingDocument63 pagesUNIT-5: Pipeline and Vector ProcessingAkash KankariaNo ratings yet

- Implementation of Fast Fourier Transform (FFT) On FPGA Using Verilog HDLDocument21 pagesImplementation of Fast Fourier Transform (FFT) On FPGA Using Verilog HDLNikitaPrabhu0% (1)

- Chap-10: Speed and EfficiencyDocument29 pagesChap-10: Speed and EfficiencyGuru BalanNo ratings yet

- Pipelining Size and DepthDocument19 pagesPipelining Size and Depthwardabibi69No ratings yet

- Lecture Notes On Parallel Processing PipelineDocument12 pagesLecture Notes On Parallel Processing PipelineYowaraj ChhetriNo ratings yet

- Pipelining Instruction Execution and Cache Memory PoliciesDocument10 pagesPipelining Instruction Execution and Cache Memory PoliciesDinesh DevaracondaNo ratings yet

- Illinois Exam2 Practice Solfa08Document4 pagesIllinois Exam2 Practice Solfa08bittronicNo ratings yet

- Principles of Linear Pipelining: Understanding Performance and ClassificationDocument71 pagesPrinciples of Linear Pipelining: Understanding Performance and Classificationrag28xbox50% (2)

- VI. Implicit Parallelism - Instruction Level VI. Implicit Parallelism Instruction Level Parallelism. Pipeline Superscalar & Vector P ProcessorsDocument26 pagesVI. Implicit Parallelism - Instruction Level VI. Implicit Parallelism Instruction Level Parallelism. Pipeline Superscalar & Vector P Processorstt_aljobory3911No ratings yet

- Vector Processing and PipeliningDocument22 pagesVector Processing and Pipeliningpraveenpin2No ratings yet

- CSC 424 AssignmentDocument8 pagesCSC 424 AssignmentBalsesbiz Consults100% (1)

- Computational foundations of cyber physical systems tutorial on pipelining and memory hierarchy problemsDocument13 pagesComputational foundations of cyber physical systems tutorial on pipelining and memory hierarchy problemsbrahma2deen2chaudharNo ratings yet

- Questions Pool For Distributed SystemsDocument15 pagesQuestions Pool For Distributed SystemsSai MovvaNo ratings yet

- 3.2 Performance EvaluationsDocument18 pages3.2 Performance EvaluationsChetan SolankiNo ratings yet

- Application of Novel Technique in Ripemd-160 Aiming at High-ThroughputDocument4 pagesApplication of Novel Technique in Ripemd-160 Aiming at High-ThroughputKiran GundeNo ratings yet

- Pipelining (DSP Implementation) : ConceptDocument7 pagesPipelining (DSP Implementation) : ConceptLokeshRathorNo ratings yet

- COMPARISON ANALYSIS OF 16-BIT ADDERSDocument3 pagesCOMPARISON ANALYSIS OF 16-BIT ADDERSThành DuongNo ratings yet

- Pipelined MIPS: Why pipelining improves performance and the challenges of implementing pipeliningDocument12 pagesPipelined MIPS: Why pipelining improves performance and the challenges of implementing pipeliningasifsultanNo ratings yet

- Homework3 Solution v2Document41 pagesHomework3 Solution v2razi haiderNo ratings yet

- Car Manufacturing With Three Plants Speed Up For N Inputs in A P-Stage PipelineDocument26 pagesCar Manufacturing With Three Plants Speed Up For N Inputs in A P-Stage PipelineJunior Gomez ContrerasNo ratings yet

- Comparison Analysis of 16-Bit AddersDocument3 pagesComparison Analysis of 16-Bit AddersInternational Jpurnal Of Technical Research And ApplicationsNo ratings yet

- Chapter 10: Pipeline: ObjectivesDocument8 pagesChapter 10: Pipeline: ObjectivesSteffany RoqueNo ratings yet

- An Adaptive Fuzzy Pid Control of Hydro-Turbine Governor: Xiao-Ying Zhang, Ming-Guang ZhangDocument5 pagesAn Adaptive Fuzzy Pid Control of Hydro-Turbine Governor: Xiao-Ying Zhang, Ming-Guang ZhangPadmo PadmundonoNo ratings yet

- Content PDFDocument14 pagesContent PDFrobbyyuNo ratings yet

- Zoom/Online Final - question Q1TITLE: Online Final Q1 PipeliningDocument3 pagesZoom/Online Final - question Q1TITLE: Online Final Q1 PipeliningMuhammad Zahid iqbalNo ratings yet

- Pipelining & Riscs: Pipelining Used Key Implementation Technique To Build Fast Processors. ItDocument6 pagesPipelining & Riscs: Pipelining Used Key Implementation Technique To Build Fast Processors. Itfayzee945150No ratings yet

- Lecture 1Document10 pagesLecture 1Asim Arunava Sahoo100% (1)

- Optimal Circuits For Parallel Multipliers: Paul F. Stelling,,, Charles U. Martel, Vojin G. Oklobdzija,,, and R. RaviDocument13 pagesOptimal Circuits For Parallel Multipliers: Paul F. Stelling,,, Charles U. Martel, Vojin G. Oklobdzija,,, and R. RaviMathew GeorgeNo ratings yet

- Processor Design Using Square Root Carry Select AdderDocument6 pagesProcessor Design Using Square Root Carry Select AdderAJER JOURNALNo ratings yet

- Numerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityFrom EverandNumerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityNo ratings yet

- Spline and Spline Wavelet Methods with Applications to Signal and Image Processing: Volume III: Selected TopicsFrom EverandSpline and Spline Wavelet Methods with Applications to Signal and Image Processing: Volume III: Selected TopicsNo ratings yet

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsFrom EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikNo ratings yet

- BCS302 Unit 3 (Part I)Document7 pagesBCS302 Unit 3 (Part I)dp06vnsNo ratings yet

- BCS302 Unit-3 (Part-II)Document8 pagesBCS302 Unit-3 (Part-II)dp06vnsNo ratings yet

- KCS302-01 (Design of Bus Using MUXs, 3-State Buffers)Document8 pagesKCS302-01 (Design of Bus Using MUXs, 3-State Buffers)dp06vnsNo ratings yet

- KCS302-01 (Microoperations)Document8 pagesKCS302-01 (Microoperations)dp06vnsNo ratings yet

- Power On Sequence GuideDocument8 pagesPower On Sequence GuidedraNo ratings yet

- Lab Session 3: Arithmetic Operations in Assembly LanguageDocument6 pagesLab Session 3: Arithmetic Operations in Assembly LanguageShehzadtajNo ratings yet

- Board PcChips M756LMRT-M756LRT-M756TDocument43 pagesBoard PcChips M756LMRT-M756LRT-M756Tmelecobd0% (1)

- Dell Inspiron 1520 Dafm5bmb6d0 (Cosica-Gilligan UMA) PDFDocument57 pagesDell Inspiron 1520 Dafm5bmb6d0 (Cosica-Gilligan UMA) PDFFausto DavidNo ratings yet

- Asus K8V-MXDocument36 pagesAsus K8V-MXcarmenoltNo ratings yet

- ELEX MCQ-Digital Systems - Principles and ApplicationsDocument253 pagesELEX MCQ-Digital Systems - Principles and ApplicationsJohnPatrickRamirezCuevasNo ratings yet

- At 90 S 851555Document112 pagesAt 90 S 851555mike_helplineNo ratings yet

- Tiva C Series LaunchPadDocument13 pagesTiva C Series LaunchPadVivek ShrigiriNo ratings yet

- Electronic Dice Using At89C2051: IdeasDocument2 pagesElectronic Dice Using At89C2051: IdeaschakralabsNo ratings yet

- ECO Timing Optimization Using Spare CellsDocument31 pagesECO Timing Optimization Using Spare CellsSiva RaoNo ratings yet

- Hikmat o Kalam K Imam Fazl e Haq by Mufti Abdul Hakeem Sharf QadriDocument30 pagesHikmat o Kalam K Imam Fazl e Haq by Mufti Abdul Hakeem Sharf QadrisunnivoiceNo ratings yet

- MCS 012june2020Document8 pagesMCS 012june2020kk2760057No ratings yet

- G31M04 Schematic Foxconn Precision Co. Inc.: Fab.A Data: 2007/6/15 Page IndexDocument39 pagesG31M04 Schematic Foxconn Precision Co. Inc.: Fab.A Data: 2007/6/15 Page IndexLeonard Gržetić100% (1)

- DicaDocument26 pagesDicaganga_ch1No ratings yet

- Motorola Driver LogDocument8 pagesMotorola Driver LogDanny Enrique Villasmil PerdomoNo ratings yet

- Manual Kit TivaC Tm4c1294 Spmu365cDocument42 pagesManual Kit TivaC Tm4c1294 Spmu365cFernandoSydorNo ratings yet

- Nexys2 Board Reference ManualDocument17 pagesNexys2 Board Reference ManualTudor CiotloșNo ratings yet

- PICBASIC PROGRAM FOR SERVO CONTROL USING TIMER INTERRUPTDocument13 pagesPICBASIC PROGRAM FOR SERVO CONTROL USING TIMER INTERRUPTleo2tvNo ratings yet

- Mini Project Report On: Visvesvaraya Technological UniversityDocument8 pagesMini Project Report On: Visvesvaraya Technological UniversityTejáś ĢøwđâNo ratings yet

- Arduino TimerDocument16 pagesArduino TimerAhnaf HassanNo ratings yet

- Advanced CMOS Process Technology Part 1 and 2 Dr. Lynn FullerDocument51 pagesAdvanced CMOS Process Technology Part 1 and 2 Dr. Lynn FullerPauloConstantinoNo ratings yet

- Mekelle Institute of Technology: PC Hardware Troubleshooting (CSE501) Lecture - 4Document63 pagesMekelle Institute of Technology: PC Hardware Troubleshooting (CSE501) Lecture - 4Tsehayou SieleyNo ratings yet

- 96mpaa 2.8g 2mam3t DatasheetDocument21 pages96mpaa 2.8g 2mam3t DatasheetArimitra ChakrabartiNo ratings yet

- DLD Lab Practical Updated VersionDocument2 pagesDLD Lab Practical Updated VersionAli SarmadNo ratings yet

- Multiplier and Comparator - 1049206536Document11 pagesMultiplier and Comparator - 1049206536RUSSELLJEROME PUNZALANNo ratings yet

- Sample Midterm Exam QuestionsDocument2 pagesSample Midterm Exam QuestionsIshan JawaNo ratings yet

- Light Detector Presentation: NAND Gate Circuit Detects LightDocument14 pagesLight Detector Presentation: NAND Gate Circuit Detects Lightxeem conceptsNo ratings yet

- USB 1208 Series 1408FS DataDocument9 pagesUSB 1208 Series 1408FS DataajayikayodeNo ratings yet

- Configure and Control Devices via DeviceNetDocument164 pagesConfigure and Control Devices via DeviceNetChí NghĩaNo ratings yet