Professional Documents

Culture Documents

CA Classes-206-210

Uploaded by

SrinivasaRao0 ratings0% found this document useful (0 votes)

2 views5 pagesCopyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

2 views5 pagesCA Classes-206-210

Uploaded by

SrinivasaRaoCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 5

Computer Architecture Unit 9

Activity 1:

Find out more about a recent vector thread processor which comes in

two parts: the control processor, known as Rocket, and the vector unit,

known as Hwacha.

9.4 Vector Length and Stride Issues

This section will discuss two issues that occur in real programs. First is the

case when the vector length in a program is not precisely 64.Second is the

way non-adjacent elements in vectors that reside in memory are dealt with.

First, let us study the issue of vector length.

9.4.1 Vector length

In our study till now, we have not stated anything about the real vector size.

We just supposed that the size of the vector register is similar to the size of

the vector we hold. But this may not turn out to be always true. Particularly,

we have two cases in our hands:

One in which the vector size is less than the vector register size, and

The second in which the vector size is larger than the vector register

size.

To be more concrete, we assume 64-element vector registers as offered by

the Cray systems. Let’s observe the easier of these two problems.

Handling smaller vectors: In case the vector size is less than 64, we have

to permit the system to be aware that it should not function on all the 64

elements in the vector registers. This can be simply done by utilising the

vector length register. The Vector Length (VL) register carries the

appropriate vector length. The entire vector operations are conducted on the

first VL elements (in other words, elements in the series 0 to VL - 1). The

following two instructions are needed to load values into the VL register:

VL 1 (VL = 1)

VL Ak (VL = Ak where k ≠ 0)

For instance, in case the vector length is equivalent to 40, the code given

below can be utilised to include two vectors in registers V3 and V4:

A1 40 (A1 = 40)

VL A1 (VL = 40)

V2 V3+FV4 (V2 = V3 + V4)

Manipal University of Jaipur B1648 Page No. 206

Computer Architecture Unit 9

As we cannot write

VL 40,

We must utilise the two-instruction order for loading 40 into the VL register.

The last instruction indicates floating-point addition of vectors V3 and V4. As

the VL is 40, just the first 40 elements are included. Table 9.1 below depicts

a sample of Cray X-MP instructions.

Table 9.1: Sample Cray X-MP Instructions

Handling larger vectors: Smaller vector sizes can be handled by the VL

register, but this does not apply to vectors of larger sizes. For instance, we

Manipal University of Jaipur B1648 Page No. 207

Computer Architecture Unit 9

possess 200-element vectors (i.e., N = 200), in which way the vector

instructions can be used to total two such vectors? The instance of larger

vectors is handled by a method called strip mining.

In strip mining, the vector is segregated into strips of 64 elements. In this

way, a single odd-size piece remains which may be less than 64 elements.

The size of such a piece is provided by N mod 64. Every strip is thereafter

loaded into a vector register. Later on the vector addition instruction is put

into operation. Now, the number of strips can be portrayed by (N /64) + 1.

For this case, the 200 elements are segregated into four pieces:

64 elements are contained in three pieces.

8 elements are contained in one odd piece.

Thereafter a loop is utilised which iterates four times: VL is adjusted to 8 in

one of the iterations, and the rest of the three iterations will adjust the VL

register to 64.

9.4.2 Vector stride

We have to know the way in which elements are stored in memory in order

to understand vector stride. Let’s first observe vectors. Because vectors are

one-dimensional groups, saving a vector in memory is considerably easy:

vector elements are saved as sequential words in memory. In case, we wish

to fetch 40 elements, 40 contiguous words from memory have to be read.

Such elements are said to contain a stride of 1, i.e., to connect with the

subsequent element, we must add 1 to the recent element. It’s necessary to

observe that the distance between consecutive elements is measured in

number of elements and not in bytes.

We will require non-unit vector strides for multidimensional ranges. In order

to find out the reason, we should concentrate on two-dimensional matrices.

In case we want to save a two-dimensional matrix in memory, we must

linearise it. We are able to work on this in one of two ways: column-major or

row-major sequence. Majority of the languages with the exception of

FORTRAN, utilise the row-major order. In such a way of sequencing,

elements are saved in row order: row 0, row 1, row 2, and so on. Elements

are saved column by column: column 0, column 1, and so on in the column-

major order, which is utilised by FORTRAN. For instance, consider the 4 x 4

matrix below:

Manipal University of Jaipur B1648 Page No. 208

Computer Architecture Unit 9

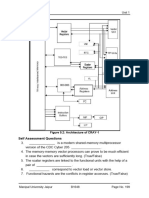

Figure 9.3: Memory Layout of Vector A.

Such a matrix is saved in memory as depicted in figure 9.3. Presuming row-

major order for saving, we should search for a way to reach all elements of

column 0. It’s obvious that such elements are not saved alongside. We are

forced to reach 0, 4, 8, and 12 elements in the memory array.

Since successive elements are divided on the basis of 4 elements, it can be

said that the stride is 4. Vector machines provide load and store instructions

that make an allowance for the stride. It can be noted from Table 9.1 that

Cray X-MP machine assists both unit as well as non-unit stride access. For

instance, the instruction

Vi, A0, Ak

loads vector register Vi along with stride Ak. As unit stride is quite usual, a

particular instruction

Vi, A0,1

is given. Alike instructions exist for storing vectors in memory.

Self Assessment Questions

8. The instance of larger vectors is dealt with by a method called

_______________.

9. Vector elements are saved in the form of ______________ in memory.

Manipal University of Jaipur B1648 Page No. 209

Computer Architecture Unit 9

9.5 Compiler Effectiveness in Vector Processors

A program can be run in vector mode successfully with the help of two

factors. The program structure is the first factor. It should be able to judge

whether the loops comprise of true data dependences or can they be

restructured in such a way that they have no such dependences. This factor

is affected by the algorithms selected and, to some degree, by the manner

in which they are coded. The second factor is the ability of the compiler.

Although no compiler is able to vectorise a loop which does not contain

parallelism among the loop iterations, however there is huge variation in the

capability of compilers to decide if a loop can be vectorised.

The techniques utilised for vectorising programs are similar to revealing ILP;

here we just review how well such techniques perform. Let's look at the

vectorisation levels noted for the Perfect Club benchmarks, as a sign of the

vectorisation level which can be achieved in scientific programs. These

benchmarks are huge and actual scientific applications. Figure 9.4 depicts

the percentage of operations implemented in vector mode for two versions

of the code performing on the Cray Y-MP.

Figure 9.4: Level of Vectorisation among the Perfect Club Benchmarks

when executed on the Cray Y-MP

The first version is that acquired with simply compiler optimisation on the

original code, whereas the second version has been considerably hand-

optimised by a team of Cray Research programmers. The extensive

Manipal University of Jaipur B1648 Page No. 210

You might also like

- Computer Architecture AllClasses-Outline-199-294Document96 pagesComputer Architecture AllClasses-Outline-199-294SrinivasaRaoNo ratings yet

- Unit Iii - AcaDocument13 pagesUnit Iii - AcaAnitha DenisNo ratings yet

- CA Classes-201-205Document5 pagesCA Classes-201-205SrinivasaRaoNo ratings yet

- Bangabandhu Sheikh Mujibur Rahman Maritime University BangladeshDocument7 pagesBangabandhu Sheikh Mujibur Rahman Maritime University BangladeshSyed Mohaiminul Haque BrintoNo ratings yet

- VectorsAndMatrices PDFDocument104 pagesVectorsAndMatrices PDFSuman BhowmickNo ratings yet

- Matlab TutorialDocument39 pagesMatlab TutorialpavithraNo ratings yet

- 7-VECTOR PROCESSING-04-Jan-2020Material - I - 04-Jan-2020 - VECTOR - PROCESSING PDFDocument31 pages7-VECTOR PROCESSING-04-Jan-2020Material - I - 04-Jan-2020 - VECTOR - PROCESSING PDFANTHONY NIKHIL REDDYNo ratings yet

- Unit IV Array and StructureDocument16 pagesUnit IV Array and Structurekenemep346No ratings yet

- Octave Tutorial Andrew NGDocument27 pagesOctave Tutorial Andrew NGalex_azNo ratings yet

- Matlab Tutorial - ShortDocument20 pagesMatlab Tutorial - ShortCam MillerNo ratings yet

- Chapter XXVDocument50 pagesChapter XXVSam VNo ratings yet

- Hive Vectorized Query Execution DesignDocument7 pagesHive Vectorized Query Execution DesignHarish RNo ratings yet

- Matlab FemDocument45 pagesMatlab FemSunny SunNo ratings yet

- Methode Des Elements Finis Cours Annexe 04 Element Quadrilatere Q4Document45 pagesMethode Des Elements Finis Cours Annexe 04 Element Quadrilatere Q4kamlNo ratings yet

- Ex 3Document12 pagesEx 3api-322416213No ratings yet

- The First-Half Review: 1.1 Local LabelsDocument5 pagesThe First-Half Review: 1.1 Local LabelsakhiyarwaladiNo ratings yet

- University of Engineering and Technology, Taxila: Introduction To MATLAB EnvironmentDocument8 pagesUniversity of Engineering and Technology, Taxila: Introduction To MATLAB EnvironmentMuhham WaseemNo ratings yet

- Assignment 3: Vector and HashsetDocument17 pagesAssignment 3: Vector and HashsetMiguelNo ratings yet

- Handout VectorsDocument18 pagesHandout VectorsJeremy PhoNo ratings yet

- Learning From Data 1 Introduction To Matlab: BackgroundDocument8 pagesLearning From Data 1 Introduction To Matlab: Backgrounddadado98No ratings yet

- Altivec ProgrammingDocument67 pagesAltivec ProgrammingbongoloidNo ratings yet

- Octave Tutorial: Andrew NGDocument28 pagesOctave Tutorial: Andrew NGvijasrinNo ratings yet

- A Relational Approach To The Compilation of Sparse Matrix ProgramsDocument16 pagesA Relational Approach To The Compilation of Sparse Matrix Programsmmmmm1900No ratings yet

- Project 4 - Matrix CalculatorDocument3 pagesProject 4 - Matrix Calculatorsuman k mNo ratings yet

- Implementing Artificial Neural Network in Python From ScratchDocument16 pagesImplementing Artificial Neural Network in Python From Scratchsidrakhalid1357No ratings yet

- Matlab PrimerDocument27 pagesMatlab Primerneit_tadNo ratings yet

- A Relational Approach To The Compilation of Sparse Matrix ProgramsDocument16 pagesA Relational Approach To The Compilation of Sparse Matrix Programsmmmmm1900No ratings yet

- Unit-5: Cocurrent Processors: Vector & Multiple Instruction Issue ProcessorsDocument106 pagesUnit-5: Cocurrent Processors: Vector & Multiple Instruction Issue ProcessorsJitender GargNo ratings yet

- Neural Network Toolbox: A Tutorial For The Course Computational IntelligenceDocument8 pagesNeural Network Toolbox: A Tutorial For The Course Computational Intelligencenehabatra14No ratings yet

- Co QBDocument26 pagesCo QBkhananu100% (1)

- Principle of Block CodingDocument6 pagesPrinciple of Block CodingpakitzaNo ratings yet

- W8-Module-Dimensions of Data TypesDocument12 pagesW8-Module-Dimensions of Data TypesJitlee PapaNo ratings yet

- Vector QuantizationDocument6 pagesVector QuantizationnavyaraviNo ratings yet

- High Performance Linear Algebra Class Reference Guide April 1996Document19 pagesHigh Performance Linear Algebra Class Reference Guide April 1996anthraxpNo ratings yet

- CA Classes-211-215Document5 pagesCA Classes-211-215SrinivasaRaoNo ratings yet

- Simple Vector Processor Modeled With VHDLDocument6 pagesSimple Vector Processor Modeled With VHDLduzngvt123No ratings yet

- Octave Tutorial: Andrew NGDocument27 pagesOctave Tutorial: Andrew NGAmit GovilkarNo ratings yet

- Vapnik-Chervonenkis DimensionDocument6 pagesVapnik-Chervonenkis Dimensionhobson616No ratings yet

- Activity 5 Arrays and MatricesDocument8 pagesActivity 5 Arrays and MatricesNicole ValerioNo ratings yet

- Computer Science C++Document43 pagesComputer Science C++sellaryNo ratings yet

- Lab 1Document11 pagesLab 1Rigor RempilloNo ratings yet

- C Programming Theory and Lab AktuDocument4 pagesC Programming Theory and Lab AktuSanjay GuptaNo ratings yet

- Labview NotebookDocument40 pagesLabview Notebooktvu0244689No ratings yet

- Matlab Tutorial: Introduction To Vectors in MatlabDocument6 pagesMatlab Tutorial: Introduction To Vectors in MatlabMatt BrennerNo ratings yet

- MatlabTutorial2 PDFDocument10 pagesMatlabTutorial2 PDFIloaie Maria GeorgetaNo ratings yet

- Power Up C++ With The Standard Template Library: Part I: DmitrykorolevDocument18 pagesPower Up C++ With The Standard Template Library: Part I: DmitrykorolevRomee PanchalNo ratings yet

- Lab Session 04: Element by Element OperationsDocument7 pagesLab Session 04: Element by Element OperationsShahansha HumayunNo ratings yet

- Module 5Document37 pagesModule 5PavithraNo ratings yet

- CA Classes-236-240Document5 pagesCA Classes-236-240SrinivasaRaoNo ratings yet

- Lecture 3 Notes Arrays: 15-122: Principles of Imperative Computation (Summer 1 2015) Frank Pfenning, Andr e PlatzerDocument10 pagesLecture 3 Notes Arrays: 15-122: Principles of Imperative Computation (Summer 1 2015) Frank Pfenning, Andr e PlatzerBelindaNo ratings yet

- Basic of MatlabDocument11 pagesBasic of MatlabAashutosh Raj TimilsenaNo ratings yet

- International Journal of Engineering Research and Development (IJERD)Document6 pagesInternational Journal of Engineering Research and Development (IJERD)IJERDNo ratings yet

- Chapter 3 INTRODUCTION TO MATLABDocument26 pagesChapter 3 INTRODUCTION TO MATLABShariff GaramaNo ratings yet

- Assigning and Returning Arrays in Visual Basic 6Document13 pagesAssigning and Returning Arrays in Visual Basic 6lalithaNo ratings yet

- ArrayDocument5 pagesArraySirajum MonirNo ratings yet

- Important QuestionsDocument18 pagesImportant Questionsshouryarastogi9760No ratings yet

- Practical Monte Carlo Simulation with Excel - Part 2 of 2: Applications and DistributionsFrom EverandPractical Monte Carlo Simulation with Excel - Part 2 of 2: Applications and DistributionsRating: 2 out of 5 stars2/5 (1)

- Integer Optimization and its Computation in Emergency ManagementFrom EverandInteger Optimization and its Computation in Emergency ManagementNo ratings yet

- Computer Architecture AllClasses-Outline-1-99Document99 pagesComputer Architecture AllClasses-Outline-1-99SrinivasaRaoNo ratings yet

- Computer Architecture AllClasses-OutlineDocument294 pagesComputer Architecture AllClasses-OutlineSrinivasaRaoNo ratings yet

- Computer Architecture AllClasses-Outline-100-198Document99 pagesComputer Architecture AllClasses-Outline-100-198SrinivasaRaoNo ratings yet

- CA Classes-261-265Document5 pagesCA Classes-261-265SrinivasaRaoNo ratings yet

- CA Classes-236-240Document5 pagesCA Classes-236-240SrinivasaRaoNo ratings yet

- CA Classes-251-255Document5 pagesCA Classes-251-255SrinivasaRaoNo ratings yet

- CA Classes-246-250Document5 pagesCA Classes-246-250SrinivasaRaoNo ratings yet

- CA Classes-141-145Document5 pagesCA Classes-141-145SrinivasaRaoNo ratings yet

- CA Classes-86-90Document5 pagesCA Classes-86-90SrinivasaRaoNo ratings yet

- CA Classes-196-200Document5 pagesCA Classes-196-200SrinivasaRaoNo ratings yet

- CA Classes-176-180Document5 pagesCA Classes-176-180SrinivasaRaoNo ratings yet

- CA Classes-216-220Document5 pagesCA Classes-216-220SrinivasaRaoNo ratings yet

- CA Classes-221-225Document5 pagesCA Classes-221-225SrinivasaRaoNo ratings yet

- CA Classes-186-190Document5 pagesCA Classes-186-190SrinivasaRaoNo ratings yet

- CA Classes-121-125Document5 pagesCA Classes-121-125SrinivasaRaoNo ratings yet

- CA Classes-126-130Document5 pagesCA Classes-126-130SrinivasaRaoNo ratings yet

- CA Classes-111-115Document5 pagesCA Classes-111-115SrinivasaRaoNo ratings yet

- CA Classes-101-105Document5 pagesCA Classes-101-105SrinivasaRaoNo ratings yet

- CA Classes-36-40Document5 pagesCA Classes-36-40SrinivasaRaoNo ratings yet

- CA Classes-106-110Document5 pagesCA Classes-106-110SrinivasaRaoNo ratings yet

- CA Classes-116-120Document5 pagesCA Classes-116-120SrinivasaRaoNo ratings yet

- CA Classes-26-30Document5 pagesCA Classes-26-30SrinivasaRaoNo ratings yet

- Programming in C - 121-140Document20 pagesProgramming in C - 121-140SrinivasaRaoNo ratings yet

- Programming in C - 21-40Document20 pagesProgramming in C - 21-40SrinivasaRaoNo ratings yet

- CA Classes-16-20Document5 pagesCA Classes-16-20SrinivasaRaoNo ratings yet

- Programming in C - 216-220Document5 pagesProgramming in C - 216-220SrinivasaRaoNo ratings yet

- Programming in C - 161-180Document20 pagesProgramming in C - 161-180SrinivasaRaoNo ratings yet

- Programming in C - 41-60Document20 pagesProgramming in C - 41-60SrinivasaRaoNo ratings yet

- Alignment Chart For ProjectDocument3 pagesAlignment Chart For Projectapi-233588556No ratings yet

- API SolidworksDocument23 pagesAPI SolidworksPaco Ol100% (1)

- Notes On Preface To ShakespeareDocument3 pagesNotes On Preface To Shakespeareliteraturelove30No ratings yet

- Test Cases and Check List Primer Test Kejsa SajtaDocument11 pagesTest Cases and Check List Primer Test Kejsa SajtaМария ДмитриеваNo ratings yet

- Wyndham Lewis: Portrait of The Artist As An EnemyDocument392 pagesWyndham Lewis: Portrait of The Artist As An EnemyJonathan Carson100% (4)

- Test (CST) : Working With Trigonometric Functions: Included Questions (20 Questions)Document50 pagesTest (CST) : Working With Trigonometric Functions: Included Questions (20 Questions)Islam Abd ElraoufNo ratings yet

- FTII Entrance PaperDocument9 pagesFTII Entrance PaperNeeraj Kumar100% (1)

- Jurus 6 Coordinate Connectors Yang BenarDocument6 pagesJurus 6 Coordinate Connectors Yang BenardayuwijayantiNo ratings yet

- Major Assignment: Sample TablesDocument3 pagesMajor Assignment: Sample TablesAtif basir khanNo ratings yet

- Alter ELETTRONICA S.R.L. 15033 Casale Monferrato (AL) - ITALYDocument28 pagesAlter ELETTRONICA S.R.L. 15033 Casale Monferrato (AL) - ITALYestevesvaldezoNo ratings yet

- New American Inside Out Elementary Unit 10 Test: Part ADocument5 pagesNew American Inside Out Elementary Unit 10 Test: Part AKeyra Aguilar CondeNo ratings yet

- W. B. Yeats and World Literature The Subject of PoetryDocument211 pagesW. B. Yeats and World Literature The Subject of PoetryeminadzNo ratings yet

- 6-0-1-SP1 SWIFTNet Module Install and Users GuideDocument102 pages6-0-1-SP1 SWIFTNet Module Install and Users GuideswiftcenterNo ratings yet

- Deixis PresentationDocument20 pagesDeixis Presentationmuna zihahNo ratings yet

- Elektro Manual ALPHA 477 488 D EDocument23 pagesElektro Manual ALPHA 477 488 D EIsakov IgorNo ratings yet

- Test - Roots and Powers - KEYDocument2 pagesTest - Roots and Powers - KEYesyt395690No ratings yet

- Detailed Lesson Plan in Math 5 - DIVISIBILITYDocument3 pagesDetailed Lesson Plan in Math 5 - DIVISIBILITYJulie Enciso100% (1)

- The Structure of Argument: Conclusions and Premises Claims and WarrantsDocument13 pagesThe Structure of Argument: Conclusions and Premises Claims and WarrantsDaniel Emmanuel De LeonNo ratings yet

- Listadopedidos5unit 2YADocument3 pagesListadopedidos5unit 2YARafael Glez Jimenez50% (2)

- Grade 1: Writing RubricsDocument3 pagesGrade 1: Writing RubricsCarol GlenNo ratings yet

- 英语作文过渡词 Transition WordsDocument3 pages英语作文过渡词 Transition WordsaubreyklassenNo ratings yet

- BHHS US Brand Guidelines 052020Document106 pagesBHHS US Brand Guidelines 052020docherty_13No ratings yet

- June 30th Comparing and ContrastingDocument12 pagesJune 30th Comparing and ContrastingCarolina Nerio MillanNo ratings yet

- Utin Nur'aini - LK 1.1 - Modul 4 English For EntertainmentDocument3 pagesUtin Nur'aini - LK 1.1 - Modul 4 English For Entertainmentutin nurainiNo ratings yet

- 09Document39 pages09AlexNo ratings yet

- F2 Pulse, 70Document4 pagesF2 Pulse, 70Dineswari Selvam50% (4)

- Background of The StudyDocument15 pagesBackground of The StudyJensi AsiNo ratings yet

- Order of AdjectivesDocument2 pagesOrder of AdjectivesNabilahNo ratings yet

- Capstone Project 1: User StoryDocument28 pagesCapstone Project 1: User StoryHoàng Văn HiếuNo ratings yet

- BIOS Master Password Generator For LaptopsDocument1 pageBIOS Master Password Generator For LaptopsVincent PhilippinesNo ratings yet