Professional Documents

Culture Documents

CA Classes-121-125

Uploaded by

SrinivasaRaoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CA Classes-121-125

Uploaded by

SrinivasaRaoCopyright:

Available Formats

Computer Architecture Unit 5

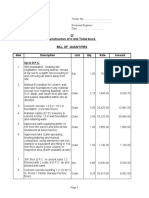

iteration. PES has hardware resources which contain one path to the

memory, two integer units and one branch unit.

Figure 5.11: Example of PES

You can see that rows are showing the time steps and columns are showing

certain operations performed in time step. In this PES we can see that in

branch unit “ble” is not taken and it is theoretically executing instruction from

predicted path. In this example we have showed renaming values for only

r3 register but others can also be renamed. Various values allotted to

register r3 are bounded to different physical register (R1, R2, R3, R4).

Now you can see numerous ways of arranging instruction issue buffer for

boosting up the complexity.

Single queue method: Renaming is not needed in single queue method

because this method has 1 queue and no out of ordering issue. In this

method the operand availability could be handled through easy reservation

bits allotted to every register. During the instructional modification of register

issues, a register reserved and after the modification finished the register is

cleared.

Multiple queue method: In multiple queue method, all the queues get

instruction issue in order. Due to other queues some queues can be issued

out. With respect to instruction type single queues are organized.

Reservation stations: In reservation stations, the instruction issue does not

follow the FIFO order. As a result for data accessibility, the reservation

stations at the same time have to observe their source operands. The

conventional way of doing this is to reserve the operand data in reservation

Manipal University Jaipur B1648 Page No. 121

Computer Architecture Unit 5

station. As reservation station receive the instruction then available operand

values are firstly read and placed in it.

After that it logically evaluate the difference between the operand

designators of inaccessible data and result designators of finishing

instructions. If there is similarity, then the result value is extracted to

matching reservation station.

Instruction got issued as all the operands are prepared in reservation

station. It can be divided into instruction type for decreasing data paths or

may behave as a single block.

Self Assessment Questions

9. In traditional pipeline implementations, load and store instructions are

processed by the ____________________.

10. The consistency of instruction completion with that of sequential

instruction execution is specified b _______________.

11. Reordering of memory accesses is not allowed by the processor which

endorses weak memory consistency does not allow (True/False).

12. _____________ is not needed in single queue method.

13. In reservation stations, the instruction issue does not follow the FIFO

order. (True/ False).

5.6 Summary

The design space of pipelines can be sub divided into two aspects:

basic layout of a pipeline and dependency resolution.

An Instruction pipeline operates on a stream of instructions by

overlapping and decomposing the three phases (fetch, decode and

execute) of the instruction cycle.

Two basic aspects of the design space are how FX pipelines are laid out

logically and how they are implemented.

A logical layout of an FX pipeline consists, first, of the specification of

how many stages an FX pipeline has and what tasks are to be

performed in these stages.

The other key aspect of the design space is how FX pipelines are imple-

mented.

Manipal University Jaipur B1648 Page No. 122

Computer Architecture Unit 5

In logical layout of FX pipelines, the FX pipelines for RISC and C1SC

processors have to be taken separately, since each type has a slightly

different scope.

Pipelined processing of loads and stores consist of sequential

consistency of instruction execution and parallel execution.

5.7 Glossary

CISC: It is an acronym for Complex Instruction Set Computer. The CISC

machines are easy to program and make efficient use of memory.

CPA: It stands for carry-propagation adder which adds two numbers

and produces an arithmetic sum.

CSA: It stands for carry-save adder which adds three input numbers

and produces one sum output.

LMD: Load Memory Data.

Load/Store bypassing: It defines that either loads can bypasss stores

or vice versa, without violating the memory data dependencies.

Memory consistency: It is used to find out whether memory access is

performed in the same order as in a sequential processor.

Processor consistency: It is used to indicate the consistency of

instruction completion with that of sequential instruction execution.

RISC: It stands for Reduced Instruction Set Computing. RISC

computers reduce chip complexity by using simpler instructions.

ROB: It stands for Reorder Buffer. ROB is an assurance tool for

sequential consistency execution where multiple EUs operate in parallel.

Speculative loads: They avoid memory access delay. This delay can

be caused due to the non- computation of required addresses or

clashes among the addresses.

Tomasulo’s algorithm: It allows the replacement of sequential order by

data-flow order.

5.8 Terminal Questions

1. Name the two sub divisions of design space of pipelines and write short

notes on them.

2. What do you mean by pipeline instruction processing?

3. Explain the concept of pipelined execution of Integer and Boolean

instructions.

Manipal University Jaipur B1648 Page No. 123

Computer Architecture Unit 5

4. Describe the logical layout of both RISC and CISC computers.

5. Write in brief the process of implementation of FX pipelines.

6. Explain the various subtasks involved in load and store processing

7. Write short notes on:

a. Sequential Consistency of Instruction Execution

b. Instruction Issuing and Parallel Execution

5.9 Answers

Self Assessment Questions

1. Microprocessor without Interlocked Pipeline Stages

2. Dynamically

3. Write Back Operand

4. Opcode, operand specifiers

5. Register operands

6. True

7. Intel 80x86 and Motorola 68K series

8. Carry-propagation adder (CPA)

9. Master pipeline

10. Processor Consistency

11. False

12. Renaming

13. True

Terminal Questions

1. The design space of pipelines can be sub divided into two aspects:

basic layout of a pipeline and dependency resolution. Refer Section 5.2.

2. A pipeline instruction processing technique is used to increase the

instruction throughput. It is used in the design of modern CPUs,

microcontrollers and microprocessors.Refer Section 5.3 for more details.

3. There are two basic aspects of the design space of pipelined execution

of Integer and Boolean instructions: how FX pipelines are laid out

logically and how they are implemented. Refer Section 5.4.

4. While processing operates instructions, RISC pipelines have to cope

only with register operands. By contrast, CISC pipelines must be able to

deal with both register and memory operands as well as destinations.

Refer Section 5.4.

Manipal University Jaipur B1648 Page No. 124

Computer Architecture Unit 5

5. Depending on the function to be implemented, different pipeline stages

in an arithmetic unit require different hardware logic. Refer Section 5.4.

6. The execution of load and store instructions begins with the

determination of the effective memory address (EA) from where data is

to be fetched. This can be broken down into subtasks. Refer

Section 5.5.

7. The overall instruction execution of a processor should mimic sequential

execution, i.e. it should preserve sequential consistency. Refer

Section 5.5. The first step is to create and buffer execution and then

determine which tuples can be issued for parallel execution. Refer

Section 5.5.

References:

Hwang, K. (1993) Advanced Computer Architecture. McGraw-Hill.

Godse D. A. & Godse A. P. (2010). Computer Organisation, Technical

Publications. pp. 3–9.

Hennessy, John L., Patterson, David A. & Goldberg, David (2002)

Computer Architecture: A Quantitative Approach, (3rd edition), Morgan

Kaufmann.

Sima, Dezsö, Fountain, Terry J. & Kacsuk, Péter (1997) Advanced

computer architectures - a design space approach, Addison-Wesley-

Longman: I-XXIII, 1-766.

E-references:

http://www.eecg.toronto.edu/~moshovos/ACA06/readings/ieee-

proc.superscalar.pdf

http://webcache.googleusercontent.com/search?q=cache:yU5nCVnju9

cJ:www.ic.uff.br/~vefr/teaching/lectnotes/AP1-topico3.5.ps.gz+load+

store+sequential+instructions&cd=2&hl=en&ct=clnk&gl=in

Manipal University Jaipur B1648 Page No. 125

You might also like

- CA Classes-106-110Document5 pagesCA Classes-106-110SrinivasaRaoNo ratings yet

- Unit 05 Design Space of PipelinesDocument24 pagesUnit 05 Design Space of PipelinesSrinivasaRaoNo ratings yet

- Computer Architecture AllClasses-Outline-100-198Document99 pagesComputer Architecture AllClasses-Outline-100-198SrinivasaRaoNo ratings yet

- CA Classes-76-80Document5 pagesCA Classes-76-80SrinivasaRaoNo ratings yet

- CA Classes-166-170Document5 pagesCA Classes-166-170SrinivasaRaoNo ratings yet

- CA Classes-101-105Document5 pagesCA Classes-101-105SrinivasaRaoNo ratings yet

- Chapter 04 Processors and Memory HierarchyDocument50 pagesChapter 04 Processors and Memory Hierarchyশেখ আরিফুল ইসলাম75% (8)

- CA Classes-116-120Document5 pagesCA Classes-116-120SrinivasaRaoNo ratings yet

- CA Classes-241-245Document5 pagesCA Classes-241-245SrinivasaRaoNo ratings yet

- Draw The Block Diagram of Von Neumann Architecture and Explain About Its Parts in Brief AnswerDocument7 pagesDraw The Block Diagram of Von Neumann Architecture and Explain About Its Parts in Brief AnswerhayerpaNo ratings yet

- Mips RIO000 Microprocessor: SuperscalarDocument13 pagesMips RIO000 Microprocessor: SuperscalarNishant SinghNo ratings yet

- Department of Computer Science and Engineering Subject Name: Advanced Computer Architecture Code: Cs2354Document7 pagesDepartment of Computer Science and Engineering Subject Name: Advanced Computer Architecture Code: Cs2354kamalsomuNo ratings yet

- Assignment 4: Course Instructor / Lab EngineerDocument8 pagesAssignment 4: Course Instructor / Lab EngineerNitasha HumaNo ratings yet

- Design of 32-Bit Risc Cpu Based On Mips: Journal of Global Research in Computer ScienceDocument5 pagesDesign of 32-Bit Risc Cpu Based On Mips: Journal of Global Research in Computer ScienceAkanksha Dixit ManodhyaNo ratings yet

- ACA - Two MarksDocument17 pagesACA - Two MarksAarthy Sekar DNo ratings yet

- MIPS Report FileDocument17 pagesMIPS Report FileAayushiNo ratings yet

- ACA Question BankDocument19 pagesACA Question BankVanitha VivekNo ratings yet

- Digital Signal Processing AdvancedDocument14 pagesDigital Signal Processing AdvancedMathi YuvarajanNo ratings yet

- Cache-Assignment Handout 12Document9 pagesCache-Assignment Handout 12sch123321No ratings yet

- Cep 4Document11 pagesCep 4ShivamNo ratings yet

- DPCO Unit3 2mark Q&ADocument11 pagesDPCO Unit3 2mark Q&Akanimozhi rajasekarenNo ratings yet

- OLP NotesDocument11 pagesOLP NotesSathish NarayananNo ratings yet

- Reduced Instruction Set Computing (RISC) : Li-Chuan FangDocument42 pagesReduced Instruction Set Computing (RISC) : Li-Chuan FangDevang PatelNo ratings yet

- Processor Verification PDFDocument7 pagesProcessor Verification PDFdovesnest_inNo ratings yet

- CA Classes-91-95Document5 pagesCA Classes-91-95SrinivasaRaoNo ratings yet

- Aca 2 Marks With AnswersDocument22 pagesAca 2 Marks With AnswersmenakadevieceNo ratings yet

- RISC MicroprocessorsDocument63 pagesRISC MicroprocessorsBoul chandra GaraiNo ratings yet

- Aca Univ 2 Mark and 16 MarkDocument20 pagesAca Univ 2 Mark and 16 MarkmenakadevieceNo ratings yet

- Solutions Ch4Document7 pagesSolutions Ch4Sangam JindalNo ratings yet

- RISC Instruction Set:: I) Data Manipulation InstructionsDocument8 pagesRISC Instruction Set:: I) Data Manipulation InstructionsSwarup BharNo ratings yet

- Chap2 SlidesDocument127 pagesChap2 SlidesDhara RajputNo ratings yet

- Beyond RISC - The Post-RISC Architecture Submitted To: IEEE Micro 3/96Document20 pagesBeyond RISC - The Post-RISC Architecture Submitted To: IEEE Micro 3/96Andreas DelisNo ratings yet

- Aca Important Questions 2 Marks 16marksDocument18 pagesAca Important Questions 2 Marks 16marksvimala60% (5)

- Computer Architecture Assignment: The ARM Cortex-A53Document8 pagesComputer Architecture Assignment: The ARM Cortex-A53destiny breakNo ratings yet

- Session2 - Introduction To RISC and CISCDocument4 pagesSession2 - Introduction To RISC and CISCHillary MurungaNo ratings yet

- Computer ArchitectDocument194 pagesComputer Architectksu2006No ratings yet

- Design and Analysis of A 32-Bit Pipelined Mips Risc ProcessorDocument18 pagesDesign and Analysis of A 32-Bit Pipelined Mips Risc ProcessorAnonymous e4UpOQEPNo ratings yet

- Ee/Ce 6370 Spring 2015: Design Assignment: Utd Pipelined MicroprocessorDocument7 pagesEe/Ce 6370 Spring 2015: Design Assignment: Utd Pipelined MicroprocessorRohit YedidaNo ratings yet

- Design of A 32-Bit Dual Pipeline Superscalar RISC-V Processor On FPGADocument4 pagesDesign of A 32-Bit Dual Pipeline Superscalar RISC-V Processor On FPGASRIRAAM VSNo ratings yet

- Machines, Machine Languages, and Digital Logic: Accumulator Machines Have A Sharply Limited Number of DataDocument6 pagesMachines, Machine Languages, and Digital Logic: Accumulator Machines Have A Sharply Limited Number of DataZanz ProjectzNo ratings yet

- 21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Document4 pages21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Rohan RNo ratings yet

- Computer Architecture Unit V - Advanced Architecture Part-ADocument4 pagesComputer Architecture Unit V - Advanced Architecture Part-AJennifer PeterNo ratings yet

- Computer ArchitectureT4Document7 pagesComputer ArchitectureT4Md. EmdadNo ratings yet

- Advanced Computer Architecture (ACA) AssignmentDocument16 pagesAdvanced Computer Architecture (ACA) AssignmentSayed Aman KonenNo ratings yet

- CS 6303 Computer Architecture TWO Mark With AnswerDocument14 pagesCS 6303 Computer Architecture TWO Mark With AnswerPRIYA RAJI100% (1)

- Computer Architecture Question BankDocument16 pagesComputer Architecture Question BankGreenkings100% (1)

- DPCO Unit 4 2mark Q&ADocument11 pagesDPCO Unit 4 2mark Q&Akanimozhi rajasekarenNo ratings yet

- Top 21 Computer Architecture Interview Questions & AnswersDocument5 pagesTop 21 Computer Architecture Interview Questions & AnswersMahadeva HerbalsNo ratings yet

- Parallelism in Computer ArchitectureDocument27 pagesParallelism in Computer ArchitectureKumarNo ratings yet

- COA Imp QUESTIONSDocument4 pagesCOA Imp QUESTIONSkazuma6362No ratings yet

- Computer ArchitectureDocument125 pagesComputer Architecturebalaji bala100% (1)

- Instruction-Level Parallelism For Recongurable ComputingDocument10 pagesInstruction-Level Parallelism For Recongurable ComputingThiyagu RajanNo ratings yet

- Test 1 Study GuideDocument6 pagesTest 1 Study GuideTravon333No ratings yet

- Instruction Pipeline Design, Arithmetic Pipeline Deign - Super Scalar Pipeline DesignDocument34 pagesInstruction Pipeline Design, Arithmetic Pipeline Deign - Super Scalar Pipeline DesignMarlon TugweteNo ratings yet

- Unit IIIDocument6 pagesUnit IIISheeba KelvinNo ratings yet

- Ec 6009 - Advanced Computer Architecture 2 MarksDocument8 pagesEc 6009 - Advanced Computer Architecture 2 MarksNS Engg&Tech EEE DEPTNo ratings yet

- 2010 Apr Cert CNT ReportDocument14 pages2010 Apr Cert CNT ReportmichaelmikealNo ratings yet

- General Question: 1. What Is Read Modify Write Technique?Document4 pagesGeneral Question: 1. What Is Read Modify Write Technique?Mohamed MalikNo ratings yet

- CA Classes-236-240Document5 pagesCA Classes-236-240SrinivasaRaoNo ratings yet

- Computer Architecture AllClasses-OutlineDocument294 pagesComputer Architecture AllClasses-OutlineSrinivasaRaoNo ratings yet

- CA Classes-251-255Document5 pagesCA Classes-251-255SrinivasaRaoNo ratings yet

- Computer Architecture AllClasses-Outline-1-99Document99 pagesComputer Architecture AllClasses-Outline-1-99SrinivasaRaoNo ratings yet

- CA Classes-261-265Document5 pagesCA Classes-261-265SrinivasaRaoNo ratings yet

- CA Classes-176-180Document5 pagesCA Classes-176-180SrinivasaRaoNo ratings yet

- CA Classes-201-205Document5 pagesCA Classes-201-205SrinivasaRaoNo ratings yet

- CA Classes-246-250Document5 pagesCA Classes-246-250SrinivasaRaoNo ratings yet

- CA Classes-216-220Document5 pagesCA Classes-216-220SrinivasaRaoNo ratings yet

- CA Classes-221-225Document5 pagesCA Classes-221-225SrinivasaRaoNo ratings yet

- CA Classes-16-20Document5 pagesCA Classes-16-20SrinivasaRaoNo ratings yet

- CA Classes-206-210Document5 pagesCA Classes-206-210SrinivasaRaoNo ratings yet

- CA Classes-196-200Document5 pagesCA Classes-196-200SrinivasaRaoNo ratings yet

- CA Classes-86-90Document5 pagesCA Classes-86-90SrinivasaRaoNo ratings yet

- CA Classes-141-145Document5 pagesCA Classes-141-145SrinivasaRaoNo ratings yet

- CA Classes-186-190Document5 pagesCA Classes-186-190SrinivasaRaoNo ratings yet

- CA Classes-111-115Document5 pagesCA Classes-111-115SrinivasaRaoNo ratings yet

- CA Classes-116-120Document5 pagesCA Classes-116-120SrinivasaRaoNo ratings yet

- CA Classes-101-105Document5 pagesCA Classes-101-105SrinivasaRaoNo ratings yet

- CA Classes-26-30Document5 pagesCA Classes-26-30SrinivasaRaoNo ratings yet

- CA Classes-36-40Document5 pagesCA Classes-36-40SrinivasaRaoNo ratings yet

- CA Classes-126-130Document5 pagesCA Classes-126-130SrinivasaRaoNo ratings yet

- Programming in C - 216-220Document5 pagesProgramming in C - 216-220SrinivasaRaoNo ratings yet

- Programming in C - 161-180Document20 pagesProgramming in C - 161-180SrinivasaRaoNo ratings yet

- Programming in C - 121-140Document20 pagesProgramming in C - 121-140SrinivasaRaoNo ratings yet

- Programming in C - 21-40Document20 pagesProgramming in C - 21-40SrinivasaRaoNo ratings yet

- Programming in C - 41-60Document20 pagesProgramming in C - 41-60SrinivasaRaoNo ratings yet

- Kuper ManualDocument335 pagesKuper Manualdonkey slap100% (1)

- 19-2 Clericis LaicosDocument3 pages19-2 Clericis LaicosC C Bờm BờmNo ratings yet

- Procurement Audit PlanDocument12 pagesProcurement Audit PlanMustafa Bilal100% (1)

- Introduction To Radar Warning ReceiverDocument23 pagesIntroduction To Radar Warning ReceiverPobitra Chele100% (1)

- Pharaoh TextDocument143 pagesPharaoh Textanon_31362848No ratings yet

- E OfficeDocument3 pagesE Officeஊக்கமது கைவிடேல்No ratings yet

- Marketing Management - Pgpmi - Class 12Document44 pagesMarketing Management - Pgpmi - Class 12Sivapriya KrishnanNo ratings yet

- Usha Unit 1 GuideDocument2 pagesUsha Unit 1 Guideapi-348847924No ratings yet

- 254 AssignmentDocument3 pages254 AssignmentSavera Mizan ShuptiNo ratings yet

- Massive X-16x9 Version 5.0 - 5.3 (Latest New Updates in Here!!!)Document158 pagesMassive X-16x9 Version 5.0 - 5.3 (Latest New Updates in Here!!!)JF DVNo ratings yet

- MPPWD 2014 SOR CH 1 To 5 in ExcelDocument66 pagesMPPWD 2014 SOR CH 1 To 5 in ExcelElvis GrayNo ratings yet

- Self-Instructional Manual (SIM) For Self-Directed Learning (SDL)Document28 pagesSelf-Instructional Manual (SIM) For Self-Directed Learning (SDL)Monique Dianne Dela VegaNo ratings yet

- Flyer Manuale - CON WATERMARK PAGINE SINGOLEDocument6 pagesFlyer Manuale - CON WATERMARK PAGINE SINGOLEjscmtNo ratings yet

- MP 221 Tanael PLUMBING CODE Definition of Terms 2Document3 pagesMP 221 Tanael PLUMBING CODE Definition of Terms 2Louie BarredoNo ratings yet

- How Can You Achieve Safety and Profitability ?Document32 pagesHow Can You Achieve Safety and Profitability ?Mohamed OmarNo ratings yet

- The April Fair in Seville: Word FormationDocument2 pagesThe April Fair in Seville: Word FormationДархан МакыжанNo ratings yet

- Nguyen Dang Bao Tran - s3801633 - Assignment 1 Business Report - BAFI3184 Business FinanceDocument14 pagesNguyen Dang Bao Tran - s3801633 - Assignment 1 Business Report - BAFI3184 Business FinanceNgọc MaiNo ratings yet

- Pyro ShieldDocument6 pagesPyro Shieldmunim87No ratings yet

- 1 Ton Per Hour Electrode Production LineDocument7 pages1 Ton Per Hour Electrode Production LineMohamed AdelNo ratings yet

- Analysis of Brand Activation and Digital Media On The Existence of Local Product Based On Korean Fashion (Case Study On Online Clothing Byeol - Thebrand)Document11 pagesAnalysis of Brand Activation and Digital Media On The Existence of Local Product Based On Korean Fashion (Case Study On Online Clothing Byeol - Thebrand)AJHSSR JournalNo ratings yet

- Rules On Evidence PDFDocument35 pagesRules On Evidence PDFEuodia HodeshNo ratings yet

- Divider Block Accessory LTR HowdenDocument4 pagesDivider Block Accessory LTR HowdenjasonNo ratings yet

- Karmex 80df Diuron MsdsDocument9 pagesKarmex 80df Diuron MsdsSouth Santee Aquaculture100% (1)

- Type BOQ For Construction of 4 Units Toilet Drawing No.04Document6 pagesType BOQ For Construction of 4 Units Toilet Drawing No.04Yashika Bhathiya JayasingheNo ratings yet

- Verma Toys Leona Bebe PDFDocument28 pagesVerma Toys Leona Bebe PDFSILVIA ROMERO100% (3)

- Permit To Work Audit Checklist OctoberDocument3 pagesPermit To Work Audit Checklist OctoberefeNo ratings yet

- Common OPCRF Contents For 2021 2022 FINALE 2Document21 pagesCommon OPCRF Contents For 2021 2022 FINALE 2JENNIFER FONTANILLA100% (30)

- Revenue Management Session 1: Introduction To Pricing OptimizationDocument55 pagesRevenue Management Session 1: Introduction To Pricing OptimizationDuc NguyenNo ratings yet

- Safety Inspection Checklist Project: Location: Inspector: DateDocument2 pagesSafety Inspection Checklist Project: Location: Inspector: Dateyono DaryonoNo ratings yet

- How To Attain Success Through The Strength of The Vibration of NumbersDocument95 pagesHow To Attain Success Through The Strength of The Vibration of NumberszahkulNo ratings yet

- Chip War: The Quest to Dominate the World's Most Critical TechnologyFrom EverandChip War: The Quest to Dominate the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (227)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)From EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Rating: 5 out of 5 stars5/5 (1)

- Computer Science: A Concise IntroductionFrom EverandComputer Science: A Concise IntroductionRating: 4.5 out of 5 stars4.5/5 (14)

- Chip War: The Fight for the World's Most Critical TechnologyFrom EverandChip War: The Fight for the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (82)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XFrom EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XRating: 3 out of 5 stars3/5 (2)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102From EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Rating: 5 out of 5 stars5/5 (2)

- CompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102From EverandCompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102No ratings yet

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesFrom EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesNo ratings yet

- Amazon Web Services (AWS) Interview Questions and AnswersFrom EverandAmazon Web Services (AWS) Interview Questions and AnswersRating: 4.5 out of 5 stars4.5/5 (3)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFFrom EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFNo ratings yet

- Programming with STM32: Getting Started with the Nucleo Board and C/C++From EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Rating: 3.5 out of 5 stars3.5/5 (3)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxFrom EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxNo ratings yet

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertFrom EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertRating: 3.5 out of 5 stars3.5/5 (6)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsFrom EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsRating: 5 out of 5 stars5/5 (2)

- Raspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesFrom EverandRaspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesNo ratings yet

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideFrom EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideRating: 1 out of 5 stars1/5 (1)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002From EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Rating: 5 out of 5 stars5/5 (1)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]From EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Rating: 5 out of 5 stars5/5 (2)

- Real-Time UML Workshop for Embedded SystemsFrom EverandReal-Time UML Workshop for Embedded SystemsRating: 3.5 out of 5 stars3.5/5 (2)

- How To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsFrom EverandHow To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsNo ratings yet

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XFrom EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XRating: 5 out of 5 stars5/5 (1)

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714829744?v=1)