Professional Documents

Culture Documents

CA Classes-201-205

Uploaded by

SrinivasaRaoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CA Classes-201-205

Uploaded by

SrinivasaRaoCopyright:

Available Formats

Computer Architecture Unit 9

facilitate high-speed vector processing. The vector processor control is

contained in the stream unit. The string and all logical operations are

performed in the string unit. The memory interface provides the read and

write ports of central memory for the scalar and vector processors. Each

port contains a one-SWORD (512-bit Super Word) buffer to facilitate high

transfer rates. The CPU processes input and output by issuing relatively

simple high-level messages to high-speed peripheral stations or a front-end

processor connected to the input/output ports.

9.3.2 Vector register architecture

In a vector-register processor, the entire vector operations excluding load

and store are in the midst of the vector registers. Such architectures are the

vector equivalent of load-store architecture. Since the late 1980s, all major

vector computers have been using a vector-register architecture which

includes the Cray Research processors (Cray-1, Cray-2, X-MP, YMP, C90,

T90 and SV1), Japanese supercomputers (NEC SX/2 through SX/5, Fujitsu

VP200 through VPP5000, and the Hitachi S820 and S-8300), and the mini-

supercomputers(Convex C-1 through C-4).

All vector operations are memory to memory in a memory-memory vector

processor, the initial vector computers and CDC’s vector computers were of

such kind. Vector register architectures possess various benefits over vector

memory-memory architectures. It is necessary for the vector memory-

memory architecture to write the entire intermediate outcomes to memory

as well as later on read them back from memory. Vector register

architecture is able to maintain intermediate outcomes in the vector

registers just near to the vector functional units, decreasing temporary

storage needs, inter-instruction latency and memory bandwidth needs.

In case a vector outcome is required by multiple other vector instructions,

memory-memory architecture should read it from memory innumerable

times; while a vector register machine can use the value from vector

registers once again, thereby decreasing memory bandwidth needs. For

such reasons, vector register machines have proved to be more effective

practically.

Components of a vector register processor: The major components of

the vector unit of a vector register machine are as given below:

Manipal University of Jaipur B1648 Page No. 201

Computer Architecture Unit 9

1. Vector registers: There are many vector registers that can perform

different vector operations in an overlapped manner. Every vector

register is a fixed-length bank that consists of one vector with multiple

elements and each element is 64-bit in length. There are also many

read and write ports. A pair of crossbars connects these ports to the

inputs/ outputs of functional unit.

2. Scalar registers: The scalar registers are also linked to the functional

units with the help of the pair of crossbars. They are used for various

purposes such as computing addresses for passing to the vector

load/store unit and as buffer for input data to the vector registers.

3. Vector functional units: These units are generally floating-point units

that are completely pipelined. They are able to initiate a new operation

on each clock cycle. They comprise all operation units that are utilised

by the vector instructions.

4. Vector load and store unit: This unit can also be pipelined and perform

an overlapped but independent transfer to or from the vector registers.

5. Control unit: This unit decodes and coordinates among functional units.

It can detect data hazards as well as structural hazards. Data hazards

are the conflicts in register accesses while functional hazards are the

conflicts in functional units.

Figure 9.1 gives you a clear picture of the above mentioned functional units

of vector processor.

Main

FP add/subtract

Memory

FP multiply

Vector

Load/Store FP divide

Logical

Vector

Integer

Registers

Scalar

Registers

Figure 9.1: Vector Register Architecture

Manipal University of Jaipur B1648 Page No. 202

Computer Architecture Unit 9

Types of Vector Instructions: The various types of vector instructions for a

register-register vector processor are:

(a) Vector-scalar instructions

(b) Vector-vector instructions

(c) Vector-memory instructions

(d) Gather and scatter instructions

(e) Masking instructions

(f) Vector reduction instructions

Let us discuss these.

(a) Vector-scalar instructions: Using these instructions, a scalar operand

can be combined with a vector one. If A and B are vector registers and

f is a function that performs some operation on each element of a

single or two vector operands, a vector-scalar operand can be defined

as follows:

Ai: = f (scalar, Bi)

(b) Vector-vector instructions: Using these instructions, one or two

vector operands are fetched from respective vector registers and

produce results in another vector register. If A, B, and C are three

vector registers, a vector-vector operand can be defined as follows:

Ai: = f (Bi, Ci)

(c) Vector-memory instructions: These instructions correspond to vector

load or vector store. The vector load can be defined as follows:

A: = f (M) where M is a memory register

The vector store can be defined as follows:

M: = f (A)

(d) Gather and scatter instructions: Gather is an operation that fetches

the non-zero elements of a sparse vector from memory as defined

below:

A x Vo: = f (M)

Scatter stores a vector in a sparse vector into memory as defined

below:

M: = f (A x Vo)

Manipal University of Jaipur B1648 Page No. 203

Computer Architecture Unit 9

(e) Masking instructions: These instructions use a mask vector to

expand or compress a vector as defined below:

V = f (A x VM) where V is a mask vector

(f) Vector reduction instructions: These instructions accept one or two

vectors as input and produce a scalar as output.

Vector processor implementation (CRAY-1): CRAY-1 is one of the oldest

processors that implemented vector processing. CRAY-1 is considered as

the world's first vector supercomputer. It was introduced in 1975 by

Seymour Cray. It is basically a register-oriented RISC-like machine requiring

all operands to be in registers. It has five kinds of registers:

(a) A registers: A set of 8 24-bit registers

(b) B registers: A set of 64 24-bit registers

(c) S registers: A set of 8 64-bit registers

(d) T registers: A set of 64 64-bit registers

(e) Vector registers: A set of 8 64-element floating point registers

There are12 functional units in CRAY-1:

(a) 2 24-bit units for address calculation

(b) 4 64-bit integer scalar units for integer operations

(c) 6 deeply pipelined units for vector operations

CRAY-1 uses 16-bit instructions. All vector operations can be executed in

one 16-bit instruction. The block diagram of CRAY-1 architecture is shown

in figure 9.2.

Manipal University of Jaipur B1648 Page No. 204

Computer Architecture Unit 9

Vector

Unit

VM

RTC FP Units

T00-T63

16-way Interleaved Memory

Scalar

Unit

VL

B00-B63

Address

Registers Address

Unit

PC

Instruction

Buffers

NIP CIP

LIP

Figure 9.2: Architecture of CRAY-1

Self Assessment Questions

3. _________________ is a modern shared-memory multiprocessor

version of the CDC Cyber 205 _________________.

4. The memory-memory vector processors can prove to be much efficient

in case the vectors are sufficiently long. (True/False)

5. The scalar registers are linked to the functional units with the help of a

pair of ____________________.

6. ______________ correspond to vector load or vector store.

7. Functional hazards are the conflicts in register accesses. (True/False)

Manipal University of Jaipur B1648 Page No. 205

You might also like

- BCS-o11 Solved Assignment 2022-2023: Q1. (Covers Block 1)Document40 pagesBCS-o11 Solved Assignment 2022-2023: Q1. (Covers Block 1)Anish kumar Das100% (1)

- Problem 1 A) Considering The Number of Instructions Here To Be A Constant ADocument13 pagesProblem 1 A) Considering The Number of Instructions Here To Be A Constant Akhang nguyenNo ratings yet

- CA Classes-211-215Document5 pagesCA Classes-211-215SrinivasaRaoNo ratings yet

- Performance Analysis of MAC Unit Using Booth, Wallace Tree, Array and Vedic MultipliersDocument8 pagesPerformance Analysis of MAC Unit Using Booth, Wallace Tree, Array and Vedic MultipliersSanchariniNo ratings yet

- CA Classes-206-210Document5 pagesCA Classes-206-210SrinivasaRaoNo ratings yet

- CA Classes-196-200Document5 pagesCA Classes-196-200SrinivasaRaoNo ratings yet

- Unit 2 - Chapter 2Document29 pagesUnit 2 - Chapter 2Pallavi BhartiNo ratings yet

- Unit Iii - AcaDocument13 pagesUnit Iii - AcaAnitha DenisNo ratings yet

- Bangabandhu Sheikh Mujibur Rahman Maritime University BangladeshDocument7 pagesBangabandhu Sheikh Mujibur Rahman Maritime University BangladeshSyed Mohaiminul Haque BrintoNo ratings yet

- Data-Level Parallelism in Vector, SIMD, and GPU ArchitecturesDocument58 pagesData-Level Parallelism in Vector, SIMD, and GPU ArchitecturesDhananjai YadavNo ratings yet

- Param MP MC QUESTION BANKDocument47 pagesParam MP MC QUESTION BANKparameswaran SNo ratings yet

- 7-VECTOR PROCESSING-04-Jan-2020Material - I - 04-Jan-2020 - VECTOR - PROCESSING PDFDocument31 pages7-VECTOR PROCESSING-04-Jan-2020Material - I - 04-Jan-2020 - VECTOR - PROCESSING PDFANTHONY NIKHIL REDDYNo ratings yet

- CH 2 Vector ProcessingDocument16 pagesCH 2 Vector Processingdigvijay dholeNo ratings yet

- Unit 2 - Chapter 2Document29 pagesUnit 2 - Chapter 2Pallavi BhartiNo ratings yet

- MP PDFDocument43 pagesMP PDFPodhigaiEceNo ratings yet

- Computing Performance Enhancement of VLIW Architecture Using Instruction Level ParallelismDocument5 pagesComputing Performance Enhancement of VLIW Architecture Using Instruction Level ParallelismInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- New Prince Shri Bhavani College of Engineering and TechnologyDocument40 pagesNew Prince Shri Bhavani College of Engineering and Technology1987parthiNo ratings yet

- Cell Broadband Engine Implementations: Viterbi Decoder: Nadia Akhtar MT2009007 (Cell: 9538308949)Document12 pagesCell Broadband Engine Implementations: Viterbi Decoder: Nadia Akhtar MT2009007 (Cell: 9538308949)FRB123No ratings yet

- Conference Template A4Document4 pagesConference Template A4ATHIRA V RNo ratings yet

- MPMC Q.bankDocument12 pagesMPMC Q.bankKaviya dharshini S -ECE-028No ratings yet

- Design of A 32-Bit Dual Pipeline Superscalar RISC-V Processor On FPGADocument4 pagesDesign of A 32-Bit Dual Pipeline Superscalar RISC-V Processor On FPGASRIRAAM VSNo ratings yet

- Out of Order Floating Point Coprocessor For RISC V ISADocument7 pagesOut of Order Floating Point Coprocessor For RISC V ISAkiranNo ratings yet

- Simple Vector Processor Modeled With VHDLDocument6 pagesSimple Vector Processor Modeled With VHDLduzngvt123No ratings yet

- SS Question BankssDocument72 pagesSS Question BankssAdvika RoyNo ratings yet

- EE 346 Microprocessor Principles and Applications An Introduction To Microcontrollers, Assembly Language, and Embedded SystemsDocument40 pagesEE 346 Microprocessor Principles and Applications An Introduction To Microcontrollers, Assembly Language, and Embedded SystemsAbG Compilation of VideosNo ratings yet

- CS Syllabus (3rd Sem)Document4 pagesCS Syllabus (3rd Sem)KashifNo ratings yet

- Timing and Control Unit: ALU Flags 8-Bit Data BusDocument12 pagesTiming and Control Unit: ALU Flags 8-Bit Data BusMarieFernandesNo ratings yet

- Lecture 20: Data Level Parallelism - Introduction and Vector ArchitectureDocument47 pagesLecture 20: Data Level Parallelism - Introduction and Vector ArchitecturePhani KumarNo ratings yet

- Fundamentals of Parallel Processing: By: Solomon SDocument35 pagesFundamentals of Parallel Processing: By: Solomon SAmanuelNo ratings yet

- Migration V3 - PCS7 V7.1: Configuration ManualDocument30 pagesMigration V3 - PCS7 V7.1: Configuration ManualmicahxNo ratings yet

- For Example: C (1:50) A (1:50) + B (1:50)Document7 pagesFor Example: C (1:50) A (1:50) + B (1:50)Sathish A AvnNo ratings yet

- Coa Unit Test QP 1Document7 pagesCoa Unit Test QP 1Sagar K DedhiaNo ratings yet

- Cao 2012Document116 pagesCao 2012nskprasad890% (1)

- CA I - Chapter 2 ISA 2 RISC VDocument66 pagesCA I - Chapter 2 ISA 2 RISC VDuc ToanNo ratings yet

- Risc Processor Using VHDLDocument5 pagesRisc Processor Using VHDLAruna RajanNo ratings yet

- Cruose ProcessorDocument30 pagesCruose Processorapi-3827000No ratings yet

- Crusoe Processor Auto Saved)Document21 pagesCrusoe Processor Auto Saved)renubingeriNo ratings yet

- Ec8691-5 Units MPMC NotesDocument165 pagesEc8691-5 Units MPMC NotesSureka N Assistant Professor - ECENo ratings yet

- ModsdDocument7 pagesModsdnurali arfanNo ratings yet

- Migration V1.8/V1.9/V2 - PCS7 V7.1: Configuration ManualDocument29 pagesMigration V1.8/V1.9/V2 - PCS7 V7.1: Configuration ManualmicahxNo ratings yet

- An Introduction To Vectorization With Intel Fortran Compiler 021712Document6 pagesAn Introduction To Vectorization With Intel Fortran Compiler 021712kameliyaNo ratings yet

- Computer Archtecture Lecture Notes PDFDocument66 pagesComputer Archtecture Lecture Notes PDFjose_mario1128No ratings yet

- Dell. Building An Open vRAN Ecosystem.2020Document14 pagesDell. Building An Open vRAN Ecosystem.2020Pavel SchukinNo ratings yet

- Advanced VLSI Architecture: Lecture 23 - 24: Data Level ParallelismDocument27 pagesAdvanced VLSI Architecture: Lecture 23 - 24: Data Level ParallelismUdai ValluruNo ratings yet

- PowerDocument6 pagesPowerParasaram SrinivasNo ratings yet

- Assignment 1 Microprocessors and Embedded Systems Nov 23 (AutoRecovered)Document8 pagesAssignment 1 Microprocessors and Embedded Systems Nov 23 (AutoRecovered)Courtney Kudra DzereNo ratings yet

- Arduino Interrupciones ManualesDocument7 pagesArduino Interrupciones Manualesleonar3177No ratings yet

- Altivec ProgrammingDocument67 pagesAltivec ProgrammingbongoloidNo ratings yet

- CA Classes-236-240Document5 pagesCA Classes-236-240SrinivasaRaoNo ratings yet

- Unit Iii Data-Level Parallelism in Vector, Simd, and Gpu ArchitecturesDocument26 pagesUnit Iii Data-Level Parallelism in Vector, Simd, and Gpu ArchitecturesShwetaNo ratings yet

- CH 04. Data-Level Parallelism in Vector, SIMD, and GPU ArchitecturesDocument50 pagesCH 04. Data-Level Parallelism in Vector, SIMD, and GPU ArchitecturesFaheem KhanNo ratings yet

- Fundamentals of Microprocessor and Microcontroller: Dr. Farid FarahmandDocument42 pagesFundamentals of Microprocessor and Microcontroller: Dr. Farid Farahmandsivakrishna nadakuduruNo ratings yet

- Avispado 222 DataSheetDocument16 pagesAvispado 222 DataSheetRicardo CoelhoNo ratings yet

- Data-Level Parallelism: Nima HonarmandDocument59 pagesData-Level Parallelism: Nima HonarmandwarriorsNo ratings yet

- Unit-5: Cocurrent Processors: Vector & Multiple Instruction Issue ProcessorsDocument106 pagesUnit-5: Cocurrent Processors: Vector & Multiple Instruction Issue ProcessorsJitender GargNo ratings yet

- Unit - Ii System Bus Structure: Course Material (Question Bank)Document8 pagesUnit - Ii System Bus Structure: Course Material (Question Bank)Haritha HariNo ratings yet

- 2 Marks With AnswersDocument14 pages2 Marks With Answersprisci_durai83% (6)

- Telecom Digsig AnDocument8 pagesTelecom Digsig Anapi-19790923No ratings yet

- Computer Architecture AllClasses-Outline-1-99Document99 pagesComputer Architecture AllClasses-Outline-1-99SrinivasaRaoNo ratings yet

- Computer Architecture AllClasses-OutlineDocument294 pagesComputer Architecture AllClasses-OutlineSrinivasaRaoNo ratings yet

- Computer Architecture AllClasses-Outline-100-198Document99 pagesComputer Architecture AllClasses-Outline-100-198SrinivasaRaoNo ratings yet

- CA Classes-261-265Document5 pagesCA Classes-261-265SrinivasaRaoNo ratings yet

- CA Classes-236-240Document5 pagesCA Classes-236-240SrinivasaRaoNo ratings yet

- CA Classes-251-255Document5 pagesCA Classes-251-255SrinivasaRaoNo ratings yet

- CA Classes-246-250Document5 pagesCA Classes-246-250SrinivasaRaoNo ratings yet

- CA Classes-141-145Document5 pagesCA Classes-141-145SrinivasaRaoNo ratings yet

- CA Classes-86-90Document5 pagesCA Classes-86-90SrinivasaRaoNo ratings yet

- CA Classes-176-180Document5 pagesCA Classes-176-180SrinivasaRaoNo ratings yet

- CA Classes-216-220Document5 pagesCA Classes-216-220SrinivasaRaoNo ratings yet

- CA Classes-221-225Document5 pagesCA Classes-221-225SrinivasaRaoNo ratings yet

- CA Classes-186-190Document5 pagesCA Classes-186-190SrinivasaRaoNo ratings yet

- CA Classes-121-125Document5 pagesCA Classes-121-125SrinivasaRaoNo ratings yet

- CA Classes-126-130Document5 pagesCA Classes-126-130SrinivasaRaoNo ratings yet

- CA Classes-111-115Document5 pagesCA Classes-111-115SrinivasaRaoNo ratings yet

- CA Classes-101-105Document5 pagesCA Classes-101-105SrinivasaRaoNo ratings yet

- CA Classes-36-40Document5 pagesCA Classes-36-40SrinivasaRaoNo ratings yet

- CA Classes-106-110Document5 pagesCA Classes-106-110SrinivasaRaoNo ratings yet

- CA Classes-116-120Document5 pagesCA Classes-116-120SrinivasaRaoNo ratings yet

- CA Classes-26-30Document5 pagesCA Classes-26-30SrinivasaRaoNo ratings yet

- Programming in C - 121-140Document20 pagesProgramming in C - 121-140SrinivasaRaoNo ratings yet

- Programming in C - 21-40Document20 pagesProgramming in C - 21-40SrinivasaRaoNo ratings yet

- CA Classes-16-20Document5 pagesCA Classes-16-20SrinivasaRaoNo ratings yet

- Programming in C - 216-220Document5 pagesProgramming in C - 216-220SrinivasaRaoNo ratings yet

- Programming in C - 161-180Document20 pagesProgramming in C - 161-180SrinivasaRaoNo ratings yet

- Programming in C - 41-60Document20 pagesProgramming in C - 41-60SrinivasaRaoNo ratings yet

- CompTIA A+ - 220-1001 - Core 1 - 50 QuestionsDocument15 pagesCompTIA A+ - 220-1001 - Core 1 - 50 QuestionsandreslunaromoNo ratings yet

- Epson Stylus Office BX935FWD Brochures 2Document2 pagesEpson Stylus Office BX935FWD Brochures 2Beata BaricsanNo ratings yet

- Konica Minolta PagePro 1400W User ManualDocument90 pagesKonica Minolta PagePro 1400W User ManualSMART REFILLNo ratings yet

- Untitled5 - Jupyter NotebookDocument11 pagesUntitled5 - Jupyter NotebookGupta Anacoolz100% (1)

- WINDOWS Driver InstallationDocument9 pagesWINDOWS Driver Installationhilya qaanitaNo ratings yet

- Chapter 3 - Input and OutputDocument63 pagesChapter 3 - Input and OutputKhairul AkmaNo ratings yet

- Duroflex Summer Price ListDocument48 pagesDuroflex Summer Price ListHans de WitNo ratings yet

- WWW - Teknisi Indonesia - com.GA H61M S2P R3Document33 pagesWWW - Teknisi Indonesia - com.GA H61M S2P R3Jayesh DalviNo ratings yet

- Running Case With Real Data Dell Direct PDFDocument6 pagesRunning Case With Real Data Dell Direct PDFaasthaNo ratings yet

- Toshiba Tecra A6 Service ManualDocument283 pagesToshiba Tecra A6 Service ManualAbu BongoNo ratings yet

- a094mMPMC Multiple Choice QuestionsDocument7 pagesa094mMPMC Multiple Choice QuestionsVenkata SureshNo ratings yet

- Technology in Education Technology Presentation in Blue Peach Illustrative StyleDocument37 pagesTechnology in Education Technology Presentation in Blue Peach Illustrative StyleAngel “Miley” SamileyNo ratings yet

- Simatic S5: S5EPROM For USB PrommerDocument10 pagesSimatic S5: S5EPROM For USB PrommerAdi SupriadiNo ratings yet

- Main Memory ManagementDocument7 pagesMain Memory ManagementpoojajadhavNo ratings yet

- History of NseDocument9 pagesHistory of NseadesloopNo ratings yet

- Introduction: What Is A Real Time System? What Is An Embedded System? What Is A Rtos/Rtes?Document8 pagesIntroduction: What Is A Real Time System? What Is An Embedded System? What Is A Rtos/Rtes?Nikhil KulkarniNo ratings yet

- Advanced System Programmers Guide For The AmigaDocument580 pagesAdvanced System Programmers Guide For The AmigaAsaf Ayoub0% (1)

- Ricoh Pro 8200S Pro 8210S Pro 8220S: Black and White Production PrinterDocument8 pagesRicoh Pro 8200S Pro 8210S Pro 8220S: Black and White Production PrinterLa Gota INKNo ratings yet

- Brochure HHMPI V4Document4 pagesBrochure HHMPI V4Ari Prasetio AjiNo ratings yet

- How To Replace A SPARC T5-4 or T5-8 Server Main Module MotherboardDocument6 pagesHow To Replace A SPARC T5-4 or T5-8 Server Main Module Motherboardvijayen123No ratings yet

- A List of Programmable and Non Programmable KBC MicrocontrollerDocument6 pagesA List of Programmable and Non Programmable KBC MicrocontrollerRubén Pérez Armas100% (2)

- 20150909codCH05 Solution PDFDocument26 pages20150909codCH05 Solution PDFAya YasserNo ratings yet

- Certificate For Reimbrusement of TabletDocument1 pageCertificate For Reimbrusement of TabletJaspreet AroraNo ratings yet

- RTC InterfacingDocument18 pagesRTC InterfacingAshis karmakarNo ratings yet

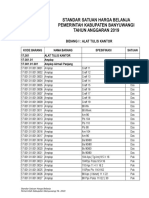

- Standart Harga 2019Document515 pagesStandart Harga 2019Anonymous dWe4nB8cJhNo ratings yet

- Hanna - Effects of The Wide Use of Technology in The Academic Performance of Senior High School Students in Aroroy National High SchoolDocument49 pagesHanna - Effects of The Wide Use of Technology in The Academic Performance of Senior High School Students in Aroroy National High SchoolHerminio Victor ValdemoroNo ratings yet

- OS Assignment 1&2 SolutionDocument6 pagesOS Assignment 1&2 Solutionlokendra singhNo ratings yet

- ISPnub - Stand-Alone AVR in-System-Programmer Module - FischDocument2 pagesISPnub - Stand-Alone AVR in-System-Programmer Module - FischNedim CurtNo ratings yet

- 8-Bit Microcontroller With 16/32/64/128K Bytes In-System Programmable FlashDocument30 pages8-Bit Microcontroller With 16/32/64/128K Bytes In-System Programmable FlashGaara564No ratings yet