Professional Documents

Culture Documents

Quizz

Quizz

Uploaded by

kalshkinguCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Quizz

Quizz

Uploaded by

kalshkinguCopyright:

Available Formats

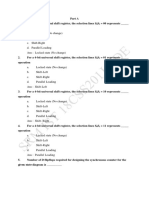

Q-15 is Mandatory and must be completed by every student and provide your answers for

additional four questions.

1. A four-bit ring counter and a four-bit Johnson counter are in turn clocked by a 10 MHz clock

signal. Determine the frequency and duty cycle of the output of the output flip-flop in the two

cases.

2. Determine the number of flip-flops required to construct (a) a MOD-10 ring counter and (b) a

MOD-10 Johnson counter. Also, write the count sequence in the two cases.

3. Show state diagram of a modulo-4 counter?

4. What do we mean by shifting left (i) a binary word 1001 0101 (ii) word 0010 0101 1001 0100? If

we shift twice then what will be the result.

5. The output frequency of a Mod-16 counter, clocked from a 10kHz clock input signal is a) 10 kHz

b) 26 kHz c) 160 kHz d) 625 Hz

6. The number stored in a 4-bit binary up-counter is 0101. What will be state of the counter after

the following clock pulses? (a) 3rd clock pulse (b) 5th clock pulse (c) 8th clock pulse (d) 12th

clock pulse

7. A binary number is to be divided by 64. By how many positions will you shift the number and in

what direction.

8. With a 100 kHz clock frequency, eight bits can be serially entered into a shift register in ___

seconds.

9. The sequence 1011 is applied to the input of a 4-bit serial shift register that is initially cleared.

What is the state of the shift register after three clock pulses?

10. A shift register has seven flip flops. What is the largest binary number that can be stored in it?

Octal number? Decimal number? Hexadecimal number?

11. What is the basic difference between a latch and a flip-flop?

12. Assume the clock for a 4-bit binary counter is 80 kHz. The output frequency of the fourth stage

(Q3) is

13. A four-bit binary UP counter is initially in the 0000 state. Then the clock pulses are applied. Some

time later the clock pulses are removed, and at that the counter is observed to be in the 0011

state. What is the minimum number of clock pulses that could possibly have occurred?

14. An eight-bit binary ripple UP counter with a modulus of 256 is holding the count 01111111.

What will be the count after 135 clock pulses be?

15. Design of a 2 bit SISO shift register which shifts from left to right if mode is 1 and right to left if

mode is 0.

You might also like

- Tutorial Sheet 8Document2 pagesTutorial Sheet 8ashish_jiitNo ratings yet

- Interview Questions 1Document40 pagesInterview Questions 1Shru GopalNo ratings yet

- Questions & Answers On CountersDocument24 pagesQuestions & Answers On Counterskibrom atsbha100% (2)

- Lab Experiment Design of Asynchronous and Synchronous CounterDocument6 pagesLab Experiment Design of Asynchronous and Synchronous CounterMani Bharathi57% (7)

- Ring Counters and Johnson CounterDocument8 pagesRing Counters and Johnson CountermailmeasddNo ratings yet

- Digital Design Interview QuestionsDocument47 pagesDigital Design Interview QuestionsSangameshwer Enterprises100% (1)

- Digital Design Interview QuestionsDocument12 pagesDigital Design Interview QuestionsUday Udu100% (8)

- Questions On RegistersDocument14 pagesQuestions On Registerskibrom atsbha100% (1)

- Johnson Ring CounterDocument8 pagesJohnson Ring CounterJohn Brix BalisterosNo ratings yet

- Unit-5 QBDocument28 pagesUnit-5 QBekvblsa vksvlijierigbNo ratings yet

- 2013 Wwk6 Counter 1 (Design of Counters) - Portal - vg3Document90 pages2013 Wwk6 Counter 1 (Design of Counters) - Portal - vg3Alips TurnerNo ratings yet

- Consequence LogicDocument83 pagesConsequence LogicLai Yon PengNo ratings yet

- Shift RegistersDocument8 pagesShift RegistersJohn Arman ArcayaNo ratings yet

- Ring CountersDocument10 pagesRing CountersMr.Vishal ShethNo ratings yet

- 7 Counters PDFDocument13 pages7 Counters PDFsaraswatthiNo ratings yet

- Tutorial Shift Register (Ans)Document7 pagesTutorial Shift Register (Ans)Symphony DreamsNo ratings yet

- Counter RegistersDocument108 pagesCounter RegistersAkshay RFNo ratings yet

- Digital Electronics Question PaperDocument14 pagesDigital Electronics Question PaperAruna N LNo ratings yet

- Counters: Compiled By: Afaq Alam KhanDocument28 pagesCounters: Compiled By: Afaq Alam KhanRajeshwari SNo ratings yet

- Ans 8 Floyd DigitalDocument7 pagesAns 8 Floyd DigitalRovina LacunaNo ratings yet

- Digital System Design - UEC 612 Tutorial# 8Document1 pageDigital System Design - UEC 612 Tutorial# 8Lakshit GuptaNo ratings yet

- Astable Multivibrator Based Decade CounterDocument11 pagesAstable Multivibrator Based Decade Counternksingh786No ratings yet

- 9 Counter CircuitsDocument9 pages9 Counter CircuitsWaseem AhmadNo ratings yet

- 6 CountersDocument61 pages6 CountersRJ AdepuNo ratings yet

- (Counter) Paper - 1 - 7967 - 163 PDFDocument57 pages(Counter) Paper - 1 - 7967 - 163 PDFmaprofNo ratings yet

- Counters & Shifters: by Dr. Alok Kumar Rastogi Professor of Physics Department of Physics & Electronics IEHE, BhopalDocument45 pagesCounters & Shifters: by Dr. Alok Kumar Rastogi Professor of Physics Department of Physics & Electronics IEHE, BhopalKritiiNo ratings yet

- Binary Coded DecimalDocument4 pagesBinary Coded DecimalKelvin YipNo ratings yet

- Binarry Counter CircuitsDocument16 pagesBinarry Counter CircuitsAhmed Shoukr MohammedNo ratings yet

- CountersDocument25 pagesCountersSonam SoniNo ratings yet

- Asynchronous CounterDocument9 pagesAsynchronous CounterzaidNo ratings yet

- A 4-Stage Johnson Counter Divides by 8Document13 pagesA 4-Stage Johnson Counter Divides by 8PrashantNirmalNo ratings yet

- Asynchronous Counters: Asynchronous 4-Bit UP CounterDocument13 pagesAsynchronous Counters: Asynchronous 4-Bit UP CounterAbhiNo ratings yet

- 3 - Counters PPT (DLP-2021-22)Document16 pages3 - Counters PPT (DLP-2021-22)SohneaNo ratings yet

- Registers Question BankDocument2 pagesRegisters Question BankSanchit RkNo ratings yet

- MA Viva BankDocument9 pagesMA Viva BankManish NarkhedeNo ratings yet

- Chapter 5 RegistersDocument25 pagesChapter 5 Registerssereenkumar0911No ratings yet

- Report TextDocument7 pagesReport TextVica Azka Novalya IINo ratings yet

- Experiment No. 2: Abstract-In This Experiment, The StudentsDocument6 pagesExperiment No. 2: Abstract-In This Experiment, The StudentsShania SarmientoNo ratings yet

- Shift RegistersDocument11 pagesShift RegistersakakaNo ratings yet

- Digital Electronics McqsDocument25 pagesDigital Electronics Mcqskunarajeet17No ratings yet

- Computer Archiecture 1 D3804a15Document5 pagesComputer Archiecture 1 D3804a15Surendra Singh ChauhanNo ratings yet

- Counters in Digital ElectronicsDocument3 pagesCounters in Digital Electronicsdhirajkumar_1No ratings yet

- Digital Electronics Tutorial Sheet-1Document13 pagesDigital Electronics Tutorial Sheet-1shraddhabansalNo ratings yet

- Solution ST1 Set ADocument12 pagesSolution ST1 Set Agaurika.sawhney2003No ratings yet

- CountersDocument16 pagesCountersgargraghav82No ratings yet

- Counter Application1Document15 pagesCounter Application1nick_KGECNo ratings yet

- Chapter 5: Counters: Ee 202 Digital ElectronicsDocument59 pagesChapter 5: Counters: Ee 202 Digital ElectronicsSyazreen RahmanNo ratings yet

- Digital Systems1Document5 pagesDigital Systems1kgovindrajanNo ratings yet

- Digital Logic Design 6 CountersDocument37 pagesDigital Logic Design 6 CountersMurad QəhramanovNo ratings yet

- Counters and Applications of CountersDocument7 pagesCounters and Applications of CountersJayant KirpekarNo ratings yet

- Ring CounterDocument12 pagesRing Counterawa buaya100% (1)

- Shift Register and Its TypesDocument22 pagesShift Register and Its TypeschoprahridyeshNo ratings yet

- 4 Bit Counter Design - Spring 2004Document15 pages4 Bit Counter Design - Spring 2004sandyk_24No ratings yet

- 03 SheetDocument2 pages03 Sheetmohamedems719No ratings yet

- ECE216Document3 pagesECE216Abhishek KumarNo ratings yet

- Lecture 2Document27 pagesLecture 2زياد عبدالله عبدالحميدNo ratings yet

- MSQ Session 5 19Document30 pagesMSQ Session 5 19Voleti VnkumarNo ratings yet

- Unit 5Document11 pagesUnit 5RajaNo ratings yet

- DLD_Chapter_4Document72 pagesDLD_Chapter_4kalshkinguNo ratings yet

- Assignment 2Document2 pagesAssignment 2kalshkinguNo ratings yet

- Chapter OneDocument14 pagesChapter OnekalshkinguNo ratings yet

- JJU Remedial Program Students Results, Social Science 2015 A Y 1Document13 pagesJJU Remedial Program Students Results, Social Science 2015 A Y 1kalshkinguNo ratings yet

- Ch-1 Computational Method 2022Document43 pagesCh-1 Computational Method 2022kalshkinguNo ratings yet

- CH-2 Computational Methods 2022Document8 pagesCH-2 Computational Methods 2022kalshkinguNo ratings yet

- ECEG-2131-AEI-Lec - 07 - DC Biasing of BJTDocument44 pagesECEG-2131-AEI-Lec - 07 - DC Biasing of BJTkalshkinguNo ratings yet