Professional Documents

Culture Documents

ICX098AK: Aaaaa Aaaaa Aaaaa

Uploaded by

Francis TaisantOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ICX098AK: Aaaaa Aaaaa Aaaaa

Uploaded by

Francis TaisantCopyright:

Available Formats

ICX098AK

Diagonal 4.5mm (Type 1/4) Progressive Scan CCD Image Sensor with Square Pixel for Color Cameras Description The ICX098AK is a diagonal 4.5mm (Type 1/4) interline CCD solid-state image sensor with a square pixel array which supports VGA format. Progressive scan allows all pixels signals to be output independently within approximately 1/30 second. Also, the adoption of monitoring mode allows output to an NTSC monitor without passing through the memory. This chip features an electronic shutter with variable charge-storage time which makes it possible to realize full-frame still image without a mechanical shutter. High resolution and high color reproductivity are achieved through the use of R, G, B primary color mosaic filters. Further, high sensitivity and low dark current are achieved through the adoption of HAD (Hole-Accumulation Diode) sensors. This chip is suitable for applications such as electronic still cameras, PC input cameras, etc. Features Progressive scan allows individual readout of the image signals from all pixels. High horizontal and vertical resolution (both approx. 400TV-lines) still image without a mechanical shutter. Supports monitoring mode Square pixel Supports VGA format Horizontal drive frequency: 12.27MHz No voltage adjustments (reset gate and substrate bias are not adjusted.) R, G, B primary color mosaic filters on chip High resolution, high color reproductivity, high sensitivity, low dark current Continuous variable-speed shutter Low smear Excellent antiblooming characteristics Horizontal register: 3.3V drive 14-pin high precision plastic package (enables dual-surface standard) Device Structure Interline CCD image sensor Image size: Number of effective pixels: Total number of pixels: Chip size: Unit cell size: Optical black: Number of dummy bits: Substrate material: 14 pin DIP (Plastic)

Pin 1 2

8 2 Pin 8 H 31

Optical black position (Top View)

Diagonal 4.5mm (Type 1/4) 659 (H) 494 (V) approx. 330K pixels 692 (H) 504 (V) approx. 350K pixels 4.60mm (H) 3.97mm (V) 5.6m (H) 5.6m (V) Horizontal (H) direction: Front 2 pixels, rear 31 pixels Vertical (V) direction: Front 8 pixels, rear 2 pixels Horizontal 16 Vertical 5 Silicon

Wfine CCD is a registered trademark of Sony Corporation. Represents a CCD adopting progressive scan, primary color filter and square pixel. Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

E96533B99

ICX098AK

VOUT

GND

V2B

V2A

VL

V3

B G B G B G

G R G R G R

B G B G B G

Vertical register

R G R G R

Horizontal register Note) : Photo sensor

10

11

12

13

14

Pin Description Pin No. 1 2 3 4 5 6 Symbol V1 V3 V2A V2B VL GND

Description Vertical register transfer clock Vertical register transfer clock Vertical register transfer clock Vertical register transfer clock Protective transistor bias GND

SUB

CSUB

GND

Pin No. 8 9 10 11 12 13

RG

VDD

Symbol VDD GND SUB CSUB RG H1

H1

H2

V1

1 Note)

Block Diagram and Pin Configuration (Top View)

Description Supply voltage GND Substrate clock Substrate bias1 Reset gate clock Horizontal register transfer clock

7 VOUT H2 Horizontal register transfer clock Signal output 14 1 DC bias is generated within the CCD, so that this pin should be grounded externally through a capacitance of 0.1F. Absolute Maximum Ratings Item VDD, VOUT, RG SUB V2A, V2B SUB Against SUB V1, V3, VL SUB H1, H2, GND SUB CSUB SUB VDD, VOUT, RG, CSUB GND Against GND V1, V2A, V2B, V3 GND H1, H2 GND Against VL V2A, V2B VL V1, V3, H1, H2, GND VL Voltage difference between vertical clock input pins Between input H1 H2 clock pins H1, H2 V3 Storage temperature Operating temperature 2 +24V (Max.) when clock width < 10s, clock duty factor < 0.1%. 2 Ratings 40 to +10 50 to +15 50 to +0.3 40 to +0.3 25 to 0.3 to +18 10 to +18 10 to +5 0.3 to +28 0.3 to +15 to +15 5 to +5 13 to +13 30 to +80 10 to +60 Unit V V V V V V V V V V V V V C C 2 Remarks

ICX098AK

Bias Conditions Item Supply voltage Protective transistor bias Substrate clock Reset gate clock Symbol VDD VL SUB RG Min. 14.55 Typ. 15.0 1 2 2 Max. 15.45 Unit V Remarks

1 VL setting is the VVL voltage of the vertical transfer clock waveform, or the same power supply as the VL power supply for the V driver should be used. 2 Do not apply a DC bias to the substrate clock and reset gate clock pins, because a DC bias is generated within the CCD.

DC Characteristics Item Supply current Symbol IDD Min. Typ. 6.0 Max. Unit mA Remarks

Clock Voltage Conditions Item Readout clock voltage VVT VVH02A VVH1, VVH2A, VVH2B, VVH3 VVL1, VVL2A, VVL2B, VVL3 Vertical transfer clock voltage V1, V2A, V2B, V3 | VVL1 VVL3 | VVHH VVHL VVLH VVLL Horizontal transfer clock voltage Reset gate clock voltage Substrate clock voltage VH VHL VRG VRGLH VRGLL VRGL VRGLm VSUB 19.75 20.5 3.0 0.05 3.0 3.3 0 3.3 Symbol Min. 14.55 0.05 0.2 5.8 5.2 Typ. 15.0 0 0 5.5 5.5 Max. 15.45 0.05 0.05 5.2 5.8 0.1 0.3 1.0 0.5 0.5 5.25 0.05 5.5 0.4 0.5 21.25 Unit V V V V V V V V V V V V V V V V Waveform diagram 1 2 2 2 2 2 2 2 2 2 3 3 4 4 4 5 Low-level coupling Low-level coupling High-level coupling High-level coupling Low-level coupling Low-level coupling VVL = (VVL1+VVL3)/2 VVH = VVH02A Remarks

ICX098AK

Clock Equivalent Circuit Constant Item Capacitance between vertical transfer clock and GND Symbol CV1 CV2A, CV2B CV3 CV12A, CV2B1 Capacitance between vertical transfer clocks Capacitance between horizontal transfer clock and GND Capacitance between horizontal transfer clocks Capacitance between reset gate clock and GND Capacitance between substrate clock and GND CV2A3, CV32B CV13 CH1, CH2 CHH CRG CSUB R1 Vertical transfer clock series resistor R2A, R2B R3 Vertical transfer clock ground resistor Horizontal transfer clock series resistor Horizontal transfer clock ground resistor Reset gate clock series resistor

V1 CV12A

Min.

Typ. 1200 470 2200 470 390 10 22 68 3 220 20 43 36 43 12 30 62

Max.

Unit pF pF pF pF pF pF pF pF pF pF k

Remarks

RGND RH RH2 RRG

V2A

R1

R2A RH H1 RH H2 CHH CV2A3 CV13 CH1 CH2 RH2

CV1 CV2B1

CV2A

CV2B RGND CV3 R2B CV32B R3

V2B

V3

Vertical transfer clock equivalent circuit

Horizontal transfer clock equivalent circuit

RRG RG

CRG

Reset gate clock equivalent circuit

ICX098AK

Drive Clock Waveform Conditions (1) Readout clock waveform

VT 100% 90%

II II

M M 2 tf 0V

VVT 10% 0% tr twh

Note) Readout clock is used by composing vertical transfer clocks V2A and V2B.

(2) Vertical transfer clock waveform

V1 VVHL VVH1 VVHH VVH

VVLH VVL01 VVL1 VVLL V2A, V2B VVH02A, VVH02B VVHH VVHL VVH2A, VVH2B VVL

VVH

VVLH VVL2A, VVL2B VVLL V3 VVHL VVH3 VVL

VVHH

VVH

VVL03 VVLL

VVLH

VVL

VVH = VVH02A VVL = (VVL01 + VVL03) /2 VVL3 = VVL03

VV1 = VVH1 VVL01 VV2A = VVH02A VVL2A VV2B = VVH02B VVL2B VV3 = VVH3 VVL03

ICX098AK

(3) Horizontal transfer clock waveform

tr H2 90% VCR VH 10% H1 two VH 2 twh tf

twl

VHL

Cross-point voltage for the H1 rising side of the horizontal transfer clocks H1 and H2 waveforms is VCR. The overlap period for twh and twl of horizontal transfer clocks H1 and H2 is two. (4) Reset gate clock waveform

tr twh tf

RG waveform

VRGH

twl VRG Point A VRGLH VRGLL VRGLm VRGL

VRGLH is the maximum value and VRGLL is the minimum value of the coupling waveform during the period from Point A in the above diagram until the rising edge of RG. In addition, VRGL is the average value of VRGLH and VRGLL. VRGL = (VRGLH + VRGLL)/2 Assuming VRGH is the minimum value during the interval twh, then: VRG = VRGH VRGL Negative overshoot level during the falling edge of RG is VRGLm.

(5) Substrate clock waveform

100% 90%

M VSUB 10% 0% VSUB (A bias generated within the CCD) M 2 tf

tr

twh

ICX098AK

Clock Switching Characteristics Item Readout clock Vertical transfer clock Horizontal transfer clock During imaging Symbol VT V1, V2A, V2B, V3 H1 H2 25.5 30.5 28 33 28 33 9 9 0.01 0.01 11 12 63.5 3 16.5 14 twh twl tr tf Unit s 350 9 9 0.01 0.01 3 16.5 14 ns ns Remarks During readout 1 2

Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. 2.3 2.5 0.5 15 0.5

25.5 30.5

During H1 parallel-serial H2 conversion RG SUB

s ns During drain charge

Reset gate clock

Substrate clock

1.5 1.8

0.5

0.5

1 When vertical transfer clock driver CXD1267AN is used. 2 tf tr 2ns, and the cross-point voltage (VCR) for the H1 rising side of the H1 and H2 waveforms must be at least VH/2 [V].

two Item Horizontal transfer clock Symbol H1, H2 Min. Typ. Max. 21.5 25.5 Unit ns Remarks

Spectral Sensitivity Characteristics (includes lens characteristics, excludes light source characteristics)

1 G

B 0.8

Relative Response

0.6

0.4

0.2

0 350 400 450 500 550 600 650 700

Wave Length [nm]

ICX098AK

Image Sensor Characteristics Item G sensitivity Sensitivity comparison Saturation signal Smear Video signal shading Uniformity between video signal channels Dark signal Dark signal shading Line crawl G Line crawl R Line crawl B Lag R B Symbol Sg Rr Rb Vsat Sm SHg Srg Sbg Vdt Vdt Lcg Lcr Lcb Lag Min. 350 0.3 0.4 500 0.001 0.0025 20 25 8 8 4 1 3.8 3.8 3.8 0.5 Typ. 440 0.45 0.55 0.6 0.7 mV % % % % % mV mV % % % % Max. Unit mV Measurement method 1 1 1 2 3 4 4 5 5 6 7 8 8 8 9

(Ta = 25C) Remarks

Ta = 60C

Zone 0 and I Zone 0 to II'

Ta = 60C Ta = 60C

Zone Definition of Video Signal Shading

659 (H) 12 12 12 H 8

H 8

V 10

494 (V)

Zone 0, I Zone II, II' V 10

10

Ignored region Effective pixel region

Measurement System

CCD signal output [A] Gr/Gb CCD C.D.S

AMP

S/H R/B S/H

Gr/Gb channel signal output [B]

R/B channel signal output [C]

Note) Adjust the amplifier gain so that the gain between [A] and [B], and between [A] and [C] equals 1. 8

ICX098AK

Image Sensor Characteristics Measurement Method Color coding and readout of this image sensor Gb R Gb R B Gr B Gr Gb R Gb R B Gr B Gr The primary color filters of this image sensor are arranged in the layout shown in the figure on the left (Bayer arrangement). Gr and Gb denote the G signals on the same line as the R signal and the B signal, respectively.

Horizontal register Color Coding Diagram All pixels signals are output successively in a 1/30s period. The R signal and Gr signal lines and the Gb signal and B signal lines are output successively. Readout modes The diagram below shows the output methods for the following two readout modes. Progressive scan mode

7 6 5 4 3 2 1 VOUT

Monitoring mode

7 6 5 4 3 2 1 VOUT

R G R G R G R

G B G B G B G

R G R G R G R

G B G B G B G

Note) Blacked out portions in the diagram indicate pixels which are not read out. 1. Progressive scan mode In this mode, all pixel signals are output in non-interlace format in 1/30s. The vertical resolution is approximately 400TV-lines and all pixel signals within the same exposure period are read out simultaneously, making this mode suitable for high resolution image capturing. 2. Monitoring mode The signals for all effective areas are output during a single field period of NTSC standard (approximately 1/60s) by repeating readout pixels and non-readout pixels every two lines. The vertical resolution is approximately 200TV-lines. Note that the same pixel signal is output for both odd and even fields. Since signals are output in a format which conforms to NTSC, the external circuit can be simplified when monitoring using an NTSC monitor. 9

ICX098AK

Measurement conditions 1) In the following measurements, the device drive conditions are at the typical values of the bias and clock voltage conditions. 2) In the following measurements, spot blemishes are excluded and, unless otherwise specified, the optical black level (OB) is used as the reference for the signal output, which is taken as the value of the Gr/Gb signal output or the R/B signal output of the measurement system. Definition of standard imaging conditions 1) Standard imaging condition I: Use a pattern box (luminance 706cd/m2, color temperature of 3200K halogen source) as a subject. (Pattern for evaluation is not applicable.) Use a testing standard lens with CM500S (t = 1.0mm) as an IR cut filter and image at F5.6. The luminous intensity to the sensor receiving surface at this point is defined as the standard sensitivity testing luminous intensity. 2) Standard imaging condition : Image a light source (color temperature of 3200K) with a uniformity of brightness within 2% at all angles. Use a testing standard lens with CM500S (t = 1.0mm) as an IR cut filter. The luminous intensity is adjusted to the value indicated in each testing item by the lens diaphragm. 1. G sensitivity, sensitivity comparison Set to standard imaging condition I. After selecting the electronic shutter mode with a shutter speed of 1/100s, measure the signal outputs (VGr, VGb, VR and VB) at the center of each Gr, Gb, R and B channel screens, and substitute the values into the following formula. VG = (VGr + VGb)/2 Sg = VG 100 [mV] 30 Rr = VR/VG Rb = VB/VG 2. Saturation signal Set to standard imaging condition II. After adjusting the luminous intensity to 20 times the intensity with the average value of the Gr signal output, 150mV, measure the minimum values of the Gr, Gb, R and B signal outputs. 3. Smear Set to standard imaging condition II. With the lens diaphragm at F5.6 to F8, first adjust the average value of the Gr signal output to 150mV. Measure the average values of the Gr signal output, Gb signal output, R signal output and B signal output (Gra, Gba, Ra, Ba), and then adjust the luminous intensity to 500 times the intensity with average value of the Gr signal output, 150mV. After the readout clock is stopped and the charge drain is executed by the electronic shutter at the respective H blankings, measure the maximum value (Vsm [mV]), independent of the Gr, Gb, R and B signal outputs, and substitute the values into the following formula. Sm = Vsm Gra + Gba + Ra + Ba 1 1 100 [%] (1/10V method conversion value) 4 10 500

4. Video signal shading Set to standard imaging condition II. With the lens diaphragm at F5.6 to F8, adjust the luminous intensity so that the average value of the Gr signal output is 150mV. Then measure the maximum (Grmax [mV]) and minimum (Grmin [mV]) values of the Gr signal output and substitute the values into the following formula. SHg = (Grmax Grmin)/150 100 [%] 10

ICX098AK

5. Uniformity between video signal channels After measuring 4, measure the maximum (Rmax [mV]) and minimum (Rmin [mV]) values of the R signal and the maximum (Bmax [mV]) and minimum (Bmin [mV]) values of the B signal, and substitute the values into the following formula. Srg = (Rmax Rmin)/150 100 [%] Sbg = (Bmax Bmin)/150 100 [%] 6. Dark signal Measure the average value of the signal output (Vdt [mV]) with the device ambient temperature 60C and the device in the light-obstructed state, using the horizontal idle transfer level as a reference. 7. Dark signal shading After measuring 6, measure the maximum (Vdmax [mV]) and minimum (Vdmin [mV]) values of the dark signal output and substitute the values into the following formula. Vdt = Vdmax Vdmin [mV] 8. Line crawl Set to standard imaging condition II. Adjusting the luminous intensity so that the average value of the Gr signal output is 150mV, and then insert R, G, and B filters and measure the difference between G signal lines (Glr, Glg, Glb [mV]) as well as the average value of the G signal output (Gar, Gag, Gab). Substitute the values into the following formula. Lci = Gli 100 [%] (i = r, g, b) Gai 9. Lag Adjust the Gr signal output value generated by strobe light to 150mV. After setting the strobe light so that it strobes with the following timing, measure the residual signal (Vlag). Substitute the value into the following formula. Lag = (Vlag/150) 100 [%]

VD

V2A Light Strobe light timing Gr signal output 150mV Output Vlag (Lag)

11

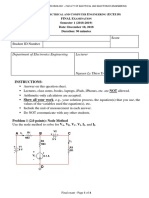

Drive Circuit

15V 20 19 18 100 5.5V 3.3/16V

1 2 3

XSUB

XV1 XV2A XSG1 22/16V 1 2 3 4 5 6 7 12

4 5 6 7 8 2SK523

CXD1267AN

17 16 15 14 13

V1

V3

V2A V2B

GND VOUT

XV2B XSG2 XV3

VL

10

11

CCD OUT 3.9K

22/20V ICX098 (Bottom View)

RG

H2 H1

CSUB

14 13 12 11 10 9 100K 0.1 1/35V

SUB GND

VDD

12

0.1 1/20V

33/20V

0.01

2200p

1M

H2 H1

RG ICX098AK

ICX098AK

Sensor Readout Clock Timing Chart

Progressive Scan Mode

XV1

XV2A

XV2B

XV3

XSG1

XSG2

Sensor readout clocks XSG1 and XSG2 are used by composing XV2A and XV2B.

81.4ns (1 bit) HD 2.53s (31 bits) 42.2s (520 bits)

V1

V2A

V2B

V3

13

ICX098AK

Sensor Readout Clock Timing Chart

Monitoring Mode

XV1

XV2A

XV2B

XV3

XSG1

XSG2

Sensor readout clock XSG1 is used by composing XV2A.

81.4ns (1 bit) HD 2.53s (31 bits) 42.2s (520 bits) V1

V2A

V2B

V3

14

Drive Timing Chart (Vertical Sync)

Progressive Scan Mode

VD

HD

504 510 520 525 1 2 3 4 5 6 7

1 2 3 4 5 6 7 8 1 2

V1

CCD OUT

494

15

V2A

V2B

V3

525 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

1 2 3 4 5 6 7 8 1 2 3 4 5 6 7 8 9 1011

ICX098AK

Drive Timing Chart (Vertical Sync)

Monitoring Mode

FLD

VD

BLK

HD

275 260 261 262 263 264 265 270 280 285

1 2 5 6 1 2 5 6 9 10 13 1417 18

520

V1

V2A

V2B

V3

525 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

1 2 5 6 1 2 5 6 9 1013 1417 18

CCD OUT

486 489 490 493 494

486 489 490 493 494

16

ICX098AK

Drive Timing Chart (Horizontal Sync)

Progressive Scan Mode

HD

78

780

BLK

140

CLK

H1

H2

V1

V2A

17

V2B

V3

SUB

RG

SHP

SHD

ICX098AK

Drive Timing Chart (Horizontal Sync)

Monitoring Mode

HD 78

780

BLK

140

CLK

H1

H2

V1

18

V2A

V2B

V3

SUB

RG

SHP

SHD

ICX098AK

ICX098AK

Notes on Handling 1) Static charge prevention CCD image sensors are easily damaged by static discharge. Before handling be sure to take the following protective measures. a) Either handle bare handed or use non-chargeable gloves, clothes or material. Also use conductive shoes. b) When handling directly use an earth band. c) Install a conductive mat on the floor or working table to prevent the generation of static electricity. d) Ionized air is recommended for discharge when handling CCD image sensor. e) For the shipment of mounted substrates, use boxes treated for the prevention of static charges. 2) Soldering a) Make sure the package temperature does not exceed 80C. b) Solder dipping in a mounting furnace causes damage to the glass and other defects. Use a ground 30W soldering iron and solder each pin in less than 2 seconds. For repairs and remount, cool sufficiently. c) To dismount an image sensor, do not use a solder suction equipment. When using an electric desoldering tool, use a thermal controller of the zero cross On/Off type and connect it to ground. 3) Dust and dirt protection Image sensors are packed and delivered by taking care of protecting its glass plates from harmful dust and dirt. Clean glass plates with the following operation as required, and use them. a) Perform all assembly operations in a clean room (class 1000 or less). b) Do not either touch glass plates by hand or have any object come in contact with glass surfaces. Should dirt stick to a glass surface, blow it off with an air blower. (For dirt stuck through static electricity ionized air is recommended.) c) Clean with a cotton bud and ethyl alcohol if the grease stained. Be careful not to scratch the glass. d) Keep in a case to protect from dust and dirt. To prevent dew condensation, preheat or precool when moving to a room with great temperature differences. e) When a protective tape is applied before shipping, just before use remove the tape applied for electrostatic protection. Do not reuse the tape. 4) Installing (attaching) a) Remain within the following limits when applying a static load to the package. Do not apply any load more than 0.7mm inside the outer perimeter of the glass portion, and do not apply any load or impact to limited portions. (This may cause cracks in the package.)

Cover glass

50N Plastic package Compressive strength

50N

1.2Nm Torsional strength

b) If a load is applied to the entire surface by a hard component, bending stress may be generated and the package may fracture, etc., depending on the flatness of the bottom of the package. Therefore, for installation, use either an elastic load, such as a spring plate, or an adhesive. 19

ICX098AK

c) The adhesive may cause the marking on the rear surface to disappear, especially in case the regulated voltage value is indicated on the rear surface. Therefore, the adhesive should not be applied to this area, and indicated values should be transferred to the other locations as a precaution. d) The notch of the package is used for directional index, and that can not be used for reference of fixing. In addition, the cover glass and seal resin may overlap with the notch of the package. e) If the lead bend repeatedly and the metal, etc., clash or rub against the package, the dust may be generated by the fragments of resin. f) Acrylate anaerobic adhesives are generally used to attach CCD image sensors. In addition, cyanoacrylate instantaneous adhesives are sometimes used jointly with acrylate anaerobic adhesives. (reference) 5) Others a) Do not expose to strong light (sun rays) for long periods, color filters will be discolored. When high luminance objects are imaged with the exposure level control by electronic-iris, the luminance of the image-plane may become excessive and discolor of the color filter will possibly be accelerated. In such a case, it is advisable that taking-lens with the automatic-iris and closing of the shutter during the power-off mode should be properly arranged. For continuous using under cruel condition exceeding the normal using condition, consult our company. b) Exposure to high temperature or humidity will affect the characteristics. Accordingly avoid storage or usage in such conditions. c) The brown stain may be seen on the bottom or side of the package. But this does not affect the CCD characteristics. d) This package has 2 kinds of internal structure. However, their package outline, optical size, and strength are the same.

Structure A Package Chip Metal plate (lead frame) Structure B

Cross section of lead frame

The cross section of lead frame can be seen on the side of the package for structure A.

20

Package Outline

Unit: mm

14 pin DIP (400mil)

A

0 to 9

5.0 8 D C 8 14

14

10.16

7.0

2.5

5.0

V 7 7 1

0.5

B' 1. A is the center of the effective image area.

2.6

1.27 3.5 0.3

21

1.0

2.5

3.35 0.15

7.0

2. The two points B of the package are the horizontal reference. The point B' of the package is the vertical reference. 3. The bottom C of the package, and the top of the cover glass D are the height reference. 4. The center of the effective image area relative to B and B' is (H, V) = (5.0, 5.0) 0.15mm. 5. The rotation angle of the effective image area relative to H and V is 1.

1.27

0.3 0.46

6. The height from the bottom C to the effective image area is 1.41 0.10mm. The height from the top of the cover glass D to the effective image area is 1.94 0.15mm. 7. The tilt of the effective image area relative to the bottom C is less than 25m. The tilt of the effective image area relative to the top D of the cover glass is less than 25m. 8. The thickness of the cover glass is 0.75mm, and the refractive index is 1.5. 9. The notch of the package is used only for directional index, that must not be used for reference of fixing.

0.3

PACKAGE STRUCTURE

PACKAGE MATERIAL

Plastic

LEAD TREATMENT

GOLD PLATING

LEAD MATERIAL

42 ALLOY

ICX098AK

PACKAGE WEIGHT

0.6g

0.25

1.0

8.9 10.0 0.1

8.9 10.0 0.1

1.7

B 1.7

2.5

This datasheet has been downloaded from: www.DatasheetCatalog.com Datasheets for electronic components.

You might also like

- Philips ToUcam Pro II Sony ICX098BQDocument21 pagesPhilips ToUcam Pro II Sony ICX098BQEduardo AlamillaNo ratings yet

- 1/4 Inch CCD Image Sensor For Ccir Camera S5F429PX02: 14pin Cer - DIPDocument18 pages1/4 Inch CCD Image Sensor For Ccir Camera S5F429PX02: 14pin Cer - DIPdragon-red0816No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- TDA8366Document48 pagesTDA8366Rigoberto Martinez LopezNo ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Tvro Ird 190107 1Document88 pagesTvro Ird 190107 1helloskmNo ratings yet

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- 20065819114669071Document58 pages20065819114669071Andrei BistriceanuNo ratings yet

- Akira Ss1 Con Lc863320a y La 76810Document12 pagesAkira Ss1 Con Lc863320a y La 76810pepino464No ratings yet

- Tda 4858Document44 pagesTda 4858utilscNo ratings yet

- Data Sheet: Economy Autosync Deflection Controller (EASDC)Document44 pagesData Sheet: Economy Autosync Deflection Controller (EASDC)Jorge BenitezNo ratings yet

- Specifications: 1. Picture Tube 4. Power SupplyDocument49 pagesSpecifications: 1. Picture Tube 4. Power Supplyfvb_spamNo ratings yet

- FOR Approval Specification: 47.0" Wuxga TFT LCD TitleDocument44 pagesFOR Approval Specification: 47.0" Wuxga TFT LCD TitlesujithamohanNo ratings yet

- TDA120xxH Hercules 128pinDocument20 pagesTDA120xxH Hercules 128pinTudor FlorianNo ratings yet

- H25X Optical Absolute EncoderDocument2 pagesH25X Optical Absolute EncoderDanielAliNo ratings yet

- Tentative: TFD58W30MM/TFD58W22MWDocument14 pagesTentative: TFD58W30MM/TFD58W22MWbala0311No ratings yet

- CXD3400N: 6-Channel CCD Vertical Clock DriverDocument9 pagesCXD3400N: 6-Channel CCD Vertical Clock DriverJaffer SultanNo ratings yet

- Tv2Kr - TXT: Service ManualDocument13 pagesTv2Kr - TXT: Service ManualCarp CornelNo ratings yet

- Datasheet Micro M65582AMF-105FPDocument46 pagesDatasheet Micro M65582AMF-105FPsel_mor100% (1)

- PLL, Digital - 74HC297Document13 pagesPLL, Digital - 74HC297Deepa DevarajNo ratings yet

- OM8373 78 N3 v1.0 PDFDocument108 pagesOM8373 78 N3 v1.0 PDFJulio Alberto Cabrera Rodriguez100% (1)

- PM 150 CSD 120Document7 pagesPM 150 CSD 120elecompinnNo ratings yet

- QPSK Demodulation and Audio Signal-Processing IC For Satellite Broadcast ReceptionDocument9 pagesQPSK Demodulation and Audio Signal-Processing IC For Satellite Broadcast ReceptionselocaNo ratings yet

- LK315T3LA57Document24 pagesLK315T3LA57Repararelcd Lcd0% (1)

- Akira ct-21jp9 Chassis-Ss1 SMDocument11 pagesAkira ct-21jp9 Chassis-Ss1 SMAnton PopaNo ratings yet

- Data Sheet: TDA4857PSDocument56 pagesData Sheet: TDA4857PSAnggye Adalah AnggyeNo ratings yet

- Tea LCD TV Lcd2603au Service ManualDocument43 pagesTea LCD TV Lcd2603au Service ManualIsrael B ChavezNo ratings yet

- DatasheetDocument24 pagesDatasheetRafael PavanNo ratings yet

- DENON AVR 1802 882 Service Manual PDFDocument94 pagesDENON AVR 1802 882 Service Manual PDFatvstereo50% (4)

- FOR Approval Specification: 47.0" Wuxga TFT LCD TitleDocument28 pagesFOR Approval Specification: 47.0" Wuxga TFT LCD TitleIonescu CristinaNo ratings yet

- Daewoo Osdtd29n001Document21 pagesDaewoo Osdtd29n001miltoncgNo ratings yet

- CMZ900S PDFDocument11 pagesCMZ900S PDFPhuoc Ho NguyenNo ratings yet

- 1 BEE54 AEd 01Document57 pages1 BEE54 AEd 01hernando2000No ratings yet

- Cxa1645 TV EncoderDocument14 pagesCxa1645 TV EncoderkorrekaminosNo ratings yet

- TRIPLE 10-BIT, 90-MSPS, Video and Graphics Digitizer With Horizontal PLLDocument59 pagesTRIPLE 10-BIT, 90-MSPS, Video and Graphics Digitizer With Horizontal PLL2527919No ratings yet

- 83C055Document40 pages83C055vdăduicăNo ratings yet

- Data Sheet: Device SpecificationDocument101 pagesData Sheet: Device SpecificationvmalvicaNo ratings yet

- Tda 9859Document24 pagesTda 9859Edgardo D ManciniNo ratings yet

- Aoc LC42H063D, LC42H063DDocument133 pagesAoc LC42H063D, LC42H063DsachinNo ratings yet

- TA1270BF: Pal / NTSC Video Chroma and Sync Processing System For Pip / Pop / PapDocument39 pagesTA1270BF: Pal / NTSC Video Chroma and Sync Processing System For Pip / Pop / PapAzmi PlgNo ratings yet

- JVC LCD Lt-19d200Document74 pagesJVC LCD Lt-19d200ngoclinhdtddNo ratings yet

- MSM6544Document13 pagesMSM6544Shuvamay GuhaNo ratings yet

- 42pf9966 Chassis Ftp2.2u Aa SMDocument139 pages42pf9966 Chassis Ftp2.2u Aa SMZoltán Ureczki100% (1)

- Service Manual: HD-52G787, HD-52G887, HD-56G787, HD-56G887, HD-61G787, HD-61G887Document205 pagesService Manual: HD-52G787, HD-52G887, HD-56G787, HD-56G887, HD-61G787, HD-61G887Rick Costa100% (1)

- Datasheet TS2012 Audio AmplifierDocument30 pagesDatasheet TS2012 Audio AmplifierNicholas AlvesNo ratings yet

- Tda4856 2Document57 pagesTda4856 2Nikola PolimenovNo ratings yet

- Controlador de HDMI TV LCD Sharp BU16028KVDocument18 pagesControlador de HDMI TV LCD Sharp BU16028KVachavez712001No ratings yet

- Encoder H9720Document10 pagesEncoder H9720Marco Antonio Henriquez100% (1)

- ATS692 H DatasheetDocument12 pagesATS692 H Datasheetshivani_mehrotra_8No ratings yet

- LG w1943sb Lgd-tlc1 SMDocument42 pagesLG w1943sb Lgd-tlc1 SMmirkovsNo ratings yet

- TX 29 P 180Document57 pagesTX 29 P 180Kee GerkengNo ratings yet

- Tda 10021 DatasheetDocument17 pagesTda 10021 DatasheetWilly DacoNo ratings yet

- TCM8230MDDocument27 pagesTCM8230MDJames BalsillieNo ratings yet

- RGB To NTSC/PAL Encoder AD722Document12 pagesRGB To NTSC/PAL Encoder AD722Firman TheLiverpudlianNo ratings yet

- AKAI - 21CT06FS - Chassis - PX20019 PDFDocument19 pagesAKAI - 21CT06FS - Chassis - PX20019 PDFsertecelecNo ratings yet

- Data Sheet: 74HC/HCT74Document13 pagesData Sheet: 74HC/HCT74Anubhav YadavNo ratings yet

- 10 KW TV TransmitterDocument58 pages10 KW TV TransmitterKirti Khandelwal80% (5)

- Display LQ038Q5DR01 SpecDocument26 pagesDisplay LQ038Q5DR01 SpecSó fogões de InduçãoNo ratings yet

- Isp C v5Document2 pagesIsp C v5Francis TaisantNo ratings yet

- TF 117 Circuit DiagramDocument9 pagesTF 117 Circuit DiagramFrancis TaisantNo ratings yet

- Sony MDX-C6500X Service ManualDocument12 pagesSony MDX-C6500X Service ManualFrancis TaisantNo ratings yet

- Service Manual: DSC-W5/W7/W15/W17Document35 pagesService Manual: DSC-W5/W7/W15/W17Francis TaisantNo ratings yet

- BS 6724 1997Document42 pagesBS 6724 1997Simon Law100% (1)

- Handover Analysis of 3G NetworkDocument43 pagesHandover Analysis of 3G NetworkMohammed NazimNo ratings yet

- SEAD - Solution Manual - 2019-2020 EditionDocument37 pagesSEAD - Solution Manual - 2019-2020 EditionYokaNo ratings yet

- Dolphin (PG) College of Science & Agriculture: Fee Per SemesterDocument1 pageDolphin (PG) College of Science & Agriculture: Fee Per Semesterlincon sNo ratings yet

- Primary Structure For A Cubesat 1U For QKD Applications: Design and AnalysisDocument7 pagesPrimary Structure For A Cubesat 1U For QKD Applications: Design and AnalysisShoaib IqbalNo ratings yet

- Ext 80165Document5 pagesExt 80165Daryl Juliette Taborda GodoyNo ratings yet

- DIN 15018-1 Cranes. Steel Structures Verification and Analysis PDFDocument37 pagesDIN 15018-1 Cranes. Steel Structures Verification and Analysis PDF8310195025080100% (1)

- Quarter 1 Summative Test in Earth and LifeDocument5 pagesQuarter 1 Summative Test in Earth and LifeHanna100% (1)

- PR2 Questionnaire FinalDocument4 pagesPR2 Questionnaire FinalGevin DuetchNo ratings yet

- 1660SM AlarmsDocument6 pages1660SM Alarmsdennis_lim_33100% (1)

- 2 Case StudyDocument8 pages2 Case Studysehrish khawerNo ratings yet

- Infocad Ifc ManualDocument8 pagesInfocad Ifc ManualMarian DragosNo ratings yet

- Surface Vehicle Recommended Practice: (R) Biaxial Wheel Fatigue TestDocument23 pagesSurface Vehicle Recommended Practice: (R) Biaxial Wheel Fatigue TestAdriana SukmanaputraNo ratings yet

- 11 Solutions KTPDocument22 pages11 Solutions KTPAdiya AshimovaNo ratings yet

- Concepts and Principles of Immersion Lesson 6Document2 pagesConcepts and Principles of Immersion Lesson 6Gringgo PanesNo ratings yet

- G11 Campos Research Proposal Group 1Document48 pagesG11 Campos Research Proposal Group 1remar rubindiazNo ratings yet

- 181 ECE110 Final ExamDocument4 pages181 ECE110 Final ExamPham Lê HuyNo ratings yet

- Abhijit MuhuratDocument7 pagesAbhijit MuhuratAbi Abilash100% (1)

- MODULE 5. Research MethodologyDocument11 pagesMODULE 5. Research MethodologyRuel ReyesNo ratings yet

- A Very Good Read On The Construction of Natural NumbersDocument5 pagesA Very Good Read On The Construction of Natural NumbersBadd ManNo ratings yet

- Geko Ansys CFD PDFDocument38 pagesGeko Ansys CFD PDFJulio Andrés Casal RamosNo ratings yet

- BS-200 Reagent ParameterDocument3 pagesBS-200 Reagent ParameterBetina NdjiemiNo ratings yet

- HW 03 - STATICS W/lab ENGG270: School of Engineering American University in DubaiDocument3 pagesHW 03 - STATICS W/lab ENGG270: School of Engineering American University in DubaiSana'a AamirNo ratings yet

- Folleto GA1-240202501-AA2-EV01Document2 pagesFolleto GA1-240202501-AA2-EV01Katherine Zapata33% (3)

- SH300B4ABEDocument6 pagesSH300B4ABE0kphNo ratings yet

- UntitledDocument2 pagesUntitledaliNo ratings yet

- ENSC 20043 Statics Lec4 Ch4 Force System ResultantsDocument63 pagesENSC 20043 Statics Lec4 Ch4 Force System ResultantsAndrei AlidoNo ratings yet

- Eis Piggery SampleDocument55 pagesEis Piggery SampleLinnel Faye C. MalibiranNo ratings yet

- Rigid Pipeline DesignDocument123 pagesRigid Pipeline DesignAditya Prasad100% (1)

- Pet Handbook Reading WritingDocument12 pagesPet Handbook Reading WritingPhương Nguyễn NguyênNo ratings yet