Professional Documents

Culture Documents

Single Event Upsets in Digital VLSI Circuits: EYES Summer Internship Program 2007 University of New Mexico

Uploaded by

GnanendraReddyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Single Event Upsets in Digital VLSI Circuits: EYES Summer Internship Program 2007 University of New Mexico

Uploaded by

GnanendraReddyCopyright:

Available Formats

Single Event Upsets in Digital VLSI

Circuits

EYES Summer Internship Program 2007

University of New Mexico

Vinay Jain Dr. Payman Zarkesh-Ha

Final Year Undergraduate Assistant Professor ECE

Indian Institute of Technology Kanpur University of New Mexico

Acknowledgements

Outline

Introduction

Soft-Spot Analysis

Inverter Model proposed

Simulation Results

Extension of the Model

Introduction

Origin

Soft errors, Single Event Transients (SET)

and Single Event Upsets (SEU)

Techniques to reduce SET propagation

Softness of a node

Particle Strike in CMOS Digital VLSI circuits. SET and SEU

Origin of Soft errors: cosmic

neutrons and - particles

Soft-Spot Analysis

Timing Masking Factor, T

N

Tendency of a node to allow noise in particular

time window

Computed using time delays and sensitive

window durations of various gates in the path

Logic Masking Factor, L

N

Likelihood for noise at a node to logically reach

the storage element

Computed using probability of nodes in the path

to acquire certain states

Electrical Masking Factor, E

N

Ability of a node to allow noise propagation

with enough strength

Computed from the characteristics of Noise

Rejection Curves

Overall Softness, S

N

S

N

= T

N

*L

N

*E

N

Noise Rejection Curves

Noise Rejection Curves for an inverter and

its effects as Load and Size of the inverter is varied

Inverter Model Proposed

Model proposed is- replacement of MOS transistors with constant current

sources the DC value of which is the average drain currents of the transistors

A. Velocity Saturation Effects in short channel MOSFETs

= .E / (1 + E / E

C

) , E < E

C

=

SAT

, E > E

C

where E

C

= 2

SAT

/

V

DSATn

= V

GTn

/ (1 + V

GTn

/ E

Cn.

L

n

)

for short channel (small L

n

)

saturates to V

DSATn

= E

Cn.

L

n

as V

GTn

is increased

= V

GTn

, long channel (large L

n

)

I

DSATn

=

SATn

.C

ox

.W

n

.( V

GTn

-V

DSATn

)

=

SATn

.C

ox

.W

n

.(V

GTn

)

2

/ (V

GTn

+ E

Cn.

L

n

)

~

SATn

. C

ox

.W

n

.(V

GTn

) for small channel MOSFETs (small L

n

)

~

SATn

. C

ox

.W

n

.(V

GTn

)

2

/ E

Cn.

L

n

for long channel MOSFETs (large L

n

)

B. Voltage Transfer Characteristic

Voltage Transfer Characteristic for an Inverter

(INVx1)

Noise can propagate only when input pulse has

magnitude greater than V

m

C. Average Current Model

I

D

V

DS

characteristic for an

inverter (INVx1) for gate

Voltage greater than V

m

I

N

=(I

Dn

)

avg

= I

DSATn

(1 +

n

(V

DD

+ V

m

)/ 2)

I

N

= C

n

*. I

DSATn

where C

n

* = 1 +

n

(V

DD

+ V

m

)/ 2

I

P

= (I

Dp

)

avg

= [ (I

P1

/2).<V

DSATp

> + {(I

P1

+I

P2

)/2}.(V

DD

V

m

<V

DSATp

>) ] /

(V

DD

V

m

)

= I

DSATp

.(1 +

p

(V

DD

- V

m

)/ 2 <V

DSATp

>/(2.(V

DD

- V

m

)) )

Thus,

I

P

= C

p

*. I

DSATp

where C

p

* = 1 +

p

(V

DD

- V

m

)/ 2 <V

DSATp

>/(2.(V

DD

- V

m

))

<V

DSATp

> = V

DSATp

at V

G

= (V

DD

+ V

m

)/ 2

I

P1

= I

DSATp

. (1+

p

.<V

DSATp

>)

I

P2

= I

DSATp

. (1+

p

.(V

DD

- V

m

))

Thus, we have I

N

= C

n

*I

DSATn

& I

P

= C

p

*I

DSATp

where both C

n

* & C

p

* are constants and close to unity.

We can now calculate T

C

as the minimum duration

required for a noise pulse of height V

C

volts, to

propagate through the inverter as

T

C

= C

L

.(V

DD

- V

m

)/(I

N

- I

P

)

with V

G

= V

C

The above equation gives a relation between T

C

and V

C

as a function of only Gate size (W and L) of p-MOS

and n-MOS.

Simulation Results

Noise Rejection Curves comparison for INVx2

(Load = 200fF)

Time taken for simulation by matlab = 0.077 sec

Time taken for simulation by Tspice = 4.45 sec

Mean %error = 4.68%

Noise Rejection Curves comparison for INVx1

(Load = 200fF)

Time taken for simulation by matlab = 0.074 sec

Time taken for simulation by Tspice = 4.48 sec

Mean %error = 11.59%

Noise Rejection Curves comparison for INVx8

(Load = 200fF)

Time taken for simulation by matlab = 0.069 sec

Time taken for simulation by Tspice = 4.42 sec

Mean %error = 17.65%

Noise Rejection Curves comparison for INVx4

(Load = 200fF)

Time taken for simulation by matlab = 0.074 sec

Time taken for simulation by Tspice = 4.61 sec

Mean %error = 6.70%

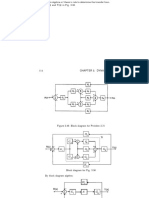

Extension of the model

Modeling of NAND gates for easy computation of Noise Rejection Curves

Modeling of NOR gates for easy computation of Noise Rejection Curves

Noise Rejection Curves comparison for

NANDx1 (Load = 200fF)

Time taken for simulation by matlab = 0.078 sec

Time taken for simulation by Tspice = 5.05 sec

Mean %error = 30.16%

Noise Rejection Curves comparison for

NORx1 (Load = 200fF)

Time taken for simulation by matlab = 0.076 sec

Time taken for simulation by Tspice = 5.09 sec

Mean %error = 9.23%

References

[1] C. Zhao, X. Bai, S. Dey, A scalable soft spot analysis methodology for

compound noise effects in nano-meter circuits, DAC04, pp. 894-899, June

2004.

[2] C. Zhao, S. Dey, Improving transient error tolerance of digital VLSI circuits

using RObustness COmpiler (ROCO), International Symposium on Quality

Electronic Design, ISQED06

[3] C.G. Sodini, P. Ko, J. Moll, The effect of high fields on MOS device and circuit

performance, IEEE transactions on Electron Devices, October 1984, pp.1386-

1393

[4] J. M. Rabaey, A. Chandrakasan, B. Nikolic, Digital Integrated Circuits,

Second edition, 2003

Thank You

You might also like

- Telecommunication Switching Lab FileDocument62 pagesTelecommunication Switching Lab FileRadhika RaghavNo ratings yet

- Digital Communication Lab ManualDocument52 pagesDigital Communication Lab ManualPRIYA RAJI100% (3)

- CHP 2Document38 pagesCHP 2NK NKNo ratings yet

- Adaptive Beam-Forming For Satellite Communication: by Prof. Binay K. Sarkar ISRO Chair ProfessorDocument50 pagesAdaptive Beam-Forming For Satellite Communication: by Prof. Binay K. Sarkar ISRO Chair ProfessorNisha Kumari100% (1)

- Experment Butterworth FilterDocument6 pagesExperment Butterworth FilterSayantan RoyNo ratings yet

- Chenming Hu Ch2 SlidesDocument40 pagesChenming Hu Ch2 SlidesfaisalphyNo ratings yet

- Carrier Transport Phenomena: Department of Microelectronics and Computer EngineeringDocument53 pagesCarrier Transport Phenomena: Department of Microelectronics and Computer Engineeringcol12No ratings yet

- Tutorial 5Document10 pagesTutorial 5bayman66No ratings yet

- CSP Lab Manual 25.2.16Document47 pagesCSP Lab Manual 25.2.16prashanthNo ratings yet

- Ijesat 2012 02 01 02Document4 pagesIjesat 2012 02 01 02Ijesat JournalNo ratings yet

- MOS Cap SimulationDocument19 pagesMOS Cap SimulationRuchirNo ratings yet

- VLSI-Design-NonidealDocument30 pagesVLSI-Design-NonidealBhagirath BhattNo ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- General Instructions To The CandidateDocument4 pagesGeneral Instructions To The Candidateapurv shuklaNo ratings yet

- RTS Noise Impact in CMOS Image Sensors Readout CircuitDocument5 pagesRTS Noise Impact in CMOS Image Sensors Readout CircuiturpublicNo ratings yet

- TC-212 DSPDocument43 pagesTC-212 DSPbakNo ratings yet

- TKBDocument134 pagesTKBVictor TolentinoNo ratings yet

- Num DistDocument5 pagesNum DistYermakov Vadim IvanovichNo ratings yet

- Bwire Ans AssgDocument5 pagesBwire Ans AssgEria NalwasaNo ratings yet

- Lecture - MOS & MOSFET-1Document21 pagesLecture - MOS & MOSFET-1Kartika MunirNo ratings yet

- Exp4 Lab ReportDocument8 pagesExp4 Lab ReportChetan GuptaNo ratings yet

- Pid00050 2 CmosDocument8 pagesPid00050 2 CmosSaurabh ChakravartyNo ratings yet

- MOS Rabaey PDFDocument32 pagesMOS Rabaey PDFalamgirNo ratings yet

- 3D-Electromagnetic Field Simulations With The Finite Integration Technique (FIT)Document23 pages3D-Electromagnetic Field Simulations With The Finite Integration Technique (FIT)Vinicius UchoaNo ratings yet

- Lecture 4: Small-Signal Diode Model and Its ApplicationDocument9 pagesLecture 4: Small-Signal Diode Model and Its Application9013227246No ratings yet

- EE 612 Home Assignment No. 3 Nov. 08, 2009 Solutions To Copy Point On Nov. 11, 2009. Quiz 3 On Nov. 12, 2009Document1 pageEE 612 Home Assignment No. 3 Nov. 08, 2009 Solutions To Copy Point On Nov. 11, 2009. Quiz 3 On Nov. 12, 2009VishalPandeyNo ratings yet

- Digital Communication Systems DesignDocument37 pagesDigital Communication Systems DesignShelNo ratings yet

- The Cmos Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004Document40 pagesThe Cmos Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004SrasVelNo ratings yet

- 0324AT Hyu PCGDocument55 pages0324AT Hyu PCGLiz BenhamouNo ratings yet

- SSED - Solved Problems For Chapter 5Document7 pagesSSED - Solved Problems For Chapter 5MINH NGUYỄN THẾNo ratings yet

- Vlsi Design - Ec - 701 - Unit - 2Document18 pagesVlsi Design - Ec - 701 - Unit - 2angelcrystl4774No ratings yet

- DSP ManualDocument44 pagesDSP ManualSuchitharaNo ratings yet

- MC Modulation and OFDM PrinciplesDocument13 pagesMC Modulation and OFDM PrinciplesOptimistic Patient Must BeNo ratings yet

- Study of The Variation of Power Loss With Frequency Along A RectangularDocument6 pagesStudy of The Variation of Power Loss With Frequency Along A RectangularIAEME PublicationNo ratings yet

- LV Dallas IEEE TutorialDocument78 pagesLV Dallas IEEE Tutorialrakesh_pal_3No ratings yet

- Mass Loading EffectDocument4 pagesMass Loading EffectGrudge stanleyNo ratings yet

- MOSFET Amplifier Analysis and Design in Different ConfigurationsDocument10 pagesMOSFET Amplifier Analysis and Design in Different Configurationsmani_vlsiNo ratings yet

- Uwb PDFDocument5 pagesUwb PDFHinduja IcchapuramNo ratings yet

- On Using Transmission Overhead Efficiently For Channel Estimation in OFDMDocument6 pagesOn Using Transmission Overhead Efficiently For Channel Estimation in OFDMAnonymous uspYoqENo ratings yet

- RF Linac Structures: Nicolas PichoffDocument15 pagesRF Linac Structures: Nicolas PichoffSurve Ayesha YusufNo ratings yet

- Homework 2Document3 pagesHomework 2Rozita RahmanNo ratings yet

- Experimental Investigations On Multi-End Fault Location System Based On Current Traveling WavesDocument6 pagesExperimental Investigations On Multi-End Fault Location System Based On Current Traveling WavesAbdelsalam ElhaffarNo ratings yet

- IR-drop Reduction Through Combinational Circuit PartitioningDocument12 pagesIR-drop Reduction Through Combinational Circuit PartitioningPramod Reddy RNo ratings yet

- Ultrasonic Preamplifier Performance EvaluationDocument6 pagesUltrasonic Preamplifier Performance Evaluationmachinator2No ratings yet

- Assignment For LecturesDocument16 pagesAssignment For LecturesDeepak JainNo ratings yet

- Gate Tunneling Current and Quantum Effects in Deep Scaled MosfetsDocument5 pagesGate Tunneling Current and Quantum Effects in Deep Scaled Mosfetsashishj1083No ratings yet

- DSP ManualDocument43 pagesDSP ManualMaryam MuneebNo ratings yet

- A Double-Tail Latch-Type Voltage Sense Amplifier With 18ps Setup+Hold TimeDocument3 pagesA Double-Tail Latch-Type Voltage Sense Amplifier With 18ps Setup+Hold TimeburakgonenNo ratings yet

- Coding Techniques For Analog Sources: Prof - Pratik TawdeDocument11 pagesCoding Techniques For Analog Sources: Prof - Pratik TawdeabayteshomeNo ratings yet

- Variations Gobal LoacalDocument11 pagesVariations Gobal LoacalPullareddy AvulaNo ratings yet

- A Double-Tail Latch-Type Voltage Sense Amplifier With 18ps Setup+Hold TimeDocument3 pagesA Double-Tail Latch-Type Voltage Sense Amplifier With 18ps Setup+Hold TimeWang TianyangNo ratings yet

- Performance Comparison of Wavelet Packet Modulation and OFDM Over Multipath Wireless Channel With Narrowband InterferenceDocument4 pagesPerformance Comparison of Wavelet Packet Modulation and OFDM Over Multipath Wireless Channel With Narrowband Interferencesachin10dulkarNo ratings yet

- Transactions Briefs: Analog Computation of Wavelet Transform Coefficients in Real-TimeDocument4 pagesTransactions Briefs: Analog Computation of Wavelet Transform Coefficients in Real-TimeHair MorenoNo ratings yet

- RF and Microwave Systems IntroductionDocument38 pagesRF and Microwave Systems IntroductionAbdul Hafiz AnuarNo ratings yet

- Jpconf6 48 088Document6 pagesJpconf6 48 088tgazmanmohdNo ratings yet

- L.C Oscillator Tutorial: 1 AbstractDocument18 pagesL.C Oscillator Tutorial: 1 AbstractChi PhamNo ratings yet

- Interactions between Electromagnetic Fields and Matter: Vieweg Tracts in Pure and Applied PhysicsFrom EverandInteractions between Electromagnetic Fields and Matter: Vieweg Tracts in Pure and Applied PhysicsNo ratings yet

- Amateur Radio Electronics on Your MobileFrom EverandAmateur Radio Electronics on Your MobileRating: 5 out of 5 stars5/5 (1)

- Root Locus Diagram: Upon Completion of This Chapter You Will Be Able ToDocument24 pagesRoot Locus Diagram: Upon Completion of This Chapter You Will Be Able ToGnanendraReddyNo ratings yet

- CH 10 PracticeDocument7 pagesCH 10 PracticeGnanendraReddy100% (1)

- Unit 31Document6 pagesUnit 31GnanendraReddyNo ratings yet

- Gnany ResumeDocument2 pagesGnany ResumeGnanendraReddyNo ratings yet

- Compulsory Land Acquisition and Compensation-FAO Land Tenure StudyDocument63 pagesCompulsory Land Acquisition and Compensation-FAO Land Tenure StudySatya Mishra100% (1)

- (WWW - Entrance-Exam - Net) - Tech Mahindra Placement Sample Paper 2Document2 pages(WWW - Entrance-Exam - Net) - Tech Mahindra Placement Sample Paper 2PERFECTPARDHUNo ratings yet

- Vocabulary Practice Lesson-1: GatecounsellorDocument1 pageVocabulary Practice Lesson-1: GatecounsellorPankaj FarswanNo ratings yet

- IES2013 EEE Objective Paper 1Document20 pagesIES2013 EEE Objective Paper 1Srinivas DalliNo ratings yet

- X X U Y U: APSPDCL A.E'S QUESTIONS HELD ON 10-07-2010 (Part-Ii)Document5 pagesX X U Y U: APSPDCL A.E'S QUESTIONS HELD ON 10-07-2010 (Part-Ii)GnanendraReddyNo ratings yet

- X X U Y U: APSPDCL A.E'S QUESTIONS HELD ON 10-07-2010 (Part-Ii)Document5 pagesX X U Y U: APSPDCL A.E'S QUESTIONS HELD ON 10-07-2010 (Part-Ii)GnanendraReddyNo ratings yet

- Basic GrammarDocument13 pagesBasic GrammarMar Carrasco CarrascoNo ratings yet

- SpecsDocument309 pagesSpecsNarendra GoudNo ratings yet

- Css - Divide - Content - Area Into Two Columns - Stack OverflowDocument5 pagesCss - Divide - Content - Area Into Two Columns - Stack OverflowjunkyardNo ratings yet

- Wsc2015 Tp10 PV TW Partslist Iso A PreDocument1 pageWsc2015 Tp10 PV TW Partslist Iso A PreCristyan ReisNo ratings yet

- Soln p3 21Document5 pagesSoln p3 21Vinicius RamosNo ratings yet

- Oxmetrics ManualDocument238 pagesOxmetrics ManualRómulo Tomé AlvesNo ratings yet

- Electric To Gas Kiln ConversionDocument13 pagesElectric To Gas Kiln Conversionkcrowder2014100% (2)

- Biffi Hydraulic ActuatorsDocument28 pagesBiffi Hydraulic ActuatorsMuthu Kumar RNo ratings yet

- Induction Training ChecklistDocument2 pagesInduction Training ChecklistGVS RaoNo ratings yet

- Method Statement For Testing and Commissioning of Lightning Protection SystemDocument9 pagesMethod Statement For Testing and Commissioning of Lightning Protection Systemjfejfe0% (1)

- Catalogos de Distribuidores Aquatrol PDFDocument24 pagesCatalogos de Distribuidores Aquatrol PDFcanizales70No ratings yet

- Heat Exchange Between Non-Black BodiesDocument5 pagesHeat Exchange Between Non-Black BodiesSubindas P KNo ratings yet

- Loadings and Sign Convention SummaryDocument9 pagesLoadings and Sign Convention SummaryGovindan KrishnamoorthybashyamNo ratings yet

- Edge Detection: From Matlab and Simulink To Real Time With Ti DspsDocument22 pagesEdge Detection: From Matlab and Simulink To Real Time With Ti DspsMohammed AL-MaaitahNo ratings yet

- Carbon Steel Plates TDCDocument3 pagesCarbon Steel Plates TDCshazanNo ratings yet

- Hach DRB200Document2 pagesHach DRB200Boyke WinterbergNo ratings yet

- 5WMNT 01CDocument2 pages5WMNT 01CSaraiNo ratings yet

- Duct Leakage TestingDocument51 pagesDuct Leakage Testingducatti996chNo ratings yet

- Object Oriented Programming 3Document18 pagesObject Oriented Programming 3rahul rastogiNo ratings yet

- Curriculum Vitae: Working ExperienceDocument2 pagesCurriculum Vitae: Working ExperienceSiti AjiraNo ratings yet

- Chemistry Study Material For CBSE Class-12Document246 pagesChemistry Study Material For CBSE Class-12Apex Institute75% (4)

- Apxvll13 CDocument2 pagesApxvll13 C1No ratings yet

- Capital BudgetingDocument30 pagesCapital BudgetingNarasimhaPrasadNo ratings yet

- Fluid Pump Maintenance ProcedureDocument8 pagesFluid Pump Maintenance ProcedureTrue StoryNo ratings yet

- HM ProjectDocument20 pagesHM ProjectChandan KumarNo ratings yet

- Model 3410: Shear Beam Load CellsDocument4 pagesModel 3410: Shear Beam Load CellsIvanMilovanovicNo ratings yet

- Wood - Bending Compound CurvesDocument4 pagesWood - Bending Compound CurveschriskpetersonNo ratings yet

- Manual Electrico Kobelco SK 330-8Document6 pagesManual Electrico Kobelco SK 330-8sanach041275% (4)

- The Potential of Seaweed Waste Gracilaria SP and eDocument10 pagesThe Potential of Seaweed Waste Gracilaria SP and eAngelica Riviera Brery GirsangNo ratings yet

- Thesis DocumentationDocument69 pagesThesis DocumentationKamiru ChanNo ratings yet

- Physicy Test XDocument12 pagesPhysicy Test XMerimaNo ratings yet