Professional Documents

Culture Documents

RC Delay Model: R Varies With The Mode of Operation Hence It Is Taken As The Ratio

Uploaded by

wajid ali0 ratings0% found this document useful (0 votes)

23 views6 pagesTransistors are modeled as having an internal resistance R that varies based on operating conditions. Smaller transistors have lower resistance. Capacitance C also increases with transistor size. The transient response of a circuit to a step input can be determined using Laplace transforms. The output will rise or fall exponentially towards the final value with a time constant of RC.

Original Description:

vlsi

Original Title

Lec11

Copyright

© © All Rights Reserved

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentTransistors are modeled as having an internal resistance R that varies based on operating conditions. Smaller transistors have lower resistance. Capacitance C also increases with transistor size. The transient response of a circuit to a step input can be determined using Laplace transforms. The output will rise or fall exponentially towards the final value with a time constant of RC.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

23 views6 pagesRC Delay Model: R Varies With The Mode of Operation Hence It Is Taken As The Ratio

Uploaded by

wajid aliTransistors are modeled as having an internal resistance R that varies based on operating conditions. Smaller transistors have lower resistance. Capacitance C also increases with transistor size. The transient response of a circuit to a step input can be determined using Laplace transforms. The output will rise or fall exponentially towards the final value with a time constant of RC.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

You are on page 1of 6

RC Delay Model

Transistors are assumed to have an internal resistance R.

R varies with the mode of operation hence it is taken as the ratio

𝑉𝑑𝑠 Τ𝐼𝑑𝑠 . This resistance in a circuit is taken to be associated with

the smallest transistor. A unit nMOS. It has a minimum length and

width ( 4Τ2 𝜆). If the width of a transistor is k times that of the unit

transistor its resistance is 𝑅Τ𝑘. pMOS, due to its higher hole

mobility compared to electron is taken to have a resistance 2R. 𝑅 ≈

10k.

A transistor operating under velocity saturation conditions ( high 𝑉𝑑𝑠 ) has a higher

resistance since the current does not change much with voltage. However we know

that 𝑉𝑑𝑠 is not large for transistors operating in series. Therefore they have lower

resistance.

Capacitance C is taken for the gate of the unit transistor. The same is taken for the

source and drain. Since the area and perimeter of the source/drain regions increase

on increasing the width, the capacitance associated increases. If the width is k

times the unit width the capacitance is kC. Capacitance generally depend on

voltages. C is taken to be 1fF/mm width.

A 3-input NAND gate and equivalent circuit is shown.

The width of each nMOS in series is adjusted to give

The same resistance when combined equal to R. The

parallel connected pMOS width is also doubled to get

R.

Transient Response

This is the ratio 𝑉𝑜𝑢𝑡 Τ𝑉𝑖𝑛

1

𝐻 𝑠 =

1 + 𝑠𝑅𝐶

s is a complex number having the dimension of inverse

time

For a step input assuming initially uncharged capacitor

The Laplace transform of input is

∞

𝑠𝑡

𝑉𝐷𝐷

න 𝑉𝐷𝐷 𝑒 𝑑𝑡 =

0 𝑠

To obtain the output we have to take the inverse Laplace

transform of 𝑡𝑟𝑎𝑛𝑠𝑓𝑒𝑟 𝑓𝑢𝑛𝑐𝑡𝑖𝑜𝑛 × 𝑖𝑛𝑝𝑢𝑡

Two methods

1. Using partial fractions and tables

2. Applying the concepts of calculus of residue

𝑉𝐷𝐷

• 𝑉𝑜𝑢𝑡 =L-1𝐻(𝑠)

𝑠

1 1 1

• 𝐻 𝑠 = − 1

𝑠 𝑠 𝑠+

𝑅𝐶

𝑡

−

𝑉𝑜𝑢𝑡 = 𝑉𝐷𝐷 1 − 𝑒 𝑅𝐶

Similarly the decay of a capacitor can be obtained by using the initial condition that the

capacitor is charged and there is no applied potential source.

𝑡

−𝑅𝐶

𝑉𝑜𝑢𝑡 = 𝑉𝐷𝐷 𝑒

Notice that the logic low threshold 𝑉𝐷𝐷 Τ2 is obtained at the time

𝑡𝑝𝑑 = 𝑅𝐶 ln 2

𝑡𝑝𝑑 = 0.693𝑅𝐶

You might also like

- CH - 3-3 - Half-Wave RectifiersDocument18 pagesCH - 3-3 - Half-Wave RectifiersEmad El shabrwayNo ratings yet

- Introduction To Energy Storage ElementsDocument13 pagesIntroduction To Energy Storage ElementspaulamarieestrellalengascoNo ratings yet

- RSE2701 06 AcFiltersDocument19 pagesRSE2701 06 AcFiltersManibharathi DNo ratings yet

- Easy(er) Electrical Principles for Extra Class Ham License (2012-2016)From EverandEasy(er) Electrical Principles for Extra Class Ham License (2012-2016)No ratings yet

- Low Pass & High Pass Pi Section Filter Lab ManualDocument17 pagesLow Pass & High Pass Pi Section Filter Lab ManualRiya MaityNo ratings yet

- HV Lec2Document15 pagesHV Lec2Thiventhiniy RajendranNo ratings yet

- Module-3: Recombination in SemiconductorsDocument6 pagesModule-3: Recombination in SemiconductorsKARUTURI AKASH 17BEC0396No ratings yet

- 5TH Chapter - Eec-01Document33 pages5TH Chapter - Eec-01Samaseen PrabhatNo ratings yet

- KUANTUM TÜNELLEME ETKİSİ VE DNA'DA NOKTA MUTASYONLARIN ZAMANI YDU-seminer Talk by Prof. Dr. Durmus DemirDocument29 pagesKUANTUM TÜNELLEME ETKİSİ VE DNA'DA NOKTA MUTASYONLARIN ZAMANI YDU-seminer Talk by Prof. Dr. Durmus DemirAli ÖvgünNo ratings yet

- Chapter 1. Time - Domain Analysis of Electric Circuits PDFDocument42 pagesChapter 1. Time - Domain Analysis of Electric Circuits PDFThùy Dung Nguyễn ThịNo ratings yet

- Notes RC Circuit Transcient BehaviorDocument33 pagesNotes RC Circuit Transcient BehaviorVinodh LahiruNo ratings yet

- Electrical Circuits Lecture 6,7,8 SummaryDocument5 pagesElectrical Circuits Lecture 6,7,8 SummaryRaghad Al-ShaikhNo ratings yet

- Resonance Power Factor and Q FactorDocument7 pagesResonance Power Factor and Q FactorBhishma Kant VermaNo ratings yet

- Inductor Inductance IIDocument29 pagesInductor Inductance IIAhmed Ajmine NehalNo ratings yet

- Analysis of RLC Parallel Circuit and Verification of KCL in AC Circuits.Document22 pagesAnalysis of RLC Parallel Circuit and Verification of KCL in AC Circuits.alex100% (1)

- Lecture 23Document22 pagesLecture 23Dinuja SenevirathneNo ratings yet

- Elec1111 - T10 - S2 2018Document36 pagesElec1111 - T10 - S2 2018Conqueror VictoryNo ratings yet

- Microelectronics Chapter 05Document19 pagesMicroelectronics Chapter 05Sanskar BiswalNo ratings yet

- EE530 231 Lect 04Document19 pagesEE530 231 Lect 04SosoNo ratings yet

- Interactive Lecture 1 Topic 3 FINALDocument18 pagesInteractive Lecture 1 Topic 3 FINALAbdulJawad Ibrahim ElmezoghiNo ratings yet

- EE6508 - Power Quality - AG - Lecture - 2 (2) .PDDocument31 pagesEE6508 - Power Quality - AG - Lecture - 2 (2) .PDwing fatt hiewNo ratings yet

- Chapter 4Document23 pagesChapter 4amanuelfitsum589No ratings yet

- Lecture Notes 10Document17 pagesLecture Notes 10JoSaNo ratings yet

- Transformer Losses and EfficiencyDocument13 pagesTransformer Losses and Efficiencydaetersomine548No ratings yet

- Buck Converter Design Part 1 - Calculations & SimulationsDocument24 pagesBuck Converter Design Part 1 - Calculations & SimulationselektronikprojeniyapNo ratings yet

- Lab 7 LRCDocument4 pagesLab 7 LRCChristina Jean-Francois100% (1)

- 1st Order Ccts AC CctsDocument15 pages1st Order Ccts AC CctsWakahare PtahNo ratings yet

- Absorptiom and EmissionDocument48 pagesAbsorptiom and EmissionashishNo ratings yet

- DC-DC ChoppersDocument24 pagesDC-DC ChoppersAbdullah NasirNo ratings yet

- 3.1 Analog MultipliersDocument17 pages3.1 Analog MultipliersMarykutty CyriacNo ratings yet

- Guian Batilo Prob. 2.6Document6 pagesGuian Batilo Prob. 2.6Andre Luice GuianNo ratings yet

- CH 14-1 - Basic Elements and PhasorsDocument35 pagesCH 14-1 - Basic Elements and Phasorsعبدالله المعتقNo ratings yet

- Electromagnetics-Lec8-Divergence Theorem, Energy and Electric PotentialDocument15 pagesElectromagnetics-Lec8-Divergence Theorem, Energy and Electric PotentialNerlisa NadadoNo ratings yet

- Charging Discharging A CapacitorDocument2 pagesCharging Discharging A CapacitorMr SonuNo ratings yet

- Formula and Figures XIIDocument12 pagesFormula and Figures XIIDr SaabNo ratings yet

- Electrical ConductivityDocument3 pagesElectrical ConductivitySambhavi MishraNo ratings yet

- Chapter 6-1st and 2nd Order Transient AnalysisDocument54 pagesChapter 6-1st and 2nd Order Transient AnalysisPoni HenryNo ratings yet

- Lesson 4Document12 pagesLesson 4Achyuta PatroNo ratings yet

- Lab Report 9 PDFDocument4 pagesLab Report 9 PDFRajput JanjuaNo ratings yet

- 12 Second-Order Circuits (Part 2)Document32 pages12 Second-Order Circuits (Part 2)Brandon CilNo ratings yet

- Lecture 1Document29 pagesLecture 1khaddamoazNo ratings yet

- RLC Circuits As Filters: 1 Circuits With Resistors and Capacitors (Continued)Document4 pagesRLC Circuits As Filters: 1 Circuits With Resistors and Capacitors (Continued)sarim rizviNo ratings yet

- Che 414n - Converging-Diverging NozzlesDocument89 pagesChe 414n - Converging-Diverging Nozzlesca1No ratings yet

- Capacitance Fall Into Two Categories Intrinsic Capacitance Extrinsic CapacitanceDocument10 pagesCapacitance Fall Into Two Categories Intrinsic Capacitance Extrinsic Capacitancewajid aliNo ratings yet

- CSE250 Lab Exp 8 Simulation TransientDocument10 pagesCSE250 Lab Exp 8 Simulation TransientArefin MahinNo ratings yet

- Surface Chemistry 3Document10 pagesSurface Chemistry 3Elisha NaidooNo ratings yet

- TransformerDocument45 pagesTransformerM.Tharun KumarNo ratings yet

- Module-3: Recombination in SemiconductorsDocument45 pagesModule-3: Recombination in Semiconductorsnidhi patelNo ratings yet

- 21.energy, Time Constant RC Source FreeDocument12 pages21.energy, Time Constant RC Source FreeIbrahim GhunaimNo ratings yet

- Chapt 2 Electric Circuits-1Document40 pagesChapt 2 Electric Circuits-1Blessed RazimosNo ratings yet

- ECEN 214 Lab 6Document10 pagesECEN 214 Lab 6Shoaib AhmedNo ratings yet

- 5b. Rectifiers With RL LoadDocument20 pages5b. Rectifiers With RL LoadAbdullah NasirNo ratings yet

- Power Elect NotesDocument112 pagesPower Elect NotesAditya AvhadNo ratings yet

- Emailing AC - Exp - 04 - StudentDocument4 pagesEmailing AC - Exp - 04 - StudentNafiul BariNo ratings yet

- 11 1 Dynamic Closed LoopDocument34 pages11 1 Dynamic Closed LoopShilpya KurniasihNo ratings yet

- DC-to-DC Converter in Maximum Power Point Tracking (THE PHOTOVOLTAIC POWER SYSTEM)Document14 pagesDC-to-DC Converter in Maximum Power Point Tracking (THE PHOTOVOLTAIC POWER SYSTEM)Andrei - Cristian SIMIONNo ratings yet

- External FlowDocument34 pagesExternal FlowEbrahim ElhawamNo ratings yet

- Eligibility Criteria For Joining Army Medical College For MBBS/BDSDocument5 pagesEligibility Criteria For Joining Army Medical College For MBBS/BDSXeric100% (2)

- DC Transfer Characteristics of CMOS Gates and Pass TransistorsDocument6 pagesDC Transfer Characteristics of CMOS Gates and Pass Transistorswajid aliNo ratings yet

- Capacitance Fall Into Two Categories Intrinsic Capacitance Extrinsic CapacitanceDocument10 pagesCapacitance Fall Into Two Categories Intrinsic Capacitance Extrinsic Capacitancewajid aliNo ratings yet

- VLSIDocument15 pagesVLSIwajid aliNo ratings yet

- Stick DiagramsDocument34 pagesStick DiagramsNagaraju NeelaNo ratings yet

- General Description: Dimmable Greenchip Driver For LED LightingDocument18 pagesGeneral Description: Dimmable Greenchip Driver For LED Lightingsluz2000No ratings yet

- Analog Layout DesignDocument244 pagesAnalog Layout DesignAgnathavasi100% (5)

- Principles and Applications of Electrical Engineering 7Th Edition Giorgio Rizzoni Download PDF ChapterDocument51 pagesPrinciples and Applications of Electrical Engineering 7Th Edition Giorgio Rizzoni Download PDF Chaptervanessa.rider154100% (8)

- Irjet V4i5125 PDFDocument5 pagesIrjet V4i5125 PDFAnonymous plQ7aHUNo ratings yet

- Artículo1 PDFDocument6 pagesArtículo1 PDFDania Largo JaimesNo ratings yet

- Electronic Principles MalvinoDocument12 pagesElectronic Principles Malvinojeravi84No ratings yet

- Xerox Phaser 6100 Parts & ServiceDocument216 pagesXerox Phaser 6100 Parts & ServiceMaks ProstNo ratings yet

- Ir 2101Document14 pagesIr 2101Willard DmpseyNo ratings yet

- M3006DDocument4 pagesM3006DFranklin JimenezNo ratings yet

- The FET-OR Connection For Power Supplies: Backup Supply, Battery Operation, diode-OR, MOSFET, Power-Supply SequencingDocument3 pagesThe FET-OR Connection For Power Supplies: Backup Supply, Battery Operation, diode-OR, MOSFET, Power-Supply SequencingJonathan JaegerNo ratings yet

- A 01 - C 01 - T 01Document101 pagesA 01 - C 01 - T 01Rasel IslamNo ratings yet

- P-Channel Power Mosfets Selector Guide: Vishay SiliconixDocument20 pagesP-Channel Power Mosfets Selector Guide: Vishay SiliconixJonny HayashiNo ratings yet

- Simple Diy Induction CircuitDocument13 pagesSimple Diy Induction CircuitSalim BlognetNo ratings yet

- IGBT - Basic - 1 EE TimeDocument11 pagesIGBT - Basic - 1 EE TimeRichard TsengNo ratings yet

- TLE ICT CSS 9 Q2 - Module1 PMCDocument25 pagesTLE ICT CSS 9 Q2 - Module1 PMCEstela Marie Damian DiuyanNo ratings yet

- Syllabus B.tech (ECE) January 2021Document69 pagesSyllabus B.tech (ECE) January 2021Lipi RajNo ratings yet

- Bipolar Junction Transistors (BJT) : Multimedia College (Sarawak) 1Document9 pagesBipolar Junction Transistors (BJT) : Multimedia College (Sarawak) 1Cathleen Erwina MangkaNo ratings yet

- Generalised Cockcroft-Walton Voltage MultipliersDocument2 pagesGeneralised Cockcroft-Walton Voltage MultipliersfeelblastNo ratings yet

- Eda ExamplesDocument27 pagesEda ExamplesTamilinbaaNo ratings yet

- Chapter - 3 MOSFET Working Operation - 2Document59 pagesChapter - 3 MOSFET Working Operation - 2Naty Dasilva Jr.No ratings yet

- ZXGD3003E6 5A (Peak) Gate Driver in SOT23-6: General DescriptionDocument8 pagesZXGD3003E6 5A (Peak) Gate Driver in SOT23-6: General DescriptionGawanimyd MydNo ratings yet

- Antipona, Clarence A. - Chapter 5-1, 5-2, 5-3 SummaryDocument3 pagesAntipona, Clarence A. - Chapter 5-1, 5-2, 5-3 Summaryclarence antiponaNo ratings yet

- Switching (30V, 9A) : RSS090N03Document4 pagesSwitching (30V, 9A) : RSS090N03uimNo ratings yet

- LAB 5-PE-LabDocument7 pagesLAB 5-PE-LabLovely JuttNo ratings yet

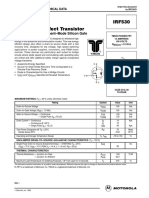

- Irf530 DDocument8 pagesIrf530 DnooneezNo ratings yet

- PREFIJOS de SemiconductoresDocument7 pagesPREFIJOS de SemiconductoresingenierossaNo ratings yet

- Syllabus PH 5118 & 5218Document5 pagesSyllabus PH 5118 & 5218Findx proNo ratings yet

- 22225-2023-Summer-Question-Paper (Msbte Study Resources)Document4 pages22225-2023-Summer-Question-Paper (Msbte Study Resources)Ronit PatilNo ratings yet

- Infineon Bts50055 1tma Ds v01 00 enDocument18 pagesInfineon Bts50055 1tma Ds v01 00 enCarlos Andres Garzon VargasNo ratings yet