Professional Documents

Culture Documents

Addressing Modes: Prepared by I. Mala Serene, AP (SG), SCOPE, VIT University

Uploaded by

VYOM GUPTA 20BCE20990 ratings0% found this document useful (0 votes)

10 views20 pagesOriginal Title

addressing modes-main1

Copyright

© © All Rights Reserved

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

10 views20 pagesAddressing Modes: Prepared by I. Mala Serene, AP (SG), SCOPE, VIT University

Uploaded by

VYOM GUPTA 20BCE2099Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

You are on page 1of 20

Addressing Modes

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Outline

• Addressing Modes

• Addressing Mode

• 1) To give programming versatility to the user

• pointers to memory, counters for loop control, indexing of data, ….

• 2) To reduce the number of bits in the addressing field of the instruction

• Instruction Cycle

• 1) Fetch the instruction from memory and PC + 1

• 2) Decode the instruction

• 3) Execute the instruction

• Program Counter (PC)

• PC keeps track of the instructions in the program stored in memory

• PC holds the address of the instruction to be executed next

• PC is incremented each time an instruction is fetched from memory

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Addressing Mode -Classification

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Types of Addressing Mode

• Implied Mode

• Operands are specified implicitly in definition of the instruction

• Examples

• COM : Complement Accumulator

• Operand in AC is implied in the definition of the

instruction

• PUSH : Stack push

• Operand is implied to be on top of the stack

• Immediate Mode

• Operand field contains the actual operand

• Useful for initializing registers to a constant value

• Example : LD #NBR

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Register Addressing Mode

• Register Mode

• Operands are in

registers

• Register is selected

from a register field in

the instruction

• k-bit register field can

specify any one of 2k

registers

• Example : LD R1

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Register Indirect

Addressing Mode

• Register Indirect Mode

• Selected register

contains the address

of the operand rather

than the operand itself

• Address field of the

instruction uses fewer

bits to select a

memory address

• Register select bit

• Example : LD (R1)

AC R1 Implied Mode

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Direct Addressing Mode

• Direct Addressing Mode

• Effective address is

equal to the address

field of the instruction

(Operand)

• Address field specifies

the actual branch

address in a branch-type

instruction AC M [ ADR]

ADR = Address part of Instruction

• Example : LD ADR

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Indirect

Addressing Mode

• Indirect Addressing Mode

• Address field of instruction

gives the address where the

effective address is stored in

memory

• Example : LD @ADR

AC M [ M [ ADR]]

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Auto increment or

Autodecrement Mode

• Autoincrement or Autodecrement Mode

• Similar to the register indirect mode except that

• the register is incremented after its value is used to access memory

• the register is decrement before its value is used to access memory

• Example (Autoincrement) : LD (R1)+ AC M [ R1], R1 R1 1

• Extension to Register indirect addressing mode.

• Register incremented or decremented before or after accessing

memory

• Useful while transferring large chunks of contiguous data.

Relative Addressing

Mode

• Relative Addressing

Mode

• PC is added to the

address part of the

instruction to obtain

the effective address

AC M: [LD

• Example PC ADR]

$ADR

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Based and Indexed Addressing

Mode

• Indexed Addressing Mode

• XR (Index register) is added to the address part of the instruction to obtain

the effective address

• Example : LD ADR(XR)

AC M [ ADR XR]

• Base Register Addressing Mode

• the content of a base register is added to the address part of the instruction

to obtain the effective address

• base register (BR) : LD ADR(BR

• base register hold a base address AC M [ BR ADR]

• the address field of the instruction gives a displacement relative to this base address

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

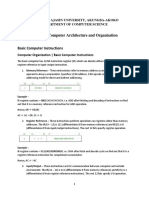

Basic Addressing Modes

Differences

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Problems

• Find the effective address and the content of AC for the given

data.

V.Saritha, SCSE, VIT University

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Addressing Mode Effective Content of AC

Address

Direct Address 500 AC ← (500) 800

Immediate operand 201 AC ← 500 500

Indirect address 800 AC ← ((500)) 300

Relative address 702 AC ← (PC + 500) 325

Indexed address 600 AC ← (XR + 500) 900

Register - AC ← R1 400

Register Indirect 400 AC ← (R1) 700

Autoincrement 400 AC ← (R1)+ 700

Autodecrement 399 AC ← -(R1) 450

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Questions

• An instruction is stored at location 300 with its address field at

location 301. The address field has the value 400. A processor

register R1 contains the number 200. Evaluate the effective

address if the addressing mode of the instruction is (a) direct; (b)

immediate (c) relative (d) register indirect; (e) index with R1 as

the index register.

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Cont ‘

• An address field in an instruction contains decimal value

14. where is the corresponding operand located for:

• Immediate addressing?

• Direct addressing?

• Indirect addressing?

• Register addressing?

• Register indirect addressing?

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

Problems

• A two-word instruction is stored in memory at an address

designated by the symbol W. The address field of the

instruction (stored at W + 1) is designated by the symbol Y.

The operand used during the execution of the instruction is

stored at an address symbolized by Z. An index register

contains the value X. State how Z is calculated from the

other addresses if the addressing mode of the instruction is

– Direct

– Indirect

– Relative

– Indexed

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

• Assume that in a certain byte-addressed machine all

instructions are 32 bits long. Assume the following state of

affairs for the machine: Fill in the following table:

Immediate

Direct

Indirect

Register

Register Indirect

Based

Relative

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

• Given the following memory values and a one-address machine with an

accumulator, what values do the following instructions load into the

accumulator?

– Word 20 contains 40

– Word 30 contains 50

– Word 40 contains 60

– Word 50 contains 70

• Load immediate 20

• Load direct 20

• Load indirect 20

• Load immediate 30

• Load direct 30

• Load indirect 30

• Let the address stored in the program counter be designated by the symbol

X1. The instruction stored in X1 has the address part (operand reference)

X2. The operand needed to execute the instruction is stored in the memory

word with address X3. An index register contains the value X4. What is

the relationship between these various quantities if the addressing mode of

the instruction is (a) direct (b) indirect (c) PC relative (d) indexed?

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

References

• W. Stallings, Computer organization and architecture,

Prentice-Hall,2000

• M. M. Mano, Computer System Architecture, Prentice-Hall

Prepared by I. Mala Serene, AP(SG), SCOPE, VIT University

You might also like

- Addressing Modes: by V.Saritha Assistant Professor (SR) SCSE, VIT UniversityDocument26 pagesAddressing Modes: by V.Saritha Assistant Professor (SR) SCSE, VIT UniversityGaurang SinhaNo ratings yet

- Addressing Modes: How Operands Are Specified in InstructionsDocument22 pagesAddressing Modes: How Operands Are Specified in InstructionsDevansh b BajpaiNo ratings yet

- Addressing Modes of Computer ArchitectureDocument25 pagesAddressing Modes of Computer ArchitectureAravindh Boopathi100% (1)

- 12-Addressing Modes-08-02-2024Document25 pages12-Addressing Modes-08-02-2024Baladhithya TNo ratings yet

- Lect13-Addressingmode 15012019Document26 pagesLect13-Addressingmode 15012019kiranrawkey2912No ratings yet

- Amity School of Engineering & Technology Addressing ModesDocument17 pagesAmity School of Engineering & Technology Addressing ModesabhishekNo ratings yet

- Midterms in Computer ArchitectureDocument23 pagesMidterms in Computer ArchitectureRealyn SolimanNo ratings yet

- Chapter 3 (Part II) - Addressing ModesDocument18 pagesChapter 3 (Part II) - Addressing ModesKirubel EsayasNo ratings yet

- Instruction Sets: Addressing Modes and FormatsDocument47 pagesInstruction Sets: Addressing Modes and FormatsVickneswaran KalerwananNo ratings yet

- Addressing Modes 8086Document19 pagesAddressing Modes 8086Infinity Star GamingNo ratings yet

- Instructions Formats & Addressing ModesDocument18 pagesInstructions Formats & Addressing ModesObsii ChalaNo ratings yet

- Addressing ModesDocument25 pagesAddressing ModesAnurag AnandNo ratings yet

- William Stallings Computer Organization and Architecture 7 Edition Instruction Sets: Addressing Modes and FormatsDocument45 pagesWilliam Stallings Computer Organization and Architecture 7 Edition Instruction Sets: Addressing Modes and FormatsAlaa YounisNo ratings yet

- 03 AddressingModesDocument25 pages03 AddressingModesAbdalrhman juberNo ratings yet

- Chapter 2.3Document29 pagesChapter 2.3Temesgen MekonenNo ratings yet

- Instruction Sets: Addressing ModesDocument28 pagesInstruction Sets: Addressing ModesnikefalconNo ratings yet

- William Stallings Computer Organization and Architecture 8 Edition Instruction Sets: Addressing Modes and FormatsDocument47 pagesWilliam Stallings Computer Organization and Architecture 8 Edition Instruction Sets: Addressing Modes and FormatsGiri KanyakumariNo ratings yet

- Assignment - I CSE2003-Computer Architecture and OrganizationDocument1 pageAssignment - I CSE2003-Computer Architecture and Organizationsharma.vivek.1512No ratings yet

- Instruction Sets: Addressing Modes and FormatsDocument52 pagesInstruction Sets: Addressing Modes and FormatsMistura AdeyemoNo ratings yet

- William Stallings Computer Organization and Architecture 6 Edition Instruction Sets: Addressing Modes and FormatsDocument36 pagesWilliam Stallings Computer Organization and Architecture 6 Edition Instruction Sets: Addressing Modes and FormatsandiNo ratings yet

- Coa Unit1Document99 pagesCoa Unit1Ashish SharmaNo ratings yet

- Instruction Sets addressing modesDocument23 pagesInstruction Sets addressing modesWaseem HaiderNo ratings yet

- Addressing ModesDocument6 pagesAddressing Modesnancy_01No ratings yet

- 1-Module 3 Instr Addressing Modes Part ADocument48 pages1-Module 3 Instr Addressing Modes Part ALalala LandNo ratings yet

- Computer Organization: Instructions andDocument25 pagesComputer Organization: Instructions andmanishNo ratings yet

- Computer Architecture and Organization Instruction Sets: Addressing Modes and FormatsDocument35 pagesComputer Architecture and Organization Instruction Sets: Addressing Modes and FormatsJohnMactavishPalmerNo ratings yet

- Computer Architecture and Organization Instruction Sets: Addressing Modes and FormatsDocument35 pagesComputer Architecture and Organization Instruction Sets: Addressing Modes and FormatsVikas BeniwalNo ratings yet

- Computer Architecture and Organization Instruction Sets: Addressing Modes and FormatsDocument35 pagesComputer Architecture and Organization Instruction Sets: Addressing Modes and FormatsVijay KanthNo ratings yet

- Computer ArchitectureDocument96 pagesComputer ArchitectureOlusi JacksonNo ratings yet

- COA Mod2Document51 pagesCOA Mod2Boban MathewsNo ratings yet

- Addressing Modes of 8086Document19 pagesAddressing Modes of 8086sureshgurujiNo ratings yet

- Addressing modes explainedDocument31 pagesAddressing modes explainedRohan TiwariNo ratings yet

- Addressing ModesDocument26 pagesAddressing ModesCineboy SkVNo ratings yet

- MCS-012Addressing ModeDocument17 pagesMCS-012Addressing ModeVishwajeetsinh Jadeja100% (1)

- Assemblyunit 1Document51 pagesAssemblyunit 1RubyNo ratings yet

- Chapter 3 LMSDocument37 pagesChapter 3 LMSvexadid644No ratings yet

- Computer Architecture and Organization: Dr. Khawar Khurshid Spring 20Document48 pagesComputer Architecture and Organization: Dr. Khawar Khurshid Spring 20The AwsomistNo ratings yet

- Common Addressing ModesDocument7 pagesCommon Addressing ModeskingofsuperstarNo ratings yet

- CO Formula Notes - PDF 62Document11 pagesCO Formula Notes - PDF 62Girdhar GopalNo ratings yet

- Introduction of Stack Based CPU Organization: Processer DesignDocument15 pagesIntroduction of Stack Based CPU Organization: Processer DesignlalitNo ratings yet

- (SS) System Software Viva Question and AnswersDocument15 pages(SS) System Software Viva Question and AnswersVenkatesh NaiduNo ratings yet

- Adhiparasakthi College of Engineering, G.B.Nagar, KalavaiDocument19 pagesAdhiparasakthi College of Engineering, G.B.Nagar, KalavaiNandha KumarNo ratings yet

- Module 4Document21 pagesModule 4barnabasNo ratings yet

- 2 Marks Que &ansDocument30 pages2 Marks Que &ansKanthimathi SureshNo ratings yet

- UIE CSE 8085 Addressing ModesDocument11 pagesUIE CSE 8085 Addressing ModesaattishNo ratings yet

- CH 5 OnDUPdated UNit 4 Addressing ModesDocument46 pagesCH 5 OnDUPdated UNit 4 Addressing ModesSujan TimalsinaNo ratings yet

- Computer ArchitectureDocument3 pagesComputer ArchitectureS.Ramesh rajaNo ratings yet

- Addressing ModesDocument20 pagesAddressing ModesAkhil B SkariaNo ratings yet

- Assembly Word SheetDocument7 pagesAssembly Word SheetnazmulNo ratings yet

- CS1203-SYSTEM SOFTWAREDocument31 pagesCS1203-SYSTEM SOFTWAREMohammed HashimNo ratings yet

- CAO - Unit-3 (Addressing Modes)Document8 pagesCAO - Unit-3 (Addressing Modes)naqeebansari1221No ratings yet

- Addressing Modes GuideDocument4 pagesAddressing Modes GuideMesay NebelbalNo ratings yet

- 8086 Instruction Addressing Modes ExplainedDocument29 pages8086 Instruction Addressing Modes Explainedayush bansalNo ratings yet

- Addressing Modes in Computer OrganizationDocument8 pagesAddressing Modes in Computer OrganizationArchana R gopinathNo ratings yet

- Presented By: Syeda Rida Fatima TaqviDocument22 pagesPresented By: Syeda Rida Fatima TaqviSadaf RasheedNo ratings yet

- Instruction Sets: Characteristics and Functions Addressing Modes and FormatsDocument21 pagesInstruction Sets: Characteristics and Functions Addressing Modes and FormatsPankaj SlathiaNo ratings yet

- Addressing Pentium and Powerpc Addressing Modes Instruction Formats Pentium and Powerpc Instruction FormatsDocument30 pagesAddressing Pentium and Powerpc Addressing Modes Instruction Formats Pentium and Powerpc Instruction FormatsSagar GopaniNo ratings yet

- Addressing Modes ExplainedDocument25 pagesAddressing Modes ExplainedTariku KebedeNo ratings yet

- 02Unit2pptx__2024_01_23_07_24_47Document66 pages02Unit2pptx__2024_01_23_07_24_47jaynathavani9711No ratings yet

- DISK and RAIDDocument37 pagesDISK and RAIDVYOM GUPTA 20BCE2099No ratings yet

- DatarepDocument69 pagesDatarepVYOM GUPTA 20BCE2099No ratings yet

- 3 Data Storage: Foundations of Computer Science à Cengage LearningDocument69 pages3 Data Storage: Foundations of Computer Science à Cengage LearningVYOM GUPTA 20BCE2099No ratings yet

- Addressing Modes: Prepared by I. Mala Serene, AP (SG), SCOPE, VIT UniversityDocument20 pagesAddressing Modes: Prepared by I. Mala Serene, AP (SG), SCOPE, VIT UniversityVYOM GUPTA 20BCE2099No ratings yet

- Asynchronous Data TransferDocument26 pagesAsynchronous Data TransferVYOM GUPTA 20BCE2099No ratings yet

- Addressing Modes: Prepared by I. Mala Serene, AP (SG), SCOPE, VIT UniversityDocument20 pagesAddressing Modes: Prepared by I. Mala Serene, AP (SG), SCOPE, VIT UniversityVYOM GUPTA 20BCE2099No ratings yet

- Performance of A Processor - Instruction Execution Rate: Frequency Cycle Time Instruction CountDocument15 pagesPerformance of A Processor - Instruction Execution Rate: Frequency Cycle Time Instruction CountVYOM GUPTA 20BCE2099No ratings yet

- A Mini Project ReportDocument54 pagesA Mini Project ReportPosi NamdamNo ratings yet

- 1979 Motorola Memory Data BookDocument320 pages1979 Motorola Memory Data BookBapeNo ratings yet

- Android-Based Simulator To Support Tomasulo Algorithm Teaching and LearningDocument7 pagesAndroid-Based Simulator To Support Tomasulo Algorithm Teaching and Learningowais khanNo ratings yet

- Modbus Controller (2080 Serialisol)Document2 pagesModbus Controller (2080 Serialisol)Piyush KumarNo ratings yet

- Brkarc 2035Document128 pagesBrkarc 2035Ernaldo TobingNo ratings yet

- 11-3-2019 001 Bizgram Daily DIY PricelistDocument14 pages11-3-2019 001 Bizgram Daily DIY PricelistSaasidharan SaasiNo ratings yet

- Characteristics of Virtualized EnvironmentDocument54 pagesCharacteristics of Virtualized EnvironmentmassNo ratings yet

- SUNGLAO - TM PortfolioDocument60 pagesSUNGLAO - TM PortfolioGIZELLE SUNGLAONo ratings yet

- DFU ExplainDocument18 pagesDFU Explainjoshua camachoNo ratings yet

- MS - v01 MP6000 7000 8000 PDFDocument1,465 pagesMS - v01 MP6000 7000 8000 PDFNguyễn Thế ThaoNo ratings yet

- SAP 1 Simple As Possible ComputerDocument51 pagesSAP 1 Simple As Possible ComputerShawon Nazrul Islam80% (5)

- Lab Windows - User ManualDocument304 pagesLab Windows - User ManualPratik PanchalNo ratings yet

- AppendixDocument118 pagesAppendixAbu Yussif AlaboodiNo ratings yet

- 8bae00 A7608e H at - V4.01 - DL (230725) 1Document16 pages8bae00 A7608e H at - V4.01 - DL (230725) 1vakif.techNo ratings yet

- SAP BPA Sizing Guide V9Document11 pagesSAP BPA Sizing Guide V9RaviNo ratings yet

- CCTV Questionnaire TemplateDocument9 pagesCCTV Questionnaire TemplateVishalNo ratings yet

- Modicon X80 I/O Platform: CompatibilityDocument2 pagesModicon X80 I/O Platform: CompatibilityGillSportNo ratings yet

- VITHALANI PARESH K Sr Lect /EC GPT RAICHUR UNIT-1 ARM Lecture NotesDocument19 pagesVITHALANI PARESH K Sr Lect /EC GPT RAICHUR UNIT-1 ARM Lecture NotesRangaraj A.GNo ratings yet

- 586 Card DatasheetDocument4 pages586 Card DatasheetArtur HeiseNo ratings yet

- 1734-SG001D-EN-P - September 2010Document68 pages1734-SG001D-EN-P - September 2010jesusortegavNo ratings yet

- Anviz W2Pro Catalogue en 05.10.2019Document4 pagesAnviz W2Pro Catalogue en 05.10.2019Marius MurariuNo ratings yet

- JAIPUR NATIONAL UNIVERSITY INTERNAL ASSIGNMENTDocument15 pagesJAIPUR NATIONAL UNIVERSITY INTERNAL ASSIGNMENTGhanshyam Sharma33% (3)

- Introduction To ComputerDocument30 pagesIntroduction To ComputerSama Lex alexisNo ratings yet

- M64 RS 232 Setup PDFDocument9 pagesM64 RS 232 Setup PDFLuthfi Naufal WaliyyudienNo ratings yet

- Connecting A Yamaha Engine To The NMEA 2000 NetworkDocument10 pagesConnecting A Yamaha Engine To The NMEA 2000 Networkpetercharland100% (2)

- 2018 Edpm Paper 1 PDFDocument5 pages2018 Edpm Paper 1 PDFCeline DookramNo ratings yet

- Oracle Database in MemoryDocument9 pagesOracle Database in MemoryezioflavioNo ratings yet

- 8051Document72 pages8051Arjun Aj100% (1)

- Universal Willem EPROM Programmer Quick Start Guide V1.2: 1. InstallationDocument8 pagesUniversal Willem EPROM Programmer Quick Start Guide V1.2: 1. InstallationmarcofirminoNo ratings yet

- Skema Toshiba-L600-L640-L645-TE2-U4-atherosDocument35 pagesSkema Toshiba-L600-L640-L645-TE2-U4-atherosDaniNo ratings yet