0% found this document useful (0 votes)

657 views21 pagesPower Management - PPT

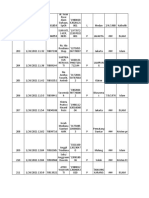

- Power management defines states for both functions (D0-D3) and links (L0-L3). D0 is the operational state while D3 is powered off. L0 is the operational link state while L3 is the link off state.

- Active state power management allows links to enter lower power states like L0s and L1 while functions are in the active D0 state, improving power savings.

- Software initiates transitions to lower power states by placing functions in D-states like D3. This triggers autonomous link state transitions through various states until the L2/L3 ready state is reached and main power can be removed.

Uploaded by

suvendra123Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPTX, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

657 views21 pagesPower Management - PPT

- Power management defines states for both functions (D0-D3) and links (L0-L3). D0 is the operational state while D3 is powered off. L0 is the operational link state while L3 is the link off state.

- Active state power management allows links to enter lower power states like L0s and L1 while functions are in the active D0 state, improving power savings.

- Software initiates transitions to lower power states by placing functions in D-states like D3. This triggers autonomous link state transitions through various states until the L2/L3 ready state is reached and main power can be removed.

Uploaded by

suvendra123Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPTX, PDF, TXT or read online on Scribd