Professional Documents

Culture Documents

DPCO Chapter 4

Uploaded by

kanimozhi rajasekarenOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DPCO Chapter 4

Uploaded by

kanimozhi rajasekarenCopyright:

Available Formats

Chapter 4

The Processor

Chapter 4 — The Processor — 1

• Instruction Execution

• Building a Data Path

• Designing a Control Unit

• Hardwired Control

• Micro programmed Control

• Pipelining

• Data Hazard

• Control Hazards

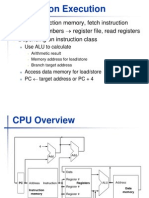

Instruction Execution

Instruction Execution

• PC points to instruction memory,

– To FETCH instruction

• Register numbers point to the register file,

– To read register contents

• Depending on instruction class

– Use ALU to calculate

• Arithmetic result

• Memory address for load/store

• Branch target address

– Access data memory for load/store

– PC target address or next instruction (PC + 4)

Basic MIPS Implementation

Building a Data Path

Data path Segment for

Arithmetic-Logic Instructions

Data path Segment for Store word and Load

Word Instructions

Data Path Segment For Branch Instructions

Creating a single data path

ALU Control

• ALU used for

– Load/Store: F = add

– Branch: F = subtract

– R-type: F depends on funct field

ALU control Function

0000 AND

0001 OR

0010 add

0110 subtract

0111 set-on-less-than

1100 NOR

ALU Control

Assume 2-bit ALUOp derived from opcode

Combinational logic derives ALU control

The Main Control Unit

• Control signals derived from instruction

R-type 0 rs rt rd shamt funct

31:26 25:21 20:16 15:11 10:6 5:0

Load/

35 or 43 rs rt address

Store

31:26 25:21 20:16 15:0

Branch 4 rs rt address

31:26 25:21 20:16 15:0

opcode always read, write for sign-extend

read except R-type and and add

for load load

The datapath with all necessary multiplexors and all control lines identified.

Effect of the 7 control signals in the datapath

The effect of each of the seven control signals. When the 1-bit control to a twoway multiplexor is asserted, the multiplexor selects

the input corresponding to 1. Otherwise, if the control is deasserted, the multiplexor selects the 0 input. Remember that the state

elements all have the clock as an implicit input and that the clock is used in controlling writes. Gating the clock externally to a state

element can create timing problems.

Chapter 4 — The Processor — 18

Simple Datapath With Control Unit

Setting of control lines

The setting of the control lines is completely determined by the opcode fields of the

instruction.

Chapter 4 — The Processor — 20

R-Type Instruction

Load Instruction

Branch-on-Equal Instruction

Finalizing Control

Implementing Jumps

Jump 000010 address

31:26 25:0

• Jump uses word address

• Update PC with concatenation of

– Top 4 bits of old PC

– 26-bit jump address

– 00

Add

4

4

Jump

Instruction Shift

Memory

address

left 2 28

PC Read Instruction

Address 26

• Need an extra control signal decoded from opcode

Datapath With Jumps Added

You might also like

- The PIC Microcontroller: Your Personal Introductory CourseFrom EverandThe PIC Microcontroller: Your Personal Introductory CourseRating: 1 out of 5 stars1/5 (2)

- Computer Architecture: Chapter 4: The Processor Part 1Document51 pagesComputer Architecture: Chapter 4: The Processor Part 1Kiet LuongNo ratings yet

- Chapter 4 The ProcessorDocument131 pagesChapter 4 The ProcessorAk GptNo ratings yet

- Chapter V Processor ArchitectureDocument140 pagesChapter V Processor Architecturesiva prasadNo ratings yet

- Pooja VashisthDocument40 pagesPooja VashisthApurva SinghNo ratings yet

- CSA Seoultech 04Document137 pagesCSA Seoultech 04이다원No ratings yet

- Lecture 12Document29 pagesLecture 12Neal SchneierNo ratings yet

- Chapter 04 Computer Architecture and DDocument95 pagesChapter 04 Computer Architecture and DPooja VashisthNo ratings yet

- Chapter - 04 Mips Assembly Data PathDocument137 pagesChapter - 04 Mips Assembly Data PathAbubakar sabirNo ratings yet

- Patterson6e MIPS Ch04 PPTDocument137 pagesPatterson6e MIPS Ch04 PPTalapabainviNo ratings yet

- Ca06 2014 PDFDocument53 pagesCa06 2014 PDFPance CvetkovskiNo ratings yet

- Processor PDFDocument98 pagesProcessor PDFArafat KhanNo ratings yet

- Computer Organization and ArchitectureDocument108 pagesComputer Organization and ArchitectureMuhammad Zeeshan MughalNo ratings yet

- Lecture-13 CH-04 1Document26 pagesLecture-13 CH-04 1Osama RousanNo ratings yet

- Chapter 04 RISC VDocument130 pagesChapter 04 RISC VTrí ĐôNo ratings yet

- Chap 4 1Document57 pagesChap 4 1Tin TranNo ratings yet

- Chapter 4 PDFDocument135 pagesChapter 4 PDFMukesh Kumar MeenaNo ratings yet

- Arm InstDocument75 pagesArm InstJohnJohnNo ratings yet

- Datapath3 1upDocument26 pagesDatapath3 1upJaydeep RajputNo ratings yet

- ARM 1vDocument31 pagesARM 1vsuntosh_14No ratings yet

- Chapter Four The Processor: Datapath and ControlDocument45 pagesChapter Four The Processor: Datapath and ControlOsama AlqahtaniNo ratings yet

- CA 06 DatapathDocument26 pagesCA 06 Datapathwlsh2001No ratings yet

- D KannanDocument35 pagesD Kannanpreneeth Ramesh007No ratings yet

- Chapter 04 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface (The Morgan Kaufmann Series in Computer Architecture and Design) 5th EditionDocument137 pagesChapter 04 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface (The Morgan Kaufmann Series in Computer Architecture and Design) 5th EditionPriyanka Meena67% (6)

- Chapter 4 The ProcessorDocument131 pagesChapter 4 The ProcessorRahman AsmadNo ratings yet

- L13 Multicycle DatapathDocument62 pagesL13 Multicycle DatapathIsaacNo ratings yet

- Control Unit Design: Decoder &Document30 pagesControl Unit Design: Decoder &blackmaverick0912No ratings yet

- Chapter 5 Basic Computer Organization and DesignDocument84 pagesChapter 5 Basic Computer Organization and DesignKulwinder Jeet SinghNo ratings yet

- ACE201slides 8Document75 pagesACE201slides 8alexistheNo ratings yet

- The ARM Instruction Set: Advanced RISC MachinesDocument58 pagesThe ARM Instruction Set: Advanced RISC MachinesPoorva RathoreNo ratings yet

- Arm InstructionDocument102 pagesArm InstructionSHRIDHAR NNo ratings yet

- The ProcessorDocument27 pagesThe ProcessorPradhibaSelvaraniNo ratings yet

- Sap 2Document35 pagesSap 2Michael Vincent B. Nierva88% (8)

- ARM7TDMI ProcessorDocument44 pagesARM7TDMI Processormuralik_64No ratings yet

- 8085 Processor Unit I: Mr. S. VinodDocument52 pages8085 Processor Unit I: Mr. S. VinodVinod SrinivasanNo ratings yet

- PIC1Document183 pagesPIC1Gokul GocoolNo ratings yet

- Chapter5 2Document37 pagesChapter5 2preneeth Ramesh007No ratings yet

- CO Unit 2Document125 pagesCO Unit 2KarthikNo ratings yet

- CPU Structure and Function: Arithmetic Logic Unit Control Unit Control Registers DatapathDocument47 pagesCPU Structure and Function: Arithmetic Logic Unit Control Unit Control Registers DatapathSuhaila NajibNo ratings yet

- The ARM Instruction Set: Advanced RISC MachinesDocument58 pagesThe ARM Instruction Set: Advanced RISC MachinesarthicseNo ratings yet

- Unit 5Document56 pagesUnit 5TakeItEasyDude TIEDNo ratings yet

- SAPDocument21 pagesSAPdanielcasayuranNo ratings yet

- Unit 4Document53 pagesUnit 4subithavNo ratings yet

- Chapter 1Document26 pagesChapter 1SHRIDHAR NNo ratings yet

- The ARM Instruction Set: Advanced RISC MachinesDocument83 pagesThe ARM Instruction Set: Advanced RISC MachinesABHAYNo ratings yet

- ARM ProcessorDocument46 pagesARM Processoryixexi7070No ratings yet

- RTES - Chapter 2Document55 pagesRTES - Chapter 2Adugna NegeroNo ratings yet

- Sap-1 ArchitectureDocument9 pagesSap-1 ArchitectureAshna100% (1)

- Module 1 - Basic Computer Organization and Design-1Document61 pagesModule 1 - Basic Computer Organization and Design-1ajajaNo ratings yet

- Design of The MIPS ProcessorDocument24 pagesDesign of The MIPS Processorwelcome to my worldNo ratings yet

- Unit IiiDocument19 pagesUnit IiiPavithra JanarthananNo ratings yet

- Unit 1-2Document69 pagesUnit 1-2kiran281196No ratings yet

- Introduction To Processor Design & The ARM ArchitectureDocument65 pagesIntroduction To Processor Design & The ARM Architectureveer_frnd89100% (1)

- Module 4 Topic 2 ARM Processor FundamentalsDocument64 pagesModule 4 Topic 2 ARM Processor FundamentalsDeepti ChandrasekharanNo ratings yet

- CS401 - Short Notes Chapter 9Document3 pagesCS401 - Short Notes Chapter 9Zoha SheikhNo ratings yet

- Implementation of A 16-Bit RISC Processor Using FPGA ProgrammingDocument25 pagesImplementation of A 16-Bit RISC Processor Using FPGA ProgrammingTejashree100% (3)

- Cad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationDocument10 pagesCad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationkbkkrNo ratings yet

- Unit 5a - CPU DesignDocument64 pagesUnit 5a - CPU DesignMʌŋı ßʌķŞhı100% (1)

- MicroprocessorPPT 1Document40 pagesMicroprocessorPPT 1Gaurav KispottaNo ratings yet

- Image Segmentation Based On Adaptive K-Means Algorithm: Research Open AccessDocument10 pagesImage Segmentation Based On Adaptive K-Means Algorithm: Research Open Accesskanimozhi rajasekarenNo ratings yet

- A Review On Different Techniques of FICDocument14 pagesA Review On Different Techniques of FICkanimozhi rajasekarenNo ratings yet

- CS3351 Digital Principles and Computer Organization Lecture Notes 2Document213 pagesCS3351 Digital Principles and Computer Organization Lecture Notes 2kanimozhi rajasekarenNo ratings yet

- Shift Register - Parallel and Serial Shift RegisterDocument8 pagesShift Register - Parallel and Serial Shift Registerkanimozhi rajasekarenNo ratings yet

- CS3351 Digital Principles and Computer Organization Nov Dec 2022 Question Paper DownloadDocument3 pagesCS3351 Digital Principles and Computer Organization Nov Dec 2022 Question Paper Downloadkanimozhi rajasekarenNo ratings yet

- Shift RegistersDocument24 pagesShift Registerskanimozhi rajasekarenNo ratings yet

- Parkinson S Disease Detection Based On SDocument5 pagesParkinson S Disease Detection Based On SdaytdeenNo ratings yet

- Rivers and Their Origin (Top MCQ)Document24 pagesRivers and Their Origin (Top MCQ)Anil Yadav100% (1)

- Cusps: Ramesh 04-Jun-1976 12:30:00 PM Krishnagiri 78:14:0 E, 12:32:0 N Tzone: 5.5 KP (Original) Ayanamsha 23:26:2Document1 pageCusps: Ramesh 04-Jun-1976 12:30:00 PM Krishnagiri 78:14:0 E, 12:32:0 N Tzone: 5.5 KP (Original) Ayanamsha 23:26:2Suresh NatarajanNo ratings yet

- Lubricants - McMaster-CarrDocument8 pagesLubricants - McMaster-CarrjeanyoperNo ratings yet

- NeedScope On TechnologyDocument22 pagesNeedScope On TechnologyNguyen Ngo Dinh PhuongNo ratings yet

- Propositional LogicDocument41 pagesPropositional LogicMuneeb Javaid100% (1)

- List of Tyre Pyrolysis Oil Companies in IndiaDocument2 pagesList of Tyre Pyrolysis Oil Companies in IndiaHaneesh ReddyNo ratings yet

- Original Research PapersDocument13 pagesOriginal Research Papersrikaseo rikaNo ratings yet

- Conquering College The Most Fun You Can Have Learning The Things You Need To Know NodrmDocument144 pagesConquering College The Most Fun You Can Have Learning The Things You Need To Know NodrmVithorNo ratings yet

- Week 8: Spread-Spectrum Modulation - Direct Sequence Spread SpectrumDocument79 pagesWeek 8: Spread-Spectrum Modulation - Direct Sequence Spread SpectrumAmir MustakimNo ratings yet

- KV Class 3 Half Yearly Previous Year Question Paper 2019 ComputerDocument2 pagesKV Class 3 Half Yearly Previous Year Question Paper 2019 Computer02 Aanya Gupta VII CNo ratings yet

- Grade 8 - EnglishDocument2 pagesGrade 8 - EnglishTCHR KIMNo ratings yet

- Jimma UniversityDocument99 pagesJimma UniversityBekan NegesaNo ratings yet

- THE REFUND - Frigyes Karinthy: AuthorDocument6 pagesTHE REFUND - Frigyes Karinthy: AuthorMilind JamnekarNo ratings yet

- Book - Sefer Yetzira - Book of Creation - Free KabbalahDocument3 pagesBook - Sefer Yetzira - Book of Creation - Free KabbalahJoshuaNo ratings yet

- Revised Research ZoomDocument51 pagesRevised Research ZoomAubrey Unique EvangelistaNo ratings yet

- Om en A: F in Ite D Iffe Ren Ce-B Ase DN Um Eri Ca L M Eth Od SDocument426 pagesOm en A: F in Ite D Iffe Ren Ce-B Ase DN Um Eri Ca L M Eth Od SPrateek Kumar PandeyNo ratings yet

- PC Engineering Undergr 2014Document94 pagesPC Engineering Undergr 2014Austin JamesNo ratings yet

- Pearson Letter To ParentsDocument2 pagesPearson Letter To ParentsPatricia WillensNo ratings yet

- Presentation DelcorteDocument15 pagesPresentation Delcortecarlos2685No ratings yet

- SH5108 - 5 Occupational Health ProgrammeDocument34 pagesSH5108 - 5 Occupational Health Programmetaaouicha mujahidNo ratings yet

- Validation For A Login PageDocument2 pagesValidation For A Login PageAmal RajNo ratings yet

- FDocument102 pagesFTop channelNo ratings yet

- Case Study: Medisys Corp The Intense Care Product Development TeamDocument10 pagesCase Study: Medisys Corp The Intense Care Product Development TeamBig BNo ratings yet

- Solution PDFDocument20 pagesSolution PDFVard FarrellNo ratings yet

- Making Women's Medicine Masculine: OxpordDocument17 pagesMaking Women's Medicine Masculine: OxpordAdolfo Baqueiro100% (1)

- SOL-Logarithm, Surds and IndicesDocument12 pagesSOL-Logarithm, Surds and Indicesdevli falduNo ratings yet

- Report Writing: IBS HyderabadDocument35 pagesReport Writing: IBS HyderabadHarita SudhirNo ratings yet

- Bike Share ReportDocument16 pagesBike Share Reportsanjay975100% (1)

- THE INDIAN NAVY - Artificer Apprentice & Senior Secondary Recruit PDFDocument3 pagesTHE INDIAN NAVY - Artificer Apprentice & Senior Secondary Recruit PDFUjjwalNo ratings yet