Professional Documents

Culture Documents

Digital IC Tester

Uploaded by

Abhinav ChoudharyOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital IC Tester

Uploaded by

Abhinav ChoudharyCopyright:

Available Formats

Digital IC Tester

Thursday, November 20th, 2008

An Integrated Circuit tester (IC tester) is used to test Integrated Circuits (ICs). We can easily test any digital IC using this kind of an IC tester. For testing an IC, we need to use different hardware circuits for different ICs; like we need a particular kind of tester for testing a logic gate and another for testing flip flops or shift registers which involves more complication and time involved will also be more. So heres an IC tester to overcome this problem. Unlike other IC testers, this is more reliable and easier since we dont need to rig up different kind of circuits for different kind of ICs, each time we need to test them. Unlike the IC testers available in the market today which are usually expensive, this IC tester is affordable and user-friendly. This IC tester is constructed using 8951 microcontroller along with a keyboard and a display unit. It can test digital ICs having a maximum of 24 pins. Since it is programmable, any number of ICs can be tested within the constraint of the memory available. This IC tester can be used to test a wide variety of ICs which includes simple logic gates and also sequential and combinational ICs like flip-flops, counters, shift registers etc. It is portable and easy to use. The block diagram of the programmable digital IC tester is as shown in below. It consists of two 8951 microcontroller ICs, a 24-pin IC socket, a keyboard unit, a display unit and indicators. To test a particular digital IC, one needs to insert the IC into the IC socket and enter the IC number using the keyboard and then press the ENTER key. The IC number gets displayed in the 7-segment display unit. Four LEDs are provided as indicators. If the IC being tested is a logic gate, then each of the 4 indicator LEDs correspond to the 4 gates of the IC. In any other case wherein the inserted IC is not a logic gate, all the 4 LEDs work as a single indicator.

Digital IC Tester

Digital IC Tester Block diagram of Programmable Digital IC Tester:

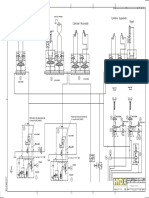

Block diagram Circuit diagram of programmable digital IC tester is shown below.

Circuit diagram The programmable digital IC tester consists of 2 8951 microcontroller. One is called master and the other slave. The master controls the slave and the working of the display and keyboard units. The slave IC is used for testing the IC inserted into the IC socket. Out of the four ports available in the 8951, three ports port 0, port 1(Not all pins), port 2 are connected to the 24 pins of the IC socket. Port 3 is used for parallel communication between the slave and the master. The keyboard and display units are interfaced with the master IC. Four indicators are also connected to the master IC. When we feed the number of the IC being tested, the number gets stored in the memory of the master IC and also gets displayed in the in the 7-segment display. The display unit is connected to the lower pins of port 0 of the master IC. The keyboard is connected to port 1 and the four indicators are connected to the port 1 of Slave IC. Parallel communication is used between the master and the slave. There are four data lines and three control lines for transfer and control of data between the master and the slave. Port 3 of the slave IC and port 2 of the master IC are used for parallel communication.

To test a particular digital IC, one needs to insert the IC into the IC socket and enter the IC number using the keyboard and then press the ENTER key. The IC number gets displayed in the 7-segment display unit. The IC number gets transferred to the slave using parallel communication. The process of parallel communication is as follows: 1. 2. 3. 4. 5. 6. The slave sends a ready bit to the master IC when it is ready to receive data. If the slave is ready, the master places the data on the data lines. A control bit gets set as soon the master transmits the data. The slave checks whether the bit is set, and then receives the data. Another control bit gets set as soon as the slave receives the data. A third control bit gets set whenever the slave is ready to accept another set of data.

As soon as the slave gets the IC number, it compares the IC number with the stored list and then goes to the corresponding service routine. The service routine checks the particular IC. Depending to the IC, it assigns some ports as input ports and some as output ports. It gives the corresponding inputs and checks for the output according to the IC logic. If the output is according to the IC logic, the slave sends the data to the master IC. If the IC is a logic gate, then the data will consist of 4 bits, where each bit corresponds to each gate of the IC. In case the IC is not a logic gate, the data consists of a single bit, which may be a 0 or a 1. Corresponding to these four bits, the master sets or resets the lower port of P3, which is connected to the indicators. Four LEDs are interfaced to the master IC as indicators. If the IC being tested is a logic gate, then each of the 4 indicator LEDs correspond to the 4 gates of the IC. In any other case wherein the inserted IC is not a logic gate, all the 4 LEDs work as a single indicator. Using this IC tester, any digital IC can be tested provided its program is written. For a particular IC, the corresponding program must be written in the slave. The total number of ICs that can be tested using this IC tester, depends on the memory available in the slave. The 8951 microcontroller consists of a 4k ROM, using which around 150 ICs can be tested. To test more number of ICs, a microcontroller with an 8k ROM can be used. The keyboard is provided with a RESET button, which when pressed resets both the microcontrollers and the 4 shift registers. The shift registers require a low pulse to get reset, whereas the microcontrollers require a high pulse to get reset. To synchronize this, a NOT gate is used. Display Unit: The display unit is used to display the IC number. This unit consists of five common anode 7-segment displays, five 7447 ICs(BCD to 7-segment converter) and four 74194 ICs(4-bit bidirectional universal shift register). Here, the shift registers are used in parallel load (parallel in parallel out) mode. These shift registers are used to shift the digits of the IC number. When the first digit is pressed, the

master recognizes it and places it in the lower pins of port 0. These four bits are connected to the input of the first shift register and also to the input of the first 7447 IC. The 7447 is a BCD to 7-segment converter, which converts the four input bits (BCD) to their corresponding 7-segment codes. The outputs of the 7447 are connected to the 7-segment displays. Hence the first digit gets displayed in the right-most 7-segment display. As the next number is typed in, the master gives a clock pulse to the shift registers to shift the data. Then the master places the second digit on the lower pins of port 0. Hence the new digit gets displayed in the right-most 7segment display and the previous digit gets shifted to the left. S0 and S1 of the 74194 IC are connected to +Vcc, to work in parallel mode. P3.4 of the master is connected to the clock pins of all the shift registers. These shift registers require a low to high clock pulse. The RESET button provided in the keyboard resets all the shift registers. The common pins of the 7-segment display are connected to +Vcc. The entire display section is shown in the figure below.

Circuit diagram of Display section Keyboard section: The keyboard section is as shown in the figure below. The keyboard is designed as a matrix and is interfaced to port 1 of the master IC. Here P1.0, P1.1, P1.2 are configured as input ports, and P1.3, P1.4, P1.5, P1.6 are configured as output ports. The keyboard consists of 10 digits as well as an ENTER button.

Circuit diagram of Keyboard section Software program for master IC: setb p2.7 mov r0,#30h mov p1,#0ffh mov r7,#01 start: mov p0,#0 wait: setb p1.3 setb p1.4 setb p1.5 setb p1.6 jb p1.0,key

;Clear first digit ;Keyboard interfacing ;Enable all rows ;Check whether key is pressed

jb p1.1,key jb p1.2,key jmp wait

;If not, check again

key: mov r2,#0a0h d: djnz r2,d mov r1,#01 ;Pressed digit mov r2,#01 nextrow:cjne r2,#01,nextr1 setb p1.6 ;Enable first row clr p1.5 ;Disable other rows clr p1.4 clr p1.3 jmp over nextr1: cjne r2,#02,nextr2 setb p1.5 ;Enable second row clr p1.6 ;Disable other rows clr p1.4 clr p1.3 jmp over nextr2: cjne r2,#03,nextr3 setb p1.4 ;Enable third row clr p1.5 ;Disable other rows clr p1.6 clr p1.3 jmp over nextr3: setb p1.3 clr p1.5 ;Enable fourth row clr p1.4 ;Disable other rows clr p1.6 over: jb p1.0,col1 ;If key is pressed in particular row, check jb p1.1,col2 ; for corresponding column jb p1.2,col3 mov a,#03 add a,r1 mov r1,a inc r2 jmp nextrow col1: jnb p1.0,over jmp done col2: jnb p1.1,over inc r1 jmp done col3: jnb p1.2,over mov a,#02

add a,r1 mov r1,a done: mov a,r1 cjne a,#0bh,enter mov r1,#0 jmp down enter: mov a,r1 cjne a,#0ch,down jmp out down: mov @r0,r1 inc r0 mov a,#01 xrl a,r7 jz noshift clr p3.4 mov r2,#0ffh here: djnz r2,here setb p3.4 noshift: mov r7,#00 mov p0,r1 wait1: jb p1.0,wait1 jb p1.1,wait1 jb p1.2,wait1 mov r2,#0ffh delay2: djnz r2,delay2 wait2: jmp wait out: cjne a,#0ch,wait2 clr p2.4 mov r2,#0ffh here1: djnz r2,here1 setb p2.4 mov a,#0 mov p0,a out1: jb p1.0,out1 jb p1.1,out1 jb p1.2,out1 mov a,r0 subb a,#02 mov r0,a mov a,@r0 swap a mov r5,a inc r0 mov a,@r0

add a,r5 mov r5,a cjne r5,#0,nor mov a,#1 jmp x nor: cjne r5,#02,and mov a,#2 jmp x and: cjne r5,#08,or mov a,#3 jmp x or: cjne r5,#32h,xor mov a,#4 jmp x xor: cjne r5,#86h,else mov a,#5 jmp x else: mov a,#0fh x: mov p2,#00 jnb a.0,nextb1 setb p2.0 nextb1: jnb a.1,nextb2 setb p2.1 nextb2: jnb a.2,nextb3 setb p2.2 nextb3: jnb a.3,ove setb p2.3 ove: clr p2.7 end: jmp end Software program for slave IC: mov p0,#0 mov p2,#0 mov p1,#0 mov r0,#0ffh del: djnz r0,del setb p3.7 wait:jb p3.7,wait mov a,#0 setb p3.0 setb p3.1 setb p3.2 setb p3.3

jnb p3.0,nextb1 setb a.0 nextb1: jnb p3.1,nextb2 setb a.1 nextb2: jnb p3.2,nextb3 setb a.2 nextb3: jnb p3.3,over setb a.3 over:cjne a,#1,next2 call gateic mov a,r3 rl a mov r2,#07h xrl a,r2 jnz checkg12 setb p1.2 checkg12: mov a,r4 rl a mov r2,#07h xrl a,r2 jnz checkg13 setb p1.3 checkg13: mov a,r5 rl a mov r2,#07h xrl a,r2 jnz checkg14 setb p1.4 checkg14: mov a,r5 rl a mov r2,#07h xrl a,r2 jnz end2 setb p1.5 jmp end2 next2: cjne a,#2,next3 call gateic mov a,r3 rl a mov r2,#01h xrl a,r2 ;NOR ;NAND

jnz checkg22 setb p1.2 checkg22: mov a,r4 rl a mov r2,#01h xrl a,r2 jnz checkg23 setb p1.3 checkg23: mov a,r5 rl a mov r2,#01h xrl a,r2 jnz checkg24 setb p1.4 checkg24: mov a,r5 rl a mov r2,#01h xrl a,r2 jnz end1 setb p1.5 end2: jmp end1 next3: cjne a,#3,next4 call gateic mov a,r3 rl a mov r2,#08h xrl a,r2 jnz checkg32 setb p1.2 checkg32: mov a,r4 rl a mov r2,#08h xrl a,r2 jnz checkg33 setb p1.3 checkg33: mov a,r5 rl a mov r2,#08h xrl a,r2 ;AND

jnz checkg34 setb p1.4 checkg34: mov a,r5 rl a mov r2,#08h xrl a,r2 jnz end1 setb p1.5 jmp end1 next4: cjne a,#4,next5 call gateic mov a,r3 rl a mov r2,#0Eh xrl a,r2 jnz checkg2 setb p1.2 checkg2: mov a,r4 rl a mov r2,#0Eh xrl a,r2 jnz checkg3 setb p1.3 checkg3: mov a,r5 rl a mov r2,#0Eh xrl a,r2 jnz checkg4 setb p1.4 checkg4: mov a,r5 rl a mov r2,#0Eh xrl a,r2 jnz end3 setb p1.5 end1: jmp end3 next5: cjne a,#5,end2 call gateic mov a,r3 ;XOR ;OR

rl a mov r2,#06h xrl a,r2 jnz checkg52 setb p1.2 checkg52: mov a,r4 rl a mov r2,#06h xrl a,r2 jnz checkg53 setb p1.3 checkg53: mov a,r5 rl a mov r2,#06h xrl a,r2 jnz checkg54 setb p1.4 checkg54: mov a,r5 rl a mov r2,#06h xrl a,r2 jnz end setb p1.5 end3: jmp end gateic: mov r0,#25h mov a,#24h mov @r0,a inc r0 mov a,#2Dh mov @r0,a inc r0 mov a,#36h mov @r0,a inc r0 mov a,#3Fh mov @r0,a mov r1,#30h mov a,#92h mov @r1,a inc r1 mov a,#B6h mov @r1,a

inc r1 mov a,#DAh mov @r1,a inc r1 mov a,#FEh mov @r1,a mov r0,#25h mov r1,#30h mov r3,#0 mov r4,#0 mov r5,#0 mov r6,#0 mov r7,#4 nextcnd:mov a,@r0 inc r0 mov p0,a mov a,r3 jnb p0.2,g2 setb a.3 g2: rr a mov r3,a mov a,r4 jnb p0.5,g3 setb a.3 g3: rr a mov r4,a mov a,@r1 inc r1 mov p2,a mov a,r5 jnb p2.1,g4 setb a.3 g4: rr a mov r5,a mov a,r6 jnb p2.4,overcnd setb a.3 overcnd:rr a mov r6,a djnz r7,nextcnd ret end: clr p3.6 stop: jmp stop

You might also like

- Ic Tester ReportDocument44 pagesIc Tester Reportamit101192100% (1)

- Digital Ic TesterDocument28 pagesDigital Ic TesterChris ManojNo ratings yet

- ETE Micro ProjectDocument6 pagesETE Micro ProjectParth Sushil InamdarNo ratings yet

- " Build and Test Voltmeter Using PMMC..": Under The Guidance ofDocument10 pages" Build and Test Voltmeter Using PMMC..": Under The Guidance ofOnkar ChavanNo ratings yet

- Group No.18 DTE Microproject SYCODocument14 pagesGroup No.18 DTE Microproject SYCOvighnesh PatilNo ratings yet

- Control System MicroprojectDocument9 pagesControl System Microprojectshubham bhandekarNo ratings yet

- Pavi Internship Report 2 PDFDocument55 pagesPavi Internship Report 2 PDFSuhas Naik100% (1)

- JAVA Micro ProjectDocument13 pagesJAVA Micro ProjectArib Khan100% (1)

- "Digital Technique": Micro Project Work Submitted byDocument9 pages"Digital Technique": Micro Project Work Submitted bysudarshan sonawane50% (2)

- Complete Micro-Project ReportDocument13 pagesComplete Micro-Project Reportkhanirtekaz50% (2)

- A Project Report On: Fractional Horse Power MotorDocument12 pagesA Project Report On: Fractional Horse Power MotorShivraj Dasange75% (4)

- Embedded Design and Development GuideDocument39 pagesEmbedded Design and Development GuideAyushNo ratings yet

- Under Ground Cable Fault Detection Using IOT-1Document22 pagesUnder Ground Cable Fault Detection Using IOT-1Sarath V PradheepNo ratings yet

- Priti Kadam Dte ProjectDocument15 pagesPriti Kadam Dte ProjectAk MarathiNo ratings yet

- Dte Micro Project OriginalDocument14 pagesDte Micro Project Originaljhjh25% (4)

- Free Network Firewall Computer Graphics Project Using OpenGL ReportDocument38 pagesFree Network Firewall Computer Graphics Project Using OpenGL ReportMisba nausheenNo ratings yet

- Assignment For Course-Gad 22034Document13 pagesAssignment For Course-Gad 22034Vishal KesharwaniNo ratings yet

- Comp. Periferals and Hardware Maintenance Diploma MicroprojectDocument14 pagesComp. Periferals and Hardware Maintenance Diploma MicroprojectAmey Pashte96% (23)

- Arduino Nano Propeller LED Analog Clock Syn PDFDocument11 pagesArduino Nano Propeller LED Analog Clock Syn PDFchandan chandu100% (2)

- Eec MicroprojectDocument30 pagesEec MicroprojectANSARI ARHAMA100% (2)

- FET Co Micro Project 2nd SemDocument11 pagesFET Co Micro Project 2nd SemAnujkumar Yadav75% (8)

- Automated Multilevel Car Parking System ProjectDocument21 pagesAutomated Multilevel Car Parking System ProjectOdhieNo ratings yet

- Build a Clap Switch CircuitDocument14 pagesBuild a Clap Switch Circuitheyyou100% (1)

- Final Intrenship ReportDocument32 pagesFinal Intrenship Report046 KISHORE33% (3)

- Eec Micro-ProjectDocument12 pagesEec Micro-ProjectAniket KumavatNo ratings yet

- Ede AssignmentDocument65 pagesEde AssignmentNikhil Gaikwad0% (1)

- BEC Microproject 2021Document14 pagesBEC Microproject 2021194-Abrar Sheikh100% (1)

- CG - Mini Project - ReportDocument37 pagesCG - Mini Project - ReportMeghana100% (1)

- A Digital Clock (Microproject)Document12 pagesA Digital Clock (Microproject)Ganesh GoreNo ratings yet

- MVPS's Rajarshi Shahu Maharaj Polytechnic, Nashik: Department of Information TechnologyDocument20 pagesMVPS's Rajarshi Shahu Maharaj Polytechnic, Nashik: Department of Information TechnologyVaibhav Bhagwat100% (1)

- BEC Micro Project (Report)Document14 pagesBEC Micro Project (Report)roshni60% (5)

- Machine Learning 22618 ETIDocument14 pagesMachine Learning 22618 ETISandip kotkarNo ratings yet

- A Snake Game Using JavascriptDocument18 pagesA Snake Game Using JavascriptPratham BhosaleNo ratings yet

- Internship Report On Embedded System and IoT Technology.Document72 pagesInternship Report On Embedded System and IoT Technology.manish80% (10)

- Stepper Motor ReportDocument13 pagesStepper Motor ReportVolda0% (2)

- Embedded System Training Report on AVR MicrocontrollerDocument48 pagesEmbedded System Training Report on AVR MicrocontrollerAtishay Kumar100% (3)

- Understanding TransformersDocument12 pagesUnderstanding Transformersroshni88% (8)

- Python Mini Report PDFDocument13 pagesPython Mini Report PDFRahul Singh100% (1)

- Two Digit CounterDocument29 pagesTwo Digit Counteruugef67% (3)

- Survey of Different Database SsoftwaresDocument17 pagesSurvey of Different Database Ssoftwareslocal man100% (1)

- DCS Microproject Report Ghodke SurajDocument18 pagesDCS Microproject Report Ghodke SurajSuraj Ghodke0% (1)

- Osy Microproject 29Document15 pagesOsy Microproject 29Rohit GadekarNo ratings yet

- A Micro Project OnDocument12 pagesA Micro Project OnVrushabh HuleNo ratings yet

- Project On Ic TesterDocument14 pagesProject On Ic TesterDebashish PalNo ratings yet

- Micro Project Report On MotherboardDocument15 pagesMicro Project Report On Motherboardabu100% (14)

- Department of Electronic Engineering: "Design of An Arduino Based Radar System"Document8 pagesDepartment of Electronic Engineering: "Design of An Arduino Based Radar System"Meer Zafarullah Noohani0% (1)

- Internet of Things TutorialDocument39 pagesInternet of Things TutorialTAMIRE SANTOSH MOHANNo ratings yet

- DteDocument18 pagesDterushi matre50% (2)

- 22212-2019-Winter-Model-Answer-Paper (Msbte Study Resources)Document22 pages22212-2019-Winter-Model-Answer-Paper (Msbte Study Resources)pravin khadeNo ratings yet

- Powerpoint Presentaion On NodeMCUDocument23 pagesPowerpoint Presentaion On NodeMCUSouvik KunduNo ratings yet

- 2) Annexure - I & Ii - Micro Project ReportDocument15 pages2) Annexure - I & Ii - Micro Project Reportkhanirtekaz100% (1)

- Clock Design in CDocument18 pagesClock Design in Cluseffur luseffur100% (1)

- 3D Bike Simulation OpenGLDocument23 pages3D Bike Simulation OpenGLSyed Asrar asrar0% (2)

- DCC MicroprojectDocument13 pagesDCC Microprojectᴠɪɢʜɴᴇꜱʜ ɴᴀʀᴀᴡᴀᴅᴇ.No ratings yet

- An Integrated Circuit TesterDocument6 pagesAn Integrated Circuit TesterlvrevathiNo ratings yet

- Interfacing Keyboard to 8051 MicrocontrollerDocument10 pagesInterfacing Keyboard to 8051 Microcontrollerrajinikanth100% (1)

- Digital Thermometer Final ReportDocument22 pagesDigital Thermometer Final Reportrayedkhan100% (1)

- Keypad ScanningDocument11 pagesKeypad Scanningrose8051No ratings yet

- NEC 022 External Paper SolutionDocument13 pagesNEC 022 External Paper SolutionSachin PalNo ratings yet

- 7led DiceDocument8 pages7led DiceMthokozisi Jet NgcoboNo ratings yet

- ImpDocument1 pageImpAbhinav ChoudharyNo ratings yet

- All Rights Reserved © Valores Corporativos Softtek S.A. de C.V. 2015.internalDocument65 pagesAll Rights Reserved © Valores Corporativos Softtek S.A. de C.V. 2015.internalAbhinav ChoudharyNo ratings yet

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- CM8870Document9 pagesCM8870Karthik KalyanaramanNo ratings yet

- N M D C LimitedDocument4 pagesN M D C LimitedAbhinav ChoudharyNo ratings yet

- Water TurbineDocument21 pagesWater TurbineAbhinav ChoudharyNo ratings yet

- E1 - Digital Logic GatesDocument5 pagesE1 - Digital Logic GatesNEIL NADANo ratings yet

- Colpitts Oscillator Circuit Design and Working PrincipleDocument3 pagesColpitts Oscillator Circuit Design and Working PrincipleVishal BasugadeNo ratings yet

- KG-UV920R Service ManualDocument38 pagesKG-UV920R Service ManualErik JirikNo ratings yet

- Fan 7621Document17 pagesFan 7621siamak adldoustNo ratings yet

- AC Thevenin's Theorem LabDocument5 pagesAC Thevenin's Theorem Labyasir aliNo ratings yet

- Pink Noise Generator For Audio TestingDocument3 pagesPink Noise Generator For Audio Testingmmd3No ratings yet

- LSU EE 3755 - Fall 2012 - Computer Organization Verilog Notes 4 - Synthesis Under ConstructionDocument20 pagesLSU EE 3755 - Fall 2012 - Computer Organization Verilog Notes 4 - Synthesis Under ConstructionMerupu DebbaNo ratings yet

- Block Diagram of Communication Receiver: DetectorDocument1 pageBlock Diagram of Communication Receiver: DetectorDharang ShahNo ratings yet

- 051796F0.sch-1 - Thu Dec 15 11:09:57 2005Document25 pages051796F0.sch-1 - Thu Dec 15 11:09:57 2005Aconatic tvhomeNo ratings yet

- Dac and Adc Circuits: Topic OutcomeDocument9 pagesDac and Adc Circuits: Topic OutcomeSegfred NavarroNo ratings yet

- Atmel 0037Document1 pageAtmel 0037namerNo ratings yet

- Department of Electrical & Computer Engineering: North South UniversityDocument8 pagesDepartment of Electrical & Computer Engineering: North South UniversityMD Shariful IslamNo ratings yet

- Chapter 6Document46 pagesChapter 6uchihaitachi1394100% (1)

- Wa0000.Document43 pagesWa0000.eanzil696No ratings yet

- Introduction Au TransistorsDocument3 pagesIntroduction Au TransistorsY WNo ratings yet

- Rf205x Calibration User GuideDocument11 pagesRf205x Calibration User GuideFrancisco Javier FritzNo ratings yet

- EEE Job PreparationDocument12 pagesEEE Job Preparationpinare2193No ratings yet

- Ucx52Xa Regulating Pulse Width Modulators: 1 Features 3 DescriptionDocument23 pagesUcx52Xa Regulating Pulse Width Modulators: 1 Features 3 DescriptionAnonymous e3XZzQNo ratings yet

- 15-W Stereo Class-D Audio Power Amplifier: Features ApplicationsDocument21 pages15-W Stereo Class-D Audio Power Amplifier: Features Applicationsvishnu csNo ratings yet

- Calibration of High Voltage Resistor DividersDocument2 pagesCalibration of High Voltage Resistor DividersLina Muñoz CantilloNo ratings yet

- Operational AmplifiersDocument13 pagesOperational Amplifiersabhey1991100% (2)

- NSTU EEE Power Electronics Assignment QuestionsDocument6 pagesNSTU EEE Power Electronics Assignment QuestionsSalma AkterNo ratings yet

- BJT Prob PDFDocument9 pagesBJT Prob PDFharikeshmn09No ratings yet

- CMOS Frequency Synthesizer Technical Data SheetDocument36 pagesCMOS Frequency Synthesizer Technical Data SheetsrikanthvajjalaNo ratings yet

- EC-101 Electrical Sciences Electrical Sciences 3-1-0-8: Course InstructorsDocument13 pagesEC-101 Electrical Sciences Electrical Sciences 3-1-0-8: Course InstructorsMd ArifNo ratings yet

- Digital Lab VIVA QuestionsDocument4 pagesDigital Lab VIVA QuestionsAnirudhan RaviNo ratings yet

- M2017-0061 PB3S-22-26 Manual - Part IIDocument30 pagesM2017-0061 PB3S-22-26 Manual - Part IILe DuNo ratings yet

- C1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN MergedDocument18 pagesC1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN Mergedchini_naniNo ratings yet

- NPN Silicon Epitaxial Planar TransistorDocument5 pagesNPN Silicon Epitaxial Planar TransistorLaZúu DomiciliosNo ratings yet

- 74HC590Document18 pages74HC590Juan José Lopez NietoNo ratings yet

- Chip War: The Quest to Dominate the World's Most Critical TechnologyFrom EverandChip War: The Quest to Dominate the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (227)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002From EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Rating: 5 out of 5 stars5/5 (1)

- Chip War: The Fight for the World's Most Critical TechnologyFrom EverandChip War: The Fight for the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (82)

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102From EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Rating: 5 out of 5 stars5/5 (2)

- Amazon Web Services (AWS) Interview Questions and AnswersFrom EverandAmazon Web Services (AWS) Interview Questions and AnswersRating: 4.5 out of 5 stars4.5/5 (3)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XFrom EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XRating: 3 out of 5 stars3/5 (2)

- Model-based System and Architecture Engineering with the Arcadia MethodFrom EverandModel-based System and Architecture Engineering with the Arcadia MethodNo ratings yet

- Dancing with Qubits: How quantum computing works and how it can change the worldFrom EverandDancing with Qubits: How quantum computing works and how it can change the worldRating: 5 out of 5 stars5/5 (1)

- Creative Selection: Inside Apple's Design Process During the Golden Age of Steve JobsFrom EverandCreative Selection: Inside Apple's Design Process During the Golden Age of Steve JobsRating: 4.5 out of 5 stars4.5/5 (49)

- 2018 (40+) Best Free Apps for Kindle Fire Tablets: +Simple Step-by-Step Guide For New Kindle Fire UsersFrom Everand2018 (40+) Best Free Apps for Kindle Fire Tablets: +Simple Step-by-Step Guide For New Kindle Fire UsersNo ratings yet

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxFrom EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxNo ratings yet

- From Cell Phones to VOIP: The Evolution of Communication Technology - Technology Books | Children's Reference & NonfictionFrom EverandFrom Cell Phones to VOIP: The Evolution of Communication Technology - Technology Books | Children's Reference & NonfictionNo ratings yet

- Electronic Dreams: How 1980s Britain Learned to Love the ComputerFrom EverandElectronic Dreams: How 1980s Britain Learned to Love the ComputerRating: 5 out of 5 stars5/5 (1)

- Cancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionFrom EverandCancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionRating: 5 out of 5 stars5/5 (2)

- The No Bull$#!£ Guide to Building Your Own PC: No Bull GuidesFrom EverandThe No Bull$#!£ Guide to Building Your Own PC: No Bull GuidesNo ratings yet