Professional Documents

Culture Documents

IO Interfacingup

Uploaded by

Paras BaliOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IO Interfacingup

Uploaded by

Paras BaliCopyright:

Available Formats

I/O INTERFACING

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

I/O STRUCTURE OF A TYPICAL

MICROCOMPUTER

There are three major types of data transfer

between the microcomputer and art I/O device.

They are,

Programmed I/O : In programmed I/O the data

transfer is accomplished through an I/O port and

controlled by software.

Interrupt driven I/O : In interrupt driven I/O, the I/O

device will interrupt the processor, and initiate data

transfer.

Direct memory access (DMA) : In DMA, the data

transfer between memory and I/O can be performed

by bypassing the microprocessor.

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

INTERFACING I/O AND

PERIPHERAL DEVICES

1. For data transfer from input device to processor the following

operations are performed.

The input device will load the data to the port.

When the port receives a data, it sends message to the processor to

read the data.

The processor will read the data from the port.

After a data have been read by the processor the input device will

load the next data into the port.

2. For data transfer from processor to output device the following

operations are performed.

The processor will load the data to the port.

The port will send a message to the output device to read the data.

The output device will read the data from the port.

After the data have been read by the output device the processor can

load the next data to the port.

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

There are two types for interfacing I/O devices:

Memory mapped I/O device.

Standard I/O mapped I/O device or isolated I/O mapping.

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

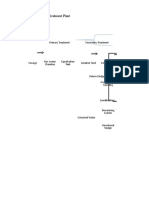

Fig - Memory and I/O Port Interfacing with 8085

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

Example :

A system requires 16kb EPROM and 16kb RAM. Also the system has 2 numbers of 8255, one number of 8279,

one number of 8251 and one number of 8254. (8255 - Programmable peripheral interface; 8279-

Keyboard/display controller, 8251 - USART and 8254 - Timer). Draw the Interface diagram. Allocate

addresses to all the devices. The peripheral IC should be I/O mapped.

The I/O devices in the system should be mapped by standard I/O mapping. Hence separate decoders can be

used to generate chip select signals for memory IC and peripheral IC's.

For 16kb EPROM, we can provide 2 numbers of 2764(8k x 8) EPROM.

For 16kb RAM we can provide 2 numbers of 6264 (8k x 8) RAM.

The 8kb memories require 13 address lines. Hence the address lines A0 - A12 are used for selecting the

memory locations.

The unused address lines A13, A14 and A15 are used as input to decoder 74LS138 (3-to-8-deeoder) of memory

IC. The logic low enables of this decoder are tied to IO/ M(low) of 8085, so that this decoder is enabled for

memory read/write operation. The other enable pins of decoder are tied to appropriate logic levels

permanently. The 4-outputs of the decoder are used to select memory lCs and the remaining 4 are kept for

future expansion.

The EPROM is mapped in the beginning of memory space from 0000H to 3FFF.

The RAM is mapped at the end of memory space from C000 to FFFFH.

There are five peripheral IC's to be interfaced to the system. The chip-select signals for these IC's are given

through another 3-to-8 decoder 74LS138 (I/O decoder). The input to this decoder is A11, A12 and A13

The address lines A13, A14 and A15 are logically ORed and applied to low enable of I/O decoder.

The logic high enable of I/O decoder is tied to IO / M(low) signal of 8085, so that this decoder is enabled for I/O

read/write operation.

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

Fig - Memory and I/O Port Interfacing with 8085

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

Example :

A system requires 8kb EPROM and 8kb RAM. Also the system has 2

numbers of 8155. Draw the Interface diagram. Allocate addresses to

all the devices. The peripheral IC should be I/O mapped.

The IC 2764 (8k x 8) is selected for EPROM memory and IC 6264 (8k x 8)

is selected for RAM memory. Both the memory IC has time

compatibility with 8085 processor.

The 8kb memory requires 13 address lines. Hence the address lines A0 -

A12 are used to select memory locations.

The RAM locations of 8155 are selected by address lines A0 to A7.

3-to-8 decoder, 74LS138 is used for generating chip select signals by

decoding the address lines A13, A14 and A15.

Eight bit addresses are allotted to ports of 8l55 and sixteen bit

addresses are allotted to RAM memory locations of 8155.

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

Fig - Memory and I/O Port Interfacing with 8085

B

h

a

r

a

t

S

a

n

k

h

l

e

c

h

a

You might also like

- Unit Ii Hardware Interfacing With Intel 8085Document44 pagesUnit Ii Hardware Interfacing With Intel 8085Basheer V.PNo ratings yet

- Unit 2 PDFDocument44 pagesUnit 2 PDFprashantvlsiNo ratings yet

- 04 - Generation of Control Signals & Address DecodingDocument20 pages04 - Generation of Control Signals & Address DecodingOFFICIAL BUVAPADA0% (1)

- Interfacing Devices Memory Devices and Interfacing Interfacing DevicesDocument14 pagesInterfacing Devices Memory Devices and Interfacing Interfacing DevicesShilpa ShettyNo ratings yet

- 8085 PDocument31 pages8085 PAnish ChibNo ratings yet

- Experiment No. 1: Department of Electronics & Comm - EnggDocument7 pagesExperiment No. 1: Department of Electronics & Comm - EnggJaspreet KaurNo ratings yet

- Unit 3Document49 pagesUnit 3Durgesh GandiNo ratings yet

- Basic Concepts in Serial I/O Interfacing I/O DevicesDocument33 pagesBasic Concepts in Serial I/O Interfacing I/O DevicessubendNo ratings yet

- 2nd CHAPTER MechatronicsDocument50 pages2nd CHAPTER MechatronicspremscrebdNo ratings yet

- InterfacingDocument9 pagesInterfacingHement SharmaNo ratings yet

- Week 1 - Chapter 04Document30 pagesWeek 1 - Chapter 04Chee Keat LimNo ratings yet

- Semiconductor Memory InterfacingxDocument18 pagesSemiconductor Memory InterfacingxsujathaNo ratings yet

- Unit-3 Instruction CycleDocument9 pagesUnit-3 Instruction CycleBakemono . 5 years agoNo ratings yet

- Peripheral InterfacingDocument32 pagesPeripheral Interfacingsulekha saxenaNo ratings yet

- EE2354 MC 2marks 2013 PDFDocument19 pagesEE2354 MC 2marks 2013 PDFAmy MaggiNo ratings yet

- MicroprocessorDocument7 pagesMicroprocessorSanoxNo ratings yet

- GLA UNIVERSITY Mathura, Uttar Pradesh, IndiaDocument31 pagesGLA UNIVERSITY Mathura, Uttar Pradesh, IndiaANSHY SINGHNo ratings yet

- Unit 3 Notes PDFDocument68 pagesUnit 3 Notes PDFPadmanaban MNo ratings yet

- Interfacing ConceptsDocument17 pagesInterfacing Conceptsanon_61073984100% (1)

- Basic Concepts of Memory Interfacing - ComputerSCDocument7 pagesBasic Concepts of Memory Interfacing - ComputerSCParamartha BanerjeeNo ratings yet

- Unit IDocument22 pagesUnit Iaravinth69601No ratings yet

- 8085 Note-3Document21 pages8085 Note-3Anonymous dxqddDNo ratings yet

- MP8085 2Document38 pagesMP8085 2Ravi TejaNo ratings yet

- Chapter Five PDFDocument34 pagesChapter Five PDFtesfuNo ratings yet

- 8085 Features, Signal DescriptionDocument13 pages8085 Features, Signal DescriptionRakesh Kumar DNo ratings yet

- Microprocessor 8085 ADocument134 pagesMicroprocessor 8085 ASaumya MohanNo ratings yet

- Microprocessors and Microcontrollers Answer KeyDocument14 pagesMicroprocessors and Microcontrollers Answer KeyselvaNo ratings yet

- MP Lab Manual FinalDocument72 pagesMP Lab Manual FinalRavindra KumarNo ratings yet

- of Unit-1: Introduction To Microprocessor and Microprocessor 8085Document22 pagesof Unit-1: Introduction To Microprocessor and Microprocessor 8085abahynNo ratings yet

- Eec 503 PDFDocument22 pagesEec 503 PDFmohitNo ratings yet

- 8085 MicroprocessorDocument38 pages8085 MicroprocessorPrateek PandeyNo ratings yet

- Mpin TDocument55 pagesMpin Tzinabuhaile26No ratings yet

- EE6502 MPMC Two Marks With AnswerDocument10 pagesEE6502 MPMC Two Marks With Answervlsimani9110100% (1)

- CN 320: Microprocessor and Microcontroller SystemsDocument40 pagesCN 320: Microprocessor and Microcontroller SystemsAlango Jr TzNo ratings yet

- Microprocessor and Microcontroller Interview QuestionsDocument25 pagesMicroprocessor and Microcontroller Interview QuestionsDony George Paul67% (15)

- 8085 OperationDocument12 pages8085 OperationMandeep SinghNo ratings yet

- MPMCDocument20 pagesMPMCAnonymous 3XeTp7drNo ratings yet

- Unit-I: 8-Bit MicroprocessorsDocument55 pagesUnit-I: 8-Bit MicroprocessorsAASTHA KIETNo ratings yet

- Assignment1 ContentDocument13 pagesAssignment1 Contentmuhamed21bcs2No ratings yet

- Micro Lecture 4Document47 pagesMicro Lecture 4EnesVSNo ratings yet

- Architecture of 8085 MicroprocessorDocument69 pagesArchitecture of 8085 Microprocessornamrata puranikNo ratings yet

- 8085microproceesor ArchitectureDocument60 pages8085microproceesor ArchitecturePooja Anand JhaNo ratings yet

- Microprocessor 8085Document25 pagesMicroprocessor 8085hetal_limbaniNo ratings yet

- MPDocument34 pagesMPAbhinandan JainNo ratings yet

- 8085 MicroprocessorDocument13 pages8085 MicroprocessorSajid Akram100% (1)

- MCT Unit 2Document26 pagesMCT Unit 2Aravind RajNo ratings yet

- Module 4Document102 pagesModule 4popNo ratings yet

- Microprocessor Lab Manual - FinalDocument47 pagesMicroprocessor Lab Manual - FinalPatel manav PatelNo ratings yet

- 21cs1302-Camp-Unit 5 - NotesDocument27 pages21cs1302-Camp-Unit 5 - Notespec libraryNo ratings yet

- V K Mehta, Rohit Mehta - Principles of Power System (0, Schand Publisching)Document40 pagesV K Mehta, Rohit Mehta - Principles of Power System (0, Schand Publisching)Jaswanth KadaNo ratings yet

- MPD e ContentsDocument112 pagesMPD e Contentsmeera joshiNo ratings yet

- Presentation 1Document23 pagesPresentation 1khushalee.chavadaNo ratings yet

- 3-Ee8551-Microprocessors and MicrocontrollersDocument109 pages3-Ee8551-Microprocessors and MicrocontrollersKeerthana SahadevanNo ratings yet

- Micro Processor QBDocument36 pagesMicro Processor QBNarayanan VenkatNo ratings yet

- Unit II Special Purpose Programmable Peripherals and Their InterfacingDocument10 pagesUnit II Special Purpose Programmable Peripherals and Their InterfacingPraveen RathnamNo ratings yet

- EMISY Second Test Exemplary Questions Solved-3Document15 pagesEMISY Second Test Exemplary Questions Solved-3YANG LIUNo ratings yet

- 2021BCS0002 Assignment 01Document14 pages2021BCS0002 Assignment 01muhamed21bcs2No ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Infiniteskills - Learning Ubuntu Linux (Download Torrent) - TPBDocument2 pagesInfiniteskills - Learning Ubuntu Linux (Download Torrent) - TPBAnuj KansalNo ratings yet

- Technology in Education FinalDocument11 pagesTechnology in Education FinalSaiful IslamNo ratings yet

- 12 Rashis and Their LordsDocument1 page12 Rashis and Their LordsAnonymous Fhs3ufkCNo ratings yet

- 1968 Plymouth Service ManualDocument960 pages1968 Plymouth Service ManualСергей Филиппов100% (1)

- Sound Mind BodyDocument1 pageSound Mind BodyURBNAnthony.com is NOW at No4sale.net Still Urbn Just No4SaleNo ratings yet

- State MachineDocument8 pagesState MachineUriel Cruz MedelNo ratings yet

- Valid Known PacksDocument20 pagesValid Known Packscayson logsdonNo ratings yet

- Natural and Built Environment PDFDocument16 pagesNatural and Built Environment PDFBrylle De GuzmanNo ratings yet

- New CCNP Security v1.1 Release NotesDocument10 pagesNew CCNP Security v1.1 Release NotesشﻻيخNo ratings yet

- Design Sheet STPDocument17 pagesDesign Sheet STPBhagyashree Rath0% (1)

- Propulsion of VLC C 19993990Document7 pagesPropulsion of VLC C 19993990hpss77No ratings yet

- Fuel Filtration Systems: Products and Custom SolutionsDocument28 pagesFuel Filtration Systems: Products and Custom Solutionsphilip connieNo ratings yet

- Fluid and Electrolyte Therapy, Calculation of Fluids and Its AdministrationDocument11 pagesFluid and Electrolyte Therapy, Calculation of Fluids and Its AdministrationAnusha Verghese100% (2)

- Vii & Viii: August 2021Document15 pagesVii & Viii: August 2021rohith mittuNo ratings yet

- Official Enrolment List: Male FemaleDocument20 pagesOfficial Enrolment List: Male FemaleZamZamieNo ratings yet

- Task 1 Sla Interview QuestionsDocument2 pagesTask 1 Sla Interview QuestionsTESL10621 Jihan Syahirah Binti AzliNo ratings yet

- Riph ReviewerDocument16 pagesRiph ReviewerREVECA AVIGAIL JOY SAMINNo ratings yet

- MessageDocument5 pagesMessageธีรพิชญ์ ศรีสมวงศ์No ratings yet

- The Sweet Future of DurianDocument1 pageThe Sweet Future of DuriankakangmasNo ratings yet

- Symbolism in Everyday Life PDFDocument6 pagesSymbolism in Everyday Life PDFIzhar AliNo ratings yet

- Environmental PhysicsDocument63 pagesEnvironmental PhysicsNGOGA NISINGIZWE NESTOR100% (1)

- Power System Analysis Syallbus MG Univ KeralaDocument1 pagePower System Analysis Syallbus MG Univ KeralaChristy CyriacNo ratings yet

- Dynamics of Disease TransmissionDocument30 pagesDynamics of Disease TransmissionSyed Sanan shahNo ratings yet

- Spare Parts List: Hydraulic BreakersDocument24 pagesSpare Parts List: Hydraulic BreakersJean MoralesNo ratings yet

- Marginal CallDocument3 pagesMarginal Calllexredondo22No ratings yet

- Model Solutions: Supplimentary Paper 1 - Set ADocument19 pagesModel Solutions: Supplimentary Paper 1 - Set ACARPE NOCTEMNo ratings yet

- Activity Based CostingDocument30 pagesActivity Based CostingBalakrishna ChakaliNo ratings yet

- Oxy-Fuel Tech & FurnacesDocument22 pagesOxy-Fuel Tech & FurnacesAlirƎza Mhzd100% (1)

- Mechansims of FiltrationDocument21 pagesMechansims of FiltrationNaubeqNo ratings yet

- ART CX310 Active Crossover SMDocument18 pagesART CX310 Active Crossover SMkilol0No ratings yet