Professional Documents

Culture Documents

DM7474 Dual Positive-Edge-Triggered D-Type Flip-Flops With Preset, Clear and Complementary Outputs

DM7474 Dual Positive-Edge-Triggered D-Type Flip-Flops With Preset, Clear and Complementary Outputs

Uploaded by

ann7834Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DM7474 Dual Positive-Edge-Triggered D-Type Flip-Flops With Preset, Clear and Complementary Outputs

DM7474 Dual Positive-Edge-Triggered D-Type Flip-Flops With Preset, Clear and Complementary Outputs

Uploaded by

ann7834Copyright:

Available Formats

2001 Fairchild Semiconductor Corporation DS006526 www.fairchildsemi.

com

September 1986

Revised July 2001

D

M

7

4

7

4

D

u

a

l

P

o

s

i

t

i

v

e

-

E

d

g

e

-

T

r

i

g

g

e

r

e

d

D

-

T

y

p

e

F

l

i

p

-

F

l

o

p

s

w

i

t

h

P

r

e

s

e

t

,

C

l

e

a

r

a

n

d

C

o

m

p

l

e

m

e

n

t

a

r

y

O

u

t

p

u

t

s

DM7474

Dual Positive-Edge-Triggered D-Type Flip-Flops

with Preset, Clear and Complementary Outputs

General Description

This device contains two independent positive-edge-trig-

gered D-type flip-flops with complementary outputs. The

information on the D input is accepted by the flip-flops on

the positive going edge of the clock pulse. The triggering

occurs at a voltage level and is not directly related to the

transition time of the rising edge of the clock. The data on

the D input may be changed while the clock is LOW or

HIGH without affecting the outputs as long as the data

setup and hold times are not violated. A LOW logic level on

the preset or clear inputs will set or reset the outputs

regardless of the logic levels of the other inputs.

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter X to the ordering code.

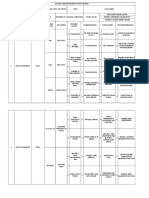

Connection Diagram Function Table

H = HIGH Logic Level

X = Either LOW or HIGH Logic Level

L = LOW Logic Level

= Positive-going transition of the clock.

Q

0

= The output logic level of Q before the indicated input conditions were

established.

Note 1: This configuration is nonstable; that is, it will not persist when either

the preset and/or clear inputs return to their inactive (HIGH) level.

Order Number Package Number Package Description

DM7474M M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow

DM7474N N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Inputs Outputs

PR CLR CLK D Q Q

L H X X H L

H L X X L H

L L X X H

(Note 1)

H

(Note 1)

H H H H L

H H L L H

H H L X Q

0

Q

0

www.fairchildsemi.com 2

D

M

7

4

7

4

Absolute Maximum Ratings(Note 2)

Note 2: The Absolute Maximum Ratings are those values beyond which

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The Recommended Operating Conditions table will define the conditions

for actual device operation.

Recommended Operating Conditions

Note 3: The symbol () indicates the rising edge of the clock pulse is used for reference.

Note 4: T

A

= 25C and V

CC

= 5V.

Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Note 5: All typicals are at V

CC

= 5V, T

A

= 25C.

Note 6: Not more than one output should be shorted at a time.

Note 7: With all outputs open, I

CC

is measured with the Q and Q outputs HIGH in turn. At the time of measurement the clock is grounded.

Note 8: Clear is tested with preset HIGH and preset is tested with clear HIGH.

Supply Voltage 7V

Input Voltage 5.5V

Operating Free Air Temperature Range 0C to +70C

Storage Temperature Range 65C to +150C

Symbol Parameter Min Nom Max Units

V

CC

Supply Voltage 4.75 5 5.25 V

V

IH

HIGH Level Input Voltage 2 V

V

IL

LOW Level Input Voltage 0.8 V

I

OH

HIGH Level Output Current 0.4 mA

I

OL

LOW Level Output Current 16 mA

f

CLK

Clock Frequency (Note 4) 0 15 MHz

t

W

Pulse Width Clock HIGH 30

(Note 4) Clock LOW 37

ns

Clear LOW 30

Preset LOW 30

t

SU

Input Setup Time (Note 3)(Note 4) 20 ns

t

H

Input Hold Time (Note 3)(Note 4) 5 ns

T

A

Free Air Operating Temperature 0 70 C

Symbol Parameter Conditions Min

Typ

Max Units

(Note 5)

V

I

Input Clamp Voltage V

CC

= Min, I

I

= 12 mA 1.5 V

V

OH

HIGH Level V

CC

= Min, I

OH

= Max

2.4 3.4 V

Output Voltage V

IL

= Max, V

IH

= Min

V

OL

LOW Level V

CC

= Min, I

OL

= Max

0.2 0.4 V

Output Voltage V

IH

= Min, V

IL

= Max

I

I

Input Current @ Max Input Voltage V

CC

= Max, V

I

= 5.5V 1 mA

I

IH

HIGH Level V

CC

= Max D 40

Input Current V

I

= 2.4V Clock 80

A

Clear 120

Preset 40

I

IL

LOW Level V

CC

= Max D 1.6

Input Current V

I

= 0.4V Clock 3.2

mA

(Note 8) Clear 3.2

Preset 1.6

I

OS

Short Circuit Output Current V

CC

= Max (Note 6) 18 55 mA

I

CC

Supply Current V

CC

= Max (Note 7) 17 30 mA

3 www.fairchildsemi.com

D

M

7

4

7

4

Switching Characteristics

at V

CC

= 5V and T

A

= 25C

Symbol Parameter

From (Input) R

L

= 400, C

L

= 15 pF

Units

To (Output) Min Max

f

MAX

Maximum Clock

15 MHz

Frequency

t

PHL

Propagation Delay Time Preset to Q

40 ns

HIGH-to-LOW Level Output

t

PLH

Propagation Delay Time Preset to Q

25 ns

LOW-to-HIGH Level Output

t

PHL

Propagation Delay Time Clear to Q

40 ns

HIGH-to-LOW Level Output

t

PLH

Propagation Delay Time Clear to Q

25 ns

LOW-to-HIGH Level Output

t

PHL

Propagation Delay Time Clock to Q or Q

40 ns

HIGH-to-LOW Level Output

t

PLH

Propagation Delay Time Clock to Q or Q

25 ns

LOW-to-HIGH Level Output

www.fairchildsemi.com 4

D

M

7

4

7

4

Physical Dimensions inches (millimeters) unless otherwise noted

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow

Package Number M14A

5 www.fairchildsemi.com

D

M

7

4

7

4

D

u

a

l

P

o

s

i

t

i

v

e

-

E

d

g

e

-

T

r

i

g

g

e

r

e

d

D

-

T

y

p

e

F

l

i

p

-

F

l

o

p

s

w

i

t

h

P

r

e

s

e

t

,

C

l

e

a

r

a

n

d

C

o

m

p

l

e

m

e

n

t

a

r

y

O

u

t

p

u

t

s

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Package Number N14A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and

Fairchild reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be rea-

sonably expected to result in a significant injury to the

user.

2. A critical component in any component of a life support

device or system whose failure to perform can be rea-

sonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- TPM Concept and Literature Review PDFDocument110 pagesTPM Concept and Literature Review PDFheru984100% (4)

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- Workflow PDFDocument17 pagesWorkflow PDFFibrin Yang Uelek'sNo ratings yet

- IMEI OrdersDocument4 pagesIMEI Ordersrynocloud9No ratings yet

- HAZOP FinalDocument2 pagesHAZOP Finalchiang95100% (3)

- Astm F 1249Document3 pagesAstm F 1249deepak100% (1)

- 74LS109Document5 pages74LS109ЭРекиNo ratings yet

- DM7473 Dual Master-Slave J-K Flip-Flops With Clear and Complementary OutputsDocument4 pagesDM7473 Dual Master-Slave J-K Flip-Flops With Clear and Complementary OutputsAbhishek VishwakarmaNo ratings yet

- 74LS73Document5 pages74LS73Cristin BarnesNo ratings yet

- Flip Flop D 74ls74Document13 pagesFlip Flop D 74ls74Kath EmiNo ratings yet

- DM7474 Dual Positive-Edge-Triggered D Flip-Flops With Preset, Clear and Complementary OutputsDocument6 pagesDM7474 Dual Positive-Edge-Triggered D Flip-Flops With Preset, Clear and Complementary OutputsJuan JoachinNo ratings yet

- 74 F 74Document6 pages74 F 74teurgoule76No ratings yet

- Hoja Caracteristicas 7476Document5 pagesHoja Caracteristicas 7476GroplyNo ratings yet

- Hoja Caracteristicas 7476Document5 pagesHoja Caracteristicas 7476Hardian SyaputraNo ratings yet

- DM74LS164 8-Bit Serial In/Parallel Out Shift Register: General Description FeaturesDocument5 pagesDM74LS164 8-Bit Serial In/Parallel Out Shift Register: General Description FeaturesRoby Adi WibowoNo ratings yet

- 74LS393-Dual 4-Bit Binary CounterDocument6 pages74LS393-Dual 4-Bit Binary Counterkakashi116No ratings yet

- DM74164 8-Bit Serial In/Parallel Out Shift Registers: General Description FeaturesDocument5 pagesDM74164 8-Bit Serial In/Parallel Out Shift Registers: General Description FeaturesdeivisroseroNo ratings yet

- DM74LS574 Octal D-Type Flip-Flop With 3-STATE Outputs: General DescriptionDocument6 pagesDM74LS574 Octal D-Type Flip-Flop With 3-STATE Outputs: General DescriptionNicolas Yesenia VictorNo ratings yet

- 74LS574Document6 pages74LS574aminotepNo ratings yet

- 74F74Document7 pages74F74Erick NegreteNo ratings yet

- 74LS374Document8 pages74LS374Bechtel LanutanNo ratings yet

- 74LS86P PDFDocument6 pages74LS86P PDFOsman KoçakNo ratings yet

- DM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputsDocument6 pagesDM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputssoulchordsNo ratings yet

- 74150-Multiplexor 16 EntrDocument4 pages74150-Multiplexor 16 Entrmirchi14No ratings yet

- Mid Semester 2012 TID203Document17 pagesMid Semester 2012 TID203peas002No ratings yet

- 74LS573Document6 pages74LS573Negru P. PlantatieNo ratings yet

- DM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeaturesDocument8 pagesDM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeatureshuvillamilNo ratings yet

- DM74LS136 Quad 2-Input Exclusive-OR Gate With Open-Collector OutputsDocument5 pagesDM74LS136 Quad 2-Input Exclusive-OR Gate With Open-Collector OutputsMarco MenezesNo ratings yet

- sn74138 PDFDocument7 pagessn74138 PDFdujobozinovicNo ratings yet

- DM 74 Ls 90Document6 pagesDM 74 Ls 90Clesio MichaelNo ratings yet

- Datasheet 7420 PDFDocument3 pagesDatasheet 7420 PDFMerce ZumbaNo ratings yet

- 74LS30 DatasheetDocument4 pages74LS30 DatasheetJonathan RoachNo ratings yet

- Dual D-Type Flip-Flop: Integrated CircuitsDocument8 pagesDual D-Type Flip-Flop: Integrated CircuitsRakesh Kumar DNo ratings yet

- DM7490A Decade and Binary Counters: General Description FeaturesDocument6 pagesDM7490A Decade and Binary Counters: General Description FeaturesamrspNo ratings yet

- DM7414 Hex Inverter With Schmitt Trigger Inputs: General DescriptionDocument6 pagesDM7414 Hex Inverter With Schmitt Trigger Inputs: General DescriptionGeorge Rahul PaulNo ratings yet

- 74ACT323 8-Bit Universal Shift/Storage Register With Synchronous Reset and Common I/O PinsDocument7 pages74ACT323 8-Bit Universal Shift/Storage Register With Synchronous Reset and Common I/O PinsPiero SotoNo ratings yet

- C.I 74HC175Document7 pagesC.I 74HC175DOMINGOS ALADIRNo ratings yet

- DM74LS244 Octal 3-STATE Buffer/Line Driver/Line Receiver: General Description FeaturesDocument6 pagesDM74LS244 Octal 3-STATE Buffer/Line Driver/Line Receiver: General Description FeaturesNegru P. PlantatieNo ratings yet

- 74HCT74 PDFDocument7 pages74HCT74 PDFDeni KhanNo ratings yet

- 7408Document3 pages7408Kunal KundanamNo ratings yet

- Octal 3-State Noninverting D Flip-Flop: KK74HC574ADocument6 pagesOctal 3-State Noninverting D Flip-Flop: KK74HC574Ajksb100No ratings yet

- 74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsDocument11 pages74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsRicardo MercadoNo ratings yet

- DM74LS193 Synchronous 4-Bit Binary Counter With Dual Clock: General DescriptionDocument7 pagesDM74LS193 Synchronous 4-Bit Binary Counter With Dual Clock: General DescriptionsabarithasNo ratings yet

- 7Z08Document7 pages7Z08André Frota PaivaNo ratings yet

- CD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionDocument10 pagesCD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionWillianNo ratings yet

- DM74ALS138 3 To 8 Line Decoder/Demultiplexer: General Description FeaturesDocument6 pagesDM74ALS138 3 To 8 Line Decoder/Demultiplexer: General Description FeaturesImran SharieffNo ratings yet

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Document8 pagesMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601No ratings yet

- MM74HC164 8-Bit Serial-in/Parallel-out Shift Register: General DescriptionDocument7 pagesMM74HC164 8-Bit Serial-in/Parallel-out Shift Register: General Descriptionmalirezazadeh5549No ratings yet

- 74138Document6 pages74138Pedro SousaNo ratings yet

- DM74S32 Quad 2-Input OR Gate: General DescriptionDocument3 pagesDM74S32 Quad 2-Input OR Gate: General Description'aldo WaapNo ratings yet

- 74LS164Document5 pages74LS164Byron MendozaNo ratings yet

- HD74LS164: 8-Bit Parallel-Out Serial-In Shift RegisterDocument9 pagesHD74LS164: 8-Bit Parallel-Out Serial-In Shift RegisterRafael GutierrezNo ratings yet

- CD4029BC Presettable Binary/Decade Up/Down CounterDocument10 pagesCD4029BC Presettable Binary/Decade Up/Down CounterIbrahimEssamNo ratings yet

- 74ls193-Contador Binario de 4 BitsDocument8 pages74ls193-Contador Binario de 4 BitsEspartano HernándezNo ratings yet

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- (WWW - Entrance-Exam - Net) - Wipro Sample Paper 2 PDFDocument0 pages(WWW - Entrance-Exam - Net) - Wipro Sample Paper 2 PDFRaffi SkNo ratings yet

- Vlsi Lab DocumentDocument18 pagesVlsi Lab DocumentRaffi SkNo ratings yet

- 4bit ProcessorDocument6 pages4bit ProcessorRaffi SkNo ratings yet

- 2 Design Specification For 4 Bit ProcessorDocument4 pages2 Design Specification For 4 Bit ProcessorAjay G BellamNo ratings yet

- Exercise 6 - Sequential Circuit Design: 60-265 Computer Architecture I: Digital Design Fall 2012Document5 pagesExercise 6 - Sequential Circuit Design: 60-265 Computer Architecture I: Digital Design Fall 2012Raffi SkNo ratings yet

- Written Test Pattern Is Verbal 15 Quetions Quanti. Cum Reasoing 15 Questions Technical 20 QuestionsDocument3 pagesWritten Test Pattern Is Verbal 15 Quetions Quanti. Cum Reasoing 15 Questions Technical 20 QuestionsRaffi SkNo ratings yet

- Chapter 4: Modules and Ports: AnswerDocument2 pagesChapter 4: Modules and Ports: AnswerRaffi SkNo ratings yet

- Assignment6 Solution 3rd EditionDocument10 pagesAssignment6 Solution 3rd EditionRaffi SkNo ratings yet

- Tcs Talent Test 015Document17 pagesTcs Talent Test 015Raffi SkNo ratings yet

- Chapter 6. Dataflow Modeling: 6.7 ExercisesDocument8 pagesChapter 6. Dataflow Modeling: 6.7 ExercisesRaffi SkNo ratings yet

- A Greedy Algorithm For Wire Length OptimizationDocument4 pagesA Greedy Algorithm For Wire Length OptimizationRaffi SkNo ratings yet

- BPSK 2012Document6 pagesBPSK 2012Raffi SkNo ratings yet

- A Fixed-Outline Floorplanning Method Based On 2.5D: Sheqin Dong Qi XieDocument6 pagesA Fixed-Outline Floorplanning Method Based On 2.5D: Sheqin Dong Qi XieRaffi SkNo ratings yet

- Numerically Controlled Oscillator With Spur Reduction: Hans-Jörg Pfleiderer Stefan LachowiczDocument4 pagesNumerically Controlled Oscillator With Spur Reduction: Hans-Jörg Pfleiderer Stefan LachowiczRaffi SkNo ratings yet

- Housekeeping-Reviewer IIDocument3 pagesHousekeeping-Reviewer IITheodiffer TemblorNo ratings yet

- Internship On KSRTC Central Works PappanamcodeDocument64 pagesInternship On KSRTC Central Works Pappanamcodeajay.pNo ratings yet

- 'Pati Bet', Schumannianthus Dichotomus (Roxb.) Gagnep. - A Raw Material For Preparation of Livelihood Supporting HandicraftsDocument6 pages'Pati Bet', Schumannianthus Dichotomus (Roxb.) Gagnep. - A Raw Material For Preparation of Livelihood Supporting HandicraftsBengal TextileNo ratings yet

- Absolute Holdings Circular To Shareholders 17may2010Document206 pagesAbsolute Holdings Circular To Shareholders 17may2010Billy LeeNo ratings yet

- Patty Cake 09 321 Martha Chavez ResumeDocument2 pagesPatty Cake 09 321 Martha Chavez Resumeapi-24664729No ratings yet

- Development Assistant Salary Grade 7 and Also License Inspector Salary 6 Thank You CBA 7 Professional Eligibility Required Some Professional Help Civil Service Exams on March Filing December So Good Luck That IDocument2 pagesDevelopment Assistant Salary Grade 7 and Also License Inspector Salary 6 Thank You CBA 7 Professional Eligibility Required Some Professional Help Civil Service Exams on March Filing December So Good Luck That ICaptain Armer D' LuffyNo ratings yet

- Topic 1 - Power Control DevicesDocument10 pagesTopic 1 - Power Control DevicesRETRO GAMERSNo ratings yet

- Vegetable Planting Calendar For Maricopa County: at A GlanceDocument4 pagesVegetable Planting Calendar For Maricopa County: at A GlancedemanieshsNo ratings yet

- Tech3300 Lesson IdeaDocument2 pagesTech3300 Lesson Ideaapi-652284943No ratings yet

- Hi-Pe High Performance Metal DetectorDocument2 pagesHi-Pe High Performance Metal Detectorhaitem burweenNo ratings yet

- 3 Foot Operated Hydraulic LiftDocument4 pages3 Foot Operated Hydraulic LiftSaravanan ViswakarmaNo ratings yet

- Implementation of EU Directives On Work-Life Balance and On Transparent and Predictable Working ConditionsDocument38 pagesImplementation of EU Directives On Work-Life Balance and On Transparent and Predictable Working ConditionsAdelina Elena OlogeanuNo ratings yet

- Library Management System - System Use Case DiagramDocument24 pagesLibrary Management System - System Use Case Diagramjmadongit4752No ratings yet

- English To Tamil - Google SearchDocument1 pageEnglish To Tamil - Google SearchpreethamshyamNo ratings yet

- Tower Erection - Construction SequenceDocument2 pagesTower Erection - Construction SequenceAmar MistryNo ratings yet

- E-283 (2) Gondi 930K PDFDocument1 pageE-283 (2) Gondi 930K PDFLuis Manuel CastilloNo ratings yet

- Agitador MecanicoDocument1 pageAgitador Mecanicoakarcz6731No ratings yet

- Sanfu 92.5K BC C-0283 SF060138 Final Drawing PDFDocument161 pagesSanfu 92.5K BC C-0283 SF060138 Final Drawing PDFrp100% (1)

- Manual Bristol 33xx Site Considerations For Equipment Installation Grounding Wiring en 133316 PDFDocument38 pagesManual Bristol 33xx Site Considerations For Equipment Installation Grounding Wiring en 133316 PDFemv_prasadNo ratings yet

- Financial Accounting and Analysis - Assignment Dec 2021 - Set 1 GvzfOVqGMUDocument3 pagesFinancial Accounting and Analysis - Assignment Dec 2021 - Set 1 GvzfOVqGMUTanmay KothariNo ratings yet

- Final Work: General Principles, Analytical Review of Financial Statements, Fixed Assets and DebtorsDocument57 pagesFinal Work: General Principles, Analytical Review of Financial Statements, Fixed Assets and DebtorsFani anitaNo ratings yet

- The Bridge, March 20, 2014Document24 pagesThe Bridge, March 20, 2014The BridgeNo ratings yet

- Sicam Toolbox Ii, V5.11 SecurityDocument2 pagesSicam Toolbox Ii, V5.11 SecurityicovinyNo ratings yet

- Topic: Best Out of WasteDocument36 pagesTopic: Best Out of WasteShashank ShettyNo ratings yet

- ISO 4427-5 2007 (E) - Character PDF Document PDFDocument12 pagesISO 4427-5 2007 (E) - Character PDF Document PDFgustavoNo ratings yet