Professional Documents

Culture Documents

Announcements: - Lab 1 Due in One Week

Uploaded by

Mohamed RiasOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Announcements: - Lab 1 Due in One Week

Uploaded by

Mohamed RiasCopyright:

Available Formats

Announcements

Lab 1 due in one week

CSE372

Digital Systems Organization and Design

Lab

Questions/comments?

Testbench coming soon (according to the TAs)

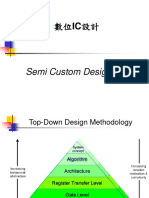

Todays lecture:

How FPGAs work

Prof. Milo Martin

Unit 2: Field Programmable Gate Arrays (FPGAs)

CSE 372 (Martin): FPGAs

Field Programmable Gate Array (FPGA)

CSE 372 (Martin): FPGAs

Early Programmable Logic Device

An alternative to a custom design

A high-end custom design mask set is expensive (millions of $!)

Advantages

Simplicity of gate-level design (no transistor-level design)

Fast time-to-market

No manufacturing delay

Can fix design errors over time (more like software)

Disadvantages

Expensive: unit cost is higher

Inefficient: slower and more power hungry

Result: good for low-volume or initial designs

CSE 372 (Martin): FPGAs

CSE 372 (Martin): FPGAs

From UC-Berkeley CS152 slides

Modern FPGA: Xilinx Vertex II

For Comparison: FGPA vs Pentium 4

Not to scale

CSE 372 (Martin): FPGAs

CSE 372 (Martin): FPGAs

FPGA Design Flow

Review: Logical Completeness

Synthesis

AND, OR, NOT can implement ANY truth table

Break design into well-define logic blocks

Examples:

2-input gates

Only NANDs

Limited set of standard cells with three-inputs, one output

Place and route

Custom: position the devices and wires that connect them

FPGA: configure logic blocks and interconnect

Goals:

Reduce latency (performance)

Reduce area (cost)

Reduce power (performance and/or cost)

CSE 372 (Martin): FPGAs

Cin S

A B Cin

1. AND combinations

that yield a "1" in the

truth table

S

2. OR the results

of the AND gates

Mechanical process, but many optimizations

7

CSE 372 (Martin): FPGAs

Our Old Friend, The Full Adder

Add two bits and carry-in

produce one-bit sum and carry-out

An

Bn

A Better Full Adder

1

1

A B Cin S Cout

CarryInn

1

Add

Sn

!module full_adder(s, cout, a, b, cin);

output s, cout;

input a, b, cin;

CarryInn

xor (t1, a, b);

xor (s, t1, cin);

and (t2, t1, cin);

and (t3, a, b);

or (cout, t2, t3);

endmodule

CarryOutn

0 0

0 0

0 1

0 1

cin

1 0

1 0

a

b

1 1

1 1

An

Bn

Sn

Add

CarryOutn

t1

t2

cout

t3

CSE 372 (Martin): FPGAs

A Simple (Fake) FPGA Substrate

CSE 372 (Martin): FPGAs

10

How Do We Route Signals?

Switch matrix

Each junction has 6 switches

Each switch is a pass gate

Switch

Programming

Each pass gate controlled by 1-bit flip-flop

0/1 value of flip-flop set at configuration

Programmable interconnect

Pass Gate

Allows for arbitrary routing of signals

Each segment adds delay

Takes up lots of chip area

CSE 372 (Martin): FPGAs

11

CSE 372 (Martin): FPGAs

12

More Wires

IBM

IBM

On-Chip Wires

IBM CMOS7, 6 layers of copper wiring

CSE 372 (Martin): FPGAs

13

Configure This As a Full Adder

14

A Better FPGA

Replace gates with general CLB

cin

a

b

Combinational logic block

s

cout

CSE 372 (Martin): FPGAs

CSE 372 (Martin): FPGAs

15

CLB

CLB

CLB

CLB

CLB

CLB

CSE 372 (Martin): FPGAs

16

Combinational Logic Block

A Standard Xilinx CLB

Simple example CLB

Two 4-input LUTs

Any 4-input function

Limited 5-input functions

Configure as any two-input gate

Use 4-bit RAM to implement function

LUT - Lookup Table

Simple lookup operation

Two flip-flops

Fast carry logic (direct connect from adjacent CLBs)

LUTs can be be configured as RAM:

2x16 bit or 1x32 bit, single ported

1x16 bit dual ported

Add sequential state

Add a latch/flipflop or two

Routing

Short and long wires (skip some CLBs)

Clocks have dedicated wires

Also has IOBs (input/output blocks)

Specialized for off-chip signals, one per pin on package

CSE 372 (Martin): FPGAs

17

The Xilinx 4000 CLB

CSE 372 (Martin): FPGAs

CSE 372 (Martin): FPGAs

18

Two 4-input functions, registered output

From UC-Berkeley CS150 slides

19

CSE 372 (Martin): FPGAs

From UC-Berkeley CS150 slides

20

5-input function, combinational output

CSE 372 (Martin): FPGAs

From UC-Berkeley CS150 slides

CLB Used as RAM

21

Fast Carry Logic

CSE 372 (Martin): FPGAs

CSE 372 (Martin): FPGAs

From UC-Berkeley CS150 slides

22

Xilinx 4000 Interconnect

From UC-Berkeley CS150 slides

23

CSE 372 (Martin): FPGAs

From UC-Berkeley CS150 slides

24

Switch Matrix

CSE 372 (Martin): FPGAs

Xilinx 4000 Interconnect Details

From UC-Berkeley CS150 slides

25

CSE 372 (Martin): FPGAs

From UC-Berkeley CS150 slides

FPGA Design Issues

Our FPGAs: Virtex-2 Pro XC2VP30

How large should a CLB be?

Viertex-2 Pro

How many inputs?

How much logic and state?

Example: two full-adders plus two latches in each Xilinx CLB

N-bit counter uses N/2 CLBs

More powerful CLBs

More routing resources

Embedded PowerPC core

XC2VP30

Routing resources

Faster, better routing

Other imbedded hardware structures

RAM blocks

Multipliers

Processors

CSE 372 (Martin): FPGAs

26

27

30,816 CLBs

136 18-bit multipliers

2,448 Kbits of block RAM

Two PowerPC processors

400+ pins

CSE 372 (Martin): FPGAs

28

FPGA vs Custom Designs

FPGA vs Custom Designs

Downside of configurability

Wires are much slower on FPGAs

Logic is much slower on FPGAs

However, FPGAs are real logic (not software)

Great for our prototyping

Synthesis to chip an option ($$$)

Standard cell design

Hard coded, but based on synthesis design flow

Not as good as full custom as used by Intel, AMD, IBM

Not to scale

CSE 372 (Martin): FPGAs

29

CSE 372 (Martin): FPGAs

30

You might also like

- How Does FPGA Work: OutlineDocument17 pagesHow Does FPGA Work: OutlinehariharankalyanNo ratings yet

- Boundary ScanDocument61 pagesBoundary ScanGéza HorváthNo ratings yet

- Eecs150 - Digital Design: Lecture 3 - Field Programmable Gate Arrays (Fpgas)Document23 pagesEecs150 - Digital Design: Lecture 3 - Field Programmable Gate Arrays (Fpgas)mridul_teotiaNo ratings yet

- Implementation Implementation Technology: (PART 2)Document45 pagesImplementation Implementation Technology: (PART 2)katral-jamerson-9379No ratings yet

- Fpga Module PresDocument45 pagesFpga Module PrescatchmereddyNo ratings yet

- Eecs150 - Digital Design: Lecture 6 - Field Programmable Gate Arrays (Fpgas)Document25 pagesEecs150 - Digital Design: Lecture 6 - Field Programmable Gate Arrays (Fpgas)lambajituNo ratings yet

- FPGAsDocument55 pagesFPGAsSerge Mandhev SwamotzNo ratings yet

- Cmos Design MethodsDocument69 pagesCmos Design MethodsPuneet PatilNo ratings yet

- Chapter 1Document27 pagesChapter 1s9222647No ratings yet

- Xilinx XC2C512-10PQ208I - 5G Technology - Industrial ControlDocument5 pagesXilinx XC2C512-10PQ208I - 5G Technology - Industrial ControljackNo ratings yet

- N2X-N2XT Product Presentation May 2011Document35 pagesN2X-N2XT Product Presentation May 2011cnbattsonNo ratings yet

- STADocument123 pagesSTAMoon Sadia DiptheeNo ratings yet

- 001 29 Spartan FPGA ImplementationDocument43 pages001 29 Spartan FPGA ImplementationMuhammadimran AliNo ratings yet

- Chapter 2Document40 pagesChapter 2s9222647No ratings yet

- 1143448609Document23 pages1143448609Qaisar Abbas QasimiNo ratings yet

- Cs295: Modern Systems What Are Fpgas and Why Should You CareDocument22 pagesCs295: Modern Systems What Are Fpgas and Why Should You CareGiovanni OrsariNo ratings yet

- VLSI Interview Questions - FPGA Interview QuestionsDocument8 pagesVLSI Interview Questions - FPGA Interview QuestionsBhyrapaneni LakshmanNo ratings yet

- Debugging Clock Trees Will Now Be Easier: Cadence Cdnlive! 2007 Emea Conference in MunichDocument22 pagesDebugging Clock Trees Will Now Be Easier: Cadence Cdnlive! 2007 Emea Conference in MunichSandeep PatilNo ratings yet

- Unit 7Document54 pagesUnit 7Pavankumar GorpuniNo ratings yet

- ECE 448 - FPGA and ASIC Design With VHDL: George Mason UniversityDocument76 pagesECE 448 - FPGA and ASIC Design With VHDL: George Mason Universityerdvk100% (1)

- A Systolic FFT Architecture For Real Time FPGA SystemsDocument33 pagesA Systolic FFT Architecture For Real Time FPGA SystemshariharankalyanNo ratings yet

- f28m36p53c2 PDFDocument253 pagesf28m36p53c2 PDFGustavo LimaNo ratings yet

- PLD Architectures and TestingDocument37 pagesPLD Architectures and TestingParesh SawantNo ratings yet

- Lecture 11Document32 pagesLecture 11songoku711No ratings yet

- FPGA: What? Why?: Marco D. Santambrogio Marco - Santambrogio@polimi - ItDocument30 pagesFPGA: What? Why?: Marco D. Santambrogio Marco - Santambrogio@polimi - ItravinarsingojuNo ratings yet

- Moore's Law: FPGA-Based System Design: Chapter 1 2004 Prentice Hall PTRDocument32 pagesMoore's Law: FPGA-Based System Design: Chapter 1 2004 Prentice Hall PTRArjun NagNo ratings yet

- Assignment 9Document1 pageAssignment 9Bala Subrahmanyam KNo ratings yet

- VLSI 2 Project ReportDocument36 pagesVLSI 2 Project ReportTabassum RezaNo ratings yet

- Digital Systems Design Using VHDL: Designing With FpgasDocument51 pagesDigital Systems Design Using VHDL: Designing With FpgasPrashant ReddyNo ratings yet

- ARM Based ESD UNIT 5CDocument17 pagesARM Based ESD UNIT 5CManu ManuNo ratings yet

- DEsign and Implementation of PID On FPGADocument6 pagesDEsign and Implementation of PID On FPGAdhirendraNo ratings yet

- Lecture 9Document29 pagesLecture 9Ram MurthyNo ratings yet

- TRADITIONAL Asic Design FlowDocument24 pagesTRADITIONAL Asic Design FlowTarun Prasad100% (1)

- Fundamentals of Digital IC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Document29 pagesFundamentals of Digital IC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Huzur AhmedNo ratings yet

- Traditional Asic DesignflowDocument103 pagesTraditional Asic DesignflowYamini SaraswathiNo ratings yet

- Digital Design and System Implementation Overview of Physical ImplementationsDocument4 pagesDigital Design and System Implementation Overview of Physical ImplementationsGuganesan PerumalNo ratings yet

- Introduction To Programmable Logic: John Coughlan RAL Technology Department Electronics DivisionDocument28 pagesIntroduction To Programmable Logic: John Coughlan RAL Technology Department Electronics DivisionSwati ChavanNo ratings yet

- Debugging Clock Trees Will Now Be Easier: Cadence Cdnlive! 2007 Emea Conference in MunichDocument22 pagesDebugging Clock Trees Will Now Be Easier: Cadence Cdnlive! 2007 Emea Conference in MunichSumanth VarmaNo ratings yet

- CPLD and FpgaDocument28 pagesCPLD and FpgaUday KumarNo ratings yet

- Fpga Based System DesignDocument30 pagesFpga Based System DesignKrishna Kumar100% (1)

- Rabbit - Overview of The Rabbit 4000 Product Line & Dynamic C SoftwareDocument23 pagesRabbit - Overview of The Rabbit 4000 Product Line & Dynamic C SoftwareAmr ElmestekawiNo ratings yet

- An Introduction To Vlsi Processor Architecture For GaasDocument35 pagesAn Introduction To Vlsi Processor Architecture For GaasBibin JohnsonNo ratings yet

- PIC185452 SpecificationsDocument20 pagesPIC185452 SpecificationsSampath Kumar DuraisamyNo ratings yet

- Ece 465 Introduction To Cplds and Fpgas: Shantanu Dutt Ece Dept. University of Illinois at ChicagoDocument11 pagesEce 465 Introduction To Cplds and Fpgas: Shantanu Dutt Ece Dept. University of Illinois at ChicagoMamoon BarbhuyanNo ratings yet

- Programmable ASIC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Document25 pagesProgrammable ASIC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Huzur AhmedNo ratings yet

- Mapping DSP Algorithms Into FpgasDocument35 pagesMapping DSP Algorithms Into FpgasMayam AyoNo ratings yet

- Ece 5017-Digital Design With Fpga Lab: Slot:L31+L32 Instructor: Dr.K.SivasankaranDocument21 pagesEce 5017-Digital Design With Fpga Lab: Slot:L31+L32 Instructor: Dr.K.SivasankaranVibha M VNo ratings yet

- Spartan-II FPGA FamilyDocument99 pagesSpartan-II FPGA FamilyRavindra SainiNo ratings yet

- Ece 5017-Digital Design With Fpga Lab: Slot:L5+L6 /L29+L30/L31+L32/L45+L46Document22 pagesEce 5017-Digital Design With Fpga Lab: Slot:L5+L6 /L29+L30/L31+L32/L45+L46Aakanksha SharmaNo ratings yet

- LaunchPad Ecosystem Selection Guide Slat152bDocument17 pagesLaunchPad Ecosystem Selection Guide Slat152bventsym100% (1)

- PIC Microcontrollers: Peeyush.K.P. Amrita School of Engineering CoimbatoreDocument46 pagesPIC Microcontrollers: Peeyush.K.P. Amrita School of Engineering Coimbatorepeeyushkp100% (1)

- 5.2 CMOS Logic Gate Design: Serial or Parallel in Rs Transisto of NoDocument15 pages5.2 CMOS Logic Gate Design: Serial or Parallel in Rs Transisto of NoRaj AryanNo ratings yet

- TMS320F28004x Real-Time Microcontrollers: 1 FeaturesDocument266 pagesTMS320F28004x Real-Time Microcontrollers: 1 FeaturesAnurag1996No ratings yet

- Spartan 2 e 07Document74 pagesSpartan 2 e 07Huzur AhmedNo ratings yet

- ASIC-System On Chip-VLSI Design - Clock GatingDocument4 pagesASIC-System On Chip-VLSI Design - Clock Gatinguni_saraNo ratings yet

- DFTDocument23 pagesDFTChaitanya VarmaNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- PHP Tutorial PDFDocument128 pagesPHP Tutorial PDFDaniel SapnuNo ratings yet

- Computer Science, MC Graw Hill Book Company, 1997Document1 pageComputer Science, MC Graw Hill Book Company, 1997Mohamed RiasNo ratings yet

- Power Optimization For SRAM and Its ScalingDocument8 pagesPower Optimization For SRAM and Its ScalingMohamed RiasNo ratings yet

- Finfet Sram Optimization With Fin Thickness and Surface OrientationDocument9 pagesFinfet Sram Optimization With Fin Thickness and Surface OrientationMohamed RiasNo ratings yet

- Phpmysql Tutorial EbookDocument27 pagesPhpmysql Tutorial Ebookarupghosh88No ratings yet

- Announcements: - Lab 1 Due in One WeekDocument8 pagesAnnouncements: - Lab 1 Due in One WeekMohamed RiasNo ratings yet

- 02-nfd (1) VLIWDocument11 pages02-nfd (1) VLIWMohamed RiasNo ratings yet

- 02-nfd (1) VLIWDocument11 pages02-nfd (1) VLIWMohamed RiasNo ratings yet

- SCWCD ExamDocument72 pagesSCWCD ExamLcc VuNo ratings yet

- AbstractDocument1 pageAbstractMohamed RiasNo ratings yet

- Tcs 6Document117 pagesTcs 6Mohamed RiasNo ratings yet

- Template - W-8ben FormDocument1 pageTemplate - W-8ben FormFaisal Khan100% (1)

- Lines and Planes in Matlab: Math 50C - Multivariable CalculusDocument18 pagesLines and Planes in Matlab: Math 50C - Multivariable CalculusMohamed RiasNo ratings yet