Professional Documents

Culture Documents

Microprocessor Architecture Computer Architecture: Von Neumann Von Neumann vs. Harvard

Microprocessor Architecture Computer Architecture: Von Neumann Von Neumann vs. Harvard

Uploaded by

Ashish KumarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Microprocessor Architecture Computer Architecture: Von Neumann Von Neumann vs. Harvard

Microprocessor Architecture Computer Architecture: Von Neumann Von Neumann vs. Harvard

Uploaded by

Ashish KumarCopyright:

Available Formats

Computer Architecture

Microprocessor Architecture

in a nutshell

Separation of CPU and memory distinguishes

programmable computer.

CPU fetches instructions from memory.

Registers help out: program counter (PC),

instruction register (IR), general-purpose

registers, etc.

Alternative approaches

Two opposite examples

SHARC

ARM7

Chenyang Lu

CSE 467S

von Neumann

Chenyang Lu

CSE 467S

von Neumann vs. Harvard

von Neumann

Same memory holds data, instructions.

A single set of address/data buses between

CPU and memory

address

memory

200

ADD r5,r1,r3

Chenyang Lu

200

PC

data

Harvard

CPU

Separate memories for data and instructions.

Two sets of address/data buses between

CPU and memory

ADD r5,r1,r3

IR

CSE 467S

Harvard Architecture

program memory

Chenyang Lu

data

CSE 467S

Harvard allows two simultaneous memory

fetches.

Most DSPs use Harvard architecture for

streaming data:

data

address

CSE 467S

von Neumann vs. Harvard

address

data memory

Chenyang Lu

CPU

greater memory bandwidth;

more predictable bandwidth.

IR

PC

Chenyang Lu

CSE 467S

RISC vs. CISC

Microprocessors

Reduced Instruction Set Computer (RISC)

Compact, uniform instructions facilitate pipelining

More lines of code large memory footprint

Allow effective compiler optimization

RISC

ARM7

ARM9

CISC

Pentium

SHARC

(DSP)

von Neumann

Harvard

Complex Instruction Set Computer (CISC)

Many addressing modes and long instructions

High code density

Often require manual optimization of assembly code

for embedded systems

Chenyang Lu

CSE 467S

Digital Signal Processor

= Harvard + CISC

Chenyang Lu

CSE 467S

DSP Optimizations

Streaming data

Need high data throughput

Harvard architecture

Signal processing

Memory footprint

Require high code density

Need CISC instead of RISC

Real-time requirements

Chenyang Lu

CSE 467S

Support floating point operation

Efficient loops (matrix, vector operations)

Ex. Finite Impulse Response (FIR) filters

Execution time must be predictable opportunistic

optimization in general purpose processors may not

work (e.g., caching, branch prediction)

Chenyang Lu

SHARC Architecture

Registers

Modified Harvard architecture.

Register files

10

Data address generator registers.

Loop registers.

Register files connect to:

Two pieces of data can be loaded in parallel

Support for signal processing

multiplier

shifter;

ALU.

Powerful floating point operations

Efficient loop

Parallel instructions

CSE 467S

CSE 467S

40 bit R0-R15 (aliased as F0-F15 for floating point)

Separate data/code memories.

Program memory can be used to store data.

Chenyang Lu

11

Chenyang Lu

CSE 467S

12

Assembly Language

SHARC Assembly

1-to-1 representation of binary instructions

Why do we need to know?

Algebraic notation terminated by semicolon:

R1=DM(M0,I0), R2=PM(M8,I8); ! comment

label: R3=R1+R2;

Performance analysis

Manual optimization of critical code

data memory access

Focus on architecture characteristics

program memory access

NOT specific syntax

Chenyang Lu

CSE 467S

13

Chenyang Lu

Computation

Data Types

Floating point operations

Hardware multiplier

Parallel computation

Chenyang Lu

CSE 467S

15

CSE 467S

32-bit IEEE single-precision floating-point.

40-bit IEEE extended-precision floating-point.

32-bit integers.

48-bit instructions.

Chenyang Lu

CSE 467S

Rounding and Saturation

Parallel Operations

Floating-point can be:

Can issue some computations in parallel:

Rounded toward zero;

Rounded toward nearest.

14

16

dual add-subtract;

multiplication and dual add/subtract

floating-point multiply and ALU operation

ALU supports saturation arithmetic

Overflow results in max value, not rollover.

R6 = R0*R4, R9 = R8 + R12, R10 = R8 - R12;

CLIP Rx within range [-Ry,Ry]

Rn = CLIP Rx by Ry;

Chenyang Lu

CSE 467S

17

Chenyang Lu

CSE 467S

18

Example: Exploit Parallelism

Memory Access

if (a>b) y = c-d; else y = c+d;

Parallel load/store

Circular buffer

Compute both cases, then choose which one to store.

! Load values

R1=DM(_a); R2=DM(_b);

R3=DM(_c); R4=DM(_d);

! Compute both sum and difference

R12 = R2+R4, R0 = R2-R4;

! Choose which one to save

COMP(R1,R2);

IF LE R0 = R12;

DM(_y) = R0 ! Write to y

Chenyang Lu

CSE 467S

19

Chenyang Lu

CSE 467S

Load/Store

Basic Addressing

Load/store architecture

Can use direct addressing

Two set of data address generators (DAGs):

Immediate value:

R0 = DM(0x20000000);

Direct load:

program memory;

data memory.

Can perform two load/store per cycle

R0 = DM(_a); ! Load contents of _a

Direct store:

DM(_a)= R0; ! Stores R0 at _a

Must set up DAG registers to control

loads/stores.

Chenyang Lu

CSE 467S

21

DAG1 Registers

M0

M1

L0

L1

B0

B1

I2

M2

L2

B2

I3

M3

L3

B3

I4

M4

L4

B4

I5

M5

L5

B5

I6

M6

L6

B6

I7

M7

L7

B7

CSE 467S

Chenyang Lu

CSE 467S

22

Post-Modify with Update

I0

I1

Chenyang Lu

20

I register holds base address.

M register/immediate holds modifier value.

R0 = DM(I3,M3) ! Load

DM(I2,1) = R1 ! Store

23

Chenyang Lu

CSE 467S

24

Zero-Overhead Loop

Circular Buffer

L: buffer size

B: buffer base address

I, M in post-modify mode

I is automatically wrapped around the circular

buffer when it reaches B+L

Example: FIR filter

No cost for jumping back to start of loop

Decrement counter, cmp, and jump back

LCNTR=30, DO L UNTIL LCE;

R0=DM(I0,M0), F2=PM(I8,M8);

R1=R0-R15;

F4=F2+F3;

L:

Chenyang Lu

CSE 467S

25

FIR Filter on SHARC

26

PC Stack

! Executed after new sensor data is stored in xnew

R1=DM(_xnew);

! Use post-increment mode

PM(I8,M8)=R1;

! Loop body

LCNTR=4, DO L UNTIL LCE;

! Use post-increment mode

R1=DM(I0,M0), R2=PM(I8,M8);

L: R8=R1*R2, R12=R12+R8;

CSE 467S

CSE 467S

Nested Loop

! Init: Set up circular buffers for x[] and c[].

B8=PM(_x); ! I8 is automatically set to _x

L8=4; ! Buffer size

M8=1; ! Increment of x[]

B0=DM(_c); L0=4; M0=1; ! Set up buffer for c

Chenyang Lu

Chenyang Lu

27

Example: Nested Loop

Loop start address

Return addresses for subroutines

Interrupt service routines

Max depth = 30

Loop Address Stack

Loop end address

Max depth = 6

Loop Counter Stack

Loop counter values

Max depth = 6

Chenyang Lu

CSE 467S

28

SHARC

CISC + Harvard architecture

Computation

S1:

S2:

LCNTR=3, DO LP2 UNTIL LCE;

LCNTR=2, DO LP1 UNTIL LCE;

R1=DM(I0,M0), R2=PM(I8,M8);

LP1: R8=R1*R2;

R12=R12+R8;

LP2: R11=R11+R12;

Floating point operations

Hardware multiplier

Parallel operations

Memory Access

Parallel load/store

Circular buffer

Zero-overhead and nested loop

Chenyang Lu

CSE 467S

29

Chenyang Lu

CSE 467S

30

Microprocessors

ARM7

RISC

ARM7

CISC

Pentium

DSP

(SHARC)

von Neumann

Harvard

von Neumann + RISC

Compact, uniform instruction set

ARM9

32 bit or 12 bit

Usually one instruction/cycle

Poor code density

No parallel operations

Memory access

Chenyang Lu

CSE 467S

No parallel access

No direct addressing

31

Chenyang Lu

CSE 467S

FIR Filter on ARM7

Sample Prices

; loop

MOV

MOV

LDR

MOV

ADR

ADR

ARM7: $14.54

SHARC: $51.46 - $612.74

initiation code

r0, #0 ; use r0 for loop counter

r8, #0 ; use separate index for arrays

r1, #4 ; buffer size

r2, #0 ; use r2 for f

r3, c ; load r3 with base of c[ ]

r5, x ; load r5 with base of x[ ]

32

; loop; instructions for circular buffer are not shown

L: LDR r4, [r3, r8] ; get c[i]

LDR r6, [r5, r8] ; get x[i]

MUL r4, r4, r6 ; compute c[i]x[i]

ADD r2, r2, r4 ; add into sum

ADD r8, r8, #4 ; add one word to array index

ADD r0, r0, #1 ; add 1 to i

CMP r0, r1 ; exit?

BLT L ; if i < 4, continue

Chenyang Lu

CSE 467S

33

Chenyang Lu

CSE 467S

MIPS/FLOPS Metrics

Evaluating DSP Speed

Do not indicate how much work is accomplished

by each instruction.

Implement, manually optimize, and compare complete

application on multiple DSPs

34

Time consuming

Depend on architecture and instruction set.

Benchmarks: a set of small pieces (kernel) of

representative code

Especially unsuitable for DSPs due to the

diversity of architecture and instruction sets.

Ex. FIR filter

Inherent to most embedded systems

Small enough to allow manual optimization on multiple DSPs

Circular buffer load

Zero-overhead loop

Application profile + benchmark testing

Assign relative importance of each kernel

Chenyang Lu

CSE 467S

35

Chenyang Lu

CSE 467S

36

Other Important Metrics

Chenyang Lu

CSE 467S

37

Reading

Chapter 2 (only the sections related to slides)

Optional: J. Eyre and J. Bier, DSP Processors Hit the

Mainstream, IEEE Micro, August 1998.

Optional: More about SHARC

http://www.analog.com/processors/processors/sharc/

Nested loops: Pages (3-37) (3-59)

http://www.analog.com/UploadedFiles/Associated_Docs/476124

543020432798236x_pgr_sequen.pdf

Chenyang Lu

CSE 467S

39

Power consumption

Cost

Code density

Chenyang Lu

CSE 467S

38

You might also like

- Convenience SystemDocument48 pagesConvenience Systemrobika79100% (1)

- Terzija-Koglin2001 Article ANewApproachToArcResistanceCalDocument6 pagesTerzija-Koglin2001 Article ANewApproachToArcResistanceCalAndres Vergara100% (1)

- Manual Jack A4sDocument8 pagesManual Jack A4sIliana IvanovaNo ratings yet

- Aesd QP SolDocument26 pagesAesd QP Sollaxmi shindeNo ratings yet

- Architecture of c5xDocument19 pagesArchitecture of c5xB11 Aswathy SureshNo ratings yet

- Acorn RISC MachineDocument6 pagesAcorn RISC Machinesolomon girmaNo ratings yet

- Module-2: Microcontroller and Embedded SystemsDocument74 pagesModule-2: Microcontroller and Embedded Systemsswethaashok28No ratings yet

- Pic16f FeaturesDocument40 pagesPic16f Featuresveeramaniks408No ratings yet

- DSP Processor FundamentalsDocument58 pagesDSP Processor FundamentalsSayee KrishnaNo ratings yet

- Embedded Lecture 4 ARMDocument47 pagesEmbedded Lecture 4 ARMmsmukeshsinghmsNo ratings yet

- Lecture6 ARMDocument50 pagesLecture6 ARMRohith ThurlapatiNo ratings yet

- CHAPTER 3 - 1 - Ver2-Intro To Assembly Language PDFDocument34 pagesCHAPTER 3 - 1 - Ver2-Intro To Assembly Language PDFWeehao Siow100% (1)

- ARM - Advanced RISC Machines: RISC-Reduce Instruction Set ComputersDocument60 pagesARM - Advanced RISC Machines: RISC-Reduce Instruction Set ComputersPraveen EdulaNo ratings yet

- Lecture 6b: MSP430 Assembly Language Tutorial: MSP430 CPUDocument64 pagesLecture 6b: MSP430 Assembly Language Tutorial: MSP430 CPUSufyan NikaninNo ratings yet

- Unit - IDocument47 pagesUnit - IcjramancjNo ratings yet

- Ss 1Document78 pagesSs 1NithiBoazNo ratings yet

- l18 ArmDocument71 pagesl18 ArmVamsi SomisettyNo ratings yet

- Reduced Instruction Set Computers: William Stallings Computer Organization and Architecture 7 EditionDocument38 pagesReduced Instruction Set Computers: William Stallings Computer Organization and Architecture 7 EditionSaimo FortuneNo ratings yet

- 03 - Instruction Set Architecture DesignDocument38 pages03 - Instruction Set Architecture DesignOscar Carballal DíazNo ratings yet

- SSSCDocument28 pagesSSSCMahesh KoliNo ratings yet

- Week 02Document55 pagesWeek 02aroosa naheedNo ratings yet

- Arm NotesDocument52 pagesArm NotesSanjana GaneshNo ratings yet

- Chapter 2 - Architecture of ARM ProcessorDocument43 pagesChapter 2 - Architecture of ARM Processor方勤No ratings yet

- Advanced Risc MachinersDocument21 pagesAdvanced Risc MachinersAANCHALNo ratings yet

- 04 8051 Instruction SetDocument76 pages04 8051 Instruction SetharinkhedetNo ratings yet

- Digital Signal Processor 3Document25 pagesDigital Signal Processor 3Vijayaraghavan VNo ratings yet

- Architecture of Computers Lab1Document28 pagesArchitecture of Computers Lab1q5nfvkbyyrNo ratings yet

- Unit One NotesDocument92 pagesUnit One NotesbharathimmkNo ratings yet

- Instruction Set Principles and ExamplesDocument77 pagesInstruction Set Principles and Examplesdayat_ridersNo ratings yet

- L1 - Instructions - Intro - Operations - Operands of The ComputerDocument19 pagesL1 - Instructions - Intro - Operations - Operands of The ComputerJaisaiarun P SrinivasanNo ratings yet

- ARM Introduction & Instruction Set ArchitectureDocument71 pagesARM Introduction & Instruction Set Architecturebala100% (1)

- DSP ArchitectureDocument31 pagesDSP Architecturehameedirfan100% (1)

- What Is A Microprocessor?: - Computer's Central Processing Unit (CPU) Built On A SingleDocument74 pagesWhat Is A Microprocessor?: - Computer's Central Processing Unit (CPU) Built On A SingleDarren Sherwin KennyNo ratings yet

- ch4 HandoutsDocument72 pagesch4 HandoutsMarah IrshedatNo ratings yet

- Unit5 - Ch2 COADocument61 pagesUnit5 - Ch2 COAVighnesh SarwankarNo ratings yet

- Lecture1 2Document21 pagesLecture1 2da_oakNo ratings yet

- 8085 Intel MicroprocessorDocument16 pages8085 Intel MicroprocessorMartino Ojwok AjangnayNo ratings yet

- Embedded CDocument48 pagesEmbedded CTejassarwajna Degala100% (2)

- Memory Access Memory Access Modes Modes: Steps in Address MappingDocument12 pagesMemory Access Memory Access Modes Modes: Steps in Address MappingshubhangiNo ratings yet

- MSP 430 (Mixed Signal Processor)Document64 pagesMSP 430 (Mixed Signal Processor)Pradeepdarshan PradeepNo ratings yet

- Week 6Document33 pagesWeek 6aroosa naheedNo ratings yet

- Micro ControllersDocument141 pagesMicro ControllersBiswajit SarkarNo ratings yet

- Assembly Language Lab-1Document6 pagesAssembly Language Lab-1mudassar87No ratings yet

- Micro ControllersDocument31 pagesMicro ControllersMohammad HassanNo ratings yet

- ch2 Arm 1Document37 pagesch2 Arm 1Anonymous 4Ck3aR0No ratings yet

- Mces03 8051alp PDFDocument17 pagesMces03 8051alp PDFIndranilNo ratings yet

- PIC1Document183 pagesPIC1Gokul GocoolNo ratings yet

- 8051 MicrocontrollerDocument32 pages8051 MicrocontrollerRachit Sharma91% (11)

- Week 2Document70 pagesWeek 2abbazh rakhondeNo ratings yet

- 5.dsp UNIT 5 With 8XDocument69 pages5.dsp UNIT 5 With 8XpraveenNo ratings yet

- Architecture of ARM Processor Family: Seminar On Architectures and Design MethodsDocument27 pagesArchitecture of ARM Processor Family: Seminar On Architectures and Design MethodsSree Harsha VemulapalliNo ratings yet

- Thumb InstructionsDocument37 pagesThumb InstructionsSuhas ShirolNo ratings yet

- Basic Computer Organization and DesignDocument46 pagesBasic Computer Organization and DesignKirollos ShawkyNo ratings yet

- Arm 2Document30 pagesArm 2ayush.verma2022No ratings yet

- HCS12Document36 pagesHCS12alzyoud100% (2)

- Topic 3 Processor FunctionDocument52 pagesTopic 3 Processor FunctionTharinda LasithaNo ratings yet

- SJB Institute of Technology: CO & ARM Microcontrollers (21EC52)Document61 pagesSJB Institute of Technology: CO & ARM Microcontrollers (21EC52)rohitrajww4No ratings yet

- Intro To ARM Cortex-M3 (CM3) and LPC17xx MCU: OutlineDocument79 pagesIntro To ARM Cortex-M3 (CM3) and LPC17xx MCU: OutlinesupriyaNo ratings yet

- TMS320LF2407Document90 pagesTMS320LF2407Polumuri RamanaNo ratings yet

- Co Unit 2.1Document45 pagesCo Unit 2.1Prasanth ReddyNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- William Stallings Computer Organization and Architecture 6 EditionDocument52 pagesWilliam Stallings Computer Organization and Architecture 6 EditionRahmat RafliNo ratings yet

- RS 15 SpecDocument2 pagesRS 15 SpecChowKC03No ratings yet

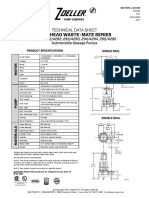

- High Head Waste-Mate Series: Technical Data SheetDocument2 pagesHigh Head Waste-Mate Series: Technical Data SheetEuribiades CordobaNo ratings yet

- SummaryDocument2 pagesSummaryFayed GamalNo ratings yet

- Ele804 Lab Manual LnaDocument58 pagesEle804 Lab Manual Lnaanhnhamoi100% (1)

- Design and Analysis of A Novel Brushless Wound Rotor Synchronous MachineDocument4 pagesDesign and Analysis of A Novel Brushless Wound Rotor Synchronous MachineHuong ThaoNo ratings yet

- TUNNEL DIODE (Esaki Diode)Document11 pagesTUNNEL DIODE (Esaki Diode)Altaf KudaratiNo ratings yet

- Acer Aspire 4320 4720 4720G 4720Z - QUANTA ZO1 - REV 1ASecDocument25 pagesAcer Aspire 4320 4720 4720G 4720Z - QUANTA ZO1 - REV 1ASecBudi Ono100% (1)

- APart Audio CatalogueDocument82 pagesAPart Audio CataloguevsvNo ratings yet

- Titus Sound Acoustics PresentationDocument63 pagesTitus Sound Acoustics PresentationNdia2007No ratings yet

- Samsung Chassis Ks1a cz21h12t SCHDocument107 pagesSamsung Chassis Ks1a cz21h12t SCHTara TaraNo ratings yet

- Literature Review of Automatic Voltage RegulatorDocument6 pagesLiterature Review of Automatic Voltage Regulatoraflskeqjr100% (1)

- F7U5-Megatester V3 Software 3.2Document13 pagesF7U5-Megatester V3 Software 3.2kittisak RunganothaiNo ratings yet

- PresentationDocument15 pagesPresentationT XombiNo ratings yet

- Redrawing Curva Capability GridDocument9 pagesRedrawing Curva Capability GridarekimbaNo ratings yet

- Textbook Audio Production Principles Practical Studio Applications 1St Edition Stephane Elmosnino Ebook All Chapter PDFDocument53 pagesTextbook Audio Production Principles Practical Studio Applications 1St Edition Stephane Elmosnino Ebook All Chapter PDFjames.byers710100% (17)

- Standard Electro-Magnetic Locks (Grade 3) : Product Data Sheet Ds15-009Document2 pagesStandard Electro-Magnetic Locks (Grade 3) : Product Data Sheet Ds15-009AlviNo ratings yet

- And 20240116 Log of System Maintenance at UIDocument4 pagesAnd 20240116 Log of System Maintenance at UIajengsepuhNo ratings yet

- Feasibility Study For Small Scaling Flywheel-Energy-Storage Systems in Energy Harvesting SystemsDocument9 pagesFeasibility Study For Small Scaling Flywheel-Energy-Storage Systems in Energy Harvesting SystemsshawnleegabrielNo ratings yet

- WM8731 PDFDocument64 pagesWM8731 PDFRAMON JARAMILLO MARTINEZNo ratings yet

- DEC50113-Chapter 1 - 6 Display DevicesDocument52 pagesDEC50113-Chapter 1 - 6 Display DevicesFaiz ZakariaNo ratings yet

- 4F Series (NAMUR) Series Specifications・How to Order・Dimensions (0.4MB)Document6 pages4F Series (NAMUR) Series Specifications・How to Order・Dimensions (0.4MB)FREDY PAT 019889335555No ratings yet

- S7-1500 ModbusRTU PROJ v21 enDocument39 pagesS7-1500 ModbusRTU PROJ v21 enManju Nath100% (1)

- Capacity Dimensioning of HSDPA Urban NetworkDocument14 pagesCapacity Dimensioning of HSDPA Urban NetworkNino BongoyNo ratings yet

- ITA2 User ManualDocument93 pagesITA2 User ManualHosni Ben KhimissaNo ratings yet

- Jinko Solar 400WcDocument2 pagesJinko Solar 400WcGaddour TriguiNo ratings yet

- Burkert Type 8056 Electromagnetic Flowmeter Full Bore Sanitary Version 1Document9 pagesBurkert Type 8056 Electromagnetic Flowmeter Full Bore Sanitary Version 1Carlos Enrique De Gumucio VargasNo ratings yet