Professional Documents

Culture Documents

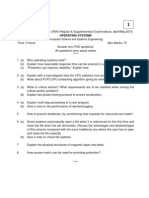

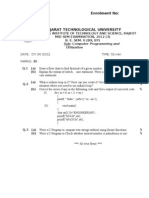

Answer All Questions: Sub. Title: Date Sub. Code: CS2253 Branch: Cse & It Time Max. Marks: 50

Uploaded by

BIBIN CHIDAMBARANATHANOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Answer All Questions: Sub. Title: Date Sub. Code: CS2253 Branch: Cse & It Time Max. Marks: 50

Uploaded by

BIBIN CHIDAMBARANATHANCopyright:

Available Formats

R.M.K.

COLLEGE OF ENGINEERING AND TECHNOLOGY

R.S.M NAGAR, PUDUVOYAL-601206

4th Semester B.E. / B.Tech.

Second Internal Assessment Test March 2013

Sub. Title : COMPUTER ORGANIZATION AND ARCHITECTURE

Sub. Code : CS2253

Time

: 100 minutes

Date

: 02.03.2013

Branch

: CSE & IT

Max. Marks: 50

Answer all questions

Part A - (5 x 2 = 10)

1. What are the relative merits of horizontal and vertical microinstruction format?

2. In what ways the width and height of the control memory be reduced?

3. A=5;

A 3 + A

B4xA

What hazard does the above two instructions create when executed concurrently?

4. How can memory access be made faster in a pipelined operation? Which hazard can be reduced by

faster memory access?

5. List the key aspects in gaining the performance in pipelined systems.

Part B - (2 x 16 + 1 x 8 = 40)

6. a. (i) Briefly describe the design of a hardwired control unit.

(ii) Draw and explain the block diagram of a complete processor.

(8)

(8)

Or

b. Explain the basic organization of a micro programmed control unit and the generation of

control signals using micro program.

(16)

7. a. i) Discuss the role of cache in pipelining.

(8)

ii) Discuss about the pipeline performance considerations.

(8)

Or

b. Discuss the techniques for handling data and instruction hazards in pipelining. (16)

8. a. Discuss the influence of pipelining on instruction set design.

(8)

Or

b. Write a brief note on nano programming.

(8)

You might also like

- Answer All QuestionsDocument1 pageAnswer All QuestionsBIBIN CHIDAMBARANATHANNo ratings yet

- Answer All QuestionsDocument1 pageAnswer All QuestionsBIBIN CHIDAMBARANATHANNo ratings yet

- Visvodaya Engineering College Mid-1 Question Bank for Computer OrganizationDocument3 pagesVisvodaya Engineering College Mid-1 Question Bank for Computer OrganizationMᴀɴɪ TᴇᴊᴀNo ratings yet

- Answer All QuestionsDocument1 pageAnswer All QuestionsBIBIN CHIDAMBARANATHANNo ratings yet

- Part A: (Answer All The Questions) (7 2 14)Document1 pagePart A: (Answer All The Questions) (7 2 14)Selvanathan RathinamNo ratings yet

- R.M.K. College of Engineering and Technology R.S.M NAGAR, PUDUVOYAL-601206Document1 pageR.M.K. College of Engineering and Technology R.S.M NAGAR, PUDUVOYAL-601206BIBIN CHIDAMBARANATHANNo ratings yet

- CIT309 April 2019Document1 pageCIT309 April 2019Igbani VictoryNo ratings yet

- Answer All Questions: Sub. Title: Date: 28.02.2013 Sub. Code: IT2251 Branch: IT Time Max. Marks: 50Document1 pageAnswer All Questions: Sub. Title: Date: 28.02.2013 Sub. Code: IT2251 Branch: IT Time Max. Marks: 50BIBIN CHIDAMBARANATHANNo ratings yet

- C R Engineering College Computer Organization and Architecture Important QuestionsDocument1 pageC R Engineering College Computer Organization and Architecture Important Questionsr_nirmalNo ratings yet

- Answer All QuestionsDocument1 pageAnswer All QuestionsBIBIN CHIDAMBARANATHANNo ratings yet

- PTU B.tech CSE 5th Sem SyllabusDocument84 pagesPTU B.tech CSE 5th Sem SyllabusJasmine SinghNo ratings yet

- DBMS T1 1Document2 pagesDBMS T1 1ushaalagiri_mca_No ratings yet

- Eit062 Unix Internals Qust PaperDocument1 pageEit062 Unix Internals Qust Papersaravanasai10No ratings yet

- DITS 2213 Final Exam OSDocument6 pagesDITS 2213 Final Exam OSAmirul FaizNo ratings yet

- 4 ECE EC2255 - Control SystemsDocument2 pages4 ECE EC2255 - Control SystemsBIBIN CHIDAMBARANATHANNo ratings yet

- Narasus'S Sarathy Institute of Technology, Salem Internal Test - I (Common To ECE/EEE/IT)Document2 pagesNarasus'S Sarathy Institute of Technology, Salem Internal Test - I (Common To ECE/EEE/IT)Dhivya DuraisamyNo ratings yet

- CA3-QUESTION FORMAT (DDBMS)Document2 pagesCA3-QUESTION FORMAT (DDBMS)subhasis mitraNo ratings yet

- Mechatronics Design 1 Mid Term Exam 2010-2011 PDFDocument2 pagesMechatronics Design 1 Mid Term Exam 2010-2011 PDFseraj sersawiNo ratings yet

- 9A05704 Advanced Computer ArchitectureDocument4 pages9A05704 Advanced Computer ArchitecturesivabharathamurthyNo ratings yet

- Embedded Internal 1 - 2 - Sets IV ECE CDocument2 pagesEmbedded Internal 1 - 2 - Sets IV ECE CjubairNo ratings yet

- 4364 529 Embedded SystemDocument2 pages4364 529 Embedded Systemyogesh_b_kNo ratings yet

- Charya Nstitute OF Echnology: D C S & EDocument5 pagesCharya Nstitute OF Echnology: D C S & EnandanvraghuNo ratings yet

- Mid 1Document2 pagesMid 1anilstaffNo ratings yet

- Vaigai College of Engineering: Therkutheru, Melur (TK), Madurai - 625122Document4 pagesVaigai College of Engineering: Therkutheru, Melur (TK), Madurai - 625122Rajesh LingamNo ratings yet

- Sns College of Technology: Reg NoDocument1 pageSns College of Technology: Reg NoAnonymous JnvCyu85No ratings yet

- CS9223 - ADVANCED SYSTEM SOFTWARE Question Paper - Anna UniversityDocument2 pagesCS9223 - ADVANCED SYSTEM SOFTWARE Question Paper - Anna UniversityNithya Preya SreetharanNo ratings yet

- JNTU M.Tech Precision Engineering Previous Year Question PapersDocument5 pagesJNTU M.Tech Precision Engineering Previous Year Question Paperssimalaravi100% (1)

- Svs College of Engineering: COIMBATORE - 642 109Document1 pageSvs College of Engineering: COIMBATORE - 642 109logu87No ratings yet

- Answer All QuestionsDocument1 pageAnswer All QuestionsBIBIN CHIDAMBARANATHANNo ratings yet

- Answer All Questions: 4 Semester - B.E. / B.Tech Second Internal Assesment Test - March 2013Document2 pagesAnswer All Questions: 4 Semester - B.E. / B.Tech Second Internal Assesment Test - March 2013BIBIN CHIDAMBARANATHANNo ratings yet

- JNTU M.Tech Exam PC Instrumentation QuestionsDocument1 pageJNTU M.Tech Exam PC Instrumentation QuestionsBharath ThatipamulaNo ratings yet

- Answer All Questions: 4 Semester - B.E. / B.Tech First Internal Assessment: 31-01-2013 100 MinutesDocument1 pageAnswer All Questions: 4 Semester - B.E. / B.Tech First Internal Assessment: 31-01-2013 100 MinutesBIBIN CHIDAMBARANATHANNo ratings yet

- WT Internal 1Document1 pageWT Internal 1prkshjsNo ratings yet

- Series 1 EE8691 EMBEDDED SYSTEMSDocument1 pageSeries 1 EE8691 EMBEDDED SYSTEMSMARIA MCETNo ratings yet

- ABET - Design Project Summary Form SampleDocument9 pagesABET - Design Project Summary Form SampleMuthukumaran ChandrasekaranNo ratings yet

- SODCDocument1 pageSODCpravin2275767No ratings yet

- 9A10701 Automation of Industrial ProcessesDocument4 pages9A10701 Automation of Industrial ProcessessivabharathamurthyNo ratings yet

- Capp Unit-IDocument1 pageCapp Unit-IdsakfhNo ratings yet

- PictureDocument1 pagePictureHemalatha AnandhanNo ratings yet

- Embedded Internal QuestionDocument1 pageEmbedded Internal QuestionKumar PraveenkumarNo ratings yet

- Mechatronics Design 1 Second Mid Term Exam 2010-2011Document2 pagesMechatronics Design 1 Second Mid Term Exam 2010-2011seraj sersawi100% (1)

- Thapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Document4 pagesThapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Forza HorizonNo ratings yet

- Department of Informatics: Kakatiya University, Warangal Mca Course Structure & SyllabusDocument58 pagesDepartment of Informatics: Kakatiya University, Warangal Mca Course Structure & SyllabusBapuji ValabojuNo ratings yet

- 6.ims 28 06 2014 Elective IvDocument2 pages6.ims 28 06 2014 Elective IvMech Royal VivekNo ratings yet

- 3 MDM Curriculum AsOn 04nov2011Document25 pages3 MDM Curriculum AsOn 04nov2011Vamsi KrishnaNo ratings yet

- 9A15401 Operating SystemsDocument4 pages9A15401 Operating SystemssivabharathamurthyNo ratings yet

- Full Answer Final ExamDocument6 pagesFull Answer Final ExamNor Faridah YahyaNo ratings yet

- University of Ghana Computer Science Exam Designs 4-Bit CPU Logic CircuitsDocument3 pagesUniversity of Ghana Computer Science Exam Designs 4-Bit CPU Logic CircuitsPhilip Pearce-PearsonNo ratings yet

- Cse Mid 2Document3 pagesCse Mid 2Satya Narayana AravapalliNo ratings yet

- ES Internal2 2014Document1 pageES Internal2 2014lnisarahmedNo ratings yet

- CIM PrefinalDocument2 pagesCIM PrefinalM.ThirunavukkarasuNo ratings yet

- Unit-Iii: M.Tech. Degree Examination Electronic InstrumentationDocument2 pagesUnit-Iii: M.Tech. Degree Examination Electronic InstrumentationSrinath BonakurthiNo ratings yet

- Karaikudi Institute of Technology: Year/Dept: Ii/Cse Date: 07.08.2014 Time:09:20 A.M. - 11:00 A.MDocument2 pagesKaraikudi Institute of Technology: Year/Dept: Ii/Cse Date: 07.08.2014 Time:09:20 A.M. - 11:00 A.Mrathiramsha7No ratings yet

- AKTU MTech Exam Grid Integration of DGDocument2 pagesAKTU MTech Exam Grid Integration of DGjibipmathewNo ratings yet

- CT006-3-0-ICAN - UCFF2017CT - ICAN Group AssignmentDocument5 pagesCT006-3-0-ICAN - UCFF2017CT - ICAN Group AssignmentSDMNo ratings yet

- IA 2 VlsidtDocument2 pagesIA 2 VlsidtAnonymous JnvCyu85No ratings yet

- 19ecb231 - Computer Organization & ArchitectureDocument2 pages19ecb231 - Computer Organization & ArchitectureAsha Pavani KNo ratings yet

- 2nd Sem Cpu Paper - BX, byDocument1 page2nd Sem Cpu Paper - BX, byJayesh RathodNo ratings yet

- ME 8391 Engineering Thermodynamics Workbook - UNIT 1Document154 pagesME 8391 Engineering Thermodynamics Workbook - UNIT 1BIBIN CHIDAMBARANATHANNo ratings yet

- Me6301 Engineering Thermodynamics - Uq - Nov Dec 2015Document3 pagesMe6301 Engineering Thermodynamics - Uq - Nov Dec 2015BIBIN CHIDAMBARANATHANNo ratings yet

- Me2202 Engineering Thermodynamics - Uq - Nov Dec 2015Document3 pagesMe2202 Engineering Thermodynamics - Uq - Nov Dec 2015BIBIN CHIDAMBARANATHANNo ratings yet

- Me6016 Advanced I.C Engines - Unit - 1Document60 pagesMe6016 Advanced I.C Engines - Unit - 1BIBIN CHIDAMBARANATHAN75% (4)

- RMK ENGINEERING THERMODYNAMICS UNIT TESTDocument2 pagesRMK ENGINEERING THERMODYNAMICS UNIT TESTBIBIN CHIDAMBARANATHANNo ratings yet

- Me2202 Engineering Thermodynamics - Uq - May June 2012Document4 pagesMe2202 Engineering Thermodynamics - Uq - May June 2012BIBIN CHIDAMBARANATHAN100% (1)

- Me6301 Engineering Thermodynamics - Uq - April May 2015Document3 pagesMe6301 Engineering Thermodynamics - Uq - April May 2015BIBIN CHIDAMBARANATHANNo ratings yet

- Me6301 Engineering Thermodynamics Nov Dec 2011Document3 pagesMe6301 Engineering Thermodynamics Nov Dec 2011BIBIN CHIDAMBARANATHANNo ratings yet

- Me2202 Engineering Thermodynamics - Uq - Nov Dec 2014Document3 pagesMe2202 Engineering Thermodynamics - Uq - Nov Dec 2014BIBIN CHIDAMBARANATHANNo ratings yet

- Me2202 Engineering Thermodynamics - Uq - Nov Dec 2012Document4 pagesMe2202 Engineering Thermodynamics - Uq - Nov Dec 2012BIBIN CHIDAMBARANATHANNo ratings yet

- Me2202 Engineering Thermodynamics - Uq - Nov Dec 2010Document4 pagesMe2202 Engineering Thermodynamics - Uq - Nov Dec 2010BIBIN CHIDAMBARANATHANNo ratings yet

- Me2202 Engineering Thermodynamics - Uq - Nov Dec 2011Document3 pagesMe2202 Engineering Thermodynamics - Uq - Nov Dec 2011BIBIN CHIDAMBARANATHAN100% (1)

- Me6301 Engineering Thermodynamics - Uq - Nov Dec 2014Document3 pagesMe6301 Engineering Thermodynamics - Uq - Nov Dec 2014BIBIN CHIDAMBARANATHANNo ratings yet

- Me6301 Engineering Thermodynamics - Uq - May June 2016Document4 pagesMe6301 Engineering Thermodynamics - Uq - May June 2016BIBIN CHIDAMBARANATHANNo ratings yet

- Me6301 Engineering Thermodynamics May June 2013Document3 pagesMe6301 Engineering Thermodynamics May June 2013BIBIN CHIDAMBARANATHANNo ratings yet

- Me2202 Engineering Thermodynamics - Uq - May June 2014Document4 pagesMe2202 Engineering Thermodynamics - Uq - May June 2014BIBIN CHIDAMBARANATHANNo ratings yet

- Me6301 Engineering Thermodynamics Nov Dec 2013Document2 pagesMe6301 Engineering Thermodynamics Nov Dec 2013BIBIN CHIDAMBARANATHANNo ratings yet

- Me2202 Engineering Thermodynamics - Uq - May June 2016Document4 pagesMe2202 Engineering Thermodynamics - Uq - May June 2016BIBIN CHIDAMBARANATHANNo ratings yet

- Engineering Thermodynamics (Nov, Dec2008) R2004Document4 pagesEngineering Thermodynamics (Nov, Dec2008) R2004Vijaya Prabhu KumarasamyNo ratings yet

- ME 2202 - ENGINEERING THERMODYNAMICS Mech 3rrdDocument5 pagesME 2202 - ENGINEERING THERMODYNAMICS Mech 3rrddharmaraj_meapNo ratings yet

- Me2202 Engineering Thermodynamics - Uq - April May 2010Document4 pagesMe2202 Engineering Thermodynamics - Uq - April May 2010BIBIN CHIDAMBARANATHANNo ratings yet

- Me6301 Engineering Thermodynamics May June 2011Document3 pagesMe6301 Engineering Thermodynamics May June 2011BIBIN CHIDAMBARANATHANNo ratings yet

- Engineering Thermodynamics (Nov, Dec2009) R2004Document4 pagesEngineering Thermodynamics (Nov, Dec2009) R2004Siva2sankarNo ratings yet

- Me6301 Engineering Thermodynamics Nov Dec 2007Document3 pagesMe6301 Engineering Thermodynamics Nov Dec 2007BIBIN CHIDAMBARANATHANNo ratings yet

- Engineering Thermodynamics (May2009)Document3 pagesEngineering Thermodynamics (May2009)Siva2sankarNo ratings yet

- Me2202 Engineering Thermodynamics - Uq - April May 2015Document3 pagesMe2202 Engineering Thermodynamics - Uq - April May 2015BIBIN CHIDAMBARANATHANNo ratings yet

- Me6301 Engineering Thermodynamics May June 2011Document3 pagesMe6301 Engineering Thermodynamics May June 2011BIBIN CHIDAMBARANATHANNo ratings yet

- Me6301 Engineering Thermodynamics Nov Dec 2006Document3 pagesMe6301 Engineering Thermodynamics Nov Dec 2006BIBIN CHIDAMBARANATHANNo ratings yet

- Me1201 Engineering Thermodynamics - Uq - May June 2012Document3 pagesMe1201 Engineering Thermodynamics - Uq - May June 2012BIBIN CHIDAMBARANATHANNo ratings yet

- Engineering Thermodynamics Question Paper Maj June 2007Document4 pagesEngineering Thermodynamics Question Paper Maj June 2007Anirudhan RaviNo ratings yet