Professional Documents

Culture Documents

VLSI Design Process and Unit Processes

Uploaded by

Venkata SatishOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VLSI Design Process and Unit Processes

Uploaded by

Venkata SatishCopyright:

Available Formats

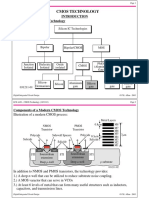

ECE DEPARTMENT

VLSI DESIGN

Prepared By R.V.V R.V.V. Krishna Associate Professor ECE Dept & N.Venkata N.Venkata Satish Sr.Asst Professor ECE Dept

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

MooresLaw In 1965, Gordon Moore noted that the number of transistors on a chip doubled every 18 to 24 months. He made a prediction that semiconductor technology will double its effectiveness every 18 months

Note: To form the depletion mode devices it is only necessary to introduce a masked ion implantation step between steps indicated by an arrow in the above figure.

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

N-well CMOS fabrication

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

Note: For P-well CMOS technology, follow same the process steps as we have discussed in N-well CMOS.

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

NOTE: Students are advised to use these symbols instead of colors for indicating the layers.

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

Twin Tub Processes

Twin-tub CMOS technology provides the basis for separate optimization of the p-type and n-type transistors.One can optimize independently for threshold voltage, body effect, and the gain associated with n- and p-devices. The major steps in the twin tub technology shown below, whereas for intermediate steps (formation of nmos S/D regions and pmos S/D regions as usual) follow the procedures as we have discussed.

Comparison between CMOS and BIPOLAR technologies

CMOS technology Low static power consumption High input impedance High Noise margin High packing density High Delay sensitivity to load Low output drive current Low gm (gm vin) Bidirectional Capability Bipolar Technology High power consumption Low input impedance Low voltage swing logic Low packing density Low delay sensitivity to load High output drive current High gm (gm ) Essential unidirectional

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

BICMOS Fabrication in an N-well process

It is the merging of both CMOS and bipolar technology Its a CMOS based process flow ie core process flow. Here a high performance bipolar device (npn BJT) is incorporated in the CMOS core process flow. In this we are trying to enhance the performance of both CMOS and bipolar device while we incorporating bipolar junction transistor (n-p-n) in CMOS process flow.

Main Steps in BICMOS technology 1. 2. 3. 4. In order to reduce the latch up problem in cmos circuits, simply start with p on p+ substrate Creation of n-well, one for housing p-mos device and another n-well (serves as ncollector) is for bipolar junction transistor ie n-p-n. this step is common. P base (low concentration) doping. This is an extra step To cut down the base resistance as it is doped with low concentration, P+ base contact is formed. We can process this step together with p+ source and drain regions for PMOS device. N+ emitter region formation: This step is in common with the diffusion of n+ source/drain regions for NMOS device which is fabricated on the same p on p+ substrate.

5.

6.

7.

Finally this structure is not going to be a high performance transistor as the n-well collector is doped with low concentration. The resistance of this n-well collector region is about 2k ohm per square cm. The solution to reduce the resistance is to use N+ BURIED LAYER. The use of N+ buried layer (under n-well) not only increases the performance of npn Bipolar junction transistor and also increases the performance of CMOS transistor by reducing the latchup problems (shown in fig below).

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

UNIT PROCESSES

OXIDATION ION IMPLANTATION DIFFUSION LITHOGRAPHY DEPOSITION ETCHING CONTACT PROCESSING METALLIZATION OXIDATION Silicon dioxide is the most important component of VLSI technology Used for gate oxides, isolation oxides, masking, inter-metal dielectrics etc. Thin Oxides Are Used As Gate Oxides Thick oxides are used for isolation and masking Traditionally oxides have been grown through thermal oxidation ( wet and dry) As gate oxides become very thin (< 100 ) the growth processes as well as the dielectric strength become critical issues. o Deposited oxides or alloys of oxides or high dielectric constant materials become choices. o Natural oxide: silicon will readily grow an oxide (5-10nm) if exposed to oxygen in the air! o The range for useful oxide thickness: 25nm (MOS gates) - 1500nm (field oxide) Wet Oxidation (water vapor or steam) Si + H2O SiO2 + 2H2 (900-1200C) 700nm oxide: 0.65hours (1200C) Poor oxide quality: field oxide Dry Oxidation Si + O2 SiO2 (900-1200C) 700nm oxide: 10hours (1200C) Good oxide quality: gate oxide o o o o o o

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

LOCOS During etching, anything irregular becomes more irregular. So we grow oxide fields 50% above and 50% below the wafer. This is called LOCAL Oxidation of silicon. 0.45 mU of silicon, when oxidized, becomes 1mU of sio2 because of change in density. When field oxides are grown, there is an encroachment of the oxide layer in the active transistor region below the gate oxide, because of the affinity of the sio2 gate oxide for oxygen. The resulting structure resembles a birdbeak. This affects the device performance. If we use Si3N4 as the gate dielectric, it will not let oxygen pass through. But due to mismatch of the thermal coefficients of Si and Si3N4, hence the resulting stress produces a non-planar structure called birds crest. The thermal coefficients of Si and Si02 match. So when Si3N4 is used as the gate dielectric, we first grow a thin oxide layer underneath. The stress which would otherwise be generated on the account of the difference in the thermal coefficients of Si and Sio2 is now reduced. Since Sio2 is now there, birds beak will be formed

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

10

Kinetics of Thermal Oxidation Deal-Grove Model The Deal Grove model mathematically describes the growth of an oxide layer on the surface of a material. In particular, it is used to analyze thermal oxidation of silicon in semiconductor device fabrication. The model was first published in 1965 by Bruce Deal and Andrew Grove, of Fair Child Corporation. The model assumes that oxidation occurs at the interface between the oxide and the substrate, rather than between the oxide and the ambient gas. Thus, it considers three phenomena that the oxidizing species undergoes, in this order as shown in fig below.

1. 2. 3.

It diffuses from the bulk of the ambient gas to the surface It diffuses through the existing oxide layer to the oxide- substrate interface It reacts with the substrate.

The oxide thickness grown on the silicon by the process of dry or wet oxidation is dependent on the oxidation time and temperature. This thickness can be expressed as a linear-parabolic relation d2+Ad= B (t+) d= oxide thickness A and B are coefficients that depend on the oxidation time and temperature t=Oxidation time = parameter for fitting the initial value of the oxide thickness For short duration of time, d<<A then above equation is approximated as d=b/a(t+ ) The equation says that when oxidation is carried out for short duration of time, the oxide thickness increases linearly with time. The oxidation in this regime is limited by surface reaction rate and is characterized by linear rate constant (B/A). For longer duration of oxidation (t+ ) >>(A2/4B), the oxide thickness can be expressed as d= In this regime, the oxidation rate is governed by diffusion of the oxidizing agent through the already existing oxide layer and is characterized by parabolic rate constant (B).

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

11

DEPOSITION POLY SILICON GATE Doped poly silicon which provides self aligned gate structures has a good work function matching with the substrate and allows subsequent high temperature processing. This has been the choice as the gate electrode for a very long time. Poly silicon and oxide layers are deposited through cvd processes. ayers Implant doped poly ( n+ n channel side and p+ on p channel side capped with silicides is the present gate electrode. Basic CVD processing: a gas containing an atom(s) of the material to be deposited reacts with another gas liberating the reacts desired material the freed material (atom or molecular form) deposits on the substrate the unwanted products of the chemical reaction leave the reaction chamber Ex.: CVD of silicon from silicon tetrachloride

Why Polysilicon preferred over aluminium as gate material? n 1. Penetration of silicon substrate: If aluminium is deposited as gate, we cant increase the substrate: temperature beyond 500 degree celcius due to the fact that aluminium will then start penetrating the silicon substrate and act as p p-type impurity. Problem with non-self alignment: In case of aluminum gate, we have to first creat source self alignment: and drain and then gate implant. We cant do the reverse because diffusion is a high temperature process. And this creates parasitic overlap input capacitances Cgd and Cgs. Cgd is more harmful because it is a feedback capacitance and hence it is reflected on the input magnified by (k+1) times (recall miller theorem) where k is the gain. So if aluminium is used, theorem), re the input capacitance i citance increase unnecessarily which further increases the charging time of input capacitance. Therefore output doesnt appear immediately. If polysilicon is used instesd, it is possible to first create gate and then source & drain implant, which eliminate the problem of overlap capacitances Cgd and Cgs. Resistivity of poly-silicon is silicon ohm/cm. So we need do dope poly-silicon so that it resembles silicon a metal like Al and its resistance is reduced to 100 or 300 ohm (although its still grater than Al)

2.

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

12

Self-aligned Silicon Gate technology When the metal is used as the gate material, then the source and drain are deposited before the gate and thus to align the gate, mask aligners are used and errors in aligning takes place. In case of polysilicon gate process, the exposed gate oxide(not covered by polysilicon) is etched away and the wafer is subjected to dopant-souce or ion-implant which causes sourcedrain deposition and also these are formed in the regions not coverd by polysilicon and thus souce and drain do not extend under the gate. This is called self-aligning process.

Channel Stopper Implant As we know million of transistors are fabricated on a single chip. To separate (insulate) from each-other, we grow thick oxides (called field oxides). So at very high voltages, inversion may set in the region below the field oxide also, despite the large thickness of these oxides. To avoid this problem, we do an implant in this region before growing the field oxide layer so that threshold voltage for this region is much greater than that for the desired active transistor channel region. This implant layer is called channel stopper implant.

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

13

Photolithography

Photolithography is the process of transferring geometric shapes on a mask to the surface of a silicon wafer. The steps involved in the photolithographic process are wafer cleaning; barrier layer formation; photoresist application; soft baking; mask alignment; exposure and development; and hard-baking. 1. Wafer Cleaning, Barrier Formation and Photoresist Application In the first step, the wafers are chemically cleaned to remove particulate matter on the surface as well as any traces of organic, ionic, and metallic impurities. After cleaning, silicon dioxide, which serves as a barrier layer, is deposited on the surface of the wafer. After the formation of the SiO2 layer, photoresist is applied to the surface of the wafer. High-speed centrifugal whirling of silicon wafers is the standard method for applying photoresist coatings in IC manufacturing. This technique, known as "Spin Coating," produces a thin uniform layer of photoresist on the wafer surface.

2. Positive and Negative Photoresist There are two types of photoresist: positive and negative. For positive resists, the resist is exposed with UV light wherever the underlying material is to be removed. In these resists, exposure to the UV light changes the chemical structure of the resist so that it becomes more soluble in the developer. The exposed resist is then washed away by the developer solution, leaving windows of the bare underlying material. In other words, "whatever shows, goes." The mask, therefore, contains an exact copy of the pattern which is to remain on the wafer. Negative resists behave in just the opposite manner. Exposure to the UV light causes the negative resist to become polymerized, and more difficult to dissolve. Therefore, the negative resist remains on the surface wherever it is exposed, and the developer solution removes only the unexposed portions. Masks used for negative photoresists, therefore, contain the inverse (or photographic "negative") of the pattern to be transferred. The figure below shows the pattern differences generated from the use of positive and negative resist.

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

14

Negative resists were popular in the early history of integrated circuit processing, but positive resist gradually became more widely used since they offer better process controllability for small geometry features. Positive resists are now the dominant type of resist used in VLSI fabrication processes. 3. Soft-Baking Soft-baking is the step during which almost all of the solvents are removed from the photoresist coating. Soft-baking plays a very critical role in photo-imaging. The photoresist coatings become photosensitive, or imageable, only after softbaking. Oversoft-baking will degrade the photosensitivity of resists by either reducing the developer solubility or actually destroying a portion of the sensitizer. Undersoft-baking will prevent light from reaching the sensitizer. Positive resists are incompletely exposed if considerable solvent remains in the coating. This undersoft-baked positive resists is then readily attacked by the developer in both exposed and unexposed areas, causing less etching resistance. 4. Mask Alignment and Exposure One of the most important steps in the photolithography process is mask alignment. A mask or "photomask" is a square glass plate with a patterned emulsion of metal film on one side. The mask is aligned with the wafer, so that the pattern can be transferred onto the wafer surface. Each mask after the first one must be aligned to the previous pattern.

Once the mask has been accurately aligned with the pattern on the wafer's surface, the photoresist is exposed through the pattern on the mask with a high intensity ultraviolet light. There are three primary exposure methods: contact, proximity, and projection. They are shown in the figure below.

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

15

Contact Printing In contact printing, the resist-coated silicon wafer is brought into physical contact with the glass photomask. The wafer is held on a vacuum chuck, and the whole assembly rises until the wafer and mask contact each other. The photoresist is exposed with UV light while the wafer is in contact position with the mask. Because of the contact between the resist and mask, very high resolution is possible in contact printing (e.g. 1-micron features in 0.5 microns of positive resist). The problem with contact printing is that debris, trapped between the resist and the mask, can damage the mask and cause defects in the pattern. Proximity Printing The proximity exposure method is similar to contact printing except that a small gap, 10 to 25 microns wide, is maintained between the wafer and the mask during exposure. This gap minimizes (but may not eliminate) mask damage. Approximately 2- to 4-micron resolution is possible with proximity printing. Projection Printing Projection printing, avoids mask damage entirely. An image of the patterns on the mask is projected onto the resist-coated wafer, which is many centimeters away. In order to achieve high resolution, only a small portion of the mask is imaged. This small image field is scanned or stepped over the surface of the wafer. Projection printers that step the mask image over the wafer surface are called step-and-repeat systems. Step-and-repeat projection printers are capable of approximately 1-micron resolution. 5. Development One of the last steps in the photolithographic process is development.

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

16

The figure below shows response curves for negative and positive resist after exposure and development.

At low-exposure energies, the negative resist remains completely soluble in the developer solution. As the exposure is increased above a threshold energy Et, more of the resist film remains after development. At exposures two or three times the threshold energy, very little of the resist film is dissolved. For positive resists, the resist solubility in its developer is finite even at zero-exposure energy. The solubility gradually increases until, at some threshold, it becomes completely soluble. These curves are affected by all the resist processing variables: initial resist thickness, prebake conditions, developer chemistry, developing time, and others. 6. Hard-Baking Hard-baking is the final step in the photolithographic process. This step is necessary in order to harden the photoresist and improve adhesion of the photoresist to the wafer surface. Purpose of Hard Bake o Evaporating all solvents in PR o Improving etch and implantation resistance o Improve PR adhesion with surface o Polymerize and stabilize photoresist o PR flow to fill pinhole

Lithographic Techniques

1. 2. 3. 4. 5. Optical lithography Non- Optical lithography Electron lithography Ion lithography X-ray lithography

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

17

X-ray lithography

Similar to proximity printer Difficult to find pure X-ray source Challenge on mask making Unlikely will be used in production

Electron lithography

Used for making mask and reticles Smallest geometry achieved: 0.014 mm Direct print possible, no mask is required E-Beam Lithography Advantages The resolution is not limited by diffraction, Minimum feature is written on the nanoscale Can write smaller features than X-ray Lithography, Photolithography. Pattern is written directly to the wafer E-Beam Lithography Disadvantages Not an efficient process for industrial processing Takes multiple hours to pattern an entire wafer Machines are Costly, Greater than 4 million dollars System is more complex than Photolithography System Results in minimum feature being larger

Electron Beam Lithography System

Electron Gun Lens Blanking Plate Lens

Stigmator

Deflection Coils

Lens Wafer

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

18

Beam blanking Blanking, or turning the beam on and off, is usually accomplished with a pair of plates set up as a simple electrostatic deflector. Stigmator A stigmator is a special type of lens used to compensate for imperfections in the construction and alignment of the EBL column. These imperfections can result in astigmatism, where the beam focuses in different directions at different lens settings; the shape of a nominally round beam becomes oblong, with the direction of the principal axis dependent on the focus setting, resulting in smeared images in the resist. The stigmator cancels out the effect of astigmatism, forcing the beam back into its optimum shape. Deflection coils These are used to focus the beam perpendicular to the silicon wafer. Types of Scanning in Electron lithography Raster vs. Vector Scan Raster scan. A scanning technique where the beam scans line by line a section of the surface. The beam is turned on or off depending on whether the current pixel is to be exposed or not. The chip is divided into stripes of ~28 pixels The selected strip is written onto the substrate The beam scans over the substrate line by line If the current pixel is to be exposed, the beam is on If the current pixel is not to be exposed, the beam is off The substrate is moved perpendicular to the scan lines by a laser-controlled table Vector scan. A scanning technique where the beam is positioned over an area of the substrate, and the features in that area (according to the pattern data) are drawn out using lines. The beam remains on at all times. An area of an individual die is aligned under the electron beam The beam is deflected so as to draw out the features in that area of the chip The chip is completed either by a step-and-repeat method, or by continually moving the substrate The alignment of features in adjacent scanning area is important. A measure of misalignment is the butting error, i.e. a measure of the misalignment between adjacent scan areas. Ion-Beam lithography Ion-beam lithography can achieve higher resolution than optical, X-ray and electron beam lithography because ions have higher mass and therefore scatter less than electrons. By analogy to electron beam lithography, focused ion-beam lithography scans an ion beam across a surface to form a pattern. The ion beam may be used or directly sputtering the surface, or may induce chemical reactions in the exposed top layer.These are two types of ion-beam lithography systemsscanning focused beam systems and mask beam system.The former system is similar to beam lithography in which the ion source can be Ga+ or H+.The latter system is similar to an optical 5

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

19

reduction projection step and repeat system which projects 100 keV light ions such as H +2 through a stencil mask.Most important application is the repair of masks for optical lithography.

Etching

Etching is the process of removal of substrate from the unmasked regions so that the desired pattern is transferred on to it. Etching is generally done after lithography. Etching is of two types Wet etching Dry etching

Wet chemical etching It is used extensively in semiconductor processing. Chemical etchants are used for lapping and polishing an optically flat, damage free surface. The mechanism of wet chemical etching involves three essential steps (1)reactance are transported by diffusion to the reacting surface (2)chemical reaction occur near the surface (3)products from the surface are removed by diffusion.wet etching can occur isotropic ally and anisotropic ally. Silicon etching Wet chemical etching proceeds by oxidation followed by dissolution of oxide by a chemical reaction. For silicon, the most commonly used etchants are mixtures of nitric acid and hydrofluoric acid in water or acetic acid. Si+4HNO3SiO2+2H2O+4NO2 Hydrofluoric acid ids used to dissolve the sio2 layer. The reaction is Sio2+6HFH2SiF6+2H2O Water can dissolve the product acetic acid is used as it reduces dissolution of nitric acid. Silicon dioxide is etched in diluted HF solution. The etch rate of silicon dioxide solution etchant concentration, agitation, temperature.

Dry etching In this type of etching no wet chemicals are used instead plasma etching. Plasma is ionized gas composed of equal number of positive and negative charges and a different number of unionized molecules. It is produced when electric filed is applied to a gas, causing gas to break down and become ionized. The process is initiated by free electrons that gain kinetic energy from electric filed, collide with gas molecules, and lose energy. The energy transferred causes the gas molecules to be ionized (i.e...to free electrons). Free electrons gain kinetic energy from the field, and the process continues. Plasma etching involves chemical reaction combined with physical ion bombardment. Other names: Ion milling, sputter etching, Reactive ion etching (RIE), Reactive ion beam etching. Oxygen plasma is generally used for dry etching in semiconductor device fabrication. Dry etching has less etch selectively than wet etching. The process involves Etchant species generated in plasma. Reactant transported by diffusion to surface

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

20

Reactant adsorbed on the surface Chemical reaction (along with ion bombardment) forms volatile compounds Compounds desorbed from surface, diffused into the bulk gas, and pumped out by vacuum system

DOPING AND IMPURITIES In order to fabricate semiconductor devices,a controlled amount of impurities has to be introduced(doped) selectively into the single crystal wafers.There are three basic methods used for controlled doping of a semiconductor. They are Epitaxy Diffusion Ion implantation

EPITAXY

The term epitaxy literally means arranged upon.In this process, a thin layer of single crystal semiconductor(typically a few nanometers to a few microns) is grown on alreadt existing crystalline substrate such that the grown film has same lattice structure as lattice structure as the substrate. There are basically two types of epitaxy: (a) Homo Epitaxy -in which the same material as that of substrate is grown,example is growing Si on silicon substrate (b) Hetero Epitaxy-in which a different layer is grown over the substrate. Example is growing AIGaAS on GaAS. In this type the material grown also there should be lattice match between the substrate and the grown material so that crystal doesnt have strain. Thermal coefficient of expansion of both materials should match. Epitaxy is further classified into Vapour-phase epitaxy(VPE) Liquid-phase epitaxy(LPE) Molecular beam epitaxy(MBE) Vapour-Phase Epitaxy Silicon is most commonly grown from silicon tetrachloride in hydrogen at approximately 1200C SiCl4(g)+2H2(g) ------> Si(s) +4HCl(g) The reation is reversible, and the growth rate depends strongly upon the propartion of the two source gases. Growth rates above 2 micrometers per minute produce polycrystalline silicon, and negative growth rates (etching) may occur if too much hydrogen chloride by product is present.

Liquid-phase Epitaxy Liquid-pahse epitaxy (LPE) is a method to grow semiconducor crystal layers from the melt on solid substartes. This happens at temeratures will below the melting ppoint of the deposited semiconducor. The semiconducor is dissolved in the melt of another material. At conditions that are close to the equilibrium between dissolution and deposition: the deposition of the semiconducor crystal on the substrate is slow and uniform. This method is mainly used for the growth of compound semiconducors. Very thin, uniform and high quality layers can be produced.

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

21

A typical example for the liquid-phase epitaxy is the growth of ternary and quaternery III-IV compound on gallium arsenide (GaAs) substrates. As a solvent quite often gallium is used in this case. Molecular Beam Epitaxy In MBE, a source material is heated to produce an evaporated beam of particles. These particles travel through a very high vaccum to the substrate, where they condense. MBE has lower throughput than other forms of epitaxy. An epitaxial layer can be doped during deposition by adding impurities to the source gas, such as arsine, phosphine or diborane. The concentration of impurity in the gas phase determines its concentration in the deposited film.

Diffusion

Although it is possible to grow a layer with controlled doping by epiatxy, it is not possible to control the doping of selected regions of the semiconductor surface. In other words epitaxial growth takes place throughout the surface that is, it is non selective.In order to achieve selective doping, the technique most commonly used in silicon processing is called as diffision. The basic principle underlying this process is that the dopant atoms migrate from a region of high concentration to the region of low concentration. In simple, diffusion is the process of introducing controlled amounts of dopants into the semiconductors. For example, the selected source and drain regions of MOSFET are doped by diffusion. The unwanted regions of diffsion are covered by the masking material(example: Photoresist) while others are left unprotected. Now if the semiconductor is held in an ambience of high dopant concentration and temperature is raised, dopant atoms migrate move out of their regular lattice sites. Three kinds of situations arise in the process of the diffusion. Substitutional diffusion Interstitial diffusion Interstitialcy diffusion Substitutional diffusion: An impurity atom wanders through the crystal by jumping from one lattice site to the next, thus substituting for the original host atom. However, it is necessary that this adjacent site be vacant, ie ., vacancies must be present to allow substituional diffusion to occur. Note: Due to high temperature, silicon atoms get removed from its lattice position in the crystal and the impurity atom takes place.

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

22

Interstitial diffusion: An impurity atom moves through the crystal lattice by jumping one interstitial site to the next. Interstitial diffusion requires that jump motion occurring from one interstitial site to another adjacent interstitial state. This process is relatively fast, because of large number of vacant interstitial place in the semiconductor crystal.

Interstitial-substitutional diffusion: In this case, impurity atoms occupy substitutional as well as interstitial sites. However, they only move only at a significant rate when in interstitial sites (by interstitial diffusion). The dissociative mechanism, by which a substitutional impurity atom can become an interstitial, leaving behind a vacancy, can be the controlling factor for this process as a result, the effective diffusivity is a function of the disassociation rate and depends on both impurity concentration and crystal quality. An alternative pathway for interstitial diffusion is the kick-out mechanism. Here a rapid moving interstitial diffusion can move into a substitutional site by displacing an atom, which is already in place resulting in the formation of a self-interstitial.

Interstitialcy diffusion: This is modified version of substitutional diffusion. Interstitial host atoms can be annihilated by pushing located impurity atoms in interstitial sites. These impurities can now diffuse to adjacent substitutional sites and create now self-interstitials.

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

23

Diffusion Equation The basic diffusion process is similar to that of charge carriers (electrons and holes). We define flux F as the number of dopant atoms passing through a unit time and C as the dopant concentration per unit volume. Then F= -D C = carrier concentration D= diffusion coefficient or diffusivity Note: The basic driving force of diffusion process is concentration gradient I . The flux is proportional to concentration gradient and the dopant atoms will move away from a high concentration region toward a lower concentration region. Substituting F in one-dimensional continuity equation, we get

When the concentration of dopant atoms is low, the diffusion coefficient can be cosiderd independent of doping concentration and above equation becomes

This is known as Ficks diffusion equation of law.

ION Implantation

Ion implantation is alternative technique for selective doping of semiconductors. The doping profile is more precisely controlled by this technique. Ion implantation equipment typically consists of an ion source, where ions of the desired element are produced, an accelerator, where the ions are electrostatically accelearated to a high energy, and a target chamber, where the ions impinge on a target, which is the material to be implanted. Each ion is typically a single atom, and thus the actual amount of material implanted in the target is the integral over time of the ion current. This amount is called the dose. When these ions enter into the semiconductor , they loose the kinetic energy through a series of collisions with the electrons as well as nuclei of the lattice atoms Finally, the impurity atom comes to rest when its kinetic energy falls to zero. The distance perpendicular to the semiconductor surface covered by the impurity atom is called projected range Rp. The projected range for a particular impurity species depends upon the energy(E) of the ion beam. Typical ion energies are in the range of 10 to 500KeV. The doping after the implantation is given by

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

24

Metallization and interconnects

In semiconductor process technology, metal refers to a material with very high electrical conductivity. When voltage is applied at the ends of metal, electrons can move around almost freely within the metal. Due to its high conductivity, metal connects on chip devices. Metal is on-chip evaporated on the substrate and is patterned into wires wherever a connection is needed on an IC. Aluminum is the most commonly used metal. It is the most process friendly metal and has process-friendly low resistivity. Its shortcomings include electro migration and insufficient temperature resistance.

Electro Migration: In short channel devices, the corresponding current density becomes larger. High current corresponding densities can cause failure as the transport of mass under the influence of current takes place. It occurs by the transfer of momentum from the electrons to the positive metal ions. When the high current passes through the metal wires on the IC metal ions in some regions will pile up and sses voids will form in other regions. The pile up can short circuit adjacent wires while voids can result in open circuit. Copper is the metal of choice for advanced processes. Its resistivity is the lowest among the metals. Compared to aluminium, it has lower resistivity and lower electromigration. However it is harder to process. Interconnects in high density IC chips are formed by multilevel networks. For high-density a typical 90nm CMOS process, there could be seven or eight levels of metals. Between any two adjacent metal levels, there is dedicated layer called via that is used to make the necessary connection between the two metals. A via is a hole etched in the interlayer dielectric, w which is then filled with metal, usually tungsten, to provide a vertical connection between stacked interconnect metal lines. The group of metal layers is comprised of the following: (a) Metal1, the first level of interconnect (b) Via1, to connect the metal1 and metal2 (c) Metal2, the first level of interconnect (d) Via2, to connect the metal2 and metal3 (e) Metal3, the first level of interconnect (f) Via3, to connect the metal3 and metal4 (g) Metal4, the first level of interconnect (h) Via4, to connect the metal4 and metal5 (i) Metal5, the first level of interconnect (j) Via5, to connect the metal5 and metal6 (k) Metal6, the first level of interconnect (l) Via6, to connect the metal6 and metal7 (m) Metal7, the first level of interconnect (n) Via7, to connect the metal7 and metal8

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

25

ENCAPSULATION (PACKAGING)

A package is the housing of a semiconductor chip. It protects and preserves the performance of the semiconductor devices from electrical, mechanical and chemical corruption or impairment. It also electrically interconnects the chip with outside circuitry. Further, it is designed to dissipate heat generated by the chip. Package design is becoming increasingly significant as well as difficult as device performance, complexity and functionality increase with each generation of technology. Structurally, a package is a plastic, ceramic, laminate, or metal seal that encloses the chip or die inside. The package can protect the chip from contamination or damage by a foreign material in the environment. It is a medium to host the chip or die on the printed circuit board (PCB). Package can be classified into two categories, according to the way in which they attach to the PCB 1. pin-through-hole (PTH) packages have pins are inserted into through-holes in the board and soldered in place from the opposite side of the board. The through-hole mounting approach offers a mechanically reliable and sturdy connection. However, this comes at the expense of packaging density. 2. Surface-mount-technology (SMT) Packages have leads that are soldered directly to the leads on the surface of the circuit board. SMT packages are generally preferred. Packing density is increased for the following reason: (1) through-holes are eliminated. Which provides more wiring space; (2) the lead pitch is reduced; and (3) chips can be mounted on both sides of the board.

Rents rule The number of connections going off-chip tends to be roughly proportional to the complexity of the circuitry on the chip. This relationship was first observed by E. Rent of IBM who translated it into an empirical formula that is appropriately called Rents rule. This formula relates the number of input/output pins to the complexity of the circuit, as measured by the number of gates.

Where K is the average number of I/O s per gate. G the number of gates, the Rent exponent, and P the number of I/O pins to the chip, varies between 0.1 and 0.7. Its value depends strongly upon the application area, architecture and organization of the circuit. During the IC packaging process, the following operations are performed: Die attaching Die attaching is the step during which a die is mounted and fixed to the package or support structure. Bonding Bonding is the process of creating interconnections between the die and the outside world. Encapsulation

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

26

Encapsulation refers to the die being encapsulated with ceramic, plastic, metal or epoxy to prevent physical damage or corrosion. This term is sometime used synonymously with packaging.

Fabrication of Passive Components Integrated Resistors

A resistor in integrated technology is made of a thin strip of resistive layer. Fig shows its typical structure: a long sheet of resistive material is connected to metal terminals by two ohmic contacts. The body of the resistance is electrically insulated from its surroundings by an oxide layer or by a reversely biased junction. If we assume that the sheet resistance is Rs, the total resistance R, is given by

Where Rcont is a localized resistance describing the endings and metal connection contacts. The contact resistance value depends on the specific case; it can range from 10 ohm to 50 ohm. The L/W ratio expresses the aspect ratio.

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

27

Diffused Resistors These can be formed during either the base or emitter diffusion of a bipolar process. For an npn process the base diffusion resistor is a p-type of moderate sheet resistivity typically in the range of 100-200 m. This can provide resistors in 50-10k range. The heavily doped n+ emitter diffusion will produce an n+type resistor with low sheet resistivity of 2-10m. This can provide resistors with low values in 1-100 range. Since a diffusion resistor is based on a p-type base over an n-type epitaxy or an n+ type emitter over a p-type base, it is essential that the formed p-n junctions are always reverse-biased to ensure that current flows in the intended portion of the resistor. The presence of such a reverse-biased p-n junction also introduces a distributed capacitance from the resistor body to the substrate. This will cause high-frequency degradation whereby the resistor value drops from its nominal design value to a lower impedance value due to the shunting capacitance. Pinched Resistors Variation to the diffused resistor that is used to increase the sheet resistivity of base region is to use the n+ type emitter as a means to reduce the cross-sectional area of the base region, thereby

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

28

increasing the sheet resistivity. This can increase the sheet resistance to approx..1k m. In this case, one end of the n+type emitter must be tied to one end of the resistor to contain all current flow to the pinched base region. Epitaxial Resistors High resistors values can be formed using the epitaxial layer since it has higher resistivity than other regions. Epitaxial resistors can have sheet resistances around 5 K m. However, epitaxial resistors have even looser tolerances due to the wide tolerances on both epitaxial resistivity and epitaxial layer thickness. MOS Resistors A MOSFET can be biased to provide a non-linear resistor. Such a resistor provides much greater values than diffused ones while occupying a much smaller area. With the gate shortened to the drain in a mosfet, a quadratic relation between current and voltage exists and the device conducts current only when the voltage exceeds the threshold voltage. Under these circumstances, the current flowing in this resistor depends on the width to length ratio of the channel. Hence, to increase the resistors value, the aspect ratio of the MOSFET should be reduced to give a longer channel length and narrower channel width. Thin Film Resistors A resistive thin film layer can be deposited on the substrate to provide a resistors with very tight absolute value resistance. In addition, given a large variety of resistor materials a wide range of resistor values can be obtained in small footprints, thereby having very small parasitic capacitances and small temperature coefficients. Some common thin film resistor materials include tentalum, tentalum nitride, and nickel-chromium. Unlike semiconductor resistors, thinfilm resistors can be laser trimmed to adjust their values to very high accuracies of up to 0.01%. Laser trimming can increase the resistor value since the fine beam evaporates a portion of thin-film material. By its nature, laser trimmming is a slow and costly operation that is justified when very high accuracy on absolute values is necessary.

Capacitors

Most integrated capacitors are either junction capacitors or MOS capacitors Junction Capacitors A junction capacitor is formed when a p-n junction is reverse-biased. This can be formed using the base-emitter, base-collector, or collector-substrate junctions of npn structure in bipolar ICs. Of course, the particular junction must be maintained in reverse bias to provide the desired capacitance. Since the capacitance arises from the parallel plate effect across the depletion region, whose thickness in turn is voltage-dependent, the capacitance is also voltage-dependent decreasing with increased reverse bias. The capacitance depends on the reverse voltage. The base-emitter junction provides the highest capacitance per unit around 1000pF/mm2 with a low breakdown voltage (approx...5v). the base-collector junction provides 100pF/mm2 with a higher breakdown voltage (40 v) MOS capacitors MOS capacitors are usually formed as parallel plate devices with a top metallization and the high conductivity n+ emitter diffusion as the two plates with a thin oxide dielectric sandwiched in between. The oxide is usually a thin layer of Sio2 with a relative dielectric constant r of 3-4 or Si3N4 with r of 5-8. Since the capacitance obtained is 0 rA/toxide ,the oxide thickness is critical. The lower limit on the oxide thickness depends on the process yields and tolerances as well as the

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

29

desired breakdown voltage and reliability. MOS capacitors can provide around1000pF/mm2 with breakdown voltages upto 100v. Unlike junction capacitors, MOS capacitors are voltageindependent and can be biased either positively or negatively. Their breakdown, however, is destructive since the oxide fails permanently. Care should be taken to prevent overvoltage conditions. QUESTIONS & ANSWERS 1. What are four generations of Integration Circuits? SSI (Small Scale Integration) MSI (Medium Scale Integration) LSI (Large Scale Integration) VLSI (Very Large Scale Integration) 2. Give the advantages of IC? Size is less High Speed Less Power Dissipation 3. Give the variety of Integrated Circuits? More Specialized Circuits Application Specific Integrated Circuits(ASICs) Systems-On-Chips 4. Give the basic process for IC fabrication Silicon wafer Preparation Epitaxial Growth Oxidation Photolithography Diffusion Ion Implantation Isolation technique Metallization Assembly processing & Packaging 5. What are the various Silicon wafer Preparation? Crystal growth & doping Ingot trimming & grinding Ingot slicing Wafer polishing & etching Wafer cleaning. 6. Different types of oxidation? Dry & Wet Oxidation 7. What is the transistors CMOS technology provides? n-type transistors & p-type transistors. 8. What are the different layers in MOS transistors? Drain , Source & Gate 9. What is Enhancement mode transistor? The device that is normally cut-off with zero gate bias. 10. What is Depletion mode Device? The Device that conduct with zero gate bias. 11. When the channel is said to be pinched off? If a large Vds is applied this voltage with deplete the Inversion layer .This Voltage effectively pinches off the channel near the drain. 12. Give the different types of CMOS process? p-well process n-well process Silicon-On-Insulator Process Twin- tub Process 13. What are the steps involved in twin-tub process? Tub Formation Thin-oxide Construction Source & Drain Implantation

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

ECE DEPARTMENT

30

Contact cut definition Metallization.

14. What are the advantages of Silicon-on-Insulator process? No Latch-up Due to absence of bulks transistor structures are denser than bulk silicon. 15. What is BiCMOS Technology? It is the combination of Bipolar technology & CMOS technology. 16. What are the basic processing steps involved in BiCMOS process? Additional masks defining P base region N Collector area Buried Sub collector (BCCD) Processing steps in CMOS process 17. What are the advantages of CMOS process? Low power Dissipation High Packing density Bi directional capability 18. What are the advantages of CMOS process? Low Input Impedance Low delay Sensitivity to load. 19. Define Short Channel devices? Transistors with Channel length less than 3- 5 microns are termed as Short channel devices. With short channel devices the ratio between the lateral & vertical dimensions are reduced. 20. Why NMOS technology is preferred more than PMOS technology? N- channel transistors has greater switching speed when compared tp PMOS transistors. 21. What are the different operating regions for an MOS transistor? Cutoff region Non- Saturated Region Saturated Region 22. . What are the different MOS layers? n-diffusion p-diffusion Polysilicon Metal 23. . Compare between CMOS and bipolar technologies.

Prepared by R.V.V Krishna & N.Venkata Satish

Sri Sai Aditya Institute of Science & Technology (This material is restricted to Campus)

You might also like

- RAPDDocument4 pagesRAPD123vidyaNo ratings yet

- Chapter 6 Thermal Oxidation - I Bo CuiDocument23 pagesChapter 6 Thermal Oxidation - I Bo CuisbotacondNo ratings yet

- Thermal Oxidation Process BasicsDocument104 pagesThermal Oxidation Process BasicsBalamurugan Velayutham100% (1)

- A Teacher-Student Conversation On "Cmos Fabrication Process Flow"Document70 pagesA Teacher-Student Conversation On "Cmos Fabrication Process Flow"Calcutta University RPE 2020No ratings yet

- MOSCAP FabricationDocument34 pagesMOSCAP FabricationAnjireddy ThatiparthyNo ratings yet

- CMOS Fabrication Technologies and Process Design RulesDocument14 pagesCMOS Fabrication Technologies and Process Design RulesPrashant SinghNo ratings yet

- VLSI Unit 2 Technology - SDocument52 pagesVLSI Unit 2 Technology - SIndrajeet GautamNo ratings yet

- Introduction To MOS TechnologiesDocument15 pagesIntroduction To MOS TechnologieslokeshwarrvrjcNo ratings yet

- CMOS Fabrication and Device Characterization ReportDocument14 pagesCMOS Fabrication and Device Characterization ReportShafiq PanicKingNo ratings yet

- Thermal Oxidation Process in IC TechnologyDocument39 pagesThermal Oxidation Process in IC TechnologyCyrille MagdiNo ratings yet

- Course Title: VLSI Technology Course No.: EEE 489Document25 pagesCourse Title: VLSI Technology Course No.: EEE 489Rubel RiadNo ratings yet

- VLSI DesignDocument181 pagesVLSI Designprabhug22No ratings yet

- CMOS Tech-2UP (12 - 11 - 03)Document29 pagesCMOS Tech-2UP (12 - 11 - 03)Mountsinai CscNo ratings yet

- 7.6.2. Poly-Silicon Gate TechnologyDocument14 pages7.6.2. Poly-Silicon Gate TechnologyHarshad KulkarniNo ratings yet

- CMOS Fabrication Process and Layout Design Rules Lecture 10Document4 pagesCMOS Fabrication Process and Layout Design Rules Lecture 10lomash acharyaNo ratings yet

- CH 03Document37 pagesCH 03chilledkarthikNo ratings yet

- Final Report-1Document5 pagesFinal Report-1ISANI VENKATESHWAR REDDY 210146265No ratings yet

- 2CMOSFabricationMNIT (DEc2006)Document46 pages2CMOSFabricationMNIT (DEc2006)Arjun YadavNo ratings yet

- JP Aip FP CavityDocument9 pagesJP Aip FP CavityG SinghNo ratings yet

- Notes NewDocument14 pagesNotes NewPriya SirsatNo ratings yet

- BJT Ic FabricationDocument20 pagesBJT Ic Fabricationestifvnjjsnvk100% (2)

- EE143 Lecture 18 Self-Aligned IC Process Integration TechniquesDocument35 pagesEE143 Lecture 18 Self-Aligned IC Process Integration TechniquesNhật HoàngNo ratings yet

- Reaction Analysis of Initial Oxidation of Silicon by Uv-Light-Excited Ozone and The Application To Rapid and Uniform Sio2 Film GrowthDocument8 pagesReaction Analysis of Initial Oxidation of Silicon by Uv-Light-Excited Ozone and The Application To Rapid and Uniform Sio2 Film GrowthAmitNo ratings yet

- Thin Dielectric Layers Characterization Using Corona-Oxide-Semiconductor Measurement TechniqueDocument54 pagesThin Dielectric Layers Characterization Using Corona-Oxide-Semiconductor Measurement TechniqueTejpreet Singh BediNo ratings yet

- 421 Lab ManualDocument17 pages421 Lab ManualAiman LatifNo ratings yet

- Oxidation Process in IC FabricationDocument11 pagesOxidation Process in IC Fabricationhermas67No ratings yet

- Processing of DevicesDocument31 pagesProcessing of DevicesBituNo ratings yet

- Plating Processes On Aluminum and Application To Novel Solar Cell ConceptsDocument9 pagesPlating Processes On Aluminum and Application To Novel Solar Cell ConceptsĐức PhạmNo ratings yet

- ED Module 5 - Part ADocument10 pagesED Module 5 - Part ABharath CrNo ratings yet

- Unit I Ic FabricationDocument23 pagesUnit I Ic FabricationBhuvana VaradharajNo ratings yet

- ReportDocument8 pagesReportROMANCE FantasNo ratings yet

- Basic Circuit ConceptsDocument17 pagesBasic Circuit ConceptsAdiseshuMiddeNo ratings yet

- MEMS TechnologyDocument45 pagesMEMS TechnologyRITAM CHATTERJEENo ratings yet

- Electrical Activation of Nitrogen Heavily Implanted 3c-Sic 1 0 0Document6 pagesElectrical Activation of Nitrogen Heavily Implanted 3c-Sic 1 0 0Martin BlancoNo ratings yet

- A Major ProjectDocument14 pagesA Major ProjectVarun ChauhanNo ratings yet

- CMOS Fabrication OverviewDocument2 pagesCMOS Fabrication OverviewRaul Arturo Samaniego TelloNo ratings yet

- Ic FabricationDocument7 pagesIc FabricationphooolNo ratings yet

- 3.4.1.2 Silicon On Insulator: Chapter 3 CMOS Processing TechnologyDocument1 page3.4.1.2 Silicon On Insulator: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNo ratings yet

- Atmospheric Pressure Chemical DepositionDocument6 pagesAtmospheric Pressure Chemical DepositioniloveCGNo ratings yet

- MemsDocument35 pagesMemssureshmalliga100% (1)

- Fabricating A Nano-Labyrinth On Silicon Wafer: Project ReportDocument15 pagesFabricating A Nano-Labyrinth On Silicon Wafer: Project ReportEthan HuntNo ratings yet

- MINOR2 DfinalocxDocument32 pagesMINOR2 DfinalocxVenkatesh KumarNo ratings yet

- Lecture2 MicroFabTechniques PDFDocument10 pagesLecture2 MicroFabTechniques PDFdiNo ratings yet

- ECE 510-Digitial Integrated Circuit-I Winter-2011 CMOS Processing TechnologyDocument39 pagesECE 510-Digitial Integrated Circuit-I Winter-2011 CMOS Processing TechnologyGuru VelmathiNo ratings yet

- Electroplating Apparatus for Cyanide-Free Silver CoatingDocument29 pagesElectroplating Apparatus for Cyanide-Free Silver Coatingivanjose09No ratings yet

- (I) Cmos Processing Technology:-: (A) OxidesDocument7 pages(I) Cmos Processing Technology:-: (A) Oxidesmukti450No ratings yet

- Crystal Growth and Wafer Fabrication TechniquesDocument16 pagesCrystal Growth and Wafer Fabrication TechniquesMegha AgrawalNo ratings yet

- MAE 536 Micro/Nano Electromechanical Systems: Yong Zhu Lecture 10 - Surface MicromachiningDocument48 pagesMAE 536 Micro/Nano Electromechanical Systems: Yong Zhu Lecture 10 - Surface MicromachiningAnonymous 8kdwhwUNo ratings yet

- Midterm Exam 1Document9 pagesMidterm Exam 1Hemal ShahporiaNo ratings yet

- CMOS Fabrication Process and Layout Design RulesDocument3 pagesCMOS Fabrication Process and Layout Design RulesKusum34No ratings yet

- CMOS Processing Technology Silicon: A Semiconductor With Resistance Between That of Conductor and AnDocument18 pagesCMOS Processing Technology Silicon: A Semiconductor With Resistance Between That of Conductor and AntmdmurthyNo ratings yet

- EE432/EE532 Microelectronic Fabrication Techniques: Final Lab ReportDocument28 pagesEE432/EE532 Microelectronic Fabrication Techniques: Final Lab Reportapi-546410997No ratings yet

- CMOS Manufacturing Process OverviewDocument1 pageCMOS Manufacturing Process OverviewAnupam GuptaNo ratings yet

- NMOS Fabrication: Step 1: Processing The SubstrateDocument5 pagesNMOS Fabrication: Step 1: Processing The Substratechinthala santhosh srkNo ratings yet

- Unit 2 Fabrication ProcessDocument8 pagesUnit 2 Fabrication Processbhupendra1977No ratings yet

- PaperenglishDocument5 pagesPaperenglishelvaulinaNo ratings yet

- EBB 323 Semiconductor Fabrication Technology: OxidationDocument57 pagesEBB 323 Semiconductor Fabrication Technology: Oxidationdildar123No ratings yet

- Ceramic Materials for Energy Applications V: A Collection of Papers Presented at the 39th International Conference on Advanced Ceramics and CompositesFrom EverandCeramic Materials for Energy Applications V: A Collection of Papers Presented at the 39th International Conference on Advanced Ceramics and CompositesJosef MatyášNo ratings yet

- Advances in Solid Oxide Fuel Cells XFrom EverandAdvances in Solid Oxide Fuel Cells XMihails KusnezoffNo ratings yet

- Sri Sai Aditya Inst - of Science & Tech. ECE Dept..: Prepared by Venkata Satish.NDocument22 pagesSri Sai Aditya Inst - of Science & Tech. ECE Dept..: Prepared by Venkata Satish.NVenkata SatishNo ratings yet

- Important QuestionsDocument2 pagesImportant QuestionsVenkata SatishNo ratings yet

- Digital Communications 3unitsDocument108 pagesDigital Communications 3unitsVenkata SatishNo ratings yet

- Probability TheoryDocument13 pagesProbability TheoryVenkata SatishNo ratings yet

- VLSI Design Process and Unit ProcessesDocument30 pagesVLSI Design Process and Unit ProcessesVenkata SatishNo ratings yet

- VLSI Design Process and Unit ProcessesDocument30 pagesVLSI Design Process and Unit ProcessesVenkata SatishNo ratings yet