Professional Documents

Culture Documents

Fundamentals of Computer Systems: A Single Cycle MIPS Processor

Uploaded by

Mahi NurOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fundamentals of Computer Systems: A Single Cycle MIPS Processor

Uploaded by

Mahi NurCopyright:

Available Formats

Fundamentals of Computer Systems

A Single Cycle MIPS Processor

Stephen A. Edwards and Martha A. Kim

Columbia University

Spring 2012

Illustrations Copyright 2007 Elsevier

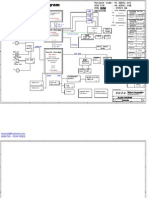

Lets Build a Simple Processor

Supported instructions: R-type: and, or, addu, subu, slt Memory instructions: lw, sw Branch instructions: beq Version 2.0: I-type: addiu J-type: j

MIPS State Elements

This is the programmer-visible state in the ISA

CLK PC'

32

CLK PC

32 32

CLK WE3 RD1 RD2 WE

32 32 32

RD

5 32 5

A1 A2 A3 WD3

Instruction Memory

5 32

Register File

32

RD Data Memory WD

32

ALU Interface and Implementation

A N B N 3F

A

N

B

N

ALU

N Y

F2

F2 0 0 0 0 1 1 1 1

F1 0 0 1 1 0 0 1 1

F0 0 1 0 1 0 1 0 1

Func. A&B A|B A+B A&B A|B AB A < B (slt)

Cout

Zero Extend N N N N

[N-1]

+ S

2

N

F1:0

Datapath Elements for the lw Instruction

Fetch instruction from instruction memory: Send the PC to the instruction memorys address

CLK PC' PC A RD Instruction Memory Instr

CLK A1 A2 A3 WD3 WE3 RD1

CLK WE A RD2 Register File RD Data Memory WD

lw rt, offset(base) LW 100011 base rt offset

Datapath Elements for the lw Instruction

Read the base register

CLK

25:21

CLK PC A RD Instr A1 A2 A3 WD3 WE3 RD1

CLK WE A RD2 Register File RD Data Memory WD

PC'

Instruction Memory

lw rt, offset(base) LW 100011 base rt offset

Datapath Elements for the lw Instruction

Sign-extend the immediate

CLK PC' PC A RD Instr

25:21

CLK A1 WE3 RD1

CLK WE A RD Data Memory WD

Instruction Memory

A2 RD2 A3 Register WD3 File

15:0

SignImm Sign Extend

lw rt, offset(base) LW 100011 base rt offset

Datapath Elements for the lw Instruction

Add the base register and the sign-extended immediate to compute the data memory address

ALUControl2:0 CLK PC' PC A RD Instr

25:21

CLK A1 WE3 RD1 SrcA

010 Zero

CLK WE A RD Data Memory WD

ALU

ALUResult

Instruction Memory

A2 RD2 A3 Register WD3 File

SrcB

SignImm

15:0

Sign Extend

lw rt, offset(base) LW 100011 base rt offset

Datapath Elements for the lw Instruction

Read data from memory and write it back to rt in the register le

RegWrite CLK PC' PC A RD Instr

25:21

ALUControl2:0 010 SrcA Zero CLK WE A RD Data Memory WD ReadData

CLK A1 A2 A3 WD3

1 WE3

ALU

RD1 RD2

ALUResult

Instruction Memory

20:16

SrcB

Register File

SignImm

15:0

Sign Extend

lw rt, offset(base) LW 100011 base rt offset

Datapath Elements for the lw Instruction

Add four to the program counter to determine address of the the next instruction to execute

RegWrite CLK PC' PC A RD Instr

25:21

ALUControl2:0 010 SrcA Zero CLK WE A RD Data Memory WD ReadData

CLK A1 A2

20:16

1 WE3

ALU

RD1 RD2

ALUResult

Instruction Memory

SrcB

A3 WD3

Register File

PCPlus4 SignImm

15:0

Sign Extend

Result

lw rt, offset(base) LW 100011 base rt offset

Additional Elements for sw

Read rt from the register le and write it to data memory

RegWrite CLK PC' PC A RD Instr

25:21

ALUControl2:0 010 SrcA Zero

MemWrite CLK 1 WE A RD Data Memory WD ReadData

CLK A1 A2 A3 WD3

0 WE3

ALU

RD1 RD2

ALUResult

Instruction Memory

20:16 20:16

SrcB

Register File

WriteData

PCPlus4 SignImm

15:0

Sign Extend

Result

sw rt, offset(base) SW 101011 base rt offset

Additional Elements for R-Type Instructions

Read from rs and rt Write ALUResult to rd (instead of rt)

RegWrite CLK PC' PC A RD Instr

25:21

RegDst 1

ALUSrc ALUControl2:0 0 SrcA varies Zero

MemWrite CLK 0 WE A RD Data Memory WD

MemtoReg 0

CLK A1 A2

1 WE3

ALU

RD1 RD2

ALUResult

ReadData

0 1

Instruction Memory

20:16

0 SrcB 1

A3 Register WD3 File

20:16 15:11

WriteData

PCPlus4

15:0

WriteReg4:0 Sign Extend

0 1

SignImm

Result

addu rd, rs, rt SPECIAL 000000 rs rt rd ADDU 00000100001

Additional Elements for beq

Determine whether rs and rt are equal Calculate branch target address

PCSrc RegWrite 0 CLK PC A RD Instr

25:21

RegDst x

ALUSrc ALUControl2:0 Branch 0 110 1 SrcA Zero

MemWrite CLK 0 WE A RD Data Memory WD

MemtoReg x

CLK 0 1 PC'

ALU

A1

WE3

RD1

ALUResult

ReadData

Instruction Memory

20:16

0 1

A2 RD2 A3 Register WD3 File 0 1

0 SrcB 1

WriteData

20:16 15:11

PCPlus4

15:0

WriteReg4:0 Sign Extend

SignImm

<<2

PCBranch

Result

beq rs, rt, offset BEQ rs rt 000100

offset

Add a controller to complete it

MemtoReg Control MemWrite Unit Branch ALUControl2:0 Op ALUSrc Funct RegDst RegWrite CLK 0 1 PC' PC A RD Instr

25:21

PCSrc

31:26 5:0

CLK A1 WE3 RD1 SrcA Zero

CLK WE A RD Data Memory WD ReadData 0 1

ALU

ALUResult

Instruction Memory

20:16

A2 RD2 A3 Register WD3 File 0 1

0 SrcB 1

WriteData

20:16 15:11

PCPlus4

15:0

WriteReg4:0 Sign Extend

SignImm

<<2

PCBranch

Result

Op

rs

Funct

R-Type Instruction Encoding

addu rd, rs, rt SPECIAL 000000 SPECIAL 000000 SPECIAL 000000 SPECIAL 000000 SPECIAL 000000 rs rt rd ADDU 00000100001 SUBU 00000100011 AND 00000100100 OR 00000100101 SLT 00000101010

subu rd, rs, rt rs rt rd

and rd, rs, rt rs rt rd

or rd, rs, rt rs rt rd

slt rd, rs, rt rs rt rd

The ALU Decoder

Control Unit

MemtoReg MemWrite Branch ALUSrc RegDst RegWrite

Opcode5:0

Main Decoder

Part of the control unit responsible for implementing the opcode Funct eld.

ALU Op 00 -1 11111Funct 100001 100011 100100 100101 101010 ALU Ctrl. 010 110 010 110 000 001 111 ALU Function Add Subtract Add Subtract AND OR Slt

ALUOp1:0 ALU Decoder

Funct5:0

ALUControl 2:0

The Main Decoder

Inst. R-type lw sw beq OP 000000 100011 101011 000100 RegWrite RegDst ALUSrc Branch MemWrite MemToReg ALUOp

31:26 5:0

MemtoReg Control MemWrite Unit Branch ALUControl2:0 Op ALUSrc Funct RegDst RegWrite

PCSrc

CLK 0 1 PC' PC A RD Instr

25:21

CLK A1 WE3 RD1 SrcA Zero

CLK WE A RD Data Memory WD ReadData 0 1

ALU

ALUResult

Instruction Memory

20:16

A2 RD2 A3 Register WD3 File 0 1

0 SrcB 1

WriteData

20:16 15:11

PCPlus4

15:0

WriteReg4:0 Sign Extend

SignImm

<<2

PCBranch

Result

The Main Decoder

Inst. R-type lw sw beq OP 000000 100011 101011 000100 RegWrite RegDst ALUSrc Branch MemWrite MemToReg ALUOp 1 1 0 0 0 0 1-

31:26 5:0

MemtoReg Control MemWrite Unit Branch ALUControl2:0 Op Funct ALUSrc RegDst RegWrite

0 PCSrc

0 0 1 PC'

CLK PC A RD Instr

25:21

CLK A1 A2

1 WE3 RD1 RD2 SrcA 0 0 SrcB 1 1 0 WriteReg4:0 1

CLK 001 Zero ALUResult A

0 WE 0 ReadData 0 1

ALU

Instruction Memory

20:16

A3 Register WD3 File

20:16 15:11

WriteData

RD Data Memory WD

PCPlus4

15:0

SignImm Sign Extend

<<2

PCBranch

Result

The Main Decoder

Inst. R-type lw sw beq OP 000000 100011 101011 000100 RegWrite RegDst ALUSrc Branch MemWrite MemToReg ALUOp 1 1 1 0 0 1 0 0 0 0 0 1 100

31:26 5:0

MemtoReg Control MemWrite Unit Branch ALUControl2:0 Op ALUSrc Funct RegDst RegWrite

PCSrc

CLK 0 1 PC' PC A RD Instr

25:21

CLK A1 WE3 RD1 SrcA Zero

CLK WE A RD Data Memory WD ReadData 0 1

ALU

ALUResult

Instruction Memory

20:16

A2 RD2 A3 Register WD3 File 0 1

0 SrcB 1

WriteData

20:16 15:11

PCPlus4

15:0

WriteReg4:0 Sign Extend

SignImm

<<2

PCBranch

Result

The Main Decoder

Inst. R-type lw sw beq OP 000000 100011 101011 000100 RegWrite RegDst ALUSrc Branch MemWrite MemToReg ALUOp 1 1 0 1 0 0 1 1 0 0 0 0 0 1 0 1 100 00

31:26 5:0

MemtoReg Control MemWrite Unit Branch ALUControl2:0 Op ALUSrc Funct RegDst RegWrite

PCSrc

CLK 0 1 PC' PC A RD Instr

25:21

CLK A1 WE3 RD1 SrcA Zero

CLK WE A RD Data Memory WD ReadData 0 1

ALU

ALUResult

Instruction Memory

20:16

A2 RD2 A3 Register WD3 File 0 1

0 SrcB 1

WriteData

20:16 15:11

PCPlus4

15:0

WriteReg4:0 Sign Extend

SignImm

<<2

PCBranch

Result

The Main Decoder

Inst. R-type lw sw beq OP 000000 100011 101011 000100 RegWrite RegDst ALUSrc Branch MemWrite MemToReg ALUOp 1 1 0 0 1 0 0 1 1 0 0 0 0 1 0 0 1 0 0 1 100 00 01

31:26 5:0

MemtoReg Control MemWrite Unit Branch ALUControl2:0 Op ALUSrc Funct RegDst RegWrite

PCSrc

CLK 0 1 PC' PC A RD Instr

25:21

CLK A1 WE3 RD1 SrcA Zero

CLK WE A RD Data Memory WD ReadData 0 1

ALU

ALUResult

Instruction Memory

20:16

A2 RD2 A3 Register WD3 File 0 1

0 SrcB 1

WriteData

20:16 15:11

PCPlus4

15:0

WriteReg4:0 Sign Extend

SignImm

<<2

PCBranch

Result

The Main Decoder

Inst. R-type lw sw beq addiu OP 000000 100011 101011 000100 001001 RegWrite RegDst ALUSrc Branch MemWrite MemToReg ALUOp 1 1 0 0 1 0 1 0 0 1 0 0 0 1 Can we do this with our datapath?

MemtoReg Control MemWrite Unit Branch ALUControl2:0 Op ALUSrc Funct RegDst RegWrite CLK 0 1 PC' PC A RD Instr

25:21

0 0 1 0

0 1 -

100 00 01

PCSrc

31:26 5:0

CLK A1 WE3 RD1 SrcA Zero

CLK WE A RD Data Memory WD ReadData 0 1

ALU

ALUResult

Instruction Memory

20:16

A2 RD2 A3 Register WD3 File 0 1

0 SrcB 1

WriteData

20:16 15:11

PCPlus4

15:0

WriteReg4:0 Sign Extend

SignImm

<<2

PCBranch

Result

The Main Decoder

Inst. R-type lw sw beq addiu OP 000000 100011 101011 000100 001001 RegWrite RegDst ALUSrc Branch MemWrite MemToReg ALUOp 1 1 0 0 1 1 0 0

MemtoReg Control MemWrite Unit Branch ALUControl2:0 Op ALUSrc Funct RegDst RegWrite CLK 0 1 PC' PC A RD Instr

25:21

0 1 1 0 1

0 0 0 1 0

0 0 1 0 0

0 1 0

100 00 01 00

PCSrc

31:26 5:0

CLK A1 WE3 RD1 SrcA Zero

CLK WE A RD Data Memory WD ReadData 0 1

ALU

ALUResult

Instruction Memory

20:16

A2 RD2 A3 Register WD3 File 0 1

0 SrcB 1

WriteData

20:16 15:11

PCPlus4

15:0

WriteReg4:0 Sign Extend

SignImm

<<2

PCBranch

Result

Additional Elements for the j Instruction

Inst. R-type lw sw beq addiu j OP 000000 100011 101011 000100 001001 000010 RegWrite RegDst ALUSrc Branch MemWrite MemToReg ALUOp Jump 1 1 0 0 1 0

Jump

1 0 0 MemtoReg Control MemWrite Unit Branch ALUControl2:0 Op ALUSrc Funct RegDst RegWrite

0 1 1 0 1 -

0 0 0 1 0 -

0 0 1 0 0 0

0 1 0 -

100 00 01 00 --

0 0 0 0 0 1

PCSrc

31:26 5:0

CLK 0 1 0 1 PC' PC A RD Instr

25:21

CLK A1 WE3 RD1 SrcA Zero

CLK WE A RD Data Memory WD ReadData 0 Result 1

ALU

ALUResult

Instruction Memory

20:16

A2 RD2 A3 Register WD3 File 0 1

0 SrcB 1

WriteData

20:16

PCJump

15:11

PCPlus4

15:0

WriteReg4:0 Sign Extend

4

27:0 31:28

SignImm

<<2

25:0

<<2

PCBranch

Processor Performance

Seconds Program

Instructions Program

Clock Cycles Instruction

Seconds Clock Cycle

Seconds Program Instructions Program Clock Cycles Instruction Seconds Clock Cycle

How long you have to wait Number that must execute to complete the task CPI: Cycles per instruction The clock period (1/frequency)

The Critical Path Here: Load from Memory

MemtoReg Control MemWrite Unit Branch ALUControl 2:0 Op ALUSrc Funct RegDst RegWrite CLK 0 1 PC' PC A RD Instr

25:21

PCSrc

31:26 5:0

CLK A1 A2 A3

1 WE3 RD1 1 RD2 SrcA 0 SrcB 1 0 0 1

CLK 010 Zero ALUResult A

0 WE 1 ReadData 0 1

ALU

Instruction Memory

20:16

Register WD3 File

20:16 15:11

WriteData

RD Data Memory WD

PCPlus4

15:0

WriteReg4:0 Sign Extend

SignImm

<<2

PCBranch

Result

Instruction Memory to Register File to ALU to Data Memory to Register File

The Critical Path Dictates the Clock Period

Element Register clk-to-Q Register setup Multiplexer ALU Memory Read Register le read Register le setup Delay tpcq-PC 30 ps tsetup 20 tmux 25 tALU 200 tmem 250 tRFread 150 tRFsetup 20

31:26 5:0

MemtoReg Control MemWrite Unit Branch ALUControl 2:0 Op ALUSrc Funct RegDst RegWrite

PCSrc

CLK 0 1 PC' PC A RD Instr

25:21

CLK A1 A2 A3 WD3

20:16 15:11

1 WE3

CLK RD1 RD2 SrcA 1 0 SrcB 1 0 0 1 010 Zero ALUResult A

0 WE ReadData 0 1

ALU

Instruction Memory

20:16

Register File

WriteData

RD Data Memory WD

PCPlus4

15:0

WriteReg4:0 Sign Extend

SignImm

<<2

PCBranch

Result

TC

= = = =

tpcq-PC + tmem-I + tRFread + tALU + tmem-D + tmux + tRFsetup (30 + 250 + 150 + 200 + 250 + 25 + 20) ps 925 ps 1.08 GHz

Execution Time for Our Single-Cycle Processor

For a 100 billion-instruction task on our single-cycle processor with a 925 ps clock period,

Seconds Program

Instructions Program

Clock Cycles Instruction

Seconds Clock Cycle

= 100 109 = 92.5 seconds

925 ps

You might also like

- Processor Architecture: Direct Execution RISC Processor: I Wonder Where This Goes?Document20 pagesProcessor Architecture: Direct Execution RISC Processor: I Wonder Where This Goes?nattu_78No ratings yet

- L16 Multicycle MIPSDocument38 pagesL16 Multicycle MIPSkumarguptav91No ratings yet

- Datapaths II & Control IDocument41 pagesDatapaths II & Control IAndrea AquinoNo ratings yet

- ECE4680 Computer Organization and Architecture Designing Single Cycle ControlDocument17 pagesECE4680 Computer Organization and Architecture Designing Single Cycle ControlNarender KumarNo ratings yet

- Chapter 5 - The Processor: Datapath and ControlDocument101 pagesChapter 5 - The Processor: Datapath and Controlapi-26072581No ratings yet

- Datapath For The MIPS Architecture (A Single-Cycle Implementation)Document22 pagesDatapath For The MIPS Architecture (A Single-Cycle Implementation)Alexander TaylorNo ratings yet

- Cab LageDocument2 pagesCab LageSalah DahouathiNo ratings yet

- Schematic DiagramDocument13 pagesSchematic DiagramSas WajiNo ratings yet

- Lcdf3 Chap 10 p2Document32 pagesLcdf3 Chap 10 p2Ali Ahmad100% (1)

- How To Design A Controller To Produce Signals To Control The DatapathDocument6 pagesHow To Design A Controller To Produce Signals To Control The DatapathNarender KumarNo ratings yet

- 03 Bagian 1 Arsitektur AVRDocument22 pages03 Bagian 1 Arsitektur AVRTito Adi NugrohoNo ratings yet

- Diagrama 333Document1 pageDiagrama 333xerox4512No ratings yet

- Control Unit Design: Decoder &Document30 pagesControl Unit Design: Decoder &blackmaverick0912No ratings yet

- Aspire+5542+ +5542g.schematicDocument61 pagesAspire+5542+ +5542g.schematicAndres LañaNo ratings yet

- Acer Aspire 4251 4551 Emachines d440 d640 d640g - Wistron Hm42-Dn Je40-Dn - Rev - 3Document63 pagesAcer Aspire 4251 4551 Emachines d440 d640 d640g - Wistron Hm42-Dn Je40-Dn - Rev - 3chatmarNo ratings yet

- Micro Programmed Control Organization.: Next-Address InformationDocument16 pagesMicro Programmed Control Organization.: Next-Address InformationZaheer AsgharNo ratings yet

- Chapter 7Document26 pagesChapter 7prachesNo ratings yet

- Fetch-Execute Cycle: Minggu 1 Arsitektur KomputerDocument12 pagesFetch-Execute Cycle: Minggu 1 Arsitektur KomputerRyan SaputraNo ratings yet

- Section 6. Oscillators: HighlightsDocument44 pagesSection 6. Oscillators: HighlightsFrancisco MartinsNo ratings yet

- Easypic Fusion v7 SCH v101Document2 pagesEasypic Fusion v7 SCH v101vietanh_askNo ratings yet

- Interrupt Control: Serial I/O ControlDocument15 pagesInterrupt Control: Serial I/O ControlnagpalanishNo ratings yet

- NB - MB Level 3-1Document83 pagesNB - MB Level 3-1harvey1specter-1No ratings yet

- F 818Document9 pagesF 818Eric YangNo ratings yet

- Computer Organization & Design: Bilgisayar Organizasyonu & TasarimiDocument32 pagesComputer Organization & Design: Bilgisayar Organizasyonu & Tasarimimanny oluanNo ratings yet

- Laboratory Introduction: 35 Instructions Same As Previous PIC Versions (Eg 16F74)Document12 pagesLaboratory Introduction: 35 Instructions Same As Previous PIC Versions (Eg 16F74)dhivakargunalanNo ratings yet

- Wistron JV50-PU Rev SB PDFDocument61 pagesWistron JV50-PU Rev SB PDFalbugNo ratings yet

- Aopen Laptop Motherboard Schematic DiagramDocument47 pagesAopen Laptop Motherboard Schematic DiagrampukymottoNo ratings yet

- Easypic v7 Schematic v104Document2 pagesEasypic v7 Schematic v104andrei_nokNo ratings yet

- MCD Demo2 Manual enDocument33 pagesMCD Demo2 Manual enmario_villarreal_110% (1)

- Actions Atm7029 Tablet Schem M2903 - SCH - V11 PDFDocument14 pagesActions Atm7029 Tablet Schem M2903 - SCH - V11 PDFparascoli0% (1)

- LC3 1 1Document59 pagesLC3 1 1Kevin HarvardNo ratings yet

- Introducere in Programarea MicrocontrollerelorDocument49 pagesIntroducere in Programarea MicrocontrollerelorJustin PuscasuNo ratings yet

- Chapter 5Document86 pagesChapter 5Muhammad OmerNo ratings yet

- BL55021 PDFDocument8 pagesBL55021 PDFjackass_tNo ratings yet

- Lenovo - 20S10 - QUANTA FL2 - REV 1ASec PDFDocument36 pagesLenovo - 20S10 - QUANTA FL2 - REV 1ASec PDFCesar AugustoNo ratings yet

- Samsung PN50A550 PN58A550 SchematicDiagram (SM)Document13 pagesSamsung PN50A550 PN58A550 SchematicDiagram (SM)coolruler40100% (1)

- Pic 16 F 628Document20 pagesPic 16 F 628Merényi Oszkár100% (1)

- LCM1602A DatasheetDocument21 pagesLCM1602A DatasheetjohnluzardoNo ratings yet

- Dell Inspiron 1440 - Wistron ALBA UMADocument61 pagesDell Inspiron 1440 - Wistron ALBA UMACao Bồi Nông ThônNo ratings yet

- Nortel PBX Cheat SheetDocument13 pagesNortel PBX Cheat SheetRahul Saini100% (1)

- Ts 7500 SchematicDocument4 pagesTs 7500 Schematicimransiddiquiatvxt100% (1)

- Easypic v7 Schematic v103Document2 pagesEasypic v7 Schematic v103Nguyen Viet AnhNo ratings yet

- HP Compaq v3500 - Wistron Tibet - SCDocument44 pagesHP Compaq v3500 - Wistron Tibet - SCphotosynergyNo ratings yet

- Acer Aspire 5740 (Wistron JV71-TR) - Wistron - JV71-TrDocument61 pagesAcer Aspire 5740 (Wistron JV71-TR) - Wistron - JV71-TrCarlosNo ratings yet

- MIPS 5 Stage PipelineDocument12 pagesMIPS 5 Stage PipelinephuonghienNo ratings yet

- IyCnet INDIRECTADD PDFDocument140 pagesIyCnet INDIRECTADD PDFmacu1820No ratings yet

- Unit 3 CSADocument25 pagesUnit 3 CSAyugdevNo ratings yet

- LMC-SSC2E16-01 Serial: User ManualDocument12 pagesLMC-SSC2E16-01 Serial: User ManualFred ShihNo ratings yet

- Pic12c508 and Adf4113Document32 pagesPic12c508 and Adf4113Lê Đình Tiến100% (1)

- ASUS A7T A7T C51MV-v20Document73 pagesASUS A7T A7T C51MV-v20netov777No ratings yet

- Exploring Arduino: Tools and Techniques for Engineering WizardryFrom EverandExploring Arduino: Tools and Techniques for Engineering WizardryRating: 4.5 out of 5 stars4.5/5 (5)

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCFrom EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCNo ratings yet

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysFrom EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Proforma - Attendance PercentageDocument6 pagesProforma - Attendance Percentageraja93satNo ratings yet

- Inside The Social Network's (Datacenter) NetworkDocument49 pagesInside The Social Network's (Datacenter) NetworkVamsi Krishna PatchamatlaNo ratings yet

- FIS-Finishes Schedule - R1Document4 pagesFIS-Finishes Schedule - R1meghadurganNo ratings yet

- Introduction To Operations Research 11E Ise 11Th Ise Edition Frederick S Hillier Full ChapterDocument67 pagesIntroduction To Operations Research 11E Ise 11Th Ise Edition Frederick S Hillier Full Chapterrobin.mccomb793No ratings yet

- Manajemen Data Standar Pelayanan Minimal Rumah Sakit The Hospital Minimum Service Standard Data Management Sigid Nugroho Adhi Kori Puspita NingsihDocument10 pagesManajemen Data Standar Pelayanan Minimal Rumah Sakit The Hospital Minimum Service Standard Data Management Sigid Nugroho Adhi Kori Puspita NingsihririnNo ratings yet

- Sogc AssignmentDocument2 pagesSogc Assignmentapi-573219210No ratings yet

- Long Quiz For Week 12345Document26 pagesLong Quiz For Week 12345Jerwyn Marie CayasNo ratings yet

- Basics On Piping LayoutDocument11 pagesBasics On Piping Layoutpuru55980No ratings yet

- BEE MCQ Unit IVDocument16 pagesBEE MCQ Unit IVUmesh PatilNo ratings yet

- PPA Application - 2700 Sloat BLVD (283 Units)Document8 pagesPPA Application - 2700 Sloat BLVD (283 Units)Sasha PerigoNo ratings yet

- Vilta-S: Stabilizer For SmartphoneDocument28 pagesVilta-S: Stabilizer For SmartphoneNivin KumarNo ratings yet

- Egs630-6 Komatsu GensetDocument2 pagesEgs630-6 Komatsu GensetimamfadiliNo ratings yet

- Learning Based Exposition-The Simple Present TenseDocument12 pagesLearning Based Exposition-The Simple Present Tenseyuri Berrocal YanceNo ratings yet

- 7.0 Overview of Vibrational Structural Health Monitoring With Representative Case StudiesDocument9 pages7.0 Overview of Vibrational Structural Health Monitoring With Representative Case Studiesankurshah1986No ratings yet

- Penurunan Waktu Tunggu Operasi Elektif Dengan Membuat Standar Prosedur Operasional Di Rumah Sakit Umum Karsa Husada BatuDocument8 pagesPenurunan Waktu Tunggu Operasi Elektif Dengan Membuat Standar Prosedur Operasional Di Rumah Sakit Umum Karsa Husada BaturirisNo ratings yet

- Bootstrap 3 All Classes List Cheat Sheet Reference PDF (2020) PDFDocument21 pagesBootstrap 3 All Classes List Cheat Sheet Reference PDF (2020) PDFHoney ShineNo ratings yet

- May DAY EVE LessonsDocument4 pagesMay DAY EVE LessonsFerdinand Pinon100% (1)

- Influences of Le Corbusier and Louis I Kahn in IndiaDocument10 pagesInfluences of Le Corbusier and Louis I Kahn in IndiaRashi Chugh88% (8)

- Catalog of Replacement Parts: Model D300 Series MixersDocument24 pagesCatalog of Replacement Parts: Model D300 Series Mixersanto starlinNo ratings yet

- Life Cycle Asset ManagementDocument1 pageLife Cycle Asset ManagementJuan EspinosaNo ratings yet

- HL956FT16-WS3 Lista de RepuestosDocument75 pagesHL956FT16-WS3 Lista de RepuestosLuis SuarezNo ratings yet

- MSA WorksheetDocument33 pagesMSA WorksheetSandrawarman BalasundramNo ratings yet

- Quarter 3-LP-Eng10-Lesson3Document4 pagesQuarter 3-LP-Eng10-Lesson3Cynthia LuayNo ratings yet

- ISO 90012015checklist - tcm14 57745 PDFDocument25 pagesISO 90012015checklist - tcm14 57745 PDFDaniela Muñoz SaldiasNo ratings yet

- KL-710 Conventional Temprature Detector PDFDocument1 pageKL-710 Conventional Temprature Detector PDFghenriquezNo ratings yet

- Image PlacementDocument4 pagesImage PlacementJanix MagbanuaNo ratings yet

- S1-1054/2 10kV Digital Insulation Tester: User ManualDocument24 pagesS1-1054/2 10kV Digital Insulation Tester: User ManualHoracio BobedaNo ratings yet

- M Pump - Plunger 300Document30 pagesM Pump - Plunger 300hebert perezNo ratings yet

- Leybold Didactic EquipmentsDocument4 pagesLeybold Didactic EquipmentsAffo AlexNo ratings yet

- Republic of The Philippines Social Security System MemberDocument1 pageRepublic of The Philippines Social Security System MemberreyNo ratings yet