Professional Documents

Culture Documents

HT27LC020 Cmos 256K 8-Bit Otp Eprom: Features

Uploaded by

vetchboyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HT27LC020 Cmos 256K 8-Bit Otp Eprom: Features

Uploaded by

vetchboyCopyright:

Available Formats

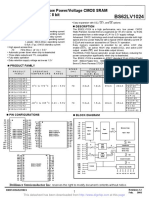

HT27LC020

CMOS 256K´8-Bit OTP EPROM

Features

· Operating voltage: +3.3V · 256K´8-bit organization

· Programming voltage · Fast read access time: 90ns

- VPP=12.5V±0.2V · Fast programming algorithm

- VCC=6.0V±0.2V · Programming time 75ms typ.

· High-reliability CMOS technology

· Two line controls (OE and CE)

· Latch-up immunity to 100mA from -1.0V to

· Standard product identification code

VCC+1.0V

· Commercial temperature ranges (0°C to +70°C)

· CMOS and TTL compatible I/O

· 32-pin DIP/SOP/TSOP/PLCC package

· Low power consumption

- Active: 15mA max.

- Standby: 1mA typ.

General Description

The HT27LC020 chip family is a low-power, 2048K with respect to Spec. This eliminates the need for WAIT

(2,097,152) bit, +3.3V electrically one-time programma- states in high-performance microprocessor systems.

ble (OTP) read-only memories (EPROM). Organized The HT27LC020 has separate Output Enable (OE) and

into 256K words with 8 bits per word, it features a fast Chip Enable (CE) controls which eliminate bus conten-

single address location programming, typically at 75ms tion issues.

per byte. Any byte can be accessed in less than 90ns

Block Diagram

R o w

X -D e c o d e r C e ll A r r a y

A d d re s s

V C C

C o lu m n G N D

A d d re s s Y -D e c o d e r Y - G a tin g

V P P

C E C E & O E & S A C K T

O E P G M & T E S T & D Q 0 ~ D Q 7

P G M C o n tr o l L o g ic O u tp u t B u ffe r

Rev. 1.40 1 November 21, 2002

HT27LC020

Pin Assignment

V P P 1 3 2 V C C

A 1 6 2 3 1 P G M

P G M

V C C

V P P

A 1 2

A 1 5

A 1 6

A 1 7

A 1 5 3 3 0 A 1 7

3 0

3 2

3 1

4

3

2

1

A 1 2 4 2 9 A 1 4

A 7 5 2 8 A 1 3 A 1 1 1 3 2 O E

A 7 5 2 9 A 1 4 A 9 2 3 1 A 1 0

A 6 6 2 7 A 8 A 6 6 2 8 A 1 3 A 8 3 3 0 C E

A 5 7 2 7 A 1 3 4 2 9 D Q 7

A 5 7 2 6 A 9 A 8 2 8

A 1 4 5 D Q 6

A 4 8 2 6 A 9 A 1 7 6 2 7 D Q 5

A 4 8 2 5 A 1 1 H T 2 7 L C 0 2 0

A 3 9 2 5 A 1 1 P G M 7 2 6 D Q 4

A 3 9 2 4 O E

A 2 1 0 3 2 P L C C -A 2 4 O E

V C C 8 H T 2 7 L C 0 2 0 2 5 D Q 3

V P P 9 2 4 G N D

A 2 1 0 2 3 A 1 0 A 1 1 1 2 3 A 1 0 A 1 6 1 0 3 2 T S O P -A 2 3 D Q 2

A 1 1 1 2 2 C E A 0 1 2 2 2 C E A 1 5 1 1 2 2 D Q 1

A 1 2 1 2 2 1 D Q 0

A 0 1 2 2 1 D Q 7 D Q 0 1 3 2 1 D Q 7 A 7 2 0 A 0

1 3

A 6 1 4 1 9 A 1

D Q 0 1 3 2 0 D Q 6 A 5 1 5 1 8 A 2

1 4

1 5

1 6

1 7

1 8

1 9

2 0

D Q 1 1 4 1 9 D Q 5 A 4 1 6 1 7 A 3

G N D

D Q 1

D Q 2

D Q 3

D Q 4

D Q 5

D Q 6

D Q 2 1 5 1 8 D Q 4

G N D 1 6 1 7 D Q 3

H T 2 7 L C 0 2 0

3 2 D IP -A /S O P -A

Pin Description

Pin Name I/O/C/P Description

A0~A17 I Address inputs

DQ0~DQ7 I/O Data inputs/outputs

CE C Chip enable

OE C Output enable

PGM C Program strobe

NC ¾ No connection

VPP P Program voltage supply

Absolute Maximum Rating

Operation Temperature Commercial ............................................................................................................0°C to 70°C

Storage Temperature.............................................................................................................................-65°C to 125 °C

Applied VCC Voltage with Respect to GND............................................................................................... -0.6V to 7.0V

Applied Voltage on Input Pin with Respect to GND.................................................................................... -0.6V to 7.0V

Applied Voltage on Output Pin with Respect to GND......................................................................... -0.6V to VCC+0.5V

Applied Voltage on A9 Pin with Respect to GND ..................................................................................... -0.6V to 13.5V

Applied VPP Voltage with Respect to GND ..............................................................................................-0.6V to 13.5V

Applied READ Voltage (Functionality is guaranteed between these limits) ..................................................3.0V to 3.6V

Note: These are stress ratings only. Stresses exceeding the range specified under ²Absolute Maximum Ratings² may

cause substantial damage to the device. Functional operation of this device at other conditions beyond those

listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliabil-

ity.

Rev. 1.40 2 November 21, 2002

HT27LC020

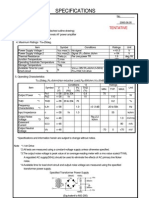

D.C. Characteristics

Test Conditions

Symbol Parameter Min. Typ. Max. Unit

VCC Conditions

Read operation

VOH Output High Level 3.3V IOH=-0.4mA 2.4 ¾ ¾ V

VOL Output Low Level 3.3V IOL=2.0mA ¾ ¾ 0.45 V

VIH Input High Level 3.3V ¾ 2.0 ¾ VCC+0.5 V

VIL Input Low Level 3.3V ¾ -0.3 ¾ 0.8 V

ILI Input Leakage Current 3.3V VIN=0 to 3.6V -5 ¾ 5 mA

ILO Output Leakage Current 3.3V VOUT=0 to 3.6V -10 ¾ 10 mA

CE=VIL, f=5MHz,

ICC VCC Active Current 3.3V ¾ ¾ 15 mA

IOUT=0mA

ISB1 Standby Current (CMOS) 3.3V CE=VCC±0.3V ¾ 1.0 10 mA

ISB2 Standby Current (TTL) 3.3V CE=VIH ¾ ¾ 0.6 mA

VPP Read/Standby

IPP 3.3V CE=OE=VIL, VPP=VCC ¾ ¾ 100 mA

Current

Programming operation

VOH Output High Level 6V IOH=-0.4mA 2.4 ¾ ¾ V

VOL Output Low Level 6V IOL=2.0mA ¾ ¾ 0.45 V

VIH Input High Level 6V ¾ 0.7VCC ¾ VCC+0.5 V

VIL Input Low Level 6V ¾ -0.5 ¾ 0.8 V

ILI Input Load Current 6V VIN=VIL, VIH ¾ ¾ 5.0 mA

VH A9 Product ID Voltage 6V ¾ 11.5 ¾ 12.5 V

ICC VCC Supply Current 6V ¾ ¾ ¾ 40 mA

IPP VPP Supply Current 6V CE=VIL ¾ ¾ 10 mA

Capacitance

CIN Input Capacitance 3.3V VIN=0V ¾ 8 12 pF

COUT Output Capacitance 3.3V VOUT=0V ¾ 8 12 pF

CVPP VPP Capacitance 3.3V VPP=0V ¾ 18 25 pF

A.C. Characteristics Ta=+25°C±5°C

Test Conditions

Symbol Parameter Min. Typ. Max. Unit

VCC Conditions

Read operation

tACC Address to Output Delay 3.3V CE=OE=VIL ¾ ¾ 90 ns

tCE Chip Enable to Output Delay 3.3V OE=VIL ¾ ¾ 90 ns

tOE Output Enable to Output Delay 3.3V CE=VIL ¾ ¾ 45 ns

CE or OE High to Output Float, Whichever

tDF 3.3V ¾ ¾ ¾ 40 ns

Occurred First

Output Hold from Address, CE or OE,

tOH 3.3V ¾ 0 ¾ ¾ ns

Whichever Occurred First

Rev. 1.40 3 November 21, 2002

HT27LC020

Test Conditions

Symbol Parameter Min. Typ. Max. Unit

VCC Conditions

Programming operation

tAS Address Setup Time 6V ¾ 2 ¾ ¾ ms

tOES OE Setup Time 6V ¾ 2 ¾ ¾ ms

tDS Data Setup Time 6V ¾ 2 ¾ ¾ ms

tAH Address Hold Time 6V ¾ 0 ¾ ¾ ms

tDH Data Hold Time 6V ¾ 2 ¾ ¾ ms

tDFP Output Enable to Output Float Delay 6V ¾ 0 ¾ 130 ns

tVPS VPP Setup Time 6V ¾ 2 ¾ ¾ ms

tPW PGM Program Pulse Width 6V ¾ 30 75 105 ms

tVCS VCC Setup Time 6V ¾ 2 ¾ ¾ ms

tCES CE Setup Time 6V ¾ 2 ¾ ¾ ms

tOE Data Valid from OE 6V ¾ ¾ ¾ 150 ns

tPRT VPP Pulse Rise Time During Programming 6V ¾ 2 ¾ ¾ ms

Test waveforms and measurements

2 .4 V

2 .0 V A C

A C D r iv in g

M e a s u re m e n t

L e v e ls

L e v e l

0 .8 V

0 .4 5 V

tR, tF<20ns (10% to 90%)

Output test load

1 .3 V

(1 N 9 1 4 )

3 .3 k 9

O u tp u t P in

C L

Note: CL=100pF including jig capacitance.

Product Identification Code

Pins Hex

Code

A0 A1 DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ0 Data

Manufacturer 0 1 0 0 0 1 1 1 0 0 1C

Device Type 1 1 0 0 0 0 0 0 1 0 02

0 0 0 1 1 1 1 1 1 1 7F

Continuation

1 0 0 1 1 1 1 1 1 1 7F

Rev. 1.40 4 November 21, 2002

HT27LC020

Functional Description

Operation mode

All the operation modes are shown in the table following.

Mode CE OE PGM A0 A1 A9 VPP Output

Read VIL VIL X (2) X X X VCC Dout

Output Disable VIL VIH X X X X VCC High Z

Standby (TTL) VIH X X X X X VCC High Z

Standby (CMOS) VCC±0.3V X X X X X VCC High Z

Program VIL VIH VIL X X X VPP DIN

Program Verify VIL VIL VIH X X X VPP DOUT

Product Inhibit VIH X X X X X VPP High Z

Manufacturer Code (3) VIL VIL X VIL VIH VH (1) VCC 1C

Device Code (3) VIL VIL X VIH VIH VH (1) VCC 02

Notes: (1) VH = 12.0V±0.5V

(2) X=Either VIH or VIL

(3) For Manufacturer Code and Device Code, A1=VIH, When A1=VIL, both codes will read 7F

Vpp=12.5±0.2V, PGM LOW, and OE HIGH will program

Programming of the HT27LC020 that HT27LC020. A high-level CE input inhibits the

When the HT27LC020 is delivered, the chip has all HT27LC020 from being programmed.

2048K bits in the ²ONE², or HIGH state. ²ZEROs² are

loaded into the HT27LC020 through programming. Program verify mode

Verification should be performed on the programmed

The programming mode is entered when 12.5±0.2V is ap-

bits to determine whether they were correctly pro-

plied to the VPP pin, OE is at VIH, and CE and PGM are

grammed. The verification should be performed with

VIL. For programming, the data to be programmed is ap-

OE and CE at VIL, PGM at VIH, and VPP at its program-

plied with 8 bits in parallel to the data pins.

ming voltage.

The programming flowchart in Figure 3 shows the fast

interactive programming algorithm. The interactive al- Auto product identification

gorithm reduces programming time by using 30ms to The Auto Product Identification mode allows the read-

105ms programming pulses and giving each address ing out of a binary code from an EPROM that will identify

only as many pulses as is necessary in order to reliably its manufacturer and the type. This mode is intended for

program the data. After each pulse is applied to a given programming to automatically match the device to be

address, the data in that address is verified. If the data programmed with its corresponding programming algo-

is not verified, additional pulses are given until it is veri- rithm. This mode is functional in the 25°C±5°C ambient

fied or until the maximum number of pulses is reached temperature range that is required when programming

while sequencing through each address of the the HT27LC020.

HT27LC020. This process is repeated while sequenc-

To activate this mode, the programming equipment must

ing through each address of the HT27LC020. This part

of the programming algorithm is done at VCC=6.0V to force 12.0±0.5V on the address line A9 of the

assure that each EPROM bit is programmed to a suffi- HT27LC020. Two identifier bytes may then be sequenced

ciently high threshold voltage. This ensures that all bits from the device outputs by toggling address line A0 from

have sufficient margin. After the final address is com- VIL to VIH, when A1=VIH. All other address lines must be

pleted, the entire EPROM memory is read at held at VIH during Auto Product Identification mode.

VCC=VPP=3.3±0.3V to verify the entire memory. Byte 0 (A0=VIL) represents the manufacturer code, and

byte 1 (A0=VIH), the device code. For HT27LC020, these

Program inhibit mode two identifier bytes are given in the Mode Select Table. All

Programming of multiple HT27LC020 in parallel with differ- identifiers for the manufacturer and device codes will pos-

ent data is also easily accomplished by using the Program sess odd parity, with the MSB (DQ7) defined as the parity

Inhibit Mode. Except for CE, all like inputs of the parallel bit. When A1=VIL, the HT27LC020 will read out the binary

HT27LC020 may be common. A TTL low-level program code of 7F, continuation code, to signify the unavailability

pulse applied to an HT27LC020 CE input with of manufacturer ID codes.

Rev. 1.40 5 November 21, 2002

HT27LC020

Read mode It is recommended that CE be decoded and used as the

The HT27LC020 has two control functions, both of primary device-selection function, while OE be made a

which must be logically satisfied in order to obtain data common connection to the READ line from the system

at outputs. Chip Enable (CE) is the power control and control bus. This assures that all deselected memory

should be used for device selection. Output Enable (OE) devices are in their low-power standby mode and that

is the output control and should be used to gate data to the output pins are only active when data is desired from

the output pins, independent of device selection. As- a particular memory device.

suming that addresses are stable, address access time

System considerations

(tACC) is equal to the delay from CE to output (tCE). Data

is available at the outputs (tOE) after the falling edge of During the switch between active and standby condi-

OE, assuming the CE has been LOW and addresses tions, transient current peaks are produced on the rising

have been stable for at least tACC-tOE. and falling edges of Chip Enable. The magnitude of

these transient current peaks is dependent on the out-

Standby mode put capacitance loading of the device. At a minimum, a

The HT27LC020 has CMOS standby mode which re- 0.1mF ceramic capacitor (high frequency, low inherent

duces the maximum VCC current to 10mA. It is placed in inductance) should be used on each device between

VCC and VPP to minimize transient effects. In addition,

CMOS standby when CE is at V CC ±0.3V. The

to overcome the voltage drop caused by the inductive

HT27LC020 also has a TTL-standby mode which re-

effects of the printed circuit board traces on EPROM ar-

duces the maximum VCC current to 0.6mA. It is placed

in TTL-standby when CE is at VIH. When in standby rays, a 4.7mF bulk electrolytic capacitor should be used

mode, the outputs are in a high-impedance state, inde- between VCC and VPP for each eight devices. The lo-

pendent of the OE input. cation of the capacitor should be close to where the

power supply is connected to the array.

Two-line output control function

To accommodate multiple memory connections, a

two-line control function is provided to allow for:

· Low memory power dissipation

· Assurance that output bus contention will not occur

A d d re s s A d d r e s s V a lid

tC E

C E

tD F

tO E

O E

tA C C tO H

O u tp u t O u tp u t V a lid

H IG H Z

Figure 1. A.C. waveforms for read operation

Rev. 1.40 6 November 21, 2002

HT27LC020

R e a d

P ro g ra m ( V e r ify )

V IH

A d d re s s A d d r e s s S ta b le

V IL

tA S tO E tA H

V IH

D a ta O u t

D a ta D a ta In V a lid

V IL

tD S tD H

6 .0 V

V C C tD F P

5 .0 V

tV C S

1 2 .5 V tV P S

V P P

5 .0 V

tP R T

V IH

C E

V IL

tC E S

V IH

P G M

V IL

tP W tO E S

V IH

O E

V IL

Figure 2. Programming waveforms

Rev. 1.40 7 November 21, 2002

HT27LC020

S T A R T

A d d r e s s = F ir s t L o c a tio n

V C C = 6 .0 V

V P P = 1 2 .5 V

X = 0

P ro g ra m o n e 7 5 s P u ls e

In te r a c tiv e

S e c tio n

In c re m e n t X

Y e s

X = 2 5 ?

N o

F a il V e r ify

B y te ?

P a s s

N o L a s t F a il

In c re m e n t A d d re s s A d d re s s

Y e s

V C C = V P P = 3 .3 V

V e r ify

S e c tio n F a il

V e r ify a ll D e v ic e F a ile d

B y te s ?

P a s s

D e v ic e P a s s e d

N o te : E ith e r 1 0 5 s o r 3 0 s p u ls e .

Figure 3. Fast programming flowchart

Rev. 1.40 8 November 21, 2002

HT27LC020

Package Information

32-pin DIP (600mil) outline dimensions

3 2 1 7

1 1 6

D

= I

E F G

Dimensions in mil

Symbol

Min. Nom. Max.

A 1635 ¾ 1665

B 535 ¾ 555

C 145 ¾ 155

D 125 ¾ 145

E 16 ¾ 20

F 50 ¾ 70

G ¾ 100 ¾

H 595 ¾ 615

I 635 ¾ 670

a 0° ¾ 15°

Rev. 1.40 9 November 21, 2002

HT27LC020

32-pin SOP (450mil) outline dimensions

3 2 1 7

A B

1 1 6

C '

G

D H

=

E F

Dimensions in mil

Symbol

Min. Nom. Max.

A 543 ¾ 557

B 440 ¾ 450

C 14 ¾ 20

C¢ ¾ ¾ 817

D 100 ¾ 112

E ¾ 50 ¾

F 4 ¾ ¾

G 32 ¾ 38

H 4 ¾ 12

a 0° ¾ 10°

Rev. 1.40 10 November 21, 2002

HT27LC020

32-pin TSOP (8´20) outline dimensions

H D

1 3 2

G

E

0 .0 1 0 L

D e ta il F

1 6 1 7

A 2 A

S e e D e ta il F b e A 1

L 1 S y

S e a tin g P la n e

Dimensions in mm

Symbol

Min. Nom. Max.

A ¾ ¾ 1.20

A1 0.05 ¾ 0.15

A2 0.95 ¾ 1.05

b ¾ 0.22 ¾

D 18.30 ¾ 18.50

HD 19.80 ¾ 20.20

E 7.90 ¾ 8.10

e ¾ 0.50 ¾

L ¾ 0.60 ¾

L1 ¾ 0.80 ¾

q 0° ¾ 5°

Rev. 1.40 11 November 21, 2002

HT27LC020

32-pin PLCC outline dimensions

A

B

4 1 3 2 2 9

5 2 8

D C

1 2 2 1

1 3 2 0

K

E F

J G

H

I

Dimensions in mil

Symbol

Min. Nom. Max.

A 485 ¾ 495

B 445 ¾ 455

C 585 ¾ 595

D 545 ¾ 555

E 105 ¾ 115

F ¾ ¾ 140

G 15 ¾ ¾

H ¾ 50 ¾

I 16 ¾ 22

J 24 ¾ 32

K 8 ¾ 12

a 0° ¾ 10°

Rev. 1.40 12 November 21, 2002

HT27LC020

Product Tape and Reel Specifications

Reel dimensions

D

T 2

A B C

T 1

SOP 32W

Symbol Description Dimensions in mm

A Reel Outer Diameter 330±1.0

B Reel Inner Diameter 100±0.1

13.0+0.5

C Spindle Hole Diameter

-0.2

D Key Slit Width 2.0±0.5

32.8+0.3

T1 Space Between Flange

-0.2

T2 Reel Thickness 38.2+0.2

PLCC 32

Symbol Description Dimensions in mm

A Reel Outer Diameter 330±1.0

B Reel Inner Diameter 62±1.5

13.0+0.5

C Spindle Hole Diameter

-0.2

D Key Slit Width 2.0±0.5

24.8+0.3

T1 Space Between Flange

-0.2

T2 Reel Thickness 30.2±0.2

Rev. 1.40 13 November 21, 2002

HT27LC020

Carrier tape dimensions

P 0 P 1 t

D

F

W C B 0

K 1

D 1 P

K 2

A 0

SOP 32W

Symbol Description Dimensions in mm

32.0+0.3

W Carrier Tape Width

-0.1

P Cavity Pitch 16.0±0.1

E Perforation Position 1.75±0.1

F Cavity to Perforation (Width Direction) 14.2±0.1

D Perforation Diameter 1.55+0.1

D1 Cavity Hole Diameter 2.0+0.25

P0 Perforation Pitch 4.0±0.1

P1 Cavity to Perforation (Length Direction) 2.0±0.1

A0 Cavity Length 14.7±0.1

B0 Cavity Width 20.9±0.1

K1 Cavity Depth 3.0±0.1

K2 Cavity Depth 3.4±0.1

t Carrier Tape Thickness 0.35±0.05

C Cover Tape Width 25.5

Rev. 1.40 14 November 21, 2002

HT27LC020

P 0 P 1

D t

F

W

B 0

C

D 1 P

K 0

A 0

PLCC 32

Symbol Description Dimensions in mm

W Carrier Tape Width 24.0±0.3

P Cavity Pitch 18.0±0.1

E Perforation Position 1.75±0.1

F Cavity to Perforation (Width Direction) 11.5±0.1

D Perforation Diameter 1.5+0.1

1.55+1.0

D1 Cavity Hole Diameter

-0.05

P0 Perforation Pitch 4.0±0.1

P1 Cavity to Perforation (Length Direction) 2.0±0.1

A0 Cavity Length 13.1±0.1

B0 Cavity Width 15.5±0.1

K0 Cavity Depth 3.9±0.1

t Carrier Tape Thickness 0.30±0.05

C Cover Tape Width 21.3

Rev. 1.40 15 November 21, 2002

HT27LC020

Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science-based Industrial Park, Hsinchu, Taiwan

Tel: 886-3-563-1999

Fax: 886-3-563-1189

http://www.holtek.com.tw

Holtek Semiconductor Inc. (Sales Office)

11F, No.576, Sec.7 Chung Hsiao E. Rd., Taipei, Taiwan

Tel: 886-2-2782-9635

Fax: 886-2-2782-9636

Fax: 886-2-2782-7128 (International sales hotline)

Holtek Semiconductor (Shanghai) Inc.

7th Floor, Building 2, No.889, Yi Shan Rd., Shanghai, China

Tel: 021-6485-5560

Fax: 021-6485-0313

http://www.holtek.com.cn

Holtek Semiconductor (Hong Kong) Ltd.

RM.711, Tower 2, Cheung Sha Wan Plaza, 833 Cheung Sha Wan Rd., Kowloon, Hong Kong

Tel: 852-2-745-8288

Fax: 852-2-742-8657

Holmate Semiconductor, Inc.

48531 Warm Springs Boulevard, Suite 413, Fremont, CA 94539

Tel: 510-252-9880

Fax: 510-252-9885

http://www.holmate.com

Copyright Ó 2002 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek as-

sumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used

solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable

without further modification, nor recommends the use of its products for application that may present a risk to human life

due to malfunction or otherwise. Holtek reserves the right to alter its products without prior notification. For the most

up-to-date information, please visit our web site at http://www.holtek.com.tw.

Rev. 1.40 16 November 21, 2002

You might also like

- HT27C020Document15 pagesHT27C020wardoyoNo ratings yet

- Terman - Merril: I II III IV X V VI VII Viii IXDocument1 pageTerman - Merril: I II III IV X V VI VII Viii IXGabbsMgNo ratings yet

- SIV 2006 - Semester 2, 20192020 Name: Matric No: SIV180011 / 17189250 - C G A - G CDocument3 pagesSIV 2006 - Semester 2, 20192020 Name: Matric No: SIV180011 / 17189250 - C G A - G CNatashaNo ratings yet

- OptimDocument2 pagesOptimKaic CangussuNo ratings yet

- 18341A05E2 Experiment-6: VCC X1Document1 page18341A05E2 Experiment-6: VCC X1Ashish SrinadhuNo ratings yet

- SchematicsV10 KeysDocument1 pageSchematicsV10 KeysGallego OrtizNo ratings yet

- ADC0809Document5 pagesADC0809Bhaskar Rao PNo ratings yet

- corrector16PF Hombres 2Document16 pagescorrector16PF Hombres 2editarosaNo ratings yet

- AQL Chart: Acceptance Quality Levels (Normal Inspection)Document2 pagesAQL Chart: Acceptance Quality Levels (Normal Inspection)ramnik20098676No ratings yet

- AssignmentsBSA21 B AnswersT1Document2 pagesAssignmentsBSA21 B AnswersT1Gio BurburanNo ratings yet

- Com 111Document3 pagesCom 111benjamin bandaNo ratings yet

- AQLChartDocument2 pagesAQLChartMIGUEL MARTINGNo ratings yet

- AQL Chart: Acceptance Quality Levels (Normal Inspection)Document2 pagesAQL Chart: Acceptance Quality Levels (Normal Inspection)Meylinda Kartika SariNo ratings yet

- Corrector16PF MDocument16 pagesCorrector16PF MrojaskarinaNo ratings yet

- Parcial 2 ProgramacionDocument6 pagesParcial 2 ProgramacionNANTESSNo ratings yet

- The AlphabetDocument2 pagesThe AlphabetPezjmNo ratings yet

- Claves Transf 01Document1 pageClaves Transf 01Tavo Polo RuizNo ratings yet

- PWM2Ballast 0v 10v - Converter PDFDocument1 pagePWM2Ballast 0v 10v - Converter PDFWil VargasNo ratings yet

- HT23C128 CMOS 16K 8-Bit Mask ROM: FeaturesDocument12 pagesHT23C128 CMOS 16K 8-Bit Mask ROM: FeaturesJoséNo ratings yet

- CSE408 Dijkstra, Huffmancoding: Lecture # 27Document52 pagesCSE408 Dijkstra, Huffmancoding: Lecture # 27avinashNo ratings yet

- Examen Final 1Document132 pagesExamen Final 1Angel GarayNo ratings yet

- Fire Panel SLD Circuit PLC CompleteDocument18 pagesFire Panel SLD Circuit PLC CompleteASHISH GORAINo ratings yet

- Ronald Lucero - Assessment Task No. 3Document1 pageRonald Lucero - Assessment Task No. 3danrish tagpisNo ratings yet

- 74lvc07apw q100j BufferDocument14 pages74lvc07apw q100j BuffersatyamNo ratings yet

- Network PlanningDocument6 pagesNetwork PlanningMisael SilooyNo ratings yet

- Installation ManualDocument261 pagesInstallation ManualinkblueNo ratings yet

- PERT AND GANT CORrrrDocument7 pagesPERT AND GANT CORrrrtamfumcknightNo ratings yet

- Painter Requirement: A - Paint First Floor Rooms 8 2 0 8 0Document6 pagesPainter Requirement: A - Paint First Floor Rooms 8 2 0 8 0Sahil TawdeNo ratings yet

- 21bk1a6640 (Ai&ml) - A Egd 2Document1 page21bk1a6640 (Ai&ml) - A Egd 221bk1a6640No ratings yet

- 74AUP1G3208 PhilipsSemiconductorsDocument16 pages74AUP1G3208 PhilipsSemiconductorsCer CerNo ratings yet

- COM111 Assignment 1Document5 pagesCOM111 Assignment 1benjamin bandaNo ratings yet

- Rits-13 Solution With Answer KeyDocument7 pagesRits-13 Solution With Answer KeyComputer GuyNo ratings yet

- Materials Science EngineeringDocument182 pagesMaterials Science EngineeringSaravananNandhuNo ratings yet

- VSP Lec00 PDFDocument10 pagesVSP Lec00 PDFManish ChavdaNo ratings yet

- MCP-03-12-2018 MT-7 Ans Key Sol 12th PDFDocument10 pagesMCP-03-12-2018 MT-7 Ans Key Sol 12th PDFRishi Dey ChowdhuryNo ratings yet

- Solution: Activity Immediate Predecessors DurationDocument5 pagesSolution: Activity Immediate Predecessors DurationherrajohnNo ratings yet

- ReliabilitasDocument8 pagesReliabilitasseptiyonoNo ratings yet

- Table Speed Chapt: Table RPM Table RPM RPM Iugh Range 8 2 1 6 0 19 5Document2 pagesTable Speed Chapt: Table RPM Table RPM RPM Iugh Range 8 2 1 6 0 19 5Tony ZuñigaNo ratings yet

- MK Electronic: Configuration Analyzing (Soft Switch)Document5 pagesMK Electronic: Configuration Analyzing (Soft Switch)Myo KyawNo ratings yet

- IOP Program Description: Use This Short-Form Register Planner or The Full Length Version, As NeededDocument1 pageIOP Program Description: Use This Short-Form Register Planner or The Full Length Version, As Neededjohn@duncancrossNo ratings yet

- Two Equations 1x + 2y 3 Two Unknowns 4x + 5y 6Document21 pagesTwo Equations 1x + 2y 3 Two Unknowns 4x + 5y 6Luton GregoryNo ratings yet

- 1 General Description: 4-To-16 Line Decoder/demultiplexer With Input Latches InvertingDocument14 pages1 General Description: 4-To-16 Line Decoder/demultiplexer With Input Latches InvertingHeroe APNo ratings yet

- 005Document1 page005Abas SumarnaNo ratings yet

- Week5 Analysis of Pipe NetworksDocument16 pagesWeek5 Analysis of Pipe Networkselif sNo ratings yet

- Wio Tracker 1110 v1.0 - SCH - PDF - 20230822Document4 pagesWio Tracker 1110 v1.0 - SCH - PDF - 20230822marcelu.phdNo ratings yet

- Part No. 30HXC130ADocument17 pagesPart No. 30HXC130ACucup Supriatna100% (1)

- 0 A 1 1 2 1 1 2 C 4 2 4 3 2 4 D 6 4 6 4 2 6 I 8 6 8 9 2Document2 pages0 A 1 1 2 1 1 2 C 4 2 4 3 2 4 D 6 4 6 4 2 6 I 8 6 8 9 2Amimah HashifahNo ratings yet

- IT - M3 - 04 - Assembly Lines - ExercisesDocument1 pageIT - M3 - 04 - Assembly Lines - ExercisesMiriam MarchesaniNo ratings yet

- 1920s Printable Escape Room 2Document8 pages1920s Printable Escape Room 2patmcgarry100% (1)

- BS62LV1024: Very Low Power/Voltage CMOS SRAM 128K X 8 BitDocument11 pagesBS62LV1024: Very Low Power/Voltage CMOS SRAM 128K X 8 BitDiego SerranoNo ratings yet

- A A A A A A A A A A: 1.4 Matrix Notation and Matrix MultiplicationDocument15 pagesA A A A A A A A A A: 1.4 Matrix Notation and Matrix MultiplicationMd Nishat HasanNo ratings yet

- FFRDocument1 pageFFRprathyushareddyNo ratings yet

- Epeai 024Document2 pagesEpeai 024li LewisNo ratings yet

- Session 1 Key ShortDocument1 pageSession 1 Key ShortJane XuNo ratings yet

- KeyboardDocument18 pagesKeyboardapi-3721578No ratings yet

- Activity Expected Time Variance 1-2 10 1 1-3 10 0 1-4 5 1 2-6 7 4 3-6 5 1 3-7 7 1 3-5 2 0 4-5 5 1 5-7 8 4 6-7 4 1Document3 pagesActivity Expected Time Variance 1-2 10 1 1-3 10 0 1-4 5 1 2-6 7 4 3-6 5 1 3-7 7 1 3-5 2 0 4-5 5 1 5-7 8 4 6-7 4 1Abdul RazzakNo ratings yet

- ADC0809 With CKT, Flow CodeDocument8 pagesADC0809 With CKT, Flow CodeBhaskar Rao PNo ratings yet

- 8x8 RGB Led Dot MatrixDocument9 pages8x8 RGB Led Dot MatrixAlex Jr SullnNo ratings yet

- CD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)Document16 pagesCD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)vetchboyNo ratings yet

- Audio Tda8567q Spec enDocument20 pagesAudio Tda8567q Spec envetchboyNo ratings yet

- Audio Tda8567q Spec enDocument20 pagesAudio Tda8567q Spec envetchboyNo ratings yet

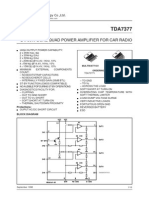

- 2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsDocument10 pages2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsJosé VidalNo ratings yet

- Audio Tda8569q Spec enDocument20 pagesAudio Tda8569q Spec envetchboyNo ratings yet

- Audio Tda8510j Spec enDocument16 pagesAudio Tda8510j Spec envetchboyNo ratings yet

- 4 X 30W Quad Bridge Car Radio Amplifier: Protections: DescriptionDocument12 pages4 X 30W Quad Bridge Car Radio Amplifier: Protections: DescriptionvetchboyNo ratings yet

- Tda 7296Document14 pagesTda 7296Mayra GonzálezNo ratings yet

- 4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionDocument10 pages4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionvetchboyNo ratings yet

- TDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierDocument9 pagesTDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierGerardo Moreno RenteriaNo ratings yet

- Tda 7313Document15 pagesTda 7313jordachadiNo ratings yet

- Digital Controlled Stereo Audio Processor With Loudness: DescriptionDocument14 pagesDigital Controlled Stereo Audio Processor With Loudness: DescriptionvetchboyNo ratings yet

- Dual Btl/Quad Power Amplifier For Car Radio: ProtectionsDocument14 pagesDual Btl/Quad Power Amplifier For Car Radio: ProtectionsvetchboyNo ratings yet

- Tda7294 PDFDocument16 pagesTda7294 PDFRoger NunesNo ratings yet

- 120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyDocument13 pages120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyvetchboyNo ratings yet

- 10W Car Radio Audio Amplifier: DescriptionDocument11 pages10W Car Radio Audio Amplifier: DescriptionvetchboyNo ratings yet

- Tda 7265 2 x25 WDocument12 pagesTda 7265 2 x25 WJavier CanaviriNo ratings yet

- Tda 2004Document11 pagesTda 2004Diana Belen Rodriguez HernandezNo ratings yet

- Tda 7269aDocument7 pagesTda 7269aAlexa DanNo ratings yet

- TDA 2822M CircuitoDocument11 pagesTDA 2822M CircuitoDATA24No ratings yet

- 30W Bridge Car Radio Amplifier: DescriptionDocument10 pages30W Bridge Car Radio Amplifier: DescriptionvetchboyNo ratings yet

- Amplificador 20W RMS TDA2003 Con Placa PCBDocument15 pagesAmplificador 20W RMS TDA2003 Con Placa PCBEnya Andrea Ribba Hernandez100% (5)

- TA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyDocument18 pagesTA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyvetchboyNo ratings yet

- Audio Tda2002 Spec enDocument2 pagesAudio Tda2002 Spec envetchboyNo ratings yet

- TDA1554Q 44W Audio AmplifierDocument11 pagesTDA1554Q 44W Audio Amplifiersava7698No ratings yet

- Audio Tas5100a Spec enDocument15 pagesAudio Tas5100a Spec envetchboyNo ratings yet

- Description: Angus Electronics Company LimitedDocument9 pagesDescription: Angus Electronics Company LimitedvetchboyNo ratings yet

- Low Power Quad Operational Amplifiers: LM124 LM224 - LM324Document13 pagesLow Power Quad Operational Amplifiers: LM124 LM224 - LM324vetchboyNo ratings yet

- STK442 110Document4 pagesSTK442 110Ivan AsimovNo ratings yet

- Description: Angus Electronics Company LimitedDocument13 pagesDescription: Angus Electronics Company LimitedvetchboyNo ratings yet

- Kata LogDocument48 pagesKata LogsofiakeramikNo ratings yet

- Wabco GuideDocument16 pagesWabco GuideMohd FairusNo ratings yet

- 5 Process SynchronizaionDocument58 pages5 Process SynchronizaionLokesh SainiNo ratings yet

- Man D28Document44 pagesMan D28Jorge Barradas Osorno100% (1)

- TEST REPORT After Earth ImprovementDocument3 pagesTEST REPORT After Earth ImprovementShami Mudunkotuwa78% (9)

- Saskatchewan Drivers HandbookDocument175 pagesSaskatchewan Drivers HandbookdrivershandbooksNo ratings yet

- 022-000015B NvcaDocument229 pages022-000015B NvcaCarlos Terraza OyagaNo ratings yet

- Features: Self Reset Auxiliary Flag Relay - Two ElementDocument3 pagesFeatures: Self Reset Auxiliary Flag Relay - Two ElementbledmikifrNo ratings yet

- IRCLASS Systems and Solutions Pvt. Ltd. (A Wholy Owned Subsidiary of Indian Register of Shipping)Document4 pagesIRCLASS Systems and Solutions Pvt. Ltd. (A Wholy Owned Subsidiary of Indian Register of Shipping)Mostafizur RahmanNo ratings yet

- Compare Models - RitchieSpecsDocument4 pagesCompare Models - RitchieSpecsMochammad JihadNo ratings yet

- Sbi Clerk MainsDocument4 pagesSbi Clerk MainspurushothamNo ratings yet

- York Ducted Split Ac Yefe 18-48Document6 pagesYork Ducted Split Ac Yefe 18-48DANISH0% (1)

- Water Cooled Chiller (SHUBAILY GRAND MALL)Document40 pagesWater Cooled Chiller (SHUBAILY GRAND MALL)kdpmansiNo ratings yet

- 20e - cTI-60t - TI Pin Converter: Blackhawk™ Jtag Pin ConvertersDocument2 pages20e - cTI-60t - TI Pin Converter: Blackhawk™ Jtag Pin ConvertersvspuriNo ratings yet

- Intro To Neutron ScatteringDocument191 pagesIntro To Neutron ScatteringEleni MitsiNo ratings yet

- Camera Tubes NDocument30 pagesCamera Tubes NRamakrishna VadlamudiNo ratings yet

- Open IVDocument84 pagesOpen IVSokr AbdoNo ratings yet

- EC160B/180B/210B/240B/290B/360B/460B: Click The Volvo-Logo in The Lower Right Corner To Return To This Menu Main MenuDocument31 pagesEC160B/180B/210B/240B/290B/360B/460B: Click The Volvo-Logo in The Lower Right Corner To Return To This Menu Main MenuMACHINERY101GEAR97% (71)

- Bicmos InvertersDocument10 pagesBicmos InvertersLily SharmaNo ratings yet

- Cs Acrovyn CatalogueDocument83 pagesCs Acrovyn CatalogueBoboc AndreiNo ratings yet

- Maxwell v16 2DDocument10 pagesMaxwell v16 2Ddesi_parisNo ratings yet

- Falcon BMS Keyfile Manual PDFDocument37 pagesFalcon BMS Keyfile Manual PDFAlessandro MigliardiNo ratings yet

- Practical Application of Pervious Concrete - Mix Designs That Are WorkableDocument20 pagesPractical Application of Pervious Concrete - Mix Designs That Are WorkablePJ FlexirNo ratings yet

- Q - Bae146 Inventory - SSS-Jan 2010Document6 pagesQ - Bae146 Inventory - SSS-Jan 2010sssavNo ratings yet

- NE5521Document9 pagesNE5521Carlos TibussiNo ratings yet

- Report of Elevator ControllerDocument36 pagesReport of Elevator ControllerSagar G Reddy100% (1)

- Structured Text CheatsheetDocument1 pageStructured Text CheatsheetMauricio Rodriguez0% (1)

- Calculating The Volume of A Stainless Steel WeldDocument6 pagesCalculating The Volume of A Stainless Steel WeldOkayNo ratings yet

- Computer Graphics - Lesson PlanDocument15 pagesComputer Graphics - Lesson PlansoniadrallNo ratings yet

- Kiln Performance - Efficiency FormulasDocument12 pagesKiln Performance - Efficiency FormulasMohamed ZayedNo ratings yet