Professional Documents

Culture Documents

VHDL BASYS Example62-TrafficLights PDF

VHDL BASYS Example62-TrafficLights PDF

Uploaded by

JamesMatthewWongOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VHDL BASYS Example62-TrafficLights PDF

VHDL BASYS Example62-TrafficLights PDF

Uploaded by

JamesMatthewWongCopyright:

Available Formats

Traffic Lights

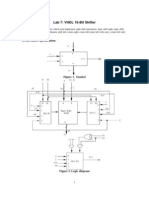

Example 62: Traffic Lights

It is often useful to be able to sequence through an arbitrary number of states,

staying in each state an arbitrary amount of time. For example, consider the set of traffic

lights shown in Figure 8.13. The lights are assumed to be at a four-way intersection with

one street going north-south and the other road going east-west.

Red

Red

Yellow

Yellow

Green

Green

North - South

East - West

Figure 8.13 Six colored LEDs can represent a set of traffic lights

To simulate these traffic lights we will use the red, yellow, and green LEDs

connected to ld(7:2) on the BASYS board and cycle through the six states shown in

Table 8.2. A state diagram for controlling these traffic lights is shown in Fig. 8.14. If we

use a 3 Hz clock to drive this state diagram then a delay of 1 second is achieved by

staying in a state for three clock cycles. Similarly, a delay of 5 second is achieved by

staying in a state for fifteen clock cycles. The count variable in Fig. 8.14 will be reset to

zero when moving to the next state after a timeout.

Listing 8.6 is a VHDL program that implements the state diagram in Fig. 8.14 and

its simulation is shown in Fig. 8.15. Because we need a counter for the delay count it is

more convenient in this case to combine the state register and combinational modules C1

in the Moore machine in Fig. 8.3 into a single sequential process as shown in Listing 8.6.

Note in this case we use only a single state variable.

To generate the 3 Hz signal we will use the version of clkdiv shown in Listing 8.7.

The top-level VHDL program is given in Listing 8.8.

State

0

1

2

3

4

5

Table 8.2 Traffic Light States

North - South

East - West

Green

Red

Yellow

Red

Red

Red

Red

Green

Red

Yellow

Red

Red

Delay (sec.)

5

1

1

5

1

1

Example 62

count < 15

S0

count < 3

count < 3

S5

S1

S4

S2

count < 3

count < 3

S3

count < 15

Figure 8.14 State diagram for controlling traffic lights

Figure 8.15 Simulation of the VHDL program in Listing 8.4

Traffic Lights

Listing 8.6 traffic.vhd

-- Example 62: traffic lights

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_unsigned.all;

entity traffic is

port (clk: in STD_LOGIC;

clr: in STD_LOGIC;

lights: out STD_LOGIC_VECTOR(5 downto 0));

end traffic;

architecture traffic of traffic is

type state_type is (s0, s1, s2, s3, s4, s5);

signal state: state_type;

signal count: STD_LOGIC_VECTOR(3 downto 0);

constant SEC5: STD_LOGIC_VECTOR(3 downto 0) := "1111";

constant SEC1: STD_LOGIC_VECTOR(3 downto 0) := "0011";

begin

process(clk, clr)

begin

if clr = '1' then

state <= s0;

count <= X"0";

elsif clk'event and clk = '1' then

case state is

when s0 =>

if count < SEC5 then

state <= s0;

count <= count + 1;

else

state <= s1;

count <= X"0";

end if;

when s1 =>

if count < SEC1 then

state <= s1;

count <= count + 1;

else

state <= s2;

count <= X"0";

end if;

when s2 =>

if count < SEC1 then

state <= s3;

count <= count + 1;

else

state <= s3;

count <= X"0";

end if;

Example 62

Listing 8.6 (cont.) traffic.vhd

when s3 =>

if count < SEC5 then

state <= s3;

count <= count + 1;

else

state <= s4;

count <= X"0";

end if;

when s4 =>

if count < SEC1 then

state <= s4;

count <= count + 1;

else

state <= s5;

count <= X"0";

end if;

when s5 =>

if count < SEC1 then

state <= s5;

count <= count + 1;

else

state <= s0;

count <= X"0";

end if;

when others =>

state <= s0;

end case;

end if;

end process;

C2: process(state)

begin

case state is

when s0 => lights <= "100001";

when s1 => lights <= "100010";

when s2 => lights <= "100100";

when s3 => lights <= "001100";

when s4 => lights <= "010100";

when s5 => lights <= "100100";

when others => lights <= "100001";

end case;

end process;

end traffic;

Traffic Lights

Listing 8.7 clkdiv.vhd

-- Example 52: clock divider

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_unsigned.all;

entity clkdiv is

port(

mclk : in STD_LOGIC;

clr : in STD_LOGIC;

clk190 : out STD_LOGIC;

clk3 : out STD_LOGIC

);

end clkdiv;

architecture clkdiv of clkdiv is

signal q:STD_LOGIC_VECTOR(24 downto 0);

begin

-- clock divider

process(mclk, clr)

begin

if clr = '1' then

q <= X"000000" & '0';

elsif mclk'event and mclk='1' then

q <= q + 1;

end if;

end process;

clk3 <= q(24); -- 3 Hz

clk190 <= q(18);

-- 190 H

end clkdiv;

Listing 8.8 traffic_lights_top.vhd

-- Example 62: traffic_lights_top

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity traffic_lights_top is

port(

clk : in STD_LOGIC;

btn : in STD_LOGIC_VECTOR(3 downto 3);

ld : out STD_LOGIC_VECTOR(7 downto 2)

);

end traffic_lights_top;

architecture traffic_lights_top of traffic_lights_top is

component clkdiv is

port(

mclk : in STD_LOGIC;

clr : in STD_LOGIC;

clk190 : out STD_LOGIC;

clk3 : out STD_LOGIC

);

end component;

Example 62

Listing 8.8 (cont.) traffic_lights_top.vhd

component traffic is

port (clk: in STD_LOGIC;

clr: in STD_LOGIC;

lights: out STD_LOGIC_VECTOR(5 downto 0));

end component;

signal clr, clk3: STD_LOGIC;

begin

clr <= btn(3);

U1: clkdiv

port map (

mclk=>clk,

clr=>clr,

clk3=>clk3

);

U2: traffic

port map (

clk=>clk3,

clr=>clr,

lights=>ld

);

end traffic_lights_top;

You might also like

- Promethean The Created - Pandoras BookDocument162 pagesPromethean The Created - Pandoras BookItzhakEven100% (5)

- Facebook Ads TemplateDocument10 pagesFacebook Ads TemplateKasnopichNo ratings yet

- Find Your Partner As Per NumerologyDocument6 pagesFind Your Partner As Per NumerologyDilip Kininge100% (1)

- Control of DC Motor Using Different Control StrategiesFrom EverandControl of DC Motor Using Different Control StrategiesNo ratings yet

- Argillaceous Rock AtlasDocument146 pagesArgillaceous Rock Atlasyaku1618No ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- VHDL UartDocument53 pagesVHDL UartEhsan Mahdavi100% (1)

- Consolidated Drained Direct Shear Test: (IS: 2720 (Part 13) - 1986)Document1 pageConsolidated Drained Direct Shear Test: (IS: 2720 (Part 13) - 1986)Biplab dattaNo ratings yet

- Register Transfer Methodology: PracticeDocument54 pagesRegister Transfer Methodology: PracticeSrinivas CherukuNo ratings yet

- 115 - Myers, Hansen - Experimental Psychology - 7th Ed PDFDocument637 pages115 - Myers, Hansen - Experimental Psychology - 7th Ed PDFHillary Fajutagana73% (15)

- FPGA Temp SensorDocument8 pagesFPGA Temp SensorRajan BhartiNo ratings yet

- Stop Watch Coding (VHDL)Document15 pagesStop Watch Coding (VHDL)Anonymous ZCb9xz100% (1)

- Program Benefits Management-1Document113 pagesProgram Benefits Management-1kk6969No ratings yet

- Verilog BASYS Example62-TrafficLightsDocument5 pagesVerilog BASYS Example62-TrafficLightsਸ. ਇੰਦਰਦੀਪ ਸਿੰਘ100% (1)

- Tutorial For Running A Stepper-Motor Using Krypton Board (Wel - Lab, Iit Bombay)Document12 pagesTutorial For Running A Stepper-Motor Using Krypton Board (Wel - Lab, Iit Bombay)Chiquita WhiteNo ratings yet

- State Graphs For Control NetworksDocument37 pagesState Graphs For Control Networksashudiya100% (1)

- Digital PID Controllers: Different Forms of PIDDocument11 pagesDigital PID Controllers: Different Forms of PIDสหายดิว ลูกพระอาทิตย์No ratings yet

- An Integer Square Root Algorithm: Example 24Document10 pagesAn Integer Square Root Algorithm: Example 24psomasalNo ratings yet

- Lab 13Document11 pagesLab 13ubaidNo ratings yet

- Fr6 FSM PassDocument67 pagesFr6 FSM PassMitroi ȘtefanNo ratings yet

- Examples of Finite State Machines (FSMS) : Counters and Pattern GeneratorsDocument71 pagesExamples of Finite State Machines (FSMS) : Counters and Pattern GeneratorsflowarNo ratings yet

- Design Example 5.5Document10 pagesDesign Example 5.5MaheshNo ratings yet

- VHDL in An HourDocument28 pagesVHDL in An HouranjugaduNo ratings yet

- Examples of Finite State Machines (FSMS) : Counters and Pattern GeneratorsDocument71 pagesExamples of Finite State Machines (FSMS) : Counters and Pattern GeneratorsArif Sumardiono100% (1)

- In Class - Finite State Machine ExamplesDocument30 pagesIn Class - Finite State Machine ExamplesAnonymous pcanQ3No ratings yet

- Pico VHDLDocument6 pagesPico VHDLapi-584316598No ratings yet

- Group-08 LabDocument10 pagesGroup-08 LabRogersNo ratings yet

- AtoD Converter System S12 NewDocument9 pagesAtoD Converter System S12 NewMina HannaNo ratings yet

- Quadrature EncoderDocument5 pagesQuadrature EncoderJaime Santiago Sanchez ReinosoNo ratings yet

- Synchronous Derived Clock and Synthesis of Low Power Sequential CircuitsDocument7 pagesSynchronous Derived Clock and Synthesis of Low Power Sequential CircuitsChaitanya ChavaNo ratings yet

- Interface Verilog CodeDocument21 pagesInterface Verilog CodeVishwanath B RajashekarNo ratings yet

- Digital Design 2 Lab: An-Najah UniversityDocument17 pagesDigital Design 2 Lab: An-Najah UniversitySudqi JawabrehNo ratings yet

- ADT7420 Codigo LibroDocument4 pagesADT7420 Codigo LibroAPRENDE LO QUE APRENDONo ratings yet

- Digital System Design Example 1: GCD Calculator: Start Signal, Which Commences The Computation ProcessDocument31 pagesDigital System Design Example 1: GCD Calculator: Start Signal, Which Commences The Computation ProcessEMJAYNo ratings yet

- Bai 15 - ADC and DAC On Spartan 3E Starter BoardDocument6 pagesBai 15 - ADC and DAC On Spartan 3E Starter BoardNguyễn Hữu DuyNo ratings yet

- New Text DocumentDocument8 pagesNew Text DocumentMuneeb AhmadNo ratings yet

- CSE 260 ExamDocument10 pagesCSE 260 ExammaddogmljNo ratings yet

- DGD 9 SolDocument9 pagesDGD 9 SolDolores Makaruina100% (1)

- H-Bridge Motor ControlDocument9 pagesH-Bridge Motor ControlSamSharmaNo ratings yet

- Beng Hons Electrical & Electronic EngineeringDocument12 pagesBeng Hons Electrical & Electronic EngineeringmohammedNo ratings yet

- Lab 14Document10 pagesLab 14ubaidNo ratings yet

- DC Motor Speed: Digital Controller Design: Eng Mohamed DobaDocument20 pagesDC Motor Speed: Digital Controller Design: Eng Mohamed DobaEng. Ibrahim Abdullah AlruhmiNo ratings yet

- Brushless DC Electric Motor Control by CPLDDocument6 pagesBrushless DC Electric Motor Control by CPLDIonela100% (3)

- Traffic Light ControlDocument5 pagesTraffic Light ControlRohit KadlagNo ratings yet

- Design of Fuzzy Sliding Mode Control For DC-DC ConverterDocument6 pagesDesign of Fuzzy Sliding Mode Control For DC-DC ConverterXime Mendez FloresNo ratings yet

- Emb 2Document7 pagesEmb 2ballmerNo ratings yet

- Lab 7: VHDL 16-Bit ShifterDocument6 pagesLab 7: VHDL 16-Bit ShifterAvinash VikramNo ratings yet

- Dcs-Ii Lab File: - Anupam Sobti 17/EC/09Document19 pagesDcs-Ii Lab File: - Anupam Sobti 17/EC/09Ankit GoelNo ratings yet

- Lec 5Document18 pagesLec 5Saad ShaikhNo ratings yet

- FPGA Lab 13 TasksDocument2 pagesFPGA Lab 13 TasksKamran KhanNo ratings yet

- Lab 04Document6 pagesLab 04Bodour MohamedNo ratings yet

- Actividad 2. Comparativo de Circuitos DigitalesDocument7 pagesActividad 2. Comparativo de Circuitos DigitalesMutante Genrri100% (1)

- Heartbeat Monitor Using AT89C51Document5 pagesHeartbeat Monitor Using AT89C51Nalini Radhakrishnan0% (1)

- Evl 104 Vlsi Design Lab-I: Ex - No:1 Modeling of Sequential Digital Systems Using VHDLDocument34 pagesEvl 104 Vlsi Design Lab-I: Ex - No:1 Modeling of Sequential Digital Systems Using VHDLvijithacvijayanNo ratings yet

- Unit 3Document24 pagesUnit 3Raja BenitaNo ratings yet

- McpuDocument6 pagesMcputpsa6668No ratings yet

- GPS Receiver Using 8051 Micro ControllerDocument9 pagesGPS Receiver Using 8051 Micro Controllercamelya_tudorNo ratings yet

- PID Analitico Conversor BuckDocument8 pagesPID Analitico Conversor BuckOdair TrujilloNo ratings yet

- Part 1 - FSM DesignDocument3 pagesPart 1 - FSM DesignMENANI ZineddineNo ratings yet

- Modulo-N Counters: Module M10.4 Section 7.2Document27 pagesModulo-N Counters: Module M10.4 Section 7.2Jeffry MarzellieNo ratings yet

- Ejemplos VHDLDocument5 pagesEjemplos VHDLLeón Emmanuel NNo ratings yet

- Lab Manual 10Document8 pagesLab Manual 10ThoughtsNo ratings yet

- Advanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkFrom EverandAdvanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkNo ratings yet

- Advanced Multilevel Converters and Applications in Grid IntegrationFrom EverandAdvanced Multilevel Converters and Applications in Grid IntegrationAli Iftekhar MaswoodNo ratings yet

- Power Systems-On-Chip: Practical Aspects of DesignFrom EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNo ratings yet

- Model Predictive Control of High Power Converters and Industrial DrivesFrom EverandModel Predictive Control of High Power Converters and Industrial DrivesNo ratings yet

- Lean Six Sigma Green Belt: TrainingDocument36 pagesLean Six Sigma Green Belt: TrainingRajkumar VijNo ratings yet

- Hold Down Guide On Saddle For Pipes " - 68" NPS: Pipe Standard SupportsDocument3 pagesHold Down Guide On Saddle For Pipes " - 68" NPS: Pipe Standard SupportsMainuddin AliNo ratings yet

- SSC JE 2023 Electrical EngineeringDocument65 pagesSSC JE 2023 Electrical Engineeringgamers die hardersNo ratings yet

- 8359 BDDocument7 pages8359 BDEduard KönigNo ratings yet

- Types of Parenting Styles and Effects On Children - StatPearls - NCBI BookshelfDocument4 pagesTypes of Parenting Styles and Effects On Children - StatPearls - NCBI BookshelfAna BarbosaNo ratings yet

- EMA Process ValidationDocument15 pagesEMA Process Validationdr3azzamNo ratings yet

- Dynamic Modeling of Gearbox Faults: A Review: Mechanical Systems and Signal Processing January 2018Document26 pagesDynamic Modeling of Gearbox Faults: A Review: Mechanical Systems and Signal Processing January 2018coroNo ratings yet

- POOCHDocument2 pagesPOOCHAmy ZhangNo ratings yet

- Endogenic and Exogenic ProcessesDocument13 pagesEndogenic and Exogenic ProcessesJohndee Mozart Dela CruzNo ratings yet

- Faculty and Staff Meeting-ChineseDocument3 pagesFaculty and Staff Meeting-ChineseMargaux Faith CCNo ratings yet

- Research ProposalDocument8 pagesResearch Proposalpearson cosmasNo ratings yet

- H & P Phrases PDFDocument13 pagesH & P Phrases PDFASISTENCIA GENERALNo ratings yet

- Materi 6 Teori Kinetik Versi Bhs InggrisDocument7 pagesMateri 6 Teori Kinetik Versi Bhs InggrisNur Budi SetiawanNo ratings yet

- Assignment 1 BMK20103Document8 pagesAssignment 1 BMK20103snekha 2412No ratings yet

- What Do You WhatDocument22 pagesWhat Do You WhatSaikat SenguptaNo ratings yet

- Analysis of Moral Value in The Martian MovieDocument11 pagesAnalysis of Moral Value in The Martian MovieFay FaizahNo ratings yet

- Mit Statement of PurposeDocument3 pagesMit Statement of Purposeapi-434089240No ratings yet

- M.e.estDocument2 pagesM.e.estShiyamala JeyakumarNo ratings yet

- Co-Hoc-Vat-Ran-Bien-Dang - T.-Nguyen-Thoi-,-T.-Vo-Duy - Chapter - 4 - New-Material-Behavior - Linear-Elastic-Solid - (Cuuduongthancong - Com)Document27 pagesCo-Hoc-Vat-Ran-Bien-Dang - T.-Nguyen-Thoi-,-T.-Vo-Duy - Chapter - 4 - New-Material-Behavior - Linear-Elastic-Solid - (Cuuduongthancong - Com)19020852 Lường Thị QuyênNo ratings yet

- Color Theory: Primary Colors Quiz Secondary ColorsDocument40 pagesColor Theory: Primary Colors Quiz Secondary ColorsnurNo ratings yet

- Unit Guidance and Counselling in Nursing: EducationDocument22 pagesUnit Guidance and Counselling in Nursing: EducationRinchin ChhotenNo ratings yet

- TransformersDocument2 pagesTransformersNithya GowdaNo ratings yet

- BPS4102 Syllabus 2020 PDFDocument2 pagesBPS4102 Syllabus 2020 PDFMohamed HussainNo ratings yet