Professional Documents

Culture Documents

01 Abstraction Levels in The Digital System Modeling

01 Abstraction Levels in The Digital System Modeling

Uploaded by

TejaRam AugusthyaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

01 Abstraction Levels in The Digital System Modeling

01 Abstraction Levels in The Digital System Modeling

Uploaded by

TejaRam AugusthyaCopyright:

Available Formats

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Budapest University of Technology and Economics

Abstraction Levels in the Digital System Modeling

Dr. Péter Horváth

Department of Electron Devices

February 8, 2017

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 1 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Contents

Contents

handling complexity – abstraction levels in digital system modeling

the Gajski-Kuhn Y-diagram – function representations, modeling

means, structural elements

a detailed discussion of the different abstraction levels and their

optimization goals

design flow of digital systems

top-down and bottom-up design approaches

top-down and bottom-up methods in digital design

a detailed discussion of the digital system design flow – from the

viewpoint of the system designer

additional readings

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 2 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Handling complexity –

Abstraction levels

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 3 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

The Gajski-Kuhn Y-diagram

The Gajski-Kuhn Y-diagram

The GK diagram is an expressive representation of the abstraction

levels.

The circles represent the abstraction levels and the arrows represent

the aspects they are examined from.

register transfers

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 4 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Abstraction levels

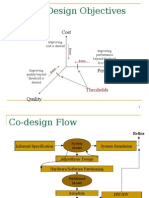

Design objectives on the different abstraction levels

System – defining design partitions and their interfaces

Algorithm – behavioral modeling with high-level programming

languages

RTL (register-transfer level) – defining "microarchitecture",

separating control and datapath

Gate – defining the behavior of RTL components with Boole-

equations

Circuit – implementing the behavior of the logic gates with

transistor-based structures

Device – constructing small, fast, and low-power transistors

Technology – optimizing the technology parameters that influence

the device construction

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 5 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Abstraction levels

System-level

The main objective is to define the partitions of the system and the

communication methods and interfaces between the partitions and

the outside world.

The object-oriented paradigm is widely used in system-level design.

design entity examples: GPCPU1 , GPGPU2 , DSP3 , memory (cache,

operative memory, mass storage), I/O subsystem, peripheral

controller

considerations on system-level

number of the microprocessors

topology of the memory subsystem in multiprocessor systems

memory hierarchy (cache levels and sizes)

communication models (hand-shake, mailbox, FIFO etc.)

1 general-purpose central processing unit

2 general-purpose graphics processing unit

3 digital signal processor

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 6 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Abstraction levels

Algorithm-level

High-level programming language representation of the

subsystems’ behavior.

Once the algorithm-level implementations of the subsystems are

created, the system can be simulated.

The simulation requires high computation capacity, therefore the

efficiencies of the algorithmic models are critical. The most widely

used tools for algorithmic modeling are native C and C++,

supplemented by a set of hardware-oriented class libraries.

algorithm-level (C++) model of a simple RC filter

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 7 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Abstraction levels

RTL – register-transfer level

The objective of RTL is to describe the data transfers and their

timing between simple functional units with (registers, register files,

arithmetic-logic units etc.)

Separating datapath and control; the datapath includes the

functional units and their interconnections. The control unit

generates control signals with appropriate timing.

data

control inputs

unit

considerations on RTL control

control: single-cycle, multicycle, signals

control

pipeline I/O

internal data-storage structures

(registers, register files)

clocking scheme: frequency, phase

status

signals signal

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 8 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Abstraction levels

Gate-level

All digital functions – even those containing data storage – can be

represented by a set of interconnected logic gates. Although the

elementary data-storage elements (flip-flops) can be described with

gates, they are considered basic building blocks of gate-level models,

because they have a unique physical realization primitive (they are

not implemented as interconnected logic gates).

considerations on gate-level

handling logical hazards

two-level or multilevel logic realization

gate-level architecture optimization of functional units (e.g. adder:

ripple-carry vs. carry lookahead)

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 9 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Abstraction levels

Circuit-level

The functionality of a logic gate can be realized by interconnected

transistors. This circuit-level model is a "standard cell".

representations of a standard cell

schematic: a logical network of transistors

layout: a physical realization of the schematic

To simulate a circuit-level

model, the mathematical

models of the transistors (e.g.

Ebers-Moll, Gummel-Poon,

EKV, BSIM3) are required.

considerations on circuit-level

circuit family (ECL, SCL,

static/dynamic CMOS)

topology (e.g. domino

CMOS: alternate/pipeline)

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 10 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Abstraction levels

Device-level

To improve the computation capacity, power consumption, and

device density of the digital circuits, we need small, fast, and

efficient transistors. The aim of device-level is to optimize the

transistor parameters.

considerations on device-level

threshold voltage, switching

frequency, power

consumption, size etc.

scaling: short-channel and

strait-channel effects,

hot-electron effect,

gate-depletion, latch-up,

preventing or exploiting

quantum-effects (HKMG,

EEPROM)

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 11 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Abstraction levels

Technology-level

The aim of technology-level optimization is to analyze the effect of

technological parameters on the physical indices influencing the

device characteristics.

Technological parameters: temperature and duration of diffusion,

energy of implantation, etc.

Physical indices: oxide thickness, conductivity, carrier lifetime and

mobility, dopant density and distribution, etc.

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 12 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Design flow of digital systems

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 13 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Top-down and bottom-up design approaches

Top-down design method

In the top-down approach the design process starts with a high-level

representation of the system. The high-level model includes

partitions (subsystems) with a specific task. During the design

process the implementations of the subsystems are elaborated; they

are split into components with more specific sub-tasks and more

detailed implementations. The process stops when the components

of the refined design are simple enough to substitute them with an

existing model (practically with an RTL functional unit).

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 14 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Top-down and bottom-up design approaches

Bottom-up design method

In the bottom-up approach the designer creates basic functional

units with very simple tasks. Once a sufficient set of elementary

functionalities is constructed, a more complex model can be

prepared with the combination of the simple ones. The design

process stops when the increasingly complex model is able to

implement the desired functionality defined in the specification.

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 15 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Top-down and bottom-up design approaches

Top-down and bottom-up methods in digital design

In the digital design the top-down and the bottom-up methods

are both applied. The system designer creates RTL models from

the high-level specification with top-down method but the standard

cells are constructed from circuit-level by the component library

designer with bottom-up approach.

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 16 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Digital system design flow – from the viewpoint of the system designer

Step #1. Design partitioning (manual)

concept: The subsystems, their relations and interfaces have to be

outlined. The subsystems are represented as "black boxes".

tools: UML, SystemC TLM4 , MATLAB

specification

4 transaction-level modeling; a C++ class library for system-level modeling

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 17 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Digital system design flow – from the viewpoint of the system designer

Step #2. Functional modeling (manual)

concept: The behavior of the subsystems have to be formulated.

tools: high-level programming languages (C, C++, SystemC)

functional model (C++)

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 18 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Digital system design flow – from the viewpoint of the system designer

Step #3. RTL design (manual/automated)

concept: A microarchitecture consisting of simple functional units

(registers, register files, arithmetic units, etc.) has to be constructed.

tools: hardware description languages (VHDL, Verilog, SystemC)

functional model

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 19 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Digital system design flow – from the viewpoint of the system designer

Step #4. RTL optimization (manual/automated)

concept: There are many microarchitectures implementing the same

functionality. We have to choose one with parameters optimal for

the application.

tools: hardware description languages (VHDL, Verilog, SystemC)

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 20 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Digital system design flow – from the viewpoint of the system designer

Step #5. Logic synthesis (automated)

concept: The RTL description is automatically transformed into a

technology and vendor-independent gate-level model.

tools: ISE, Quartus II, LeonardoSpectrum, Precision, Encounter

RTL Compiler

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 21 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Digital system design flow – from the viewpoint of the system designer

Step #6. Mapping (automated)

concept: The mapping assigns a specific component library

primitive to the generic resources of the gate-level model. These

library primitives are the basic elements of an ASIC technology (e.g.

AMS 0.35) or an FPGA device family (e.g. Xilinx Spartan3E).

tools: ISE, Quartus II, LeonardoSpectrum, Precision, Virtuoso,

Calibre InRoute

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 22 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Digital system design flow – from the viewpoint of the system designer

Step #7. Place & route (automated)

concept: Place: The mapped primitives are assigned to a specific

resource in a device (FPGA) or they are placed into a specific

position of the chip layout (ASIC). Route: The interconnections of

the placed primitives are constructed. The output of the design flow

is a GDSII file (ASIC) including the information required for

manufacturing or a bitstream file (FPGA) including the

configuration memory content of the FPGA device.

tools: ISE, Quartus II, Virtuoso, Calibre InRoute

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 23 / 24

Contents Handling complexity – Abstraction levels Design flow of digital systems Additional readings

Additional readings

Additional readings

David Money Harris, Sarah L. Harris – Digital Design and Computer

Architecture

Peter J. Ashenden – Digital Design – An Embedded System

Approach Using VHDL

M. Moris Mano, Charles R. Kime – Logic and Computer Design

Fundamentals

Pong P. Chu – RTL Hardware Design Using VHDL

Thorsten Grötker, Stan Liao, Grant Martin, Stuart Swan – System

Design with SystemC

Dr. Péter Horváth Abstraction Levels in the Digital System Modeling 24 / 24

You might also like

- Can People Change? - Bradford and HuckabayDocument4 pagesCan People Change? - Bradford and HuckabaysiriNo ratings yet

- Manufacturing Execution System (MES) : Deployment GuideDocument47 pagesManufacturing Execution System (MES) : Deployment GuideNhat Tan MaiNo ratings yet

- Mercedes Wis Epc Installation Guide PDFDocument3 pagesMercedes Wis Epc Installation Guide PDFDonald SchmitterNo ratings yet

- Vit Ece 5th Year SyllabusDocument16 pagesVit Ece 5th Year Syllabuspranavateja12399No ratings yet

- Design Flow OverviewDocument9 pagesDesign Flow OverviewJubin JainNo ratings yet

- Chapter 1 Introduction To Digital Systems: Design RepresentationsDocument5 pagesChapter 1 Introduction To Digital Systems: Design RepresentationstrungNo ratings yet

- Digital Design Through Verilog PDFDocument68 pagesDigital Design Through Verilog PDFSammed UpadhyeNo ratings yet

- SoC Design - A ReviewDocument131 pagesSoC Design - A ReviewSambhav VermanNo ratings yet

- Simplified FPGA Design Implementation FlowDocument36 pagesSimplified FPGA Design Implementation FlowRajendra PrasadNo ratings yet

- Fpga Based 32 Bit Risc Processor DesignDocument18 pagesFpga Based 32 Bit Risc Processor DesignAchit YadavNo ratings yet

- Physical DesignDocument12 pagesPhysical DesignPallavi ChNo ratings yet

- Synopsis Master of Technology IN Vlsi Design: Ims Engineering College, GhaziabadDocument9 pagesSynopsis Master of Technology IN Vlsi Design: Ims Engineering College, GhaziabadAnubhav SinghalNo ratings yet

- Digital Design and SynthesisDocument45 pagesDigital Design and Synthesisvirat sharmaNo ratings yet

- Microcontroller Architecture and Organization: Unit IDocument6 pagesMicrocontroller Architecture and Organization: Unit IhemanthdreamzNo ratings yet

- DSD NotesDocument5 pagesDSD NoteshkrohillaNo ratings yet

- CpE321L Lesson 1 - Introduction To IC Design and HDLDocument38 pagesCpE321L Lesson 1 - Introduction To IC Design and HDLSebastian KarlNo ratings yet

- EEDG/CE 6301: Advanced Digital Logic: Mehrdad NouraniDocument44 pagesEEDG/CE 6301: Advanced Digital Logic: Mehrdad NouraniGowtham HariNo ratings yet

- Digital Design Through Verilog-18 PDFDocument31 pagesDigital Design Through Verilog-18 PDFAnanth G NNo ratings yet

- System-Level Design Introduction To Digital System Design: Ali Kareem Abdulrazzaq September 6, 2021Document15 pagesSystem-Level Design Introduction To Digital System Design: Ali Kareem Abdulrazzaq September 6, 2021Lưu HảiNo ratings yet

- System Synthesis of Digital Systems: Petru Eles, Zebo PengDocument14 pagesSystem Synthesis of Digital Systems: Petru Eles, Zebo PengRajni YadavNo ratings yet

- Eee646 Fpga-based-system-Design Ela 2.00 Ac29Document2 pagesEee646 Fpga-based-system-Design Ela 2.00 Ac29Ranjith M KumarNo ratings yet

- Automated Solution For Data Monitoring (Dashboard) of ASIC Design FlowDocument4 pagesAutomated Solution For Data Monitoring (Dashboard) of ASIC Design FlowseventhsensegroupNo ratings yet

- System On Chip Design and ModellingDocument131 pagesSystem On Chip Design and ModellingGurram KishoreNo ratings yet

- CADocument4 pagesCAOneirosVasNo ratings yet

- Computer Architecture AllClasses-Outline-1-99Document99 pagesComputer Architecture AllClasses-Outline-1-99SrinivasaRaoNo ratings yet

- Computer Architecture AllClasses-OutlineDocument294 pagesComputer Architecture AllClasses-OutlineSrinivasaRaoNo ratings yet

- Review: Design Objectives: ThresholdsDocument19 pagesReview: Design Objectives: ThresholdsSahadev RoyNo ratings yet

- The Guider System For Classical Controller DesignDocument5 pagesThe Guider System For Classical Controller DesignEsmael FloresNo ratings yet

- Logic Synthesis and Verification: Course InfoDocument7 pagesLogic Synthesis and Verification: Course InfoManisha JadavNo ratings yet

- CA Classes-1-5Document5 pagesCA Classes-1-5SrinivasaRaoNo ratings yet

- Co Unit 1Document146 pagesCo Unit 1Adivardhan Akash MaheshwariNo ratings yet

- Programming of Industrial ComputersDocument11 pagesProgramming of Industrial ComputersshandiezzNo ratings yet

- Introduction To Hardware Description LanguageDocument5 pagesIntroduction To Hardware Description LanguageMallik KglNo ratings yet

- Introduction To DDTVDocument62 pagesIntroduction To DDTVWe are youngNo ratings yet

- Ieee PapersDocument8 pagesIeee PapersAtit PatelNo ratings yet

- Tutorial On High-Level Synthesis: and WeDocument7 pagesTutorial On High-Level Synthesis: and WeislamsamirNo ratings yet

- Design Flow OverviewDocument9 pagesDesign Flow OverviewCarlo Jose Bautista ChecaNo ratings yet

- Vlsi 1Document3 pagesVlsi 1devNo ratings yet

- Computer Architecture For Digital Signal Processing: Jonathan AllenDocument25 pagesComputer Architecture For Digital Signal Processing: Jonathan AllenDeepthi MvNo ratings yet

- Bharathidasan University, Tiruchirappalli - 620 024. Master of Computer Application (M.C.A) - Course Structure Under CBCSDocument54 pagesBharathidasan University, Tiruchirappalli - 620 024. Master of Computer Application (M.C.A) - Course Structure Under CBCSB. Srini VasanNo ratings yet

- SR PSpice SimulationDocument11 pagesSR PSpice SimulationMark Chow Khoon KeatNo ratings yet

- Hardware-Software Codesign: Jan Beutel & Iuliana Bacivarov Based On Material by Lothar ThieleDocument24 pagesHardware-Software Codesign: Jan Beutel & Iuliana Bacivarov Based On Material by Lothar ThieleEnas DhuhriNo ratings yet

- VLSI Design FlowDocument10 pagesVLSI Design Flowuday93No ratings yet

- Introduction To VLSI SystemDocument16 pagesIntroduction To VLSI SystemPrabakaran RajendranNo ratings yet

- Vlsi System DesignDocument12 pagesVlsi System DesignMahender GoudNo ratings yet

- Advanced Computer ArchitectureDocument17 pagesAdvanced Computer ArchitectureYoung LiangNo ratings yet

- CS201Document2 pagesCS201DivyanshuVermaNo ratings yet

- System-Level Power Optimization: Techniques and ToolsDocument78 pagesSystem-Level Power Optimization: Techniques and ToolsbluesoulNo ratings yet

- Syllabus-EEE646 FPGA Based System DesignDocument2 pagesSyllabus-EEE646 FPGA Based System DesignNaveen Chaubey100% (1)

- VLSI Design FlowDocument3 pagesVLSI Design FlowSaurabh PorwalNo ratings yet

- Vlsi DesignDocument12 pagesVlsi DesignTanveer AhmedNo ratings yet

- Implementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKDocument16 pagesImplementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKVLSISD36 Edwin DominicNo ratings yet

- Implementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKDocument16 pagesImplementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKhamim ahmedNo ratings yet

- Unit 5 - VHDLDocument15 pagesUnit 5 - VHDLMichael FosterNo ratings yet

- Presentation With Right FormatDocument14 pagesPresentation With Right FormatAditya KumarNo ratings yet

- Iscug 2013 Hls TutorialDocument96 pagesIscug 2013 Hls TutorialLiu WenNo ratings yet

- Data Converter BIST Development Tools: Ian Grout, Thomas O'Shea and Jeffrey RyanDocument2 pagesData Converter BIST Development Tools: Ian Grout, Thomas O'Shea and Jeffrey Ryansarin.gaganNo ratings yet

- Implementation of A Functional Verification System Using SystemcDocument4 pagesImplementation of A Functional Verification System Using Systemcnamhoa02No ratings yet

- Eee481 - Fa09 - CCSDocument3 pagesEee481 - Fa09 - CCSSai KamalaNo ratings yet

- Digital Electronics, Computer Architecture and Microprocessor Design PrinciplesFrom EverandDigital Electronics, Computer Architecture and Microprocessor Design PrinciplesNo ratings yet

- Discrete-Time Control System Implementation Techniques: Advances in Theory and ApplicationsFrom EverandDiscrete-Time Control System Implementation Techniques: Advances in Theory and ApplicationsNo ratings yet

- EncodersDocument8 pagesEncoderssuresh mariappanNo ratings yet

- Daft of Legal ContractDocument33 pagesDaft of Legal ContractOx LaoNo ratings yet

- Marketing British English Student Ver2Document3 pagesMarketing British English Student Ver2Anna PártlNo ratings yet

- Ch-2 Railway Line CIVILDocument65 pagesCh-2 Railway Line CIVILnoladawitNo ratings yet

- Communicating The Museum 2013 SlideshareDocument38 pagesCommunicating The Museum 2013 SlidesharehewhittyNo ratings yet

- Group 2 CONTEMPORARY ARTDocument47 pagesGroup 2 CONTEMPORARY ARTShiella Marie Alvindia GanibanNo ratings yet

- Mental Status: Ateneo de Zamboanga UniversityDocument10 pagesMental Status: Ateneo de Zamboanga UniversitySheryhan Tahir BayleNo ratings yet

- Summer Internship Project ReportDocument13 pagesSummer Internship Project ReportShivangi SrivastavaNo ratings yet

- IS EN 14476 - 2013 A1 2015 ResumenDocument12 pagesIS EN 14476 - 2013 A1 2015 ResumenLuciano QuinteroNo ratings yet

- SapDocument15 pagesSapMauro AlessiNo ratings yet

- Physics Sample Paper 10 - 231221 - 091030Document19 pagesPhysics Sample Paper 10 - 231221 - 091030derexax756No ratings yet

- Bond Valuation JiteshDocument83 pagesBond Valuation Jiteshjitesh_talesaraNo ratings yet

- PPE MatrixDocument2 pagesPPE MatrixDhaval DobariyaNo ratings yet

- E384 Test Method For Microindentation Hardness of MaterialsDocument33 pagesE384 Test Method For Microindentation Hardness of MaterialssumherilNo ratings yet

- Course Material Required For Board Exams 2018Document6 pagesCourse Material Required For Board Exams 2018Anh Phúc LêNo ratings yet

- Piping Support Standard Specification (190-216)Document51 pagesPiping Support Standard Specification (190-216)Emilio Huertas100% (1)

- RT GRP DraftDocument35 pagesRT GRP Draftnilish22310119No ratings yet

- AMACS Accuflow Inlet Feed Devices Web1Document1 pageAMACS Accuflow Inlet Feed Devices Web1SHINo ratings yet

- Defense Laboratories and Centers: AFRL: Air Force Research LaboratoryDocument2 pagesDefense Laboratories and Centers: AFRL: Air Force Research LaboratoryIan S Ryu100% (1)

- Software Engineering Director Manager in West Palm Beach FL Resume John GraysonDocument2 pagesSoftware Engineering Director Manager in West Palm Beach FL Resume John GraysonJohnGraysonNo ratings yet

- Assignment 5 Abhilash BollamDocument7 pagesAssignment 5 Abhilash BollamAbhilash BollamNo ratings yet

- Simultaneous Determination of Paracetamol and Its Metabolites in Rat Serum by HPLC Method and Its Application Supplement-Drug Pharmacokinetic InteractionDocument15 pagesSimultaneous Determination of Paracetamol and Its Metabolites in Rat Serum by HPLC Method and Its Application Supplement-Drug Pharmacokinetic InteractionNelson Enrique Bessone MadridNo ratings yet

- Casio px-130 Ver.4 SMDocument60 pagesCasio px-130 Ver.4 SMPoon Electronic Training CentreNo ratings yet

- English Yr5 2015 MsDocument9 pagesEnglish Yr5 2015 MsEric JBNo ratings yet

- Contracted Vendor List $25,000.00+ (V4)Document3 pagesContracted Vendor List $25,000.00+ (V4)ABC10No ratings yet

- DAA Notes CompleteDocument242 pagesDAA Notes CompleteVarnika TomarNo ratings yet

- Joy To Live EbookDocument417 pagesJoy To Live Ebookmarkuswolf11No ratings yet