Professional Documents

Culture Documents

R7210504 Digital Logic Design

Uploaded by

Mahaboob Subahan0 ratings0% found this document useful (0 votes)

10 views1 pagehi

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documenthi

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

10 views1 pageR7210504 Digital Logic Design

Uploaded by

Mahaboob Subahanhi

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

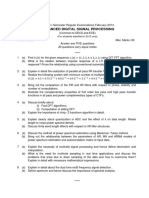

Code: R7210504 R07

B.Tech II Year I Semester (R07) Supplementary Examinations June 2015

DIGITAL LOGIC DESIGN

(Common to CSE, IT & CSS)

Time: 3 hours Max. Marks: 80

Answer any FIVE questions

All questions carry equal marks

*****

1 Convert the following numbers:

(a) (i) 10101100111.0101 to Base 10

(ii) (153.513)10 =( )8

(iii) Divide 01100100 by 00011001

(iv) Given that (292)10 = (1204)b determine ‘b’.

(b) Perform the following binary multiplication operations:

(i) 100010 X 001010=

(ii) 000100 X 010101=

2 Simplify using Boolean theorems:

(a) (i) (X’+XYZ’)+(X+X’Y’Z)(X(X’+Y’+Z))’

(ii) (X+Y)[X’(Y’+Z’)]’+X’Y’+X’Z’

(b) Explain about positive, negative and mixed logic in binary signals.

3 (a) Implement half adder using 4 NAND gates.

(b) Implement full subtract using NAND gates only.

4 Design an Excess-3 to BCD code converter using minimum number of NAND gates.

5 (a) Differentiate between sequential and combinational circuits.

(b) Differentiate between synchronous and asynchronous sequential circuits.

6 Explain about ripple counters in detail.

7 Explain about error detection and correction in detail.

8 Explain about the reduction of state and flow tables in an asynchronous sequential circuit in

detail.

*****

You might also like

- Digital Electronics For Engineering and Diploma CoursesFrom EverandDigital Electronics For Engineering and Diploma CoursesNo ratings yet

- Digital Logic Design: Assignment 1 Due Date: 10.12.2020 (Thursday)Document3 pagesDigital Logic Design: Assignment 1 Due Date: 10.12.2020 (Thursday)muktikantaNo ratings yet

- R7210504 Digital Logic DesignDocument2 pagesR7210504 Digital Logic DesignsivabharathamurthyNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignMahaboob SubahanNo ratings yet

- S T L DDocument12 pagesS T L DMohan Krishna0% (1)

- 02 - CSA - Tutorial - Data - Representation Excercises NewDocument2 pages02 - CSA - Tutorial - Data - Representation Excercises NewYong Yung HaoNo ratings yet

- r05220403 Switching Theory and Logic DesignDocument8 pagesr05220403 Switching Theory and Logic DesignSRINIVASA RAO GANTANo ratings yet

- Assignment 2Document3 pagesAssignment 2Syed Abdullah Hasan ChishtiNo ratings yet

- 9A04306 Digital Logic Design4Document4 pages9A04306 Digital Logic Design4Mahaboob SubahanNo ratings yet

- 07a4ec09 STLDDocument6 pages07a4ec09 STLDSRINIVASA RAO GANTANo ratings yet

- Tutorial Part 1Document29 pagesTutorial Part 1Noor Zilawati SabtuNo ratings yet

- Tutorial 1Document2 pagesTutorial 1Ratnam KrishnasamyNo ratings yet

- Assingnment# 1Document8 pagesAssingnment# 1Tayyab AbbasNo ratings yet

- Communication Systems PDFDocument2 pagesCommunication Systems PDFBhagyaNo ratings yet

- Digital Logic Design (Jntu - Uandistar.org)Document4 pagesDigital Logic Design (Jntu - Uandistar.org)Arepalli SathibabuNo ratings yet

- DLD Slides CombinedDocument13 pagesDLD Slides CombinedHaris BaigNo ratings yet

- TD Serie GlobalDocument6 pagesTD Serie Globalbarr.youcef.magNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- Assignment-1: Digital Electronics: CT 304-N Semester: 3 (CE/CSE/IT)Document2 pagesAssignment-1: Digital Electronics: CT 304-N Semester: 3 (CE/CSE/IT)Liyanshu patelNo ratings yet

- VL2021220504591 DaDocument2 pagesVL2021220504591 DaDattu GollapinniNo ratings yet

- DIGITAL ELECTRONICS - MicroProcessor 2016-17Document4 pagesDIGITAL ELECTRONICS - MicroProcessor 2016-17Prateek singhNo ratings yet

- STLD PDFDocument2 pagesSTLD PDFANUPAMA PonnuNo ratings yet

- Exercises W 10 11Document6 pagesExercises W 10 11monzer.mohamed9955No ratings yet

- R5210504 Digital Logic DesignDocument1 pageR5210504 Digital Logic DesignsivabharathamurthyNo ratings yet

- 03 - Data Representation WorkbookDocument1 page03 - Data Representation WorkbookyuukiblackkamaruNo ratings yet

- Code - No: 43216: Jawaharlal Nehru Technological University HyderabadDocument1 pageCode - No: 43216: Jawaharlal Nehru Technological University HyderabadKareem KhanNo ratings yet

- STLD Regular Jntu Question Papers 2008Document9 pagesSTLD Regular Jntu Question Papers 2008anjaneyulud100% (1)

- Introduction To Digital Design & Digital Logic FddsDocument3 pagesIntroduction To Digital Design & Digital Logic FddsMahima MohapatraNo ratings yet

- BCSC 1201 Digital Logic and Electronic Circuits EXAM MSDocument7 pagesBCSC 1201 Digital Logic and Electronic Circuits EXAM MSndunguloren96No ratings yet

- 1 Computer Organization and Logic Design ﻲﻘﻄﻨﻤﻟﺍ ﻢﻴﻤﺼﺘﻟﺍﻭ ﺔﺒﺳﺎﺤﻟﺍ ﺐﻴﻛﺮﺗ ﻩﺩﺎﻤﻟﺍ ﺫﺎﺘﺳﺍ: ﻡ. ﻡ. ﺮﻀﺧ ﻲﻠﻋ ﺪﺒﻋ ءﺎﺴﻴﻣDocument81 pages1 Computer Organization and Logic Design ﻲﻘﻄﻨﻤﻟﺍ ﻢﻴﻤﺼﺘﻟﺍﻭ ﺔﺒﺳﺎﺤﻟﺍ ﺐﻴﻛﺮﺗ ﻩﺩﺎﻤﻟﺍ ﺫﺎﺘﺳﺍ: ﻡ. ﻡ. ﺮﻀﺧ ﻲﻠﻋ ﺪﺒﻋ ءﺎﺴﻴﻣAshish KatochNo ratings yet

- BCA T 113 Digital Electronics Question BankDocument9 pagesBCA T 113 Digital Electronics Question BankAhana MalhotraNo ratings yet

- EE2403-Intro To computing-S2-20-21-HW1Document3 pagesEE2403-Intro To computing-S2-20-21-HW1Hoang AnhNo ratings yet

- 21 - 2011 - Dec - R09 - STLDDocument8 pages21 - 2011 - Dec - R09 - STLDvasuvlsiNo ratings yet

- R7210504-Digital Logic DesignDocument1 pageR7210504-Digital Logic DesignsivabharathamurthyNo ratings yet

- Digital Electronics QB 2015-RDocument8 pagesDigital Electronics QB 2015-RKeerthe VaasanNo ratings yet

- Digital Electronics June July 2022Document8 pagesDigital Electronics June July 2022RCEE-2020 ONLINE FDPNo ratings yet

- Computer - Grade 9 - ClassTestDocument7 pagesComputer - Grade 9 - ClassTestfarzinahammedNo ratings yet

- BEG 212 Digital Electronics and Devives - CAT-REGDocument5 pagesBEG 212 Digital Electronics and Devives - CAT-REGKimani MikeNo ratings yet

- Digital Logic Design Sept 2021Document2 pagesDigital Logic Design Sept 2021Gopl KuppaNo ratings yet

- EEL2020 Assignment 01Document1 pageEEL2020 Assignment 01b22ee084No ratings yet

- MCS 103Document3 pagesMCS 103Rahul SharmaNo ratings yet

- Repaso 1Document5 pagesRepaso 1Hector GasgaNo ratings yet

- Jntuk 2 1 DLD Nov 2017 Q.PDocument5 pagesJntuk 2 1 DLD Nov 2017 Q.PRoopa Krishna ChandraNo ratings yet

- 9A04306 Digital Logic Design3Document1 page9A04306 Digital Logic Design3Mahaboob SubahanNo ratings yet

- Avalon Brown - 2.3.4.A TwoComplementArithmeticDocument4 pagesAvalon Brown - 2.3.4.A TwoComplementArithmeticAvalon BrownNo ratings yet

- BCA I I Digital SystemDocument4 pagesBCA I I Digital SystemAmory Sabri AsmaroNo ratings yet

- Unit-1-2-3 Question Bank DEC 2131004Document2 pagesUnit-1-2-3 Question Bank DEC 2131004Amit KumarNo ratings yet

- STLD 2009 RegularDocument4 pagesSTLD 2009 RegularrangerNo ratings yet

- 9a04306-Digital Logic DesignDocument1 page9a04306-Digital Logic DesignSheikh Noor MohammadNo ratings yet

- Computer Organisation COSC 2400Document11 pagesComputer Organisation COSC 2400Mitchell PottsNo ratings yet

- Digital Logic DesignDocument4 pagesDigital Logic DesignrppvchNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- Final Revision LogicDocument66 pagesFinal Revision LogicKirillus MaherNo ratings yet

- Aditya College of EngineeringDocument2 pagesAditya College of EngineeringkarnamittapalliNo ratings yet

- ICT121 - JULY - 2017 - Exam PaperDocument8 pagesICT121 - JULY - 2017 - Exam PaperBenjamin TangNo ratings yet

- Lab 1 - DLDDocument7 pagesLab 1 - DLDTarviha FatimaNo ratings yet

- STLD Question Bank Unit I 1: (RR, R05, Nov 08SET II, III)Document16 pagesSTLD Question Bank Unit I 1: (RR, R05, Nov 08SET II, III)Harold WilsonNo ratings yet

- 12D75204 Advanced Digital Signal Processing8Document1 page12D75204 Advanced Digital Signal Processing8subbuNo ratings yet

- 12D75204 Advanced Digital Signal Processing5Document1 page12D75204 Advanced Digital Signal Processing5subbuNo ratings yet

- 9d49106a Advanced Digital Signal Processing1Document1 page9d49106a Advanced Digital Signal Processing1subbuNo ratings yet

- 9D38103 Advanced Digital Signal Processing10Document1 page9D38103 Advanced Digital Signal Processing10subbuNo ratings yet

- 9d49106a Advanced Digital Signal Processing12Document1 page9d49106a Advanced Digital Signal Processing12subbuNo ratings yet

- 9d49106a Advanced Digital Signal Processing12Document1 page9d49106a Advanced Digital Signal Processing12subbuNo ratings yet

- R5320201 Digital Signal Processing21Document1 pageR5320201 Digital Signal Processing21Mahaboob SubahanNo ratings yet

- 9d49106a Advanced Digital Signal Processing6Document1 page9d49106a Advanced Digital Signal Processing6subbuNo ratings yet

- 9d49106a Advanced Digital Signal Processing3Document1 page9d49106a Advanced Digital Signal Processing3subbuNo ratings yet

- 9D38103 Advanced Digital Signal Processing2Document1 page9D38103 Advanced Digital Signal Processing2subbuNo ratings yet

- 9D38103 Advanced Digital Signal Processing10Document1 page9D38103 Advanced Digital Signal Processing10subbuNo ratings yet

- 9A04603 Digital Signal Processing24Document1 page9A04603 Digital Signal Processing24Mahaboob SubahanNo ratings yet

- 9d49106a Advanced Digital Signal Processing9Document1 page9d49106a Advanced Digital Signal Processing9subbuNo ratings yet

- 9A04603 Digital Signal ProcessingDocument4 pages9A04603 Digital Signal ProcessingsivabharathamurthyNo ratings yet

- 9A04603 Digital Signal ProcessingDocument4 pages9A04603 Digital Signal ProcessingsivabharathamurthyNo ratings yet

- 9D38103 Advanced Digital Signal Processing13Document1 page9D38103 Advanced Digital Signal Processing13Mahaboob SubahanNo ratings yet

- 9A04603 Digital Signal Processing31Document1 page9A04603 Digital Signal Processing31Mahaboob SubahanNo ratings yet

- 9A04603 Digital Signal Processing7Document1 page9A04603 Digital Signal Processing7Mahaboob SubahanNo ratings yet

- 9A04704 DSP Processros & ArchitecturesDocument1 page9A04704 DSP Processros & ArchitecturesMahaboob SubahanNo ratings yet

- 9A04603 Digital Signal Processing31Document1 page9A04603 Digital Signal Processing31Mahaboob SubahanNo ratings yet

- 9D38103 Advanced Digital Signal Processing6Document1 page9D38103 Advanced Digital Signal Processing6subbuNo ratings yet

- 9A04603 Digital Signal Processing23Document1 page9A04603 Digital Signal Processing23Mahaboob SubahanNo ratings yet

- 9A04603 Digital Signal Processing10Document1 page9A04603 Digital Signal Processing10Mahaboob SubahanNo ratings yet

- 9A04306 Digital Logic Design1Document4 pages9A04306 Digital Logic Design1Mahaboob SubahanNo ratings yet

- SS 9A04306 Digital Logic DesignDocument1 pageSS 9A04306 Digital Logic DesignMahaboob SubahanNo ratings yet

- 9A04306 Digital Logic Design2Document1 page9A04306 Digital Logic Design2Mahaboob SubahanNo ratings yet

- 9A04603 Digital Signal Processing2Document1 page9A04603 Digital Signal Processing2Mahaboob SubahanNo ratings yet

- 9A04603 Digital Signal Processing16Document4 pages9A04603 Digital Signal Processing16Mahaboob SubahanNo ratings yet

- 9A04306 Digital Logic Design3Document1 page9A04306 Digital Logic Design3Mahaboob SubahanNo ratings yet