Professional Documents

Culture Documents

Course Handbook EEE344 DSD - FA19

Uploaded by

Zain JavedOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Course Handbook EEE344 DSD - FA19

Uploaded by

Zain JavedCopyright:

Available Formats

COMSATS University Islamabad, Lahore Campus

Block – B, Department of Electrical and Computer Engineering

COMSATS Institute of Information Technology, 1.5 KM Defence Road, Off Raiwind Road, Lahore

Course Descriptive File

1 Course Title Digital System Design

2 Course Code EEE344

3 Credit Hours 4(3,1)

4 Prerequisites Digital Logic Design

5 Co requisites

6 Semester Semester 7

7 Resource Person M. Hassan Aslam

8 Contact Hours (Theory) 3 hours per week

9 Contact Hours (Lab) 3 hours per week

10 Office Hours Monday, 8:30 am to 10 am, B1-1, B-Block, CUI, LHR

11 Email mhassanaslam@cuilahore.edu.pk

12 Course Outline as per SoS

The course is designed to teach students: Design and evaluation of control and data structures for digital

systems. Design of finite state diagram (FSM) based control unit. Design of datapath components such as

adder, subtractor, arithmetic logic unit, array multiplier, shift registers, universal registers and shifter.

Register-transfer level (RTL) design. Design of register file, RAM and ROM based systems. Design of

memory components. Timing and synchronization of digital circuits. Optimization techniques of

combinational and sequential logic circuits. Design of advanced adders and multipliers. Role of pipelining,

concurrency, component allocation and operator binding as an optimization and trade-off. Physical

implementation of digital circuits, Internals of FPGA such as lookup tables, switch matrixes and configurable

logic blocks. Hardware descriptive language (VHDL/Verilog) based design of digital systems and FPGA

implementation.

13 Course Objectives as per SoS

The main objective of this course is enabling students in designing complex, high-speed digital systems. For

this purpose, the use of modern EDA tools in the design, simulation, synthesis and implementation will be

explored. Application of a hardware description language such as Verilog or VHDL to model digital systems

at Behavior and RTL level will be studied. Field programmable gate arrays (FPGA) will be used in the

laboratory exercises as a vehicle to understand complete design-flow of an integrated circuit. Advanced

methods of logic minimization and state-machine design will be discussed. Lab sessions and projects are an

integral part of this course that culminates in a comprehensive design exercise.

14 Books

Textbook

1. Book1: Digital Design by Frank Vahid

2. Book2: Digital Systems Design using VHDL by Charles H. Roth, Jr.

3. Book3: Principles of Digital Systems Design by Charles H. Roth and L. K. John

Reference Books

1. Digital Electronics and Design with VHDL by Volnei A. Pedroni

Course Handbook | EEE344 Digital System Design 1

Circuit Design and Simulation with VHDL by Volnei A. Pedroni

15 Course Learning Outcomes (CLOs)

After successfully completing this course, the students will be able to:

Theory CLOs:

• CLO 1: Analyze and Design the working of advanced combinational and sequential logic-based

systems using the classical principals of digital logic design. (PLO3-C5)

• CLO 2: Design of digital systems in a hierarchical and top-down manner using register-transfer

logic (RTL) approach. (PLO3-C5)

Lab CLOs:

• CLO3: To design the digital systems based on HDL modelling techniques using VHDL. (PLO3-C5)

• CLO4: Reproduce the response of the designed digital systems using the software tool and hardware

platform (PLO5-P3)

• CLO5: To explain and write effective lab reports of experiments performed during lab (PLO10-A3)

16 Marks Breakup

Theory

Quizzes (minimum 4) 15%

Homework assignments (minimum 4) 10%

2 Sessional Exams (in class, 60-80 minutes each, 10%+15%) 25%

Terminal exam (3 hours) 50%

Total (theory) 100%

Lab

S-I 0.5*(S-I Exam result) + 0.5* (average of lab evaluation of Lab 1-4)

S-II 0.5*(S-II Exam result) + 0.5*[ (average of lab evaluation of Lab 5-8) * 1.5]

Terminal 0.5*(Terminal Exam result) +0.25*[(average of lab evaluation of Lab 9-12) *5] + 0.10*[(average of lab

evaluation of Lab 5-8)*5] + 0.15*[(average of lab evaluation of Lab 1-4)*5]

Final marks Theory marks * 0.75 + Lab marks * 0.25

Course Handbook | EEE344 Digital System Design 2

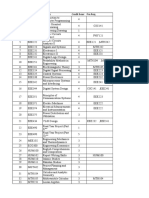

17 Lecture Plan

Students

Bloom Contact

Week Topic CLO Specific Outcome Learning Assessment

Taxonomy Hours

Hours

Comprehend the theoretical knowledge of 1.5 2

Introduction to the digital digital systems such as digital logic,

1 systems and Implementation CLO1 C2 number systems, processing of data and

methods the custom implementation using

standard conversion methods. 1.5 2

Assignment 1

Analyze and Design basic combinational Quiz 1

Combinational logic design logic digital circuits based on Boolean

2 CLO1 C5 3 4

overview functions and truth table using Boolean

algebra and its properties.

Analyze and Design basic sequential

Sequential logic design logic digital circuits based on flipflops

3 CLO1 C5 3 4

overview and registers using finite state machine

(FSM).

Design of controller based on

1.5 2

4 Controller design and pitfalls CLO1 C5 combinational and sequential logic using

controller design process 1.5 2

Datapath components- Analyze and Design the working of

Parallel and shift register, CLO1 C5 register-based components using standard 1.5 2

multifunction register analysis procedure

5 Assignment 2

Datapath components- Design Design of a simple digital system based

Quiz 2

of Subtractors, Comparators, CLO1 C5 on combinational and sequential logic 3 4

Sessional 1

Multipliers using Datapath components.

Datapath components- Design

CLO1 C5 1.5 2

of counters and timers Design of simple digital systems based on

6 Datapath components- Design combinational and sequential logic using

of arithmetic logic unit (ALU) CLO1 C5 Datapath components. 1.5 2

and register file

Design of complex digital systems based

Register Transfer Level

7 CLO2 C5 on combinational and sequential logic 3 4

(RTL) design Method using Datapath components.

Course Handbook | EEE344 Digital System Design 3

RTL Design examples, Design of complex digital systems based

8 Critical Path and Clock CLO2 C5 on combinational and sequential logic 3 4 Assignment 3

frequency using Datapath components. Quiz 3

Sessional 2 &

Analyze and compare the working of Terminal

Memory components analysis CLO1 C4 memory components using standard 1.5 2

analysis procedure

9

Design of complex digital systems based

Integration of memory and

CLO2 C5 on combinational and sequential logic 1.5 2

Datapath components

using memory components

Programmable Array Logic Analyze and compare the working of

10 (PAL), Programmable Logic CLO1 C4 PAL and PLA using standard analysis 3 4

Arrays (PLA) procedure

Analyze and compare the working of

Read Only Memories

11 CLO1 C4 ROMs and CPLD using standard analysis 3 4

(ROMs), CPLD

procedure

Combinational and Sequential Design of simple digital systems based on

12 Logic Optimization and CLO2 C5 combinational and sequential logic using 3 4

Tradeoffs optimization and tradeoff techniques

Design of complex digital systems based

Datapath component and RTL

on combinational and sequential logic Assignment 4

13 design optimizations and CLO2 C5 3 4

using optimization and tradeoff Quiz 4

Tradeoffs

techniques Terminal

Analyze and compare the working of IC

14 Manufactured IC Technology CLO1 C4 manufacturing technology using standard 3 4

analysis procedure

Design of digital systems based on

Programmable IC

15 CLO2 C5 FPGA logic using Lookup tables, switch 3 4

Technology- FPGA

matrix and configurable logic blocks

Course Handbook | EEE344 Digital System Design 4

18 Course Learning Outcomes (CLOs) and Assessment Plan

CLO Cognitive Domain Affective Domain Psychomotor Domain

LAB CLO2

LAB CLO3

LABCLO1

CLO 1

CLO2

Activity

A1

A2

A3

A4

A5

C1

C2

C3

C4

C5

C6

P1

P2

P3

P4

P5

P6

P7

Quiz 1 X X

Quiz 2 X X

Quiz 3 X X X

Quiz 4 X X

Assignment 1 X X

Assignment 2 X X

Assignment 3 X X

Assignment 4 X X X

S-I X X

S-II X X X

Lab S-I X X X X

Lab S-II X X X X

Terminal X X X

Lab Terminal X X X

Lab Assignments/ Lab Reports/

X X X X X X

Lab Performance

Course Handbook | EEE344 Digital System Design 5

19 Laboratory Experiences

There is a Laboratory component in all 3+1 credit courses taught at the department. Lab work

consists of a minimum of 15 experiments, semester project and related assignments, which

constitute 25% of the overall course-grade. The laboratory experiments include hands-on

exercises as well as computer analysis of the concepts taught in class. This course familiarizes the

students with the FPGA based Quartus analysis and design software analysis and design software

tool, which is a part of all laboratory experiments.

20 Laboratory Resources

The relevant laboratory is equipped with workbenches and computers to facilitate the experiments

outlined in the lab handbook(s) that are periodically updated. A current list of the 13 lab experiments

performed in this course is provided as Annexure-I. The list of software and equipment available is

also posted in all labs and is managed by staff dedicated for this purpose

21 Computer Resources

For the purposes of this course the FPGA based Quartus analysis and design software is used

throughout the course

22 Mapping of CLOs to PLOs

PLO 1 Engineering Knowledge: An ability to apply knowledge of mathematics, science,

engineering fundamentals and an engineering specialization to t he solution of complex

engineering problems. (Cognitive)

PLO 2 Problem Analysis: An ability to identify, formulate, research literature, and analyze

complex engineering problems reaching substantiated conclusions using first

principles of mathematics, natural sciences and engineering sciences. (Cognitive)

PLO 3 Design/Development of Solutions: An ability to design solutions for complex

engineering problems and design systems, components or processes that meet

specified needs with appropriate consideration for public health and safety, cultural,

societal, and environmental considerations. (Cognitive)

PLO 4 Investigation: An ability to investigate complex engineering problems in a

methodical way including literature survey, design and conduct of experiments,

analysis and interpretation of experimental data, and synthesis of information to

derive valid conclusions. (Cognitive, Psychomotor)

PLO 5 Modern Tool Usage: An ability to create, select and apply appropriate techniques,

resources, and modern engineering and IT tools, including prediction and modeling, to

complex engineering activities, with an understanding of the limitations.

(Psychomotor)

PLO 6 The Engineer and Society: An ability to apply reasoning informed by contextual

knowledge to assess societal, health, safety, legal and cultural issues and the consequent

responsibilities relevant to professional engineering practice and solution to complex

engineering problems. (Cognitive)

PLO 7 Environment and Sustainability: An ability to understand the impact of professional

engineering solutions in societal and environmental contexts and demonstrate

knowledge of and need for sustainable development. (Cognitive)

PLO 8 Ethics: Apply ethical principles and commit to professional ethics and responsibilities

and norms of engineering practice. (Affective)

PLO 9 Individual and Teamwork: An ability to work effectively, as an individual or in a

team, on multifaceted and /or multidisciplinary settings. (Affective)

PLO 10 Communication: An ability to communicate effectively, orally as well as in writing,

on complex engineering activities with the engineering community and with society at

large, such as being able to comprehend and write effective reports and design

documentation, make effective presentations, and give and receive clear instructions.

(Affective)

Course Handbook | EEE344 Digital System Design 6

PLO 11 Project Management: An ability to demonstrate management skills and apply

engineering principles to one’s own work, as a member and/or leader in a team, to

manage projects in a multidisciplinary environment. (Affective)

PLO 12 Lifelong Learning: An ability to recognize importance of and pursue lifelong learning

in the broader context of innovation and technological developments. (Affective)

Course Handbook | EEE344 Digital System Design 7

CLOs – PLOs Mapping

PLO Cognitive Domain Affective Domain Psychomotor Domain

PLO10

PLO11

PLO12

PLO1

PLO2

PLO3

PLO4

PLO5

PLO6

PLO7

PLO8

PLO9

A1

A2

A3

A4

A5

C1

C2

C3

C4

C5

C6

P7

P1

P2

P3

P4

P5

P6

CLOs

CLO1 X X X X X X

CLO2 X X X X X X

CLO3 X X X X X X

CLO4 X X X X

CLO5 X X X X

Course Handbook | EEE344 Digital System Design 8

23 PLOs Coverage Explanation

PLO 3 - Design/ Development of Solutions: CLO 1, CLO 2, CLO 3.

This course enables the students to design complex and high speed digital systems using advanced methods of

Logic minimization and state machine design (High relevance to the course).

Field programmable gate arrays (FPGA) will be used in the laboratory exercises to understand complete

design-flow of an integrated circuit using VHDL on Quartus platform.

PLO 5 - Modern Tool Usage: CLO 4

Laboratory exercises provides students to develop expertise in modern software tools e.g. Quartus (High

relevance to the course).

PLO10- Communication: CLO 5

Good technical communication skills developed by class presentations and viva voce help achieve this

objective (Low relevance to the course).

PLO 1, 4, 6 , 7 , 8, 9, 11, 12: These PLOs are not directly addressed in this course.

24 List of Experiment With Objectives as Per OBE Format

Lab Title and Objective

Experiment

No.

Introduction to VHDL and Altera Quartus with the design of Full Adder

OBJECTIVES

• Familiarize students with VHDL (VHSIC Hardware Description Language) and

1 Quartus.

To design the combinational and sequential circuit components using VHDL and show

output on the FPGA board

OBJECTIVES

• To understand the simulation of combinational logic problems using VHDL.

2 • Quartus shall be used for the compilation and functional verification of VHDL

design files.

Course Handbook | EEE344 Digital System Design 9

To design the finite state machines using VHDL and reproduce the results on FPGA board

OBJECTIVES

• To study several different ways of specifying and implementing finite state

3 machines (FSMs) i.e., controllers

To design the counter and sequence detector using VHDL and reproduce the sequence on

the FPGA board.

OBJECTIVES

4 • To design counters and sequence detectors using Finite state machines

To design the complex counter and vending machine using VHDL and show the results on

the FPGA board

OBJECTIVES

5 • To design a complex design i-e complex counter and vending machine in VHDL

with the help of Finite State Machines

To design the array and binary multiplier using VHDL and reproduce the output on the

FPGA board

OBJECTIVES

• To design an array multiplier (combinational logic) in VHDL and Binary

6

Multiplier (shift and add approach)

To design the signed binary multiplier using Booth’s algorithm in VHDL and show the

results on FPGA board

OBJECTIVES

• To design and test signed binary number multiplier using Booth’s algorithm

7

To design the binary and signed binary divider using VHDL and reproduce output on

FPGA board

OBJECTIVES

• To design binary divider a signed binary number divider using VHDL

Course Handbook | EEE344 Digital System Design 10

To design the traffic light controller using VHDL and show the output on the FPGA board

OBJECTIVES

• To design and test traffic light controller using VHDL.

To design the memories (RAM and ROM) using VHDL and reproduce output on FPGA

board

OBJECTIVES

• To design and test RAM and ROM using VHDL

10

To design the keypad scanner using VHDL and show the output on the FPGA board

OBJECTIVES

11 • To design a scanner for a telephone keypad using VHDL

To design the finite impulse response (FIR) filter using VHDL and reproduce output on

FPGA board

OBJECTIVES

• To design and test different architectures of Finite Impulse Response (FIR) filter

12

To design the fast fourier transform (FFT) processor using VHDL and show the output on

the FPGA board

OBJECTIVES

• To design and test a 16-point Radix-2 FFT processor

13

To design the video graphics array (VGA) controller using VHDL and reproduce output

on FPGA board

OBJECTIVES

• To design and implement a VGA controller to display a certain pattern on a VGA

14 monitor interfaced with an FPGA.

Course Handbook | EEE344 Digital System Design 11

Course Handbook | EEE344 Digital System Design 12

You might also like

- BPT Brochure 2017 Ver 1Document42 pagesBPT Brochure 2017 Ver 1upppppppppppppppNo ratings yet

- Gpat - 2019 AnalysisDocument4 pagesGpat - 2019 Analysisapi-306292630No ratings yet

- B.Pharma NotesDocument13 pagesB.Pharma NotesAnkurNo ratings yet

- Introduction Definitions and Sources of DrugsDocument4 pagesIntroduction Definitions and Sources of Drugssindhu mNo ratings yet

- HR Data BaseDocument14 pagesHR Data Base1l0veuNo ratings yet

- ELEX1105 Lecture NotesDocument192 pagesELEX1105 Lecture Notesalen GacicNo ratings yet

- Pharmacology - Anti-Arrhythmias 2019 PDFDocument11 pagesPharmacology - Anti-Arrhythmias 2019 PDFpurletpunkNo ratings yet

- Updated CN Course File PDFDocument92 pagesUpdated CN Course File PDFshahaban aliNo ratings yet

- Unit 1Document108 pagesUnit 1RAHUL R : ECE DEPTNo ratings yet

- Charusat NAAC SSRDocument204 pagesCharusat NAAC SSRbmcm bmefcolleges.edu.inNo ratings yet

- HR Pharma DetailsDocument3 pagesHR Pharma Detailssfimarpgdm2012No ratings yet

- Ec3462 Linear Integrated Circuits Laboratory Course ObjectivesDocument13 pagesEc3462 Linear Integrated Circuits Laboratory Course ObjectivesBalaNo ratings yet

- CH6403Document7 pagesCH6403NikylNo ratings yet

- GE8151 Python Programming - Unit I Question Bank With Sample CodeDocument25 pagesGE8151 Python Programming - Unit I Question Bank With Sample CodeN.Vivekananthamoorthy100% (1)

- Home Automation Using IoTDocument14 pagesHome Automation Using IoTAnkit Singh100% (1)

- ELCS Lab Manual 0Document116 pagesELCS Lab Manual 0Simon DevramNo ratings yet

- 0 4th Sem LIC Full Notes (6 Chapters) by Arunkumar G, Lecturer Dept. of E&C, STJIT RanebennurDocument520 pages0 4th Sem LIC Full Notes (6 Chapters) by Arunkumar G, Lecturer Dept. of E&C, STJIT RanebennurAmarjeet Kumar100% (5)

- List of Figures and Tables NomenclatureDocument72 pagesList of Figures and Tables NomenclatureSivasreedhar ReddyNo ratings yet

- LIST OF MAH FACTORIESDocument7,996 pagesLIST OF MAH FACTORIESmanishaNo ratings yet

- J-970 Basic Circuit Analysis PDFDocument1 pageJ-970 Basic Circuit Analysis PDFbasab0% (1)

- Crash Course Crash Course: Niper-2021Document7 pagesCrash Course Crash Course: Niper-2021ramesh joshiNo ratings yet

- Placement Report MNIT, 2018Document22 pagesPlacement Report MNIT, 2018AYUSH JAIN50% (2)

- Lecture # 11 ELENDocument17 pagesLecture # 11 ELENPhD EENo ratings yet

- EMI Control Techniques for Electronics SystemsDocument10 pagesEMI Control Techniques for Electronics SystemsYuvaraja50% (2)

- GE8151 NotesDocument118 pagesGE8151 NotesriyaNo ratings yet

- Resume: Research Work in M. Pharm: Project Title: Anti-Diabetic Activity of Bauhinia Veregate and Borriria ArticularisDocument3 pagesResume: Research Work in M. Pharm: Project Title: Anti-Diabetic Activity of Bauhinia Veregate and Borriria ArticularisHiren JethwaNo ratings yet

- Nanyang Mba Career ReportDocument18 pagesNanyang Mba Career ReportRyanNo ratings yet

- Brochure 2017-18 WebDocument64 pagesBrochure 2017-18 WebrahulNo ratings yet

- Ee6602 Embedded SystemsDocument3 pagesEe6602 Embedded SystemsNO R100% (1)

- GE8077 Total Quality Management: Handled By, Mrs H. Shanmugavalli Assistant Prof/ IT Kingston Engineering CollegeDocument79 pagesGE8077 Total Quality Management: Handled By, Mrs H. Shanmugavalli Assistant Prof/ IT Kingston Engineering CollegeShanmugavalli VijaiNo ratings yet

- PCB Assembly Business Setup GuideDocument11 pagesPCB Assembly Business Setup GuideAzeez BashaNo ratings yet

- Stakeholder-Register-Example Electric-Car PDFDocument1 pageStakeholder-Register-Example Electric-Car PDFOsama RehmanNo ratings yet

- Biotechnology Final Year Projects - InfiparkDocument5 pagesBiotechnology Final Year Projects - InfiparkmengelhuNo ratings yet

- Pantone and K100 Reverse White MedicineDocument16 pagesPantone and K100 Reverse White MedicinepaanarNo ratings yet

- List of STP Units - Indore: Sr. No Company Name AddressDocument1 pageList of STP Units - Indore: Sr. No Company Name AddressGayathriNo ratings yet

- Pharma CompaniesDocument20 pagesPharma CompaniesamberNo ratings yet

- ED Module 1Document41 pagesED Module 1ನಂದನ್ ಎಂ ಗೌಡNo ratings yet

- Syllabus - CO Wise - Programming For Problem Solving (KCS-101/KCS-201) - 2020-21Document192 pagesSyllabus - CO Wise - Programming For Problem Solving (KCS-101/KCS-201) - 2020-21ishika sharmaNo ratings yet

- BSC PhysicsDocument57 pagesBSC PhysicsEagle HawkNo ratings yet

- Course File SEMDocument24 pagesCourse File SEMRene DevNo ratings yet

- Antihypertensive DrugsDocument7 pagesAntihypertensive Drugshamadadodo7No ratings yet

- Ec8453 Lic 2 MarksDocument28 pagesEc8453 Lic 2 Markskarthikamagesh100% (1)

- Computer Centre Naac Presentation 2013Document32 pagesComputer Centre Naac Presentation 2013Nilesh BhoyarNo ratings yet

- CCNA Network Engineer ResumeDocument2 pagesCCNA Network Engineer Resumeyadav123456No ratings yet

- Asg3 Solns SketchDocument7 pagesAsg3 Solns SketchRajatAroraNo ratings yet

- Mini Project Diary 2021-22Document23 pagesMini Project Diary 2021-222BA19IS041 Nikita ShettiNo ratings yet

- Chapter 04 RISC VDocument130 pagesChapter 04 RISC VTrí ĐôNo ratings yet

- Pharma Book ListDocument6 pagesPharma Book ListMedBook DokanNo ratings yet

- Home Science (Eng) Ch-11Document16 pagesHome Science (Eng) Ch-11Ravi ShankarNo ratings yet

- Mobile App for BSES Power ConsumersDocument7 pagesMobile App for BSES Power ConsumersK Kunal RajNo ratings yet

- GE3151 - Python SyllabusDocument2 pagesGE3151 - Python Syllabussaro2330No ratings yet

- Assembly Language Short Notes by VuDocument16 pagesAssembly Language Short Notes by VuSyed HadiNo ratings yet

- Human PhysiologyDocument26 pagesHuman PhysiologyLaya ShrbagiNo ratings yet

- CNC Lesson PlanDocument8 pagesCNC Lesson Planmagesh.mxNo ratings yet

- Cloud Computing Course File for III B.Tech II SemesterDocument8 pagesCloud Computing Course File for III B.Tech II SemesterMukundha ChNo ratings yet

- Made Easy Postal ESE SyllabusDocument3 pagesMade Easy Postal ESE SyllabusutpalNo ratings yet

- DC Material PDFDocument149 pagesDC Material PDFCHARANNo ratings yet

- Study Plan EE-221 Digital Logic DesignDocument5 pagesStudy Plan EE-221 Digital Logic Designnauman yasinNo ratings yet

- DLD Theory F23Document4 pagesDLD Theory F23Imran Ahmad AhmadNo ratings yet

- CS2031 Digital Logic Design OBE AdnanDocument4 pagesCS2031 Digital Logic Design OBE Adnanseemialvi6No ratings yet

- VFD vs Soft Starter: Key Differences for Motor ControlDocument5 pagesVFD vs Soft Starter: Key Differences for Motor ControlZain JavedNo ratings yet

- List of Approved INGOsDocument4 pagesList of Approved INGOsZain JavedNo ratings yet

- My Experience of Digital Literacy TransitionDocument17 pagesMy Experience of Digital Literacy TransitionZain JavedNo ratings yet

- List of Approved INGOs by CountryDocument4 pagesList of Approved INGOs by CountryZain JavedNo ratings yet

- Industrial Stitching Machine OperatorDocument26 pagesIndustrial Stitching Machine OperatorZain JavedNo ratings yet

- Freedom of Speech: A Right and ResponsibilityDocument4 pagesFreedom of Speech: A Right and ResponsibilityZain JavedNo ratings yet

- Scheme of StudiesDocument8 pagesScheme of StudiesZain JavedNo ratings yet

- Vol CodesDocument40 pagesVol CodesyennyNo ratings yet

- Topic Name: Sensory DesignDocument20 pagesTopic Name: Sensory DesignNandini DhakanNo ratings yet

- DesignGuidebook PDFDocument24 pagesDesignGuidebook PDFMarius BarticelNo ratings yet

- PressedDocument6 pagesPressedVijay KumarNo ratings yet

- FDocument7 pagesFmasheikh1980No ratings yet

- Design Requirements.: Design of Pre Engineered BuildingsDocument2 pagesDesign Requirements.: Design of Pre Engineered BuildingsdilipNo ratings yet

- Development of A Model Code For Direct Displacement Based Seismic Design Calvi 2009Document31 pagesDevelopment of A Model Code For Direct Displacement Based Seismic Design Calvi 2009pouyamhNo ratings yet

- Hp-Ar-101 - Basement Floor Plan PDFDocument1 pageHp-Ar-101 - Basement Floor Plan PDFRupesh TripathiNo ratings yet

- Object Oriented Analysis and Design UNIT-4 Learning MaterialDocument33 pagesObject Oriented Analysis and Design UNIT-4 Learning Materialsoumya moturiNo ratings yet

- Introduction To Chemical Process DesignDocument45 pagesIntroduction To Chemical Process DesignAhmed AnsariNo ratings yet

- Design Studio Pedagogy Horizons For The PDFDocument20 pagesDesign Studio Pedagogy Horizons For The PDFCamilo Andres Reyes PachecoNo ratings yet

- Designing Wearable Sensors For Preventative HealthDocument355 pagesDesigning Wearable Sensors For Preventative HealthjorgejbmNo ratings yet

- ReportSamplefinalone 1Document33 pagesReportSamplefinalone 1ShortswallahNo ratings yet

- Operations ManagementDocument336 pagesOperations ManagementJaya Mishra100% (1)

- PUBLIC ART Making It HappenDocument73 pagesPUBLIC ART Making It Happenspynoza81No ratings yet

- Design, Prototyping and ConstructionDocument17 pagesDesign, Prototyping and ConstructionUsmanHaiderNo ratings yet

- Principles of Language Curriculum DesignDocument3 pagesPrinciples of Language Curriculum DesignSteven Waruwu100% (1)

- LPKF E44 PCB Mill Getting Started Guide: Student Workshop KTH Simon Carlsson, Emil BergvallDocument21 pagesLPKF E44 PCB Mill Getting Started Guide: Student Workshop KTH Simon Carlsson, Emil BergvallTales AugustoNo ratings yet

- DBD ProfileDocument3 pagesDBD ProfileStudio 28.5NNo ratings yet

- MBA (Global) : Deakin Business School, AustraliaDocument14 pagesMBA (Global) : Deakin Business School, AustraliaDaniel GnanaselvamNo ratings yet

- CIPS ISP Application Education Plus Experience RouteDocument9 pagesCIPS ISP Application Education Plus Experience Routekashyap_thakerNo ratings yet

- Sparx Enterprise ArchitectureDocument323 pagesSparx Enterprise ArchitecturebillNo ratings yet

- Operation StrategyDocument5 pagesOperation StrategyShriram RajasekaranNo ratings yet

- DSGN DRWN CHKD Appd AG CB CCS CB: GMR Goa International Airport LimitedDocument10 pagesDSGN DRWN CHKD Appd AG CB CCS CB: GMR Goa International Airport LimitedAditya KNo ratings yet

- Design and Implementation of Full Adder Using Different XOR GatesDocument5 pagesDesign and Implementation of Full Adder Using Different XOR GatesEvans MuokiNo ratings yet

- Shaik Salman - MEP ModelerDocument3 pagesShaik Salman - MEP ModelerAhmed RizkNo ratings yet

- A Competency-Directed Curriculum For Industrial Design EngineeringDocument6 pagesA Competency-Directed Curriculum For Industrial Design EngineeringDipu GeorgeNo ratings yet

- CS2013 Final ReportDocument518 pagesCS2013 Final ReportDiponegoro Muhammad KhanNo ratings yet

- Module 01 Interior DesignDocument17 pagesModule 01 Interior DesignGiba Emese100% (1)

- 2014 Masters Guide PDFDocument21 pages2014 Masters Guide PDFVaggy GewrgaliNo ratings yet