Professional Documents

Culture Documents

Smart Octal Low-Side Switch: Features Product Summary

Uploaded by

Ariel MercochaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Smart Octal Low-Side Switch: Features Product Summary

Uploaded by

Ariel MercochaCopyright:

Available Formats

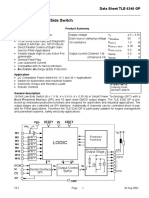

Data Sheet TLE 6230 GP

Smart Octal Low-Side Switch

Supply voltage VS 4.5 – 5.5 V

Features Drain source clamping voltage VDS(AZ)max 55 V

Product Summary On resistance RON 0.75 Ω

• Short Circuit Protection Output current (all outp.ON equal) ID(NOM) 500 mA

• Overtemperature Protection

• Overvoltage Protection (individually) 1 A

• 16 bit Serial Data Input and Diagnos-

tic Output (2 bit/ch. acc. SPI protocol)

• Direct Parallel Control of Four Channels for PWM Applications

• Parallel Inputs High or Low Active Programmable

• General Fault Flag

• Low Quiescent Current

• Compatible with 3,3 V Micro Controllers

• Electostatic Discharge (ESD) Protection

• Green Product (RoHS compliant)

• AEC Qualified

PG-DSO 36

Application

• µC Compatible Power Switch for 12 V and 24V Applications

• Switch for Automotive and Industrial Systems

• Solenoids, Relays and Resistive Loads

• Robotic Controls

General description

Octal Low-Side Switch in Smart Power Technology (SPT) with a Serial Peripheral Interface (SPI) and

eight open drain DMOS output stages. The TLE 6230 GP is protected by embedded protection func-

tions and designed for automotive and industrial applications. The output stages are controlled via an

SPI Interface. Additionally four channels can be controlled direct in parallel for PWM applications.

Therefore the TLE 6230 GP is particularly suitable for engine management and powertrain systems.

PRG RESET VS FAULT

GND VS

VBB

IN1 Protection

Functions

IN2 as Ch. 1 LOGIC

IN3 as Ch. 1

OUT1

Output Stage

IN4 as Ch. 1

16 1 4

SCLK 8 8

Output Control

SI Serial Interface

SPI Buffer OUT8

CS

SO

GND

V2.3 Page 1 18. Nov. 2009

Data Sheet TLE 6230 GP

Block Diagram

Detailed Block Diagram

RESET FAULT VS

Channel 1

Normal function

GND VS SCB/Overload

PRG

Open load

short to ground

IN1

&

Output Stage

OUT1

IN2 OUT2

& Channel 2

IN3

& Channel 3 OUT3

IN4

& Channel 4 OUT4

Channel 5 OUT5

SO Channel 6 OUT6

SPI

SI Interface

16 bit Channel 7 OUT7

SCLK

Channel 8 OUT8

CS

GND

V2.3 Page 2 18. Nov. 2009

Data Sheet TLE 6230 GP

Pin Description Pin Configuration (Top view)

Pin Symbol Function GND 1• 36 GND

1 GND Ground NC 2 35 NC

2 NC not connected NC 3 34 NC

3 NC not connected OUT1 4 33 OUT8

4 OUT1 Power Output Channel 1 OUT2 5 32 OUT7

IN1 6 31 NC

5 OUT2 Power Output Channel 2

IN2 7 30 NC

6 IN1 Input Channel 1

VS 8 29 SI

7 IN2 Input Channel 2 RESET 9 28 SCLK

8 VS Supply Voltage CS 10 27 SO

9 RESET Reset PRG 11 26 FAULT

10 CS Chip Select IN3 12 25 NC

11 PRG Program (inputs high or low-active) IN4 13 24 NC

12 IN3 Input Channel 3 OUT3 14 23 OUT6

OUT4 15 22 OUT5

13 IN4 Input Channel 4

NC 16 21 NC

14 OUT3 Power Output Channel 3

NC 17 20 NC

15 OUT4 Power Output Channel 4 GND 18 19 GND

16 NC not connected

Power SO 36

17 NC not connected

18 GND Ground

19 GND Ground

20 NC not connected

21 NC not connected

22 OUT5 Power Output Channel 5

23 OUT6 Power Output Channel 6

24 NC not connected

25 NC not connected

26 FAULT General Fault Flag

27 SO Serial Data Output

28 SCLK Serial Clock

29 SI Serial Data Input

30 NC not connected

31 NC not connected

32 OUT7 Power Output Channel 7

33 OUT8 Power Output Channel 8

34 NC not connected

35 NC not connected

36 GND Ground

Heat Slug internally connected to ground pins

V2.3 Page 3 18. Nov. 2009

Data Sheet TLE 6230 GP

Maximum Ratings for Tj = – 40°C to 150°C

Parameter Symbol Values Unit

Supply Voltage VS -0.3 ... + 7 V

Continuous Drain Source Voltage (OUT1...OUT8) VDS 40 V

Input Voltage, All Inputs and Data Lines VIN - 0.3 ... + 7 V

2)

Load Dump Protection VLoad Dump = UP+US; UP=13.5 V VLoad Dump V

With Automotive Relay Load RL = 70 Ω 80

RI1)=2 Ω; td=400ms; IN = low or high

With RL= 24 Ω; RI=2 Ω; td=400ms; IN = high or low 52

Operating Temperature Range Tj - 40 ... + 150 °C

Storage Temperature Range Tstg - 55 ... + 150

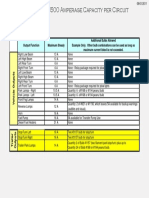

Output Current per Channel (see el. characteristics) ID(lim) ID(lim) min A

Output Current per Channel @ TA = 25°C ID 500 mA

(All 8 Channels ON; Mounted on PCB ) 3)

Output Clamping Energy (single pulse) EAS 50 mJ

ID = 0.5 A

Power Dissipation (mounted on PCB) @ TA = 25°C Ptot 3.3 W

Electrostatic Discharge Voltage (Human Body Model)

according to MIL STD 883D, method 3015.7 and EOS/ESD

assn. standard S5.1 – 1993

Output 1-8 Pins VESD 2000 V

All other Pins VESD 2000 V

DIN Humidity Category, DIN 40 040 E

IEC Climatic Category, DIN IEC 68-1 40/150/56

Thermal Resistance

junction - case RthJC 5 K/W

junction - ambient @ min. footprint RthJA 50

junction - ambient @ 6 cm2 cooling area with heat pipes 38

PCB with heat pipes,

Minimum footprint backside 6 cm2 cooling area

1)

RI=internal resistance of the load dump test pulse generator LD200

2)

VLoadDump is setup without DUT connected to the generator per ISO 7637-1 and DIN 40 839.

3)

Output current rating so long as maximum junction temperature is not exceeded. At TA = 125 °C the output

current has to be calculated using RthJA according mounting conditions.

V2.3 Page 4 18. Nov. 2009

Data Sheet TLE 6230 GP

Electrical Characteristics

Parameter and Conditions Symbol Values Unit

VS = 4.5 to 5.5 V ; Tj = - 40 °C to + 150 °C ; Reset = H min typ max

(unless otherwise specified)

1. Power Supply, Reset

Supply Voltage4 VS 4.5 -- 5.5 V

5

Supply Current (outputs ON) IS(ON) -- 1 2 mA

5

Supply Current (outputs OFF) IS(OFF) -- 1 2 mA

Minimum Reset Duration tReset,min 10 -- -- µs

2. Power Outputs

ON Resistance VS = 5 V; ID = 500 mA TJ = 25°C RDS(ON) -- 0.8 1 Ω

TJ = 150°C -- -- 1.7

Output Clamping Voltage Output OFF VDS(AZ) 40 -- 55 V

Current Limit ID(lim) 1 1.5 2 A

Output Leakage Current VReset = L ID(lkg) -- -- 5 µA

Vbb=12V

Turn-On Time ID = 0.5 A, resistive load tON -- 8 12 µs

Turn-Off Time ID = 0.5 A, resistive load tOFF -- 6 10 µs

3. Digital Inputs

Input Low Voltage VINL - 0.3 -- 1.0 V

Input High Voltage VINH 2.0 -- -- V

Input Voltage Hysteresis VINHys 50 100 200 mV

Input Pull Down/Up Current (IN1 ... IN4) IIN(1..4) 20 50 100 µA

PRG, Reset Pull Up Current IIN(PRG,Res) 20 50 100 µA

Input Pull Down Current (SI, SCLK) IIN(SI,SCLK) 10 20 50 µA

Input Pull Up Current ( CS ) IIN(CS) 10 20 50 µA

4. Digital Outputs (SO, FAULT )

SO High State Output Voltage ISOH = 2 mA VSOH VS - 0.4 -- -- V

SO Low State Output Voltage ISOL = 2.5 mA VSOL -- -- 0.4 V

Output Tri-state Leakage Current CS = H, 0 ≤ VSO ≤ VS ISOlkg -10 0 10 µA

FAULT Output Low Voltage IFAULT = 1.6 mA VFAULTL -- -- 0.4 V

4

For VS < 4.5V the power stages are switched according the input signals and data bits or are definitely switched

off. This undervoltage reset gets active at VS = 3V (typ. value) and is guaranteed by design.

5

For Reset = H.

V2.3 Page 5 18. Nov. 2009

Data Sheet TLE 6230 GP

Electrical Characteristics cont.

Parameter and Conditions Symbol Values Unit

VS = 4.5 to 5.5 V ; Tj = - 40 °C to + 150 °C ; Reset = H min typ max

(unless otherwise specified)

5. Diagnostic Functions

Open Load Detection Voltage VDS(OL) VS -2.5 VS -2 VS -1.3 V

Output Pull Down Current IPD(OL) 50 90 150 µA

Fault Delay Time td(fault) 50 100 200 µs

Short to Ground Detection Voltage VDS(SHG) VS –3.3 VS -2.9 VS -2.5 V

Short to Ground Detection Current ISHG -50 -100 -150 µA

Current Limitation; Overload Threshold Current ID(lim) 1...8 1 1.5 2 A

6

Overtemperature Shutdown Threshold Tth(sd) 170 -- 200 °C

Hysteresis6 Thys -- 10 -- K

6. SPI-Timing

Serial Clock Frequency (depending on SO load) fSCK DC -- 5 MHz

Serial Clock Period (1/fclk) tp(SCK) 200 -- -- ns

Serial Clock High Time tSCKH 50 -- -- ns

Serial Clock Low Time tSCKL 50 -- -- ns

Enable Lead Time (falling edge of CS to rising edge of CLK) tlead 250 -- -- ns

Enable Lag Time (falling edge of CLK to rising edge of CS ) tlag 250 --- -- ns

Data Setup Time (required time SI to falling of CLK) tSU 20 -- -- ns

Data Hold Time (falling edge of CLK to SI) tH 20 -- -- ns

6

Disable Time @ CL = 50 pF tDIS -- -- 150 ns

7

Transfer Delay Time tdt 200 -- -- ns

( CS high time between two accesses)

Data Valid Time CL = 50 pF6 tvalid -- 110 160 ns

CL = 100 pF6 -- 120 170

CL = 220 pF6 -- 150 200

6

This parameter will not be tested but guaranteed by design

7

This time is necessary between two write accesses. To get the correct diagnostic information, the transfer delay

time has to be extended to the maximum fault delay time td(fault)max = 200µs.

V2.3 Page 6 18. Nov. 2009

Data Sheet TLE 6230 GP

Functional Description

The TLE 6230 GP is an octal-low-side power switch which provides a serial peripheral inter-

face (SPI) to control the 8 power DMOS switches, as well as diagnostic feedback. The power

transistors are protected against short to VBB, overload, overtemperature and against over-

voltage by an active zener clamp.

The diagnostic logic recognizes a fault condition which can be read out via the serial diagnostic

output (SO).

Circuit Description

Output Stage Control

Each output is independently controlled by an output latch and a common reset line, which

disables all eight outputs. Serial data input (SI) is read on the falling edge of the serial clock. A

logic high input data bit turns the respective output channel ON, a logic low data bit turns it

OFF. CS must be low whilst shifting all the serial data into the device. A low-to-high transition

of CS transfers the serial data input bits to the output buffer.

Special conditions for Channel 1 to 4:

In addition to the serial control of the outputs it is possible to control channel 1 to channel 4

directly in parallel for PWM applications. These inputs are high or low active (programmable

via PRG pin) and ANDed with the SPI control bit.

The table shows the AND-operation of the parallel

IN 1 - 4 SPI-Bit 0 - 3 OUT 1 - 4

input pin (here active high) and the corresponding

0 0 OFF

SPI bit. For an application where the parallel input is

always "ON", it is possible to switch the channel 0 1 OFF

OFF via the SPI bit, e.g. for diagnosis in OFF-state. 1 0 OFF

1 1 ON

⇒ SPI Priority for OFF-state

Operation with parallel inputs: Set SPI bits to logic high.

Operation via SPI: Connect parallel inputs to logic high (if programmed to active high).

PRG - Program pin. PRG = High (VS): Parallel inputs Channel 1 to 4 are high active

PRG = Low (GND): Parallel inputs Channel 1 to 4 are low active.

If the parallel input pins are not connected (independent of high or low activity) it is guaranteed

that the channels 1 to 4 are switched OFF.

PRG pin itself is internally pulled up when it is not connected.

V2.3 Page 7 18. Nov. 2009

Data Sheet TLE 6230 GP

Power Transistor Protection Functions8)

Each of the eight output stages has its own zener clamp, which causes a voltage limitation at

the power transistor when solenoid loads are switched off. The outputs are provided with a

current limitation set to a minimum of 1 A. The continuous current for each channel is 500 mA

(all channels ON).

Each output is protected by embedded protection functions. In the event of an overload or

short to supply, the current is internally limited and the corresponding bit combination is set

(early warning). If this operation leads to an overtemperature condition, a second protection

level (about 170 °C) will change the output into a low duty cycle PWM (selective thermal shut-

down with restart) to prevent critical chip temperatures.

SPI Signal Description

CS - Chip Select. The system microcontroller selects the TLE 6230 GP by means of the CS

pin. Whenever the pin is in a logic low state, data can be transferred from the µC and vice

versa.

CS High to Low transition: - diagnostic status information is transferred from the power

outputs into the shift register.

- serial input data can be clocked in from then on

- SO changes from high impedance state to logic high or low

state corresponding to the SO bits

CS Low to High transition: - transfer of SI bits from shift register into output buffers

- reset of diagnosis register

To avoid any false clocking the serial clock input pin SCLK should be logic low state during

high to low transition of CS . When CS is in a logic high state, any signals at the SCLK and SI

pins are ignored and SO is forced into a high impedance state.

SCLK - Serial Clock. The system clock pin clocks the internal shift register of the TLE

6230 GP. The serial input (SI) accepts data into the input shift register on the falling edge of

SCLK while the serial output (SO) shifts diagnostic information out of the shift register on the

rising edge of serial clock. It is essential that the SCLK pin is in a logic low state whenever chip

select CS makes any transition. The number of clock pulses will be counted during a chip se-

lect cycle. The received data will only be accepted, if exactly 16 clock pulses were counted

during CS is active.

SI - Serial Input. Serial data bits are shifted in at this pin, the most significant bit first. SI infor-

mation is read in on the falling edge of SCLK. Input data is latched in the shift register and then

transferred to the control buffer of the output stages.

The input data consists of two bytes - a "control byte” followed by a "data byte". The control

byte contains the information as to whether the data byte will be accepted or ignored (see di-

agnostics section). The data byte contains the input information for the eight channels. A logic

8)

The integrated protection functions prevent an IC destruction under fault conditions and may not be used in normal operation or perma-

nently

V2.3 Page 8 18. Nov. 2009

Data Sheet TLE 6230 GP

high level at this pin (within the data byte) will switch on the power switch, provided that the

corresponding parallel input is also switched on (AND-operation for channel 1 to 4).

SO - Serial Output. Diagnostic data bits are shifted out serially at this pin, the most significant

bit first. SO is in a high impedance state until the CS pin goes to a logic low state. New diag-

nostic data will appear at the SO pin following the rising edge of SCLK.

RESET - Reset pin. If the reset pin is in a logic low state, it clears the SPI shift register and

switches all outputs OFF. An internal pull-up structure is provided on chip.

Diagnostics

FAULT - Fault pin. There is a general fault pin (open drain) which shows a high to low transi-

tion as soon as an error occurs for any one of the eight channels. This fault indication can be

used to generate a µC interrupt. Therefore a ‘diagnosis’ interrupt routine need only be called

after this fault indication. This saves processor time compared to a cyclic reading of the SO

information.

As soon as a fault occurs, the fault information is latched into the diagnosis register. A new

error will over-write the old error report. Serial data out pin (SO) is in a high impedance state

when CS is high. If CS receives a LOW signal, all diagnosis bits can be shifted out serially.

The rising edge of CS will reset all error registers.

Diagnostic Serial Data Out SO

15 14 13 12 11 10 9 8 - ----

Ch.8 Ch.7 Ch.6 Ch.5

HH Normal function

HL Overload, Shorted Load or Overtemperature

LH Open Load

LL Shorted to Ground

Figure 1: Two bits per channel diagnostic feedback

There are two diagnostic bits per channel configured as shown in Figure 1.

Normal function: The bit combination HH indicates that there is no fault condition, i.e. normal

function.

Overload, Short Circuit to Battery (SCB) or Overtemperature: HL is set when the current

limitation gets active, i.e. there is a overload, short to supply or overtemperature condition.

Open load: An open load condition is detected when the drain voltage decreases below 3 V

(typ.). LH bit combination is set.

Short Circuit to GND: If a drain to ground short circuit exists and the drain to ground current

exceeds 100 µA, short to ground is detected and the LL bit combination is set.

V2.3 Page 9 18. Nov. 2009

Data Sheet TLE 6230 GP

A definite distinction between open load and short to ground is guaranteed by design.

The standard way of obtaining diagnostic information is as follows:

Clock in serial information into SI pin and wait approximately 150 µs to allow the outputs toset-

tle. Clock in the identical serial information once again - during this process the data coming

out at SO contains the bit combinations representing the diagnosis conditions as described in

figure 1.

By means of the control byte it is possible either to:

a) control the eight outputs according to the data byte, as well as being able to read the

diagnostic information

or b) purely get diagnostic information without changing the state of the outputs.

a) Serial Control of Outputs

HHHHHHHH LHLHHLLL : Serial input information

1442443 14 4244 3

Control Byte Data Byte

Control byte is set to FFhex: Data byte will be accepted. The outputs will be switched ON or

OFF according to the information of the data byte and the parallel inputs (Channel 1 to 4 be-

cause of AND operation).

All other control words except the one for 'Diagnosis Only = 00hex' will also be accepted as a

valid control word and the data will be accepted.

Example: HLLHLHLH DDDDDDDD: Outputs will switch according to the data bits.

b) Diagnosis Only

LLLLLLLL XXXXXXXX : Serial input information

144244 3 144244 3

Control Byte Data Byte

Control byte is set to 00hex: Data byte will be ignored. Diagnostic information can be read out

at any time with no change of the switching conditions. Only 00hex means 'Diagnosis Only'.

V2.3 Page 10 18. Nov. 2009

Data Sheet TLE 6230 GP

Timing Diagrams

CS

SCLK

SI C O N T R O L Byte 7 6 5 4 3 2 1 0

MSB LSB

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SO

Figure 2: Serial Interface

Figure 3: Input Timing Diagram

CS

0.7VS

0.2 VS tdt

tlag

tSCKH

tlead 0.7VS

SCLK 0.2VS

tSCKL

tSU

tH

0.7VS

SI

0.2VS

Figure 4:

0.7 VS CS

SCLK 0.2 VS

tvalid

tDis

SO 0.7 VS SO

0.2 VS

SO

0.7 VS

0.2 VS

SO Valid Time Waveforms Enable and Disable Time Waveforms

V2.3 Page 11 18. Nov. 2009

Data Sheet TLE 6230 GP

VIN

tON tOFF

VDS

80%

20%

t

Figure 5: Power Outputs

Timing is valid for resistive load with parallel and serial control.

Rising edge of chip select initiates the switching

Application Circuits

VBB

VS = 5V C

10k

VS

PRG

OUT1

FAULT OUT2

RESET

IN1

µC IN2

e.g. C167 IN3 TLE

IN4

6230 GP

MTSR SI

MRST SO OUT8

CLK CLK

P xy CS

GND

V2.3 Page 12 18. Nov. 2009

Data Sheet TLE 6230 GP

Typical electrical Characteristics

Drain-Source on-resistance

RDS(ON) = f (Tj) ; Vs = 5V

Typical Drain- Source ON-Resistance Channel 1-8

1,5

1,4

1,3

1,2

RDS(ON) [Ohm]

1,1

1

0,9

0,8

0,7

0,6

0,5

0,4

-50 -25 0 25 50 75 100 125 150 175

Tj[°C]

Figure 6 : Typical ON Resistance versus Junction-Temperature

Channel 1-8

Output Clamping Voltage

VDS(AZ) = f (Tj) ; Vs = 5V

Typical Clamping Voltage Channel 1-8

45

44

VDS(AZ) [V]

43

42

41

-50 -25 0 25 50 75 100 125 150 175

Tj[°C]

Figure 7 : Typical Clamp Voltage versus Junction-Temperature

Channel 1-8

V2.3 Page 13 18. Nov. 2009

Data Sheet TLE 6230 GP

Maximum single clamp Energy

TLE 6230, single Clamp, linear Current Ramp

Maximum Energy Rating @ Tj=150°C

300

250

200

150

100

50

0

0 0,2 0,4 0,6 0,8 1 1,2 1,4

Peak current [A]

Figure 8 : Maximum Clamp Energy (single event) versus Peak Current

Channel 1-8

Parallel SPI Configuration

Engine Management

Injector 1

P x.1-4

4 Application

4 PW M

Channels Injector 2 TLE 6230 GP in combination

with TLE 6240 GP (16-fold

MTSR SI Injector 3 switch) for relays and general

TLE

MRST SO

6220 GP

purpose loads and TLE 6220

CLK Injector 4

CLK

P x.y CS Quad GP (quad switch) to drive the

CS

injector valves. This arrange-

4

ment covers the numerous

P x.1-4 4 PW M

Channels

loads to be driven in a modern

Engine Manage-

µC ment/Powertrain system. From

SI

SO TLE 28 channels in sum 16 can be

C167 CLK

6230 GP controlled direct in parallel for

Octal

P x.y CS PWM applications.

8

P x.1-8 8 PW M

Channels

SI

SO TLE

CLK 6240 GP

P x.y CS 16-fold

V2.3 Page 14 18. Nov. 2009

Data Sheet TLE 6230 GP

Package and Ordering Code

(all dimensions in mm)

PG-DSO 36

TLE 6230 GP

V2.3 Page 15 18. Nov. 2009

Data Sheet TLE 6230 GP

Edition 2008-04-17

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2008 Infineon Technologies AG

All Rights Reserved.

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteris-

tics. With respect to any examples or hints given herein, any typical values stated herein and/or any information

regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabili-

ties of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any

third party.

Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest In-

fineon Technologies Office (www.infineon.com).

Warnings

Due to technical requirements, components may contain dangerous substances. For information on the

types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the ex-

press written approval of Infineon Technologies, if a failure of such components can reasonably be ex-

pected to cause the failure of that life-support device or system or to affect the safety or effectiveness of

that device or system. Life support devices or systems are intended to be implanted in the human body

or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to as-

sume that the health of the user or other persons may be endangered.

V2.3 Page 16 18. Nov. 2009

You might also like

- 2005 - 2008 - Grand - Cherokee Service Manual (CRD Addendum)Document197 pages2005 - 2008 - Grand - Cherokee Service Manual (CRD Addendum)Anonymous 3oqdIISc80% (5)

- Mahindra PIK-UP Service Manual PDFDocument620 pagesMahindra PIK-UP Service Manual PDFHector Muñoz Sepulveda93% (46)

- Pinout Euro-2Document3 pagesPinout Euro-2SUELEN100% (1)

- Electronic Control Module Diagnostics GuideDocument152 pagesElectronic Control Module Diagnostics GuideAriel MercochaNo ratings yet

- 117 Mitsubishi Triton KA4 KB4 KB8 Factory Service ManualDocument558 pages117 Mitsubishi Triton KA4 KB4 KB8 Factory Service Manualโจ้ สแปร์แร็ค91% (44)

- (TM) Fiat Manual de Taller Fiat Ducato 2007 Al 2011 en InglesDocument85 pages(TM) Fiat Manual de Taller Fiat Ducato 2007 Al 2011 en InglesAriel Mercocha67% (3)

- Pinout Toyota 4runner 2007 - Motor 1GR-FEDocument4 pagesPinout Toyota 4runner 2007 - Motor 1GR-FEAriel Mercocha100% (1)

- Trouble Clearing AlarmDocument65 pagesTrouble Clearing AlarmNurrochman Prabowo71% (7)

- Smart Octal Low-Side Switch: LogicDocument17 pagesSmart Octal Low-Side Switch: Logicjuan echeverryNo ratings yet

- Tle 62326 Low Side SwitchDocument19 pagesTle 62326 Low Side SwitchDiego CaceresNo ratings yet

- DatasheetDocument16 pagesDatasheetAndres GuerreroNo ratings yet

- Infineon Tle7230r Ds v03 04 enDocument15 pagesInfineon Tle7230r Ds v03 04 enياسين الطنفوريNo ratings yet

- TLE6240GPDocument23 pagesTLE6240GPNoelNo ratings yet

- TLE6225GPDocument10 pagesTLE6225GPNoelNo ratings yet

- TLE6225GDocument9 pagesTLE6225GNoelNo ratings yet

- Datasheet 1354Document70 pagesDatasheet 1354Liliana SiscaNo ratings yet

- Infineon TLE6244X DS v07 00 enDocument71 pagesInfineon TLE6244X DS v07 00 enAlexis VázquezNo ratings yet

- TLE7209 R InfineonDocument16 pagesTLE7209 R Infineonmobil benerNo ratings yet

- TB67H451FNG: PWM Chopper Type DC Brushed Motor DriverDocument21 pagesTB67H451FNG: PWM Chopper Type DC Brushed Motor Drivermalak na3eemNo ratings yet

- Features General Description: 3A, Ultra Low Dropout (0.23V Typical) Linear RegulatorDocument24 pagesFeatures General Description: 3A, Ultra Low Dropout (0.23V Typical) Linear RegulatorOdyem SadamNo ratings yet

- AOZ2023PIDocument11 pagesAOZ2023PIjuliocunachiNo ratings yet

- A3909 DatasheetDocument10 pagesA3909 DatasheetAleksMaslyc-zykNo ratings yet

- 7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetDocument32 pages7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetMecaSoftwareNo ratings yet

- Bts 740 S 2Document15 pagesBts 740 S 2Avs ElectronNo ratings yet

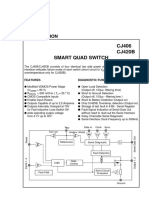

- CJ406 CJ420B Smart Quad Switch: SpecificationDocument9 pagesCJ406 CJ420B Smart Quad Switch: SpecificationAlexNo ratings yet

- Infineon Bts3408g Ds v01 05 enDocument14 pagesInfineon Bts3408g Ds v01 05 enblessingj19it018No ratings yet

- NJU72341 NewJapanRadioDocument14 pagesNJU72341 NewJapanRadioPedro Carlos da SilvaNo ratings yet

- 1-BTS707 20030923Document13 pages1-BTS707 20030923Шукурилло ШукурNo ratings yet

- XT2052 SilinktekDocument8 pagesXT2052 SilinktekRafael BrunoNo ratings yet

- M62429P/FP: Serial Data Control Dual Electronic VolumeDocument8 pagesM62429P/FP: Serial Data Control Dual Electronic VolumeahmedNo ratings yet

- 81r PDFDocument29 pages81r PDFDjalma MotaNo ratings yet

- L9651 SMART QUAD SWITCH with fault detectionDocument9 pagesL9651 SMART QUAD SWITCH with fault detectionVicenteAlvarezNo ratings yet

- YMF262_199110Document20 pagesYMF262_199110clkent2022No ratings yet

- TA84007PQ, TA84007SG, TA84007FG: PreliminaryDocument16 pagesTA84007PQ, TA84007SG, TA84007FG: PreliminarywijakesumaNo ratings yet

- LM393, LM293, LM2903, LM2903V, NCV2903 Low Offset Voltage Dual ComparatorsDocument9 pagesLM393, LM293, LM2903, LM2903V, NCV2903 Low Offset Voltage Dual ComparatorsMurillo SousaNo ratings yet

- 500 Ma Low-Noise LDO Regulator: Features General DescriptionDocument31 pages500 Ma Low-Noise LDO Regulator: Features General DescriptionEddie Kelvin Isidro LauraNo ratings yet

- MIC5209 500ma Low Noise LDO Regulator DS20005720B-2905047Document31 pagesMIC5209 500ma Low Noise LDO Regulator DS20005720B-2905047jaime elias gil rocaNo ratings yet

- Multi-Channel Power Supply IC For Car Audio Systems: DatasheetDocument44 pagesMulti-Channel Power Supply IC For Car Audio Systems: DatasheetPaulo Roberto s freireNo ratings yet

- bd34705ks2 eDocument39 pagesbd34705ks2 esatyamNo ratings yet

- Off-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Document13 pagesOff-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Renato Luther escalanteNo ratings yet

- APL5932A/B/C/D: Features General DescriptionDocument21 pagesAPL5932A/B/C/D: Features General DescriptionAku KudupiknikNo ratings yet

- 3A Ultra Low Dropout Linear Regulator: General DescriptionDocument11 pages3A Ultra Low Dropout Linear Regulator: General DescriptionIgha Intan PermataNo ratings yet

- Shenzhen Sunmoon Micro SM2255E - C881537Document12 pagesShenzhen Sunmoon Micro SM2255E - C881537Technical sidhuNo ratings yet

- Digi-Log Reverb Module (Btdr-3) : A Great Digital Reverb Sound That Easily Replaces A Spring Reverberation UnitDocument3 pagesDigi-Log Reverb Module (Btdr-3) : A Great Digital Reverb Sound That Easily Replaces A Spring Reverberation UnitDmedNo ratings yet

- BTDR 3Document3 pagesBTDR 3FlyinGaitNo ratings yet

- Features Applications: Slis124D - June 2006 - Revised February 2008Document21 pagesFeatures Applications: Slis124D - June 2006 - Revised February 2008Ahmad FarisNo ratings yet

- WS3620-LED Coor Const LAMP - WinsemiDocument7 pagesWS3620-LED Coor Const LAMP - WinsemivmsaNo ratings yet

- M65830BP/FP: PreliminaryDocument15 pagesM65830BP/FP: PreliminaryahmedNo ratings yet

- DatasheetDocument9 pagesDatasheetjim campbellNo ratings yet

- TLP2530, TLP2531: Digital Logic Isolation Line Receiver Power Supply Control Switching Power Supply Transistor InverterDocument8 pagesTLP2530, TLP2531: Digital Logic Isolation Line Receiver Power Supply Control Switching Power Supply Transistor InverterAkramNo ratings yet

- Out Products: Monolithic IC MM192x SeriesDocument16 pagesOut Products: Monolithic IC MM192x SeriesIbrain MoranNo ratings yet

- 546a2 Usb Power MagnagementDocument1 page546a2 Usb Power MagnagementJavierNo ratings yet

- NC7WZ07 ONSemiconductorDocument11 pagesNC7WZ07 ONSemiconductorsanchezmartellsNo ratings yet

- Control de Garganta TACDocument15 pagesControl de Garganta TACmario rosasNo ratings yet

- Data SheetDocument16 pagesData Sheetcarrei JohnNo ratings yet

- EM8635 ExcellianceMOSDocument13 pagesEM8635 ExcellianceMOSBruno MartinsNo ratings yet

- Features Description: Toy Motor Driver Series MX214Document8 pagesFeatures Description: Toy Motor Driver Series MX214jaluadiNo ratings yet

- SN74LS175 Quad D Flip-Flop: LOW Power SchottkyDocument8 pagesSN74LS175 Quad D Flip-Flop: LOW Power SchottkyDita RanantaNo ratings yet

- Rp130X Series: Low Noise 150ma Ldo RegulatorDocument33 pagesRp130X Series: Low Noise 150ma Ldo RegulatorСергей БрегедаNo ratings yet

- TMPA 8823-5VA4 Service Manual: IC Functions and I2C Bus ControlDocument16 pagesTMPA 8823-5VA4 Service Manual: IC Functions and I2C Bus ControlAndy AnsahNo ratings yet

- TB2906HQ Toshiba Bi-CMOS Digital Audio ICDocument17 pagesTB2906HQ Toshiba Bi-CMOS Digital Audio ICul3141592No ratings yet

- Sherwood RX-4105bDocument23 pagesSherwood RX-4105bGilberto0% (1)

- BTS 716G - Interruptor de PotênciaDocument14 pagesBTS 716G - Interruptor de PotênciaTiago LeonhardtNo ratings yet

- Az1084s2 Adje1Document21 pagesAz1084s2 Adje1Altamiro RochaNo ratings yet

- B 5.9L Series 2Document1 pageB 5.9L Series 2Ariel MercochaNo ratings yet

- Conector de BCM de Blazer 98 4.3lDocument3 pagesConector de BCM de Blazer 98 4.3lyanbarrientos100% (1)

- DR 8W-30 Fuel/Ignition System 8W - 30 - 1Document41 pagesDR 8W-30 Fuel/Ignition System 8W - 30 - 1Ariel MercochaNo ratings yet

- Pontiac Sunfire 2000Document99 pagesPontiac Sunfire 2000CybernaughtNo ratings yet

- Lathe - Spindle - Replacement - RemovalDocument3 pagesLathe - Spindle - Replacement - RemovalAriel MercochaNo ratings yet

- Codigos Presentes en d6m 168f04 190f02 298f02 299f13 468f08 722f03Document25 pagesCodigos Presentes en d6m 168f04 190f02 298f02 299f13 468f08 722f03Ed CalheNo ratings yet

- User-Manual-Elenos Etg 1000.10Document35 pagesUser-Manual-Elenos Etg 1000.10Ariel Mercocha50% (4)

- Transmission and Transfer CaseDocument1,062 pagesTransmission and Transfer CaseAriel MercochaNo ratings yet

- Brake Control System Nissan Frotier 2007Document152 pagesBrake Control System Nissan Frotier 2007Ariel MercochaNo ratings yet

- Indium SeriesDocument78 pagesIndium SeriesAriel MercochaNo ratings yet

- PhramhdlcpuDocument1 pagePhramhdlcpuAriel MercochaNo ratings yet

- Isuzu N-Series Elf Workshop Manual - Power Take Off With Oil Pump - LGPTO-WE-0091 PDFDocument63 pagesIsuzu N-Series Elf Workshop Manual - Power Take Off With Oil Pump - LGPTO-WE-0091 PDFRicardo Cornejo LafuenteNo ratings yet

- Driver Information System PDFDocument60 pagesDriver Information System PDFAriel Mercocha100% (1)

- Exterior & Interior Nissan Frontier 2007Document46 pagesExterior & Interior Nissan Frontier 2007Ariel MercochaNo ratings yet

- VW MK5 Jetta ElectricalSystem SSP 873403Document58 pagesVW MK5 Jetta ElectricalSystem SSP 873403paratonerq100% (2)

- Electrical Lighting System Troubleshooting GuideDocument150 pagesElectrical Lighting System Troubleshooting GuideAriel MercochaNo ratings yet

- Automatic Transmission PDFDocument334 pagesAutomatic Transmission PDFAriel MercochaNo ratings yet

- Engine Control System PDFDocument1,300 pagesEngine Control System PDFAriel Mercocha100% (2)

- Body, Lock and Security System Troubleshooting GuideDocument222 pagesBody, Lock and Security System Troubleshooting GuideAriel Mercocha100% (1)

- Automatic Transmission PDFDocument334 pagesAutomatic Transmission PDFAriel MercochaNo ratings yet

- Audio, Visual, Navigation & Telephone SystemDocument66 pagesAudio, Visual, Navigation & Telephone SystemAriel MercochaNo ratings yet

- GSIB25 XXDocument4 pagesGSIB25 XXedgar_dauzonNo ratings yet

- Front Final Drive Overhaul GuideDocument36 pagesFront Final Drive Overhaul GuideAriel MercochaNo ratings yet

- Automatic Transmission PDFDocument334 pagesAutomatic Transmission PDFAriel MercochaNo ratings yet

- Datasheet CPLDDocument16 pagesDatasheet CPLDFrancisco Ramferi García BedollaNo ratings yet

- ITC-Chapter 02-System Unit 39847 663Document21 pagesITC-Chapter 02-System Unit 39847 663Baktash AhmadiNo ratings yet

- North South University: Lab 3: Loading Effect of Voltage Divider CircuitDocument3 pagesNorth South University: Lab 3: Loading Effect of Voltage Divider CircuitNazmul Hasan 1911742042No ratings yet

- TE30 Electricity Meter Tester and Power Quality Analyzer Presentation enDocument19 pagesTE30 Electricity Meter Tester and Power Quality Analyzer Presentation enalejandroNo ratings yet

- Apu Carc 03 LMCDocument34 pagesApu Carc 03 LMCRamrekha AkshayNo ratings yet

- Xlogic Users Manual NewDocument339 pagesXlogic Users Manual NewJhon Jairo Medina DavisNo ratings yet

- Arranque y Paro de Un Motor de Cc. Con Un IGBTDocument20 pagesArranque y Paro de Un Motor de Cc. Con Un IGBTFernando VeraNo ratings yet

- CCM PFC Controller IC for High Power Efficiency AppsDocument2 pagesCCM PFC Controller IC for High Power Efficiency AppsAntonio Dalio67% (3)

- Instruction FormatDocument3 pagesInstruction FormatVishant ChaudharyNo ratings yet

- Fritzing - A Tutorial: Food Living Outside Play Technology WorkshopDocument7 pagesFritzing - A Tutorial: Food Living Outside Play Technology Workshopbluesky_1976No ratings yet

- Steber An LMS Impedance BridgeDocument7 pagesSteber An LMS Impedance BridgebigpriapNo ratings yet

- PanodicDocument5 pagesPanodicAlexander WieseNo ratings yet

- External Design Specification (EDS) Addendum: May 2016 Revision 001Document22 pagesExternal Design Specification (EDS) Addendum: May 2016 Revision 001draNo ratings yet

- AC To DC Power Conversion IEEEDocument40 pagesAC To DC Power Conversion IEEEvthiyagainNo ratings yet

- 9000 SPXDocument220 pages9000 SPXIsmael GraciaNo ratings yet

- Physics Project on Photo-Detector & LED UsesDocument14 pagesPhysics Project on Photo-Detector & LED UsesVARUN COMPUTERSNo ratings yet

- SX-4000+XSP-1000 Brochure (Eng) - PreviewDocument6 pagesSX-4000+XSP-1000 Brochure (Eng) - PreviewLiang ChengNo ratings yet

- Bidirectional DC-DC Converter for Automobile Electric SystemsDocument5 pagesBidirectional DC-DC Converter for Automobile Electric SystemsrowrerNo ratings yet

- QC H/G Drive: Qty Order No. Product DescriptionDocument2 pagesQC H/G Drive: Qty Order No. Product DescriptionSalim82 LKNo ratings yet

- LAB Experiment 1 GROUP NO.7Document6 pagesLAB Experiment 1 GROUP NO.7Janpherson BellecaNo ratings yet

- A CMOS Linear-in-dB High-Linearity Variable-Gain Amplifier For UWB ReceiversDocument4 pagesA CMOS Linear-in-dB High-Linearity Variable-Gain Amplifier For UWB Receiversapi-19755952No ratings yet

- A New Method For Online Thyristor Conduction Monitoring Based On Thyristor Current Waveform Recording in Static Excitation SystemDocument6 pagesA New Method For Online Thyristor Conduction Monitoring Based On Thyristor Current Waveform Recording in Static Excitation SystemR0B0T2013No ratings yet

- Arithmetic Logic Unit: CSE 429 Digital System DesignDocument36 pagesArithmetic Logic Unit: CSE 429 Digital System Designtor 3No ratings yet

- Antenna Line Configuration and VISIO Drawing Analysis: Tec-Neo-Man-RndDocument6 pagesAntenna Line Configuration and VISIO Drawing Analysis: Tec-Neo-Man-RndAziz EabNo ratings yet

- Digital Electronics exam questionsDocument8 pagesDigital Electronics exam questionsJc R. Poorana ChandranNo ratings yet

- Nutanix NX Series Cluster Specification ComparisonDocument1 pageNutanix NX Series Cluster Specification Comparisonpcoffey2240No ratings yet

- Formative Assessment: ElectronicsDocument4 pagesFormative Assessment: ElectronicsRoan ChuaNo ratings yet

- Ove Rhe Ad Proj Ec Tor SDocument11 pagesOve Rhe Ad Proj Ec Tor SEzekiel D. Rodriguez100% (2)

- ELE8331 Power System Control Dr. Nuraddeen MagajiDocument25 pagesELE8331 Power System Control Dr. Nuraddeen MagajiumarsaboNo ratings yet