Professional Documents

Culture Documents

Parallel Port

Uploaded by

Quốc BảoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Parallel Port

Uploaded by

Quốc BảoCopyright:

Available Formats

Parallel Port for

Altera DE Boards

For Quartus II 8

1 Core Overview

The Parallel Port interface provides data transfer in either input or output (or both) directions. The transfer is done

in parallel and it may involve from 1 to 32 bits. The number of bits, n , and the direction of transfer are specified by

the user through Altera’s SOPC Builder. This core is a version of the PIO Core with Avalon® Interface adapted for

use with Altera’s DE2/DE1 boards.

2 Functional Description

The Parallel Port registers are accessible as memory-mapped locations. A full description of the Parallel Port module

can be found in the document PIO Core with Avalon Interface, which is available in the literature section of Altera’s

web site. This core is different than the PIO Core with Avalon Interface as it has some presets to configure the

Parallel Port for the Simple I/O on the DE2/DE1 Boards, such as the LEDs, Switches, etc.

3 Instantiating the Core in SOPC Builder

See the PIO Core with Avalon Interface for details.

4 Software Programming Model

4.1 Register Map

The PIO can have up to four registers, as shown in Table 1. These registers have a configurable data width, n , which

can be set through the SOPC Builder Component Wizard.

Not all of these registers are generated in a given PIO interface. For example, the Direction register is included only

when a bidirectional interface is specified.

4.1.1 Data Register

This register holds the n bits of data that are transferred between the PIO interface and the Nios II processor. It can

be implemented as an input, output, or a bidirectional register by the SOPC Builder.

Altera Corporation - University Program 1

March 2009

PARALLEL P ORT FOR A LTERA DE B OARDS For Quartus II 8

Table 1. PIO register map

Offset in bytes Register name Read/Write Bits (n − 1). . . 0

Input R Data value currently on PIO inputs.

0 data

Output W New value to drive on PIO outputs.

4 direction R/W Individual direction control for each I/O port.

A value of 0 sets the direction to input; 1 sets

the direction to output.

8 interruptmask R/W IRQ enable/disable for each input port. Set-

ting a bit to 1 enables interrupts for the corre-

sponding port.

12 edgecapture R/W Edge detection for each input port.

4.1.2 Direction Register

The direction register defines the direction of the transfer for each of the n data bits when a bidirectional interface is

generated. A value of 0 sets the direction to input; a value of 1 sets the direction to output.

4.1.3 Interruptmask Register

The interruptmask register is used to enable interrupts from the input lines connected to the PIO.

4.1.4 Edgecapture Register

The edgecapture register indicates when a change of logic value is detected in the signals on the input lines connected

to the PIO.

Consult the PIO Core with Avalon Interface document for a full description of these registers and their functionality.

4.2 Programming with the Parallel Ports

The Parallel Port core is packaged with C-language device drivers accessible through the hardware abstraction layer

(HAL). These functions implement basic operations for the Parallel Port.

To use the functions, the C code must include the statement:

#include "altera_up_avalon_parallel_port.h"

2 Altera Corporation - University Program

March 2009

PARALLEL P ORT FOR A LTERA DE B OARDS For Quartus II 8

4.2.1 alt up parallel port open dev

Prototype: alt_up_parallel_port_dev* alt_up_parallel_port_open_dev(const

char *name)

Include: <altera_up_avalon_parallel_port.h>

Parameters: name – the parallel port name. For example, if the parallel port name in

SOPC Builder is "green_leds", then name should be "/dev/green_leds"

Returns: The corresponding device structure, or NULL if the device is not found.

Description: Open the parallel port device specified by name .

4.2.2 alt up parallel port read data

Prototype: unsigned int alt_up_parallel_port_read_data(alt_up_parallel_port_dev

*parallel_port)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device .

Returns: data – The data read for the parallel port.

Description: Read from the data register of the parallel port.

4.2.3 alt up parallel port write data

Prototype: void alt_up_parallel_port_write_data(alt_up_parallel_port_dev

*parallel_port, unsigned data)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device.

data – The data to be written to the parallel port.

Description: Write to the data register of the parallel port.

4.2.4 alt up parallel port read direction

Prototype: unsigned int alt_up_parallel_port_read_direction(alt_up_parallel_port_dev

*parallel_port)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device.

Returns: direction – The direction read for the parallel port.

Description: Read from the direction register of the parallel port.

4.2.5 alt up parallel port set port direction

Prototype: void alt_up_parallel_port_set_port_direction(alt_up_parallel_port_dev

*parallel_port, unsigned direction)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device.

Description: Set the direction register of the parallel port.

Altera Corporation - University Program 3

March 2009

PARALLEL P ORT FOR A LTERA DE B OARDS For Quartus II 8

4.2.6 alt up parallel port set all bits to input

Prototype: void alt_up_parallel_port_set_all_bits_to_input(alt_up_parallel_port_dev

*parallel_port)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device.

Description: Set the direction of all bits of the parallel port to be inputs.

4.2.7 alt up parallel port set all bits to output

Prototype: void alt_up_parallel_port_set_all_bits_to_output(alt_up_parallel_port_dev

*parallel_port)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device.

Description: Set the direction of one bits of the parallel port to be outputs.

4.2.8 alt up parallel port set bit to input

Prototype: void alt_up_parallel_port_set_bit_to_input(alt_up_parallel_port_dev

*parallel_port, unsigned int bit)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device.

bit – The bit of the parallel port to be set as an input.

Description: Set the direction of one bit of the parallel port to be input.

4.2.9 alt up parallel port set bit to output

Prototype: void alt_up_parallel_port_set_bit_to_output(alt_up_parallel_port_dev

*parallel_port, unsigned int bit)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device.

bit – The bit of the parallel port to be set as an output.

Description: Set the direction of one bit of the parallel port to be output.

4.2.10 alt up parallel port read interrupt mask

Prototype: unsigned int alt_up_parallel_port_read_interrupt_mask(alt_up_parallel_port

*parallel_port)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device.

Returns: data – The current interrupt mask of the parallel port.

Description: Read from the interrupt mask register of the parallel port.

4 Altera Corporation - University Program

March 2009

PARALLEL P ORT FOR A LTERA DE B OARDS For Quartus II 8

4.2.11 alt up parallel port set interrupt mask

Prototype: void alt_up_parallel_port_set_interrupt_mask(alt_up_parallel_port_dev

*parallel_port, unsigned mask)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device.

mask – The interrupt mask to be set in the parallel port.

Description: Set the interrupt mask register of the parallel port.

4.2.12 alt up parallel port read edge capture

Prototype: unsigned int alt_up_parallel_port_read_edge_capture(alt_up_parallel_port_d

*parallel_port)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device.

Returns: data – The current edge capture register of the parallel port.

Description: Read from the edge capture register of the parallel port.

4.2.13 alt up parallel port clear edge capture

Prototype: void alt_up_parallel_port_clear_edge_capture(alt_up_parallel_port_dev

*parallel_port)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device.

Description: Clear the edge capture register of the parallel port.

4.2.14 alt up parallel port read interrupt pending

Prototype: unsigned int alt_up_parallel_port_read_interrupt_pending(alt_up_parallel_p

*parallel_port)

Include: <altera_up_avalon_parallel_port.h>

Parameters: parallel_port – struct for the parallel port device.

Returns: pending – The interrupt pending bit field of the parallel port.

Description: Read interrupt pending information of the parallel port.

Altera Corporation - University Program 5

March 2009

You might also like

- IEEE-754 Floating Point Multipler in VerilogDocument8 pagesIEEE-754 Floating Point Multipler in VerilogShyam Shankar55% (11)

- Serial Port Complete: COM Ports, USB Virtual COM Ports, and Ports for Embedded SystemsFrom EverandSerial Port Complete: COM Ports, USB Virtual COM Ports, and Ports for Embedded SystemsRating: 3.5 out of 5 stars3.5/5 (9)

- Computer Organization and Design: The Hardware / Software InterfaceFrom EverandComputer Organization and Design: The Hardware / Software InterfaceRating: 4 out of 5 stars4/5 (12)

- AT&T R225 User's Manual PDFDocument18 pagesAT&T R225 User's Manual PDFedgarNo ratings yet

- Parallel Port For Intel DE-Series BoardsDocument8 pagesParallel Port For Intel DE-Series BoardsQuốc BảoNo ratings yet

- CS401 - Short Notes Chapter 14 PDFDocument3 pagesCS401 - Short Notes Chapter 14 PDFmalikNo ratings yet

- 04 I - o Ports On Pic16f877Document14 pages04 I - o Ports On Pic16f877Allen AlaskaNo ratings yet

- VHDL Stands For VHSIC Hardware Description LanguageDocument15 pagesVHDL Stands For VHSIC Hardware Description LanguageNoti GalNo ratings yet

- Section 10. I - O PortsDocument24 pagesSection 10. I - O PortsVlad MizeffNo ratings yet

- Finroc 2Document4 pagesFinroc 2revange2112No ratings yet

- Atmega128 I/O Ports: VersusDocument16 pagesAtmega128 I/O Ports: VersusZoranNo ratings yet

- Input Output PortsDocument43 pagesInput Output PortsFederico AldoNo ratings yet

- Parallel Port InterfacingDocument10 pagesParallel Port InterfacingLouieBenAbayaNo ratings yet

- Interfacing The Standard Parallel PortDocument17 pagesInterfacing The Standard Parallel Portshawnleegabriel100% (4)

- DACI Programmer's Reference ManualDocument7 pagesDACI Programmer's Reference ManualRaul Gil BayardoNo ratings yet

- Vitalab Flexor-XL HostDocument26 pagesVitalab Flexor-XL HostEugen SerovNo ratings yet

- Threadbare Parallel Port DAQ CardDocument16 pagesThreadbare Parallel Port DAQ CardPhạm Ngọc HòaNo ratings yet

- Embed Lab4Document6 pagesEmbed Lab4cointoinNo ratings yet

- Port Programming Assembly 8086Document15 pagesPort Programming Assembly 8086avmapNo ratings yet

- Lab ManualDocument82 pagesLab ManualxyzzyzNo ratings yet

- IN and OUT instructions in the 8086 microprocessor: input and output operationsDocument10 pagesIN and OUT instructions in the 8086 microprocessor: input and output operationsdtselvanNo ratings yet

- AT89C51CC01Document167 pagesAT89C51CC01don krtekNo ratings yet

- Ees06 MSP430 GpioDocument20 pagesEes06 MSP430 GpioasdsdNo ratings yet

- Implementation of Uart and Ethernet Using FpgaDocument15 pagesImplementation of Uart and Ethernet Using FpgaBANDARU SRI RAM SAI GANESH BANDARU SRI RAM SAI GANESHNo ratings yet

- Volatile Objects: Programming PointersDocument3 pagesVolatile Objects: Programming PointersnamosNo ratings yet

- Network Chapter4Document5 pagesNetwork Chapter4Yara Sherif100% (1)

- Mcu - Pic24fv32ka304 - Microchip - Section 12. Io Ports With Pps - 39711bDocument24 pagesMcu - Pic24fv32ka304 - Microchip - Section 12. Io Ports With Pps - 39711bLudwig SchmidtNo ratings yet

- How To Communicate With Parallel PortDocument24 pagesHow To Communicate With Parallel Portahmed4665100% (6)

- Mp&i Course File - unit-IVDocument25 pagesMp&i Course File - unit-IVvenkateshrachaNo ratings yet

- Passing A Port Pin As An Argument To A Function - MPLAB XC8Document1 pagePassing A Port Pin As An Argument To A Function - MPLAB XC8frank_grimesNo ratings yet

- DEMC Programmer's Reference ManualDocument18 pagesDEMC Programmer's Reference ManualRaul Gil BayardoNo ratings yet

- Serial Integration GuideDocument28 pagesSerial Integration GuideFelipe LozanoNo ratings yet

- Parallel Data TransfersDocument5 pagesParallel Data TransfersWanjira KigokoNo ratings yet

- 2021 Qna EsDocument10 pages2021 Qna Estemp.prathampalNo ratings yet

- Introduction To 8051 ProgrammingDocument24 pagesIntroduction To 8051 Programmingveeramaniks408No ratings yet

- Vls I Lab Manual 2021Document58 pagesVls I Lab Manual 2021shilpakesavNo ratings yet

- Advanced Electronic Design Automation: VHDL Quick Reference GuideDocument47 pagesAdvanced Electronic Design Automation: VHDL Quick Reference GuidegokulchandruNo ratings yet

- Spark V Exp 2Document7 pagesSpark V Exp 2yogeshNo ratings yet

- Pertemuan 7 Organisasi Input / OutputDocument29 pagesPertemuan 7 Organisasi Input / OutputYason Timothy HamdaniNo ratings yet

- Embedded Systems EE 354 ES Lab 02Document12 pagesEmbedded Systems EE 354 ES Lab 02AimanNo ratings yet

- Full Clear Download (No Error Formatting) At:: 5th-Edition-Petruzella-Solutions-ManualDocument1 pageFull Clear Download (No Error Formatting) At:: 5th-Edition-Petruzella-Solutions-ManualSamuelNo ratings yet

- 1-Microcontroller Based System Design - CompleteDocument55 pages1-Microcontroller Based System Design - CompleteWasif Bin ArifNo ratings yet

- EDC-M540-Microprocessor TrainerDocument79 pagesEDC-M540-Microprocessor TraineramrehmaniNo ratings yet

- Kartikmohta Com Tech ParallelportDocument9 pagesKartikmohta Com Tech ParallelportMike ThomsonNo ratings yet

- Micro Final TRMPPRDocument13 pagesMicro Final TRMPPRDeependra DabasNo ratings yet

- 8255 Microprocessor Programmable Peripheral Interface ChipDocument12 pages8255 Microprocessor Programmable Peripheral Interface ChipNaomi Aira Gole CruzNo ratings yet

- Microprocessor 2020Document5 pagesMicroprocessor 2020Sadikuzzaman lalinNo ratings yet

- Lecture On PC Parallel Port: Computer Engineering Junior LabDocument11 pagesLecture On PC Parallel Port: Computer Engineering Junior Labdeskaug1No ratings yet

- Vivado - HLS - To - Zynq - Design - Summary - JgarrigosDocument24 pagesVivado - HLS - To - Zynq - Design - Summary - JgarrigosALiftsNo ratings yet

- DEPP Programmer's Reference ManualDocument5 pagesDEPP Programmer's Reference ManualRaul Gil BayardoNo ratings yet

- 24fj PPSApNoteDocument26 pages24fj PPSApNoteLuis Di PintoNo ratings yet

- Programmable Peripheral Interface 8255: Specworld - inDocument27 pagesProgrammable Peripheral Interface 8255: Specworld - inSachinAggarwalNo ratings yet

- Input and Output For Microprocessors: State University Ofnew York, Buffalo, New York 14226Document5 pagesInput and Output For Microprocessors: State University Ofnew York, Buffalo, New York 14226ٍْبـٌـًُغـٰٓـدادِ كَــشِْــَخةَٓNo ratings yet

- Embedded Systems & Micro-Controllers - 01-09-2022Document32 pagesEmbedded Systems & Micro-Controllers - 01-09-2022anirudhNo ratings yet

- Parallel Port Programming (PART 1) With CDocument13 pagesParallel Port Programming (PART 1) With ChertzoliNo ratings yet

- Interfacing With PeripheralsDocument21 pagesInterfacing With PeripheralsSUDIPTA CHATTERJEENo ratings yet

- Avr NotesDocument20 pagesAvr Noteschandrakant chaudhariNo ratings yet

- GATE LEVEL MODELLING, MUX AND ADDERSDocument11 pagesGATE LEVEL MODELLING, MUX AND ADDERSMuhammad Usman RafiqNo ratings yet

- Embedded Controller Forth For The 8051 FamilyFrom EverandEmbedded Controller Forth For The 8051 FamilyRating: 4 out of 5 stars4/5 (1)

- FPGA Card Recognition SystemDocument15 pagesFPGA Card Recognition SystemQuốc BảoNo ratings yet

- Bui Quoc Bao: ObjectiveDocument3 pagesBui Quoc Bao: ObjectiveQuốc BảoNo ratings yet

- Floating Point NumbersDocument29 pagesFloating Point NumbersQuốc BảoNo ratings yet

- Logical Effort Analysis of CMOS VLSI DecoderDocument37 pagesLogical Effort Analysis of CMOS VLSI DecoderQuốc BảoNo ratings yet

- Downloaded From Manuals Search EngineDocument116 pagesDownloaded From Manuals Search EngineQuốc BảoNo ratings yet

- Calibration CameraDocument16 pagesCalibration CameraDuy Nguyễn Văn NhậtNo ratings yet

- 2016 ch2-MOS TransistorsDocument47 pages2016 ch2-MOS TransistorsQuốc BảoNo ratings yet

- Dalyk Project Final ReportDocument199 pagesDalyk Project Final ReportCésar MotaNo ratings yet

- Quine-McCluskey Tabular MinimizationDocument17 pagesQuine-McCluskey Tabular MinimizationMohammedali_Kh_1552No ratings yet

- Dalyk Project Final ReportDocument199 pagesDalyk Project Final ReportCésar MotaNo ratings yet

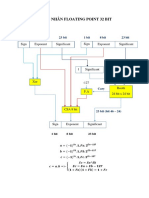

- B Nhân Floating Point 32 Bit: 1/ Data PathDocument2 pagesB Nhân Floating Point 32 Bit: 1/ Data PathQuốc BảoNo ratings yet

- 2016 ch2-MOS TransistorsDocument47 pages2016 ch2-MOS TransistorsQuốc BảoNo ratings yet

- L11 Datapath1Document49 pagesL11 Datapath1Nam LeNo ratings yet

- Le Quoc Bao: ObjectiveDocument2 pagesLe Quoc Bao: ObjectiveQuốc BảoNo ratings yet

- Bui Quoc Bao: ObjectiveDocument2 pagesBui Quoc Bao: ObjectiveQuốc BảoNo ratings yet

- DSP-FPGA Ch04-Retiming HK192Document84 pagesDSP-FPGA Ch04-Retiming HK192Quốc BảoNo ratings yet

- A3 Verilog PDFDocument17 pagesA3 Verilog PDFQuốc BảoNo ratings yet

- DSP-FPGA Ch04-Retiming HK192Document84 pagesDSP-FPGA Ch04-Retiming HK192Quốc BảoNo ratings yet

- FPGA Card Recognition SystemDocument15 pagesFPGA Card Recognition SystemQuốc BảoNo ratings yet

- Ieee PDFDocument65 pagesIeee PDFNam LeNo ratings yet

- Implementation of 24 Bit High Speed Floating Point Vedic MultiplierDocument5 pagesImplementation of 24 Bit High Speed Floating Point Vedic MultiplierNam LeNo ratings yet

- Implementation of 24 Bit High Speed Floating Point Vedic MultiplierDocument5 pagesImplementation of 24 Bit High Speed Floating Point Vedic MultiplierNam LeNo ratings yet

- Floating Point NumbersDocument29 pagesFloating Point NumbersQuốc BảoNo ratings yet

- RF Power Amplifiers: Dept. of Telecomm. Eng. Faculty of EEE CSD2020 DHT, HcmutDocument13 pagesRF Power Amplifiers: Dept. of Telecomm. Eng. Faculty of EEE CSD2020 DHT, HcmutQuốc BảoNo ratings yet

- 20 Step7 Basic v10.5 Quick Start en v11Document36 pages20 Step7 Basic v10.5 Quick Start en v11QuangThắngNo ratings yet

- Mini ProjectDocument12 pagesMini ProjectTamizh KdzNo ratings yet

- DTMF AsmDocument38 pagesDTMF AsmvancheNo ratings yet

- DLink Product GuideDocument44 pagesDLink Product GuideSANJEEVNo ratings yet

- SOP-04-Proses Penanganan Malicious CodeDocument2 pagesSOP-04-Proses Penanganan Malicious CodeNoval Saputra AjjahNo ratings yet

- A Practical File of Data Structure Lab BCA-206: Session: 2020-21Document34 pagesA Practical File of Data Structure Lab BCA-206: Session: 2020-21Gaurav MehndirattaNo ratings yet

- Financial Modelling - 3Document13 pagesFinancial Modelling - 3Hemo BoghosianNo ratings yet

- Higher Education Placement SystemDocument67 pagesHigher Education Placement Systembalaay bayyanaaNo ratings yet

- IT project management tool ProofHub presentationDocument17 pagesIT project management tool ProofHub presentationSheikh IzharNo ratings yet

- Itt Question BankDocument7 pagesItt Question BankPalak JaggiNo ratings yet

- Architectures For Implementing Hil SystemDocument5 pagesArchitectures For Implementing Hil Systemsinq57No ratings yet

- Product Data Sheet 6ES7214-1AD23-0XB0Document6 pagesProduct Data Sheet 6ES7214-1AD23-0XB0MancamiaicuruNo ratings yet

- How-TO Add Custom SIP Account in Nimbuzz (Tutorial) - TruVoIPBuzz PDFDocument9 pagesHow-TO Add Custom SIP Account in Nimbuzz (Tutorial) - TruVoIPBuzz PDFmuthuswamy77No ratings yet

- Linux Essentials Chapter 05 Exam Answers 2019 + PDFDocument4 pagesLinux Essentials Chapter 05 Exam Answers 2019 + PDFalexduquef100No ratings yet

- ESET Smart Security 9Document6 pagesESET Smart Security 9Paula OrtizNo ratings yet

- Automating HPLC and GC-Method - ValidationDocument6 pagesAutomating HPLC and GC-Method - ValidationqncargbNo ratings yet

- ReadmeDocument4 pagesReadmeLinh MtaNo ratings yet

- Igcse Ict Year11 Week3day3Document29 pagesIgcse Ict Year11 Week3day3Warnnie Musah0% (1)

- ROADM EvolutionDocument3 pagesROADM EvolutionVijay KumarNo ratings yet

- Electrical DrivesDocument113 pagesElectrical DrivesMuhammad Danyal ZahidNo ratings yet

- APCS Calculator Time QuestionsDocument5 pagesAPCS Calculator Time Questionsversa005No ratings yet

- Optus Loop Downloading OptusLoop VoiceUC For Desktop QRG PDFDocument6 pagesOptus Loop Downloading OptusLoop VoiceUC For Desktop QRG PDFmartaNo ratings yet

- Single Multi Core Comparision Report FinalDocument102 pagesSingle Multi Core Comparision Report FinalvaishnaviNo ratings yet

- Python Data TypesDocument9 pagesPython Data TypeskkkNo ratings yet

- MotoHawk Resource Guide 36333-1Document70 pagesMotoHawk Resource Guide 36333-1Franco LimaNo ratings yet

- ECE 300 Microprocessor Project Using The Texas Instruments MSP 430F449PZ ControllerDocument40 pagesECE 300 Microprocessor Project Using The Texas Instruments MSP 430F449PZ ControllerSadik PimpalkarNo ratings yet

- ISES CP Platform Survey Data Sheet 2018 FINALDocument3 pagesISES CP Platform Survey Data Sheet 2018 FINALRodolfo Cruz LaraNo ratings yet

- BA - Interview Questions 1Document6 pagesBA - Interview Questions 1Subhasis KarNo ratings yet

- Street Light Automation Using IoTDocument43 pagesStreet Light Automation Using IoTAshwin100% (1)