Professional Documents

Culture Documents

A3 Verilog PDF

Uploaded by

Quốc Bảo0 ratings0% found this document useful (0 votes)

35 views17 pages1) Behavioral Verilog is a way to describe synchronous circuits using behavioral modeling. It shows examples of basic synchronous components like registers, counters, and shift registers.

2) The examples demonstrate how to model sequential logic functions by assigning the next state values in an always block that is triggered on a clock edge.

3) Behavioral Verilog allows modeling the logical function of a circuit without specifying exact hardware implementation or timing details.

Original Description:

Original Title

A3 VERILOG.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Document1) Behavioral Verilog is a way to describe synchronous circuits using behavioral modeling. It shows examples of basic synchronous components like registers, counters, and shift registers.

2) The examples demonstrate how to model sequential logic functions by assigning the next state values in an always block that is triggered on a clock edge.

3) Behavioral Verilog allows modeling the logical function of a circuit without specifying exact hardware implementation or timing details.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

35 views17 pagesA3 Verilog PDF

Uploaded by

Quốc Bảo1) Behavioral Verilog is a way to describe synchronous circuits using behavioral modeling. It shows examples of basic synchronous components like registers, counters, and shift registers.

2) The examples demonstrate how to model sequential logic functions by assigning the next state values in an always block that is triggered on a clock edge.

3) Behavioral Verilog allows modeling the logical function of a circuit without specifying exact hardware implementation or timing details.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 17

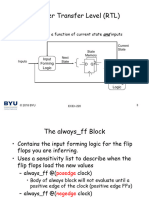

Behavioral Verilog

A Way to Describe

Synchronous Circuits

(It does much more than this –

but we won’t be covering that…)

ECEn 224 © 2003-2011

BYU

A 4-Bit Register

module reg(q, clk, d); !

parameter WID=4; !

input clk;!

input[WID-1:0] d;!

d 4

D Q q output reg[WID-1:0] q;!

4

!

always @(posedge clk)!

q <= d;!

clk endmodule !

ECEn 224 A3 Verilog © 2003-2011

Page 2 BYU

A Loadable Register

module behavLoadableReg (myreg, clk,

load, din); !

0

parameter WID=4; !

D Q input clk, load;!

myreg input din;!

din 1

output reg myreg;!

!

load always @(posedge clk)!

clk if (load)!

myreg <= din; !

endmodule `!

ECEn 224 A3 Verilog © 2003-2011

Page 3 BYU

A Counter

module upCnt (cnt, clk, clr); !

parameter WID=4; !

0

+1 input clk, clr;!

D Q 4

cnt output reg[WID-1:0] cnt;!

4

0000 1

!

always @(posedge clk)!

clr if (clr)!

clk cnt <= 0;!

else!

cnt <= q + 1;!

endmodule !

ECEn 224 A3 Verilog © 2003-2011

Page 4 BYU

Current/Next State Values

module upCnt (cnt, clk, clr); !

parameter WID=4; !

0

+1 input clk, clr;!

D Q 4

cnt output reg[WID-1:0] cnt;!

4

0000 1

!

always @(posedge clk)!

clr if (clr)!

clk cnt <= 0;!

else!

cnt <= cnt + 1;!

endmodule !

ECEn 224 A3 Verilog © 2003-2011

Page 5 BYU

Another Counter

module upCnt (cnt, clk, clr, inc); !

cnt parameter WID=4; !

4

cnt+1 input clk, clr, inc;!

4 D Q cnt output reg[WID-1:0] cnt;!

0 4 4

!

4

cnt 4 always @(posedge clk)!

2 if (clr && !inc)!

clk cnt <= 0;!

clr inc else if (!clr && inc)!

cnt <= cnt + 1;!

endmodule !

ECEn 224 A3 Verilog © 2003-2011

Page 6 BYU

Yet Another Counter

module upCnt (q, clk, clr, inc); !

0 parameter WID=4; !

0

+1 input clk, clr, inc;!

1

D Q 4

q output reg[WID-1:0] q;!

4

1

0000 !

always @(posedge clk)!

inc if (clr)!

clr clk q <= 0;!

else if (inc)!

q <= q + 1;!

endmodule !

ECEn 224 A3 Verilog © 2003-2011

Page 7 BYU

A Swapper

module swapper (clk, load, swap, !

a, b, out1, out2); !

0

0 input clk, load, swap;!

1

D Q input a, b;!

a out1 output reg out1, out2;!

1

!

swap

always @(posedge clk)!

load clk if (load)!

begin!

out1 <= a;!

out2 <= b;!

end!

0

0 else if (swap)!

1

D Q begin!

b out2 out1 <= out2;!

1

out2 <= out1;!

end!

swap

load clk endmodule !

ECEn 224 A3 Verilog © 2003-2011

Page 8 BYU

A Swapper

module swapper (clk, load, swap, !

a, b, out1, out2); !

0

0 input clk, load, swap;!

1

D Q input a, b;!

a out1 output reg out1, out2;!

1

!

swap

always @(posedge clk)!

load clk if (load)!

begin!

out1 <= a;!

out2 <= b;!

end!

0

0 else if (swap)!

1

D Q begin!

b out2 out1 <= out2;!

1

out2 <= out1;!

end!

swap

load clk endmodule !

ECEn 224 A3 Verilog © 2003-2011

Page 9 BYU

Multiple Assignments to a Signal

• When you assign

twice…

module multiAssign (clk, clr, cnt);

– Last one takes effect input clk, clr;!

on the signal value

output reg[3:0] cnt;!

!

always @(posedge clk)!

begin!

cnt <= 4'b0000; !

if (!clr)!

0 cnt <= cnt+1; !

+1

D Q 4

cnt end!

4 endmodule !

0000 1

clr

clk

ECEn 224 A3 Verilog © 2003-2011

Page 10 BYU

A Shift Register

module delay4 (clk,

Q3 Q2 Q1 Q0 SerIn, Q); !

input clk, SerIn;!

output reg[3:0] Q;!

SerIn D Q D Q D Q D Q !

always @(posedge clk)!

Q <= {SerIn, Q[3:1]};!

endmodule!

CLK CLK CLK CLK

ECEn 224 A3 Verilog © 2003-2011

Page 11 BYU

Another Shift Register

module delay4 (clk, shift,

SerIn, Q); !

input clk, shift, SerIn;!

output reg Q;

a b

SerIn D Q D Q D Q Q reg a, b;!

!

always @(posedge clk)!

begin!

a <= SerIn;!

CLK CLK CLK b <= a;!

Q <= b;!

end!

endmodule!

ECEn 224 A3 Verilog © 2003-2011

Page 12 BYU

Yet Another Shift Register

module delay4 (clk, shift,

SerIn, Q); !

input clk, shift, SerIn;!

output reg Q;

a b

SerIn D Q D Q D Q Q reg a, b;!

!

always @(posedge clk)!

begin!

Q <= b;!

CLK CLK CLK b <= a;!

a <= SerIn;!

end!

endmodule!

Order of assignments DOES NOT MATTER…

ECEn 224 A3 Verilog © 2003-2011

Page 13 BYU

A Register File

module regFile (clk, regWE, Addr,

DataIn, DataOut);!

input clk, regWE;!

Reg0 input[2:0] Addr;!

n

Register write signals

Reg1 input[15:0] DataIn;!

n

Reg2 output[15:0] DataOut;!

n 8:1 MUX !

Write Reg3

n reg [15:0] registers [7:0]; !

Decoder Reg4 DataOut

n n=16 !

Reg5 // The synchronous write logic!

n

Reg6 always @(posedge clk)!

n

Reg7 if (regWE)!

n registers[Addr] <= DataIn;!

m=3 n=16 !

regWE DataIn clk // The asynchronous read logic!

Addr assign DataOut = registers[Addr];!

!

endmodule !

ECEn 224 A3 Verilog © 2003-2011

Page 14 BYU

An FSM

module fsm (clk, reset, Xin, Z);!

To be studied after you learn FSM design input clk, reset, Xin;!

output Z;!

reg[1:0] state;!

Xin !

parameter s0 = 2'b00; !

parameter s1 = 2'b01;!

parameter s2 = 2'b10; !

parameter s3 = 2'b11;!

reset !

S0 always @(posedge clk)!

begin!

Xin if (reset)!

state <= s0;!

else !

case (state)!

S3 Z S1 Xin

s0: if (!Xin) state <= s1;!

s1: if (Xin) state <= s2;!

s2: if (Xin) state <= s1;!

else state <= s3;!

endcase!

Xin

Xin end!

assign Z = state==s3 ? 1'b1 : 1'b0;!

S2 Xin !

endmodule !

ECEn 224 A3 Verilog © 2003-2011

Page 15 BYU

A Car Wash FSM

To be studied after you learn FSM design module carWash (clk, reset, token, tdone, clrt, spray); !

input clk, reset, token, tdone;!

output reg clrt, spray;!

token reg[1:0] state;!

!

parameter sIdle = 2'b00;!

parameter sToken = 2'b01; !

reset parameter sSpray = 2'b10; !

sIdle !

always @(posedge clk)!

token begin!

if (reset)!

state <= sIdle;!

else !

tdone sToken clrt case (state)!

sIdle: if (token) state <= sToken;!

sToken: state <= sSpray;!

sSpray: if (tdone) state <= sIdle;!

endcase!

end!

spray sSpray !

always @(state)!

begin!

clrt = 1'b0;!

spray = 1'b0;!

case (state)!

tdone sToken: clrt = 1'b1;!

sSpray: spray = 1'b1;!

endcase!

end !

endmodule !

A3 Verilog © 2003-2011

Page 16 BYU

Finishing Up

• You should always know what circuitry will

result from a piece of Verilog code

– Otherwise => recipe for disaster !!!!!

• Always check your synthesizer documentation

– Will tell you how to code for synthesis

– Will let you take advantage of technology-

specific features

ECEn 224 A3 Verilog © 2003-2011

Page 17 BYU

You might also like

- The Voice: and The Musical InstrumentsDocument12 pagesThe Voice: and The Musical InstrumentsnireadaetaNo ratings yet

- Verilog Modules For Common Digital FunctionsDocument30 pagesVerilog Modules For Common Digital Functionselle868No ratings yet

- Following Is The Verilog Code For FlipDocument26 pagesFollowing Is The Verilog Code For FlipDivya MuraliNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Manual de TallerDocument252 pagesManual de TallerEdison RodriguezNo ratings yet

- Impact of Computer On SocietyDocument4 pagesImpact of Computer On SocietyraheelNo ratings yet

- Asme Y14.41 2003Document105 pagesAsme Y14.41 2003Emanuel Ovejita Arrese100% (3)

- PBL BrochureNov04Document26 pagesPBL BrochureNov04Pedro Antonio Lea Plaza Rico100% (1)

- ch46Document15 pagesch46jose perezNo ratings yet

- Exercices VHDLDocument83 pagesExercices VHDLFadi Akoury50% (2)

- VHDL Code For 4-Bit Shift RegisterDocument3 pagesVHDL Code For 4-Bit Shift Registeramollandge0450% (2)

- Static Timing Analysis - MaharshiDocument29 pagesStatic Timing Analysis - MaharshiSatish Yada100% (1)

- The PIC Microcontroller: Your Personal Introductory CourseFrom EverandThe PIC Microcontroller: Your Personal Introductory CourseRating: 1 out of 5 stars1/5 (2)

- Is Standard ListDocument11 pagesIs Standard ListSunil PulikkalNo ratings yet

- Kumar Saurabh Resume (SAP IBP)Document6 pagesKumar Saurabh Resume (SAP IBP)SaurabhSinhaNo ratings yet

- Experiment 10 P, D, I, Pi, PD and Pid Control of A Rotational SystemDocument3 pagesExperiment 10 P, D, I, Pi, PD and Pid Control of A Rotational SystemBhimsen ShresthaNo ratings yet

- Registers SVDocument28 pagesRegisters SVkrishnaavNo ratings yet

- Tutorial 03 Latch FF State Machines 1Document81 pagesTutorial 03 Latch FF State Machines 1Andreea ChiriluşNo ratings yet

- Chapter - 05 - Sequential CircuitsDocument43 pagesChapter - 05 - Sequential CircuitsThanh Diện NguyễnNo ratings yet

- Assignment 1 - ReriewDocument5 pagesAssignment 1 - ReriewAnh NamNo ratings yet

- Lecture SlideDocument25 pagesLecture SlideBilal MumtazNo ratings yet

- ASIC Va VHDL Toan TapDocument76 pagesASIC Va VHDL Toan TapCường VũNo ratings yet

- FALLSEM2022-23 BECE102L TH VL2022230102875 Reference Material I 17-09-2022 Shift Registers CountersDocument28 pagesFALLSEM2022-23 BECE102L TH VL2022230102875 Reference Material I 17-09-2022 Shift Registers CountersAakashNo ratings yet

- ET5080E Digital Design Using Verilog HDL: Fall 21Document35 pagesET5080E Digital Design Using Verilog HDL: Fall 21ifireNo ratings yet

- VHDL Code For 4-Bit Updown CounterDocument4 pagesVHDL Code For 4-Bit Updown CounterVinod ParabNo ratings yet

- Chapter 05 Sequential CircuitsDocument27 pagesChapter 05 Sequential CircuitsNguyen Yen NhiNo ratings yet

- VHDL PgmsDocument2 pagesVHDL Pgmsprabha_velNo ratings yet

- Assignment-10: DFF CodeDocument8 pagesAssignment-10: DFF CodeNarendra Babu GunnamNo ratings yet

- Cb2re TBDocument2 pagesCb2re TBOrrette BakerNo ratings yet

- Student NameDocument9 pagesStudent NameNhất Duy NguyễnNo ratings yet

- Board WorkDocument51 pagesBoard WorkRama krishna LankaNo ratings yet

- Verilog Code FAQDocument25 pagesVerilog Code FAQRAGUL RAJ SNo ratings yet

- Cycle 3 Part BDocument10 pagesCycle 3 Part BNithyashree MNo ratings yet

- Verilog Coding ExamplesDocument41 pagesVerilog Coding ExamplesKarishma PotnuruNo ratings yet

- VHDL Code For Updown CNTDocument3 pagesVHDL Code For Updown CNTmeaow88100% (2)

- VHDL Codes For Thermometer Projects Using Leds & LCD DisplayDocument26 pagesVHDL Codes For Thermometer Projects Using Leds & LCD DisplayIbrahim ShanonoNo ratings yet

- Aplicaciones Spartan6 Ver1Document42 pagesAplicaciones Spartan6 Ver1juan mezaNo ratings yet

- VHDL Code For D FF Using Behavior ModelDocument20 pagesVHDL Code For D FF Using Behavior ModelAdithya ChakilamNo ratings yet

- EE434 ASIC & Digital Systems: Partha Pande School of EECS Washington State University Pande@eecs - Wsu.eduDocument29 pagesEE434 ASIC & Digital Systems: Partha Pande School of EECS Washington State University Pande@eecs - Wsu.edumimranptclNo ratings yet

- DSD PPT Usr and CN and Odd DividerDocument22 pagesDSD PPT Usr and CN and Odd Dividerece19637ec003No ratings yet

- Verilog Sequential ModelingDocument8 pagesVerilog Sequential ModelingR INI BHANDARINo ratings yet

- ADC Using SAR Via DAC With PWMDocument35 pagesADC Using SAR Via DAC With PWMMuhammad MoinNo ratings yet

- VHDL - Xilinx Exercises CompilationDocument19 pagesVHDL - Xilinx Exercises CompilationNicko CasiNo ratings yet

- Guc 429 52 5735 2021-03-05T19 31 56Document6 pagesGuc 429 52 5735 2021-03-05T19 31 56Menna NNo ratings yet

- Dsd-Lecture ConvencoderDocument11 pagesDsd-Lecture Convencodernabeel hasanNo ratings yet

- VHDL SequentialDocument5 pagesVHDL SequentialSAKETSHOURAVNo ratings yet

- Example VHDL Entity - 0 To 9 Counter: VHDL Model VHDL Test BenchDocument1 pageExample VHDL Entity - 0 To 9 Counter: VHDL Model VHDL Test BenchsumtingwongdumgaiNo ratings yet

- Chapter - 05 - Sequential CircuitsDocument46 pagesChapter - 05 - Sequential Circuitskidgod2111No ratings yet

- Lab 7: VHDL 16-Bit ShifterDocument6 pagesLab 7: VHDL 16-Bit ShifterAvinash VikramNo ratings yet

- Dic File - 7 SemDocument22 pagesDic File - 7 SemShalini SharmaNo ratings yet

- Intro To Lab Hex CounterDocument12 pagesIntro To Lab Hex CounterYX GohNo ratings yet

- Verilog: Logic VerificationDocument9 pagesVerilog: Logic VerificationTalha AhsanNo ratings yet

- Verilog CodesDocument26 pagesVerilog CodesmdlogicsolutionsNo ratings yet

- Design Example 5.5Document10 pagesDesign Example 5.5MaheshNo ratings yet

- Proyecto Código PrincipalDocument18 pagesProyecto Código PrincipalFrancisco Javier ReyesNo ratings yet

- Proiect - Structuri FPGADocument10 pagesProiect - Structuri FPGACrocoduluNo ratings yet

- Verilog Modules For Common Digital FunctionsDocument30 pagesVerilog Modules For Common Digital Functionssudarshan poojaryNo ratings yet

- Registers and Counters: in This Topic We Will Be Covering - Registers - CountersDocument7 pagesRegisters and Counters: in This Topic We Will Be Covering - Registers - CountersZoolJcNo ratings yet

- DAC ProgramsDocument4 pagesDAC Programssudhanva p kashyapNo ratings yet

- Unit 3Document34 pagesUnit 3Amitav DasNo ratings yet

- Digital Design With HDLDocument29 pagesDigital Design With HDLw.nNo ratings yet

- Fpga ApplicationsDocument6 pagesFpga ApplicationsBHEEMANPALLY SRIMANNARAYANA R2527004No ratings yet

- Test Bench For 8 Bit CounterDocument2 pagesTest Bench For 8 Bit CounterAnuradha KhalkhoNo ratings yet

- N-Bit Shift Register PDFDocument232 pagesN-Bit Shift Register PDFAnuradha KhalkhoNo ratings yet

- Tugas8 - 2210191006 - Filosofi Dwibakti - LapsemDocument23 pagesTugas8 - 2210191006 - Filosofi Dwibakti - LapsemFD SyndromeNo ratings yet

- VHDL Code For Parallel in Parallel Out Shift RegisterDocument4 pagesVHDL Code For Parallel in Parallel Out Shift RegisterPRITY KUMARI 20BEC0773No ratings yet

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- Parallel Port For Intel DE-Series BoardsDocument8 pagesParallel Port For Intel DE-Series BoardsQuốc BảoNo ratings yet

- Lect6 LogicaleffortDocument37 pagesLect6 LogicaleffortQuốc BảoNo ratings yet

- Downloaded From Manuals Search EngineDocument116 pagesDownloaded From Manuals Search EngineQuốc BảoNo ratings yet

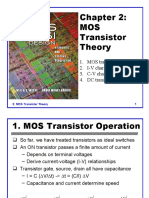

- 2016 ch2-MOS TransistorsDocument47 pages2016 ch2-MOS TransistorsQuốc BảoNo ratings yet

- Parallel PortDocument5 pagesParallel PortQuốc BảoNo ratings yet

- Bui Quoc Bao: ObjectiveDocument2 pagesBui Quoc Bao: ObjectiveQuốc BảoNo ratings yet

- B Nhân Floating Point 32 Bit: 1/ Data PathDocument2 pagesB Nhân Floating Point 32 Bit: 1/ Data PathQuốc BảoNo ratings yet

- RF Power Amplifiers: Dept. of Telecomm. Eng. Faculty of EEE CSD2020 DHT, HcmutDocument13 pagesRF Power Amplifiers: Dept. of Telecomm. Eng. Faculty of EEE CSD2020 DHT, HcmutQuốc BảoNo ratings yet

- FPGA ProjectDocument15 pagesFPGA ProjectQuốc BảoNo ratings yet

- DSP-FPGA Ch04-Retiming HK192Document84 pagesDSP-FPGA Ch04-Retiming HK192Quốc BảoNo ratings yet

- RVR FM Product ListDocument37 pagesRVR FM Product Listaspwq0% (1)

- A318/A319/A320/A321: Service BulletinDocument22 pagesA318/A319/A320/A321: Service BulletinPradeep K sNo ratings yet

- Solid Desiccant DehydrationDocument5 pagesSolid Desiccant Dehydrationca_minoNo ratings yet

- Seminarski RadDocument32 pagesSeminarski RadAdmir KlinčevićNo ratings yet

- Bhavin Desai ResumeDocument5 pagesBhavin Desai Resumegabbu_No ratings yet

- Colebrook EquationDocument3 pagesColebrook EquationMuhammad Ghufran KhanNo ratings yet

- Sell Sheet Full - Size-FinalDocument2 pagesSell Sheet Full - Size-FinalTito BustamanteNo ratings yet

- 2006 AcrotechDocument32 pages2006 Acrotechkaniappan sakthivelNo ratings yet

- Plastiment BV 40: Water-Reducing Plasticiser For High Mechanical StrengthDocument3 pagesPlastiment BV 40: Water-Reducing Plasticiser For High Mechanical StrengthacarisimovicNo ratings yet

- 2SK2188Document2 pages2SK2188Abigail HoobsNo ratings yet

- Dana Trailer Suspension: SpicerDocument14 pagesDana Trailer Suspension: SpicerCarlos Manuel Vazquez SanchezNo ratings yet

- ACCY225 Tri 1 2017 Tutorial 3 Business Processes-2Document3 pagesACCY225 Tri 1 2017 Tutorial 3 Business Processes-2henryNo ratings yet

- TX-SMS Remote Programming GuideDocument2 pagesTX-SMS Remote Programming GuidedjbobyNo ratings yet

- Trumpf TruSystem 7500 Service ManualDocument424 pagesTrumpf TruSystem 7500 Service ManualVitor FilipeNo ratings yet

- PDFDocument7 pagesPDFJose JohnNo ratings yet

- About Language UniversalsDocument8 pagesAbout Language UniversalsImran MaqsoodNo ratings yet

- The 'X' Chronicles Newspaper - August 2010Document50 pagesThe 'X' Chronicles Newspaper - August 2010Rob McConnell100% (1)

- Kuhlmann DigiTherm Digital Controller Manual ENDocument12 pagesKuhlmann DigiTherm Digital Controller Manual ENLuis SantosNo ratings yet

- Control Cable SpecificationDocument8 pagesControl Cable Specificationloli2323No ratings yet

- BSNL CRM FTTH User Manual - Release1.0 - ShiftDocument25 pagesBSNL CRM FTTH User Manual - Release1.0 - ShiftJTONIB AIZAWLNo ratings yet

- Ds Lm5006 en Co 79839 Float Level SwitchDocument7 pagesDs Lm5006 en Co 79839 Float Level SwitchRiski AdiNo ratings yet

- 26-789 Eng Manual Pcd3Document133 pages26-789 Eng Manual Pcd3Antun KoricNo ratings yet