Professional Documents

Culture Documents

Registers SV

Uploaded by

krishnaavCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Registers SV

Uploaded by

krishnaavCopyright:

Available Formats

Register Transfer Level (RTL)

• Outputs are a function of current state and inputs

Current

State

State

Memory

Input Next

Inputs State D Q

Forming D Q

Logic

Output Outputs

Forming

Logic

© 2018 BYU ECEn 220 3

The always_ff Block

• Contains the input forming logic for the flip

flops you are inferring.

• Uses a sensitivity list to describe when the

flip flops load the new values

– always_ff @(posedge clock)

• Body of always block will not evaluate until a

positive edge of the clock (positive edge FFs)

– always_ff @(negedge clock)

• Negative edge triggered flip-flops

© 2018 BYU ECEn 220 4

Assignment Statements

• Use non-blocking assignment statements (<=)

• Flip-Flops will be inferred for all signals that

are assigned within always_ff blocks

• Can use “if” and “case” statements

– Do not need to cover all cases (memory

element will hold previous value)

© 2018 BYU ECEn 220 5

1-Bit Flip-Flop

module ff(

input wire logic clk, d,

D Q

output logic q

d q

);

clk always_ff @(posedge clk)

q <= d;

endmodule

© 2018 BYU ECEn 220 6

Loadable 1-Bit Flip-Flop

module ff(

input wire logic clk, load, d,

output logic q

0 );

D Q q

d 1

always_ff @(posedge clk)

if (load)

load

clk q <= d;

endmodule

if load is ‘1’, load d to q

else nothing happens

© 2018 BYU ECEn 220 7

Flip-Flops and Logic

always_ff @(posedge clk)

begin

a<=b;

a <= b&c;

end

C D

B

B

Q A

clk CLK

© 2018 BYU ECEn 220 8

D Flip-Flop with Asynchronous Reset

always_ff @(posedge clk

or negedge rst)

rst

begin

if (!rst) A <= 0; clr

else A <= B; B D

end

Q A

To make the reset synchronous, just

remove negedge rst from the

sensitivity list. clk CLK

© 2018 BYU ECEn 220 9

D Flip-flop with Synchronous Reset and

Enable

always_ff @(posedge clk)

begin

if (rst) rst D

B

A <= 0;

else if (enable) enable EN Q A

A <= B;

clk CLK

end

© 2018 BYU ECEn 220 10

A Parameterized Loadable Register

module LoadableReg #(WID=4)(

input wire logic clk, load,

input logic[WID-1:0] din,

output logic[WID-1:0] myreg

0 );

D Q myreg

din 1

always_ff @(posedge clk)

if (load)

load myreg <= din;

clk

endmodule

© 2018 BYU ECEn 220 11

A Shift Register

logic[3:0] Q;

always_ff @(posedge clk)

begin Q[3] <= Q[2];

Q <= {Q[2:0],Q[3]} Q[2] <= Q[1];

Q[1] <= Q[0];

end Q[0] <= Q[3];

Without a reset or D Q D Q D Q D Q

load, this circuit can D Q D Q D Q D Q

never be initialized. CLK CLK CLK CLK

CLK CLK CLK CLK

clk

clk

© 2018 BYU ECEn 220 12

A Parameterized Counter

module upCnt #(WID=4)(

input wire logic clk,

output logic[WID-1:0] cnt

+1 4

D Q 4

cnt );

always_ff @(posedge clk)

cnt <= cnt + 1;

clk

endmodule

Without a clear or

load, this circuit can

never be initialized.

Must have a clr signal to reset it to 0.

Otherwise, cnt would be in X state on startup.

© 2018 BYU ECEn 220 13

A Counter with a Clear

module upCnt #(WID=4)(

input wire logic clk, clr,

0 output logic[WID-1:0] cnt

+1

4

D Q 4

cnt );

0000 1

always_ff @(posedge clk)

clr if (clr)

clk cnt <= 0;

else

cnt <= cnt + 1;

endmodule

Must have a clr signal to reset it to 0.

Otherwise, cnt would be in X state on startup.

© 2018 BYU ECEn 220 14

Current/Next State Values

module upCnt #(WID=4)(

input wire logic clk, clr,

0 output logic[WID-1:0] cnt

+1

4

D Q 4

cnt );

0000 1

always_ff @(posedge clk)

clr if (clr)

clk cnt <= 0;

else

cnt <= cnt + 1;

endmodule

© 2018 BYU ECEn 220 15

A Counter with Synchronous Reset and

Enable

parameter WID=8;

rst

logic[WID-1:0] count; clr

logic enable, reset; enable EN

always_ff @(posedge clk)

begin

if (reset)

count<=0;

count

else if (enable)

count<=count+1;

end

© 2018 BYU ECEn 220 16

Another Counter

module upCnt #(WID=4)(

cnt 00 input wire logic clk, clr, inc,

4

cnt+1 01

4 D Q cnt output logic[WID-1:0] cnt

0 10 4 4

4

11

);

cnt 4

2

always_ff @(posedge clk)

clr inc clk

if ( )

cnt <= 0;

else if ( )

A. !clr && !inc cnt <= cnt + 1;

B. !clr && inc endmodule

C. clr && !inc

D. clr && inc

© 2018 BYU ECEn 220 17

Another Counter

module upCnt #(WID=4)(

cnt 4 input wire logic clk, clr, inc,

cnt+1 output logic[WID-1:0] cnt

4 D Q cnt

0 4

4 4

);

cnt 4

2

always_ff @(posedge clk)

clr inc clk

if (clr && !inc)

cnt <= 0;

else if (!clr && inc)

cnt <= cnt + 1;

endmodule

© 2018 BYU ECEn 220 18

Yet Another Counter

module upCnt #(WID=4)(

input wire logic clk,

input wire logic clr, inc,

0

0 output logic[WID-1:0] q

+1

1 4

D Q 4

q );

1

0000

inc always_ff @(posedge clk)

clk if (?)

clr

q <= 0;

else if (?)

q <= q + 1;

A. !clr

endmodule

B. clr

C. !inc

D. inc

© 2018 BYU ECEn 220 19

Yet Another Counter

module upCnt #(WID=4)(

input wire logic clk,

input wire logic clr, inc,

0 output logic[WID-1:0] q

0

+1 );

1 4

D Q 4

q

1

0000 always_ff @(posedge clk)

inc if (clr)

clr clk q <= 0;

else if (inc)

q <= q + 1;

endmodule

© 2018 BYU ECEn 220 20

A Swapper

module swapper (

input wire logic clk, load, swap,

0

0 input wire logic a, b,

1

D Q output logic out1, out2

a out1 );

1

swap

always_ff @(posedge clk)

load clk if (?)

begin

out1 <= a; A. !load

out2 <= b;

0

end B. load

0

D Q

else if (?)

begin C. !swap

1

b 1

out2 out1 <= out2;

out2 <= out1;

D. swap

end

swap

load clk endmodule

© 2018 BYU ECEn 220 21

A Swapper

module swapper (

input wire logic clk, load, swap,

0

0 input wire logic a, b,

1

D Q output logic out1, out2

a out1 );

1

swap

always_ff @(posedge clk)

load clk if (load)

begin

out1 <= a;

out2 <= b;

end

0

0 else if (swap)

1

D Q begin

b out2 out1 <= out2;

1

out2 <= out1;

end

swap

load clk endmodule

© 2018 BYU ECEn 220 22

Multiple Assignments to a Signal

• When you assign

twice…

– Last one takes module multiAssign (

input wire logic clk, clr,

effect on the signal output logic[3:0] cnt

);

value

always_ff @(posedge clk)

begin

cnt <= 4'b0000;

0 if (!clr)

+1 cnt <= cnt+1;

4

D Q 4

cnt

end

0000 1

endmodule

clr

clk

© 2018 BYU ECEn 220 23

A Shift Register

module delay4 (

input wire logic clk, SerIn,

output logic[3:0] Q

Q[3] Q[2] Q[1] Q[0]

);

SerIn D Q D Q D Q D Q always_ff @(posedge clk)

Q <= ;

endmodule

CLK CLK CLK CLK

A.{SerIn, Q[2:0]}

B.{Q[3:1], SerIn}

C.{SerIn, Q[3:1]}

D.{Q[2:0], SerIn}

E.{Q[2:1], SerIn}

© 2018 BYU ECEn 220 24

A Shift Register

module delay4 (

input wire logic clk, SerIn,

output logic[3:0] Q

Q[3] Q[2] Q[1] Q[0] );

SerIn D Q D Q D Q D Q always_ff @(posedge clk)

Q <= {SerIn, Q[3:1]};

endmodule

CLK CLK CLK CLK

© 2018 BYU ECEn 220 25

Another Shift Register

module delay3 (

input wire logic clk,

input wire logic SerIn,

output logic Q

);

a b logic a, b;

SerIn D Q D Q D Q Q

always_ff @(posedge clk)

begin

CLK CLK CLK a <= SerIn;

b <= a;

Q <= b;

end

endmodule

© 2018 BYU ECEn 220 26

Yet Another Shift Register

module delay3 (

input wire logic clk,

input wire logic SerIn,

output logic Q

);

logic a, b;

a b

SerIn D Q D Q D Q Q

always_ff @(posedge clk)

begin

Q <= b;

CLK CLK CLK

b <= a;

a <= SerIn;

end

endmodule

Order of assignments DOES NOT MATTER…

© 2018 BYU ECEn 220 27

A Register File

module regFile (

Reg0 input wire logic clk, regWE,

n

input wire logic [2:0] Addr,

Reg1 n input wire logic [15:0] DataIn,

Register write signals

Reg2 output logic[15:0] DataOut

n

8:1 MUX

Write Reg3 );

n

Decoder DataOut

Reg4 n n=16

logic [15:0] registers [8];

Reg5

n

Reg6

n

// The synchronous write logic

Reg7

always_ff @(posedge clk)

n if (regWE)

m=3 n=16 registers[Addr] <= ;

regWE DataIn clk

// The asynchronous read logic

Addr

assign DataOut = ;

endmodule

© 2018 BYU ECEn 220 28

A Register File

module regFile (

input wire logic clk, regWE,

Reg0 input wire logic [2:0] Addr,

n

Reg1

n input wire logic [15:0] DataIn,

Register write signals

Reg2 output logic[15:0] DataOut

n

Reg3

8:1 MUX );

Write n

Decoder DataOut

Reg4 n=16

n logic [15:0] registers [8];

Reg5

n

Reg6

n

// The synchronous write logic

Reg7 always_ff @(posedge clk)

n

if (regWE)

m=3 n=16 registers[Addr] <= DataIn;

regWE DataIn clk

Addr // The asynchronous read logic

assign DataOut = registers[Addr];

endmodule

© 2018 BYU ECEn 220 29

module regFile (

input wire logic clk, regWE,

A Register File

input wire logic [2:0] Addr,

input wire logic [15:0] DataIn,

output logic[15:0] DataOut

);

logic[15:0] Reg0,Reg1,Reg2,Reg3,

Reg4,Reg5,Reg6,Reg7;

Reg0 // The synchronous write logic

n

Reg1 always_ff @(posedge clk)

n

Register write signals

if (regWE)

Reg2 case(Addr)

n

8:1 MUX

Reg3 3’b000: Reg0 <= DataIn;

Write n

Decoder DataOut 3’b001: Reg1 <= DataIn;

Reg4 n n=16 3’b010: Reg2 <= DataIn;

Reg5 3’b011: Reg3 <= DataIn;

n

3’b100: Reg4 <= DataIn;

Reg6

n 3’b101: Reg5 <= DataIn;

Reg7 3’b110: Reg6 <= DataIn;

n

default: Reg7 <= DataIn;

m=3 n=16 endcase

regWE DataIn clk

// The asynchronous read logic

Addr assign DataOut = (Addr==3’000)? Reg0:

(Addr==3’001)? Reg1:

…….

reg7;

endmodule

© 2018 BYU ECEn 220 30

You might also like

- A3 Verilog PDFDocument17 pagesA3 Verilog PDFQuốc BảoNo ratings yet

- Chapter 4 - HDL Modelling of Sequential Logic CircuitDocument26 pagesChapter 4 - HDL Modelling of Sequential Logic CircuitNG WEN CHI STUDENTNo ratings yet

- Tutorial 03 Latch FF State Machines 1Document81 pagesTutorial 03 Latch FF State Machines 1Andreea ChiriluşNo ratings yet

- Hardware Description Languages and Sequential Logic: Flip-FlopsDocument14 pagesHardware Description Languages and Sequential Logic: Flip-FlopsGREATJUSTGREATNo ratings yet

- 3rd Int Sequential Logic PDFDocument14 pages3rd Int Sequential Logic PDFUtsav ParasharNo ratings yet

- ArchL-Sequential Logic-03Document41 pagesArchL-Sequential Logic-03Ajax KrausNo ratings yet

- Lecture 7Document27 pagesLecture 7rahulNo ratings yet

- CSE369 Sp18 09 EndTopics InkDocument32 pagesCSE369 Sp18 09 EndTopics InkPokemonponponNo ratings yet

- Verilog Scheduling SemanticsDocument14 pagesVerilog Scheduling SemanticsJayesh PopatNo ratings yet

- COMSATS Institute of Information Technology: Lab#12: Convolutional EncodersDocument3 pagesCOMSATS Institute of Information Technology: Lab#12: Convolutional EncoderstalhaNo ratings yet

- Lab9Document10 pagesLab9Nrusingha Prasad PandaNo ratings yet

- Verilog: Logic VerificationDocument9 pagesVerilog: Logic VerificationTalha AhsanNo ratings yet

- Proiect - Structuri FPGADocument10 pagesProiect - Structuri FPGACrocoduluNo ratings yet

- VHDL SequentialDocument5 pagesVHDL SequentialSAKETSHOURAVNo ratings yet

- Digital Logic Lab: EE 2731 Spring 2011Document27 pagesDigital Logic Lab: EE 2731 Spring 2011lsu225No ratings yet

- Lecture SlideDocument25 pagesLecture SlideBilal MumtazNo ratings yet

- Chapter - 05 - Sequential CircuitsDocument43 pagesChapter - 05 - Sequential CircuitsThanh Diện NguyễnNo ratings yet

- ET5080E Digital Design Using Verilog HDL: Fall 21Document35 pagesET5080E Digital Design Using Verilog HDL: Fall 21ifireNo ratings yet

- L5: Simple Sequential Circuits and VerilogDocument25 pagesL5: Simple Sequential Circuits and VerilogKaleb FikreNo ratings yet

- Chapter 05 Sequential CircuitsDocument27 pagesChapter 05 Sequential CircuitsNguyen Yen NhiNo ratings yet

- Assignment 1 - ReriewDocument5 pagesAssignment 1 - ReriewAnh NamNo ratings yet

- L5: Simple Sequential Circuits and VerilogDocument25 pagesL5: Simple Sequential Circuits and VerilogGaurav UpadhyayNo ratings yet

- Clocking StrategiesDocument21 pagesClocking Strategiesswapnikasharma100% (1)

- Sequential StaticDocument20 pagesSequential Staticvivek singhNo ratings yet

- Verilog Coding ExamplesDocument41 pagesVerilog Coding ExamplesKarishma PotnuruNo ratings yet

- Verilog For Sequential Circuits: Example of D - LATCHDocument20 pagesVerilog For Sequential Circuits: Example of D - LATCHAbhishekBarmaNo ratings yet

- VHDL 3 - Sequential Logic Circuits: Reference: Roth/John Text: Chapter 2Document29 pagesVHDL 3 - Sequential Logic Circuits: Reference: Roth/John Text: Chapter 2Soni NsitNo ratings yet

- Sequential Circuits Hardware Description Language: LectureDocument38 pagesSequential Circuits Hardware Description Language: LecturemarwaNo ratings yet

- Lec 3 (VHDL For Combinational Circuits)Document30 pagesLec 3 (VHDL For Combinational Circuits)eslam MohamedNo ratings yet

- Static Timing Analysis - MaharshiDocument29 pagesStatic Timing Analysis - MaharshiSatish Yada100% (1)

- Aplicaciones Spartan6 Ver1Document42 pagesAplicaciones Spartan6 Ver1juan mezaNo ratings yet

- L8 - Sequential Circuit Design With VerilogDocument17 pagesL8 - Sequential Circuit Design With VerilogNicho GuimbaolibotNo ratings yet

- Hardware Description Languages and Sequential Logic: Flip-FlopsDocument14 pagesHardware Description Languages and Sequential Logic: Flip-FlopsMohammad Seemab AslamNo ratings yet

- Static Sequential CircuitsDocument29 pagesStatic Sequential CircuitsfneojwgfjeNo ratings yet

- N-Bit Shift Register PDFDocument232 pagesN-Bit Shift Register PDFAnuradha KhalkhoNo ratings yet

- Day 11psnewDocument19 pagesDay 11psnewEffecure HealthcareNo ratings yet

- Chapitre 3Document88 pagesChapitre 3Brahim AttiaNo ratings yet

- Week10 Sequential CircuitsDocument27 pagesWeek10 Sequential Circuitsnavarrojules53No ratings yet

- Timing For Pipelined System: BITS PilaniDocument62 pagesTiming For Pipelined System: BITS PilaniSuvigya VijayNo ratings yet

- L5: Simple Sequential Circuits and VerilogDocument25 pagesL5: Simple Sequential Circuits and VerilogKadal ChaitraNo ratings yet

- Lec02 Sequential CircuitDocument45 pagesLec02 Sequential Circuityanjia8161100No ratings yet

- Advanced VLSI Design: Timing IssuesDocument88 pagesAdvanced VLSI Design: Timing IssuesSudhanshu BadolaNo ratings yet

- Final ExamDocument14 pagesFinal Exam한지원No ratings yet

- VHDL PgmsDocument2 pagesVHDL Pgmsprabha_velNo ratings yet

- EXP-11 and 12Document10 pagesEXP-11 and 12Aryan SharmaNo ratings yet

- L25 - Datapath Design - p1Document46 pagesL25 - Datapath Design - p1Shanawar AliNo ratings yet

- Lab 7 - COADocument3 pagesLab 7 - COAABHYANSH SHRIVASTAVANo ratings yet

- Mathworks Simulink and C++ Integration With The New VLT Plc-Based Standard Development Platform For Instrument Control SystemsDocument11 pagesMathworks Simulink and C++ Integration With The New VLT Plc-Based Standard Development Platform For Instrument Control SystemsKleberson MeirelesNo ratings yet

- A Tutorial: Transient Domain Flip-Flop Models For Mixed-Mode SimulationDocument28 pagesA Tutorial: Transient Domain Flip-Flop Models For Mixed-Mode SimulationVinitKharkarNo ratings yet

- New Text DocumentDocument3 pagesNew Text DocumentNaveen NegiNo ratings yet

- Something We Can't Build (Yet)Document22 pagesSomething We Can't Build (Yet)John DingNo ratings yet

- VHDL Code For D FF Using Behavior ModelDocument20 pagesVHDL Code For D FF Using Behavior ModelAdithya ChakilamNo ratings yet

- Verilog Code FAQDocument25 pagesVerilog Code FAQRAGUL RAJ SNo ratings yet

- For Each Question Use Template in Student Database System!!!Document4 pagesFor Each Question Use Template in Student Database System!!!Mehmethan Ayrım0% (1)

- Sequential ExampleDocument11 pagesSequential ExampleAmit JadhavNo ratings yet

- SCOE Vadgaon Pune: Unit Iii Algorithmic State MachineDocument11 pagesSCOE Vadgaon Pune: Unit Iii Algorithmic State MachineDeepakNo ratings yet

- Flip FlopsDocument6 pagesFlip FlopsRahul PendyalaNo ratings yet

- VLSI Design I VLSI Design I VLSI Design I VLSI Design IDocument23 pagesVLSI Design I VLSI Design I VLSI Design I VLSI Design ISaksham sangwanNo ratings yet

- DSD RTL Coding Lec8Document31 pagesDSD RTL Coding Lec8Arshad RasheedNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Doulos SysVlog Interface Modports PaperDocument8 pagesDoulos SysVlog Interface Modports PaperkrishnaavNo ratings yet

- Unix Vi HelpDocument2 pagesUnix Vi HelpJobin IdicullaNo ratings yet

- FSM SVDocument23 pagesFSM SVkrishnaavNo ratings yet

- Sample Interview QuesitonsDocument2 pagesSample Interview QuesitonskrishnaavNo ratings yet

- A Practical Guide To Adopting The Universal Verfication MethodologyDocument199 pagesA Practical Guide To Adopting The Universal Verfication MethodologykrishnaavNo ratings yet

- FPGA Design FlowDocument6 pagesFPGA Design FlowmkumarsampathNo ratings yet

- Nowka Low Power 07Document53 pagesNowka Low Power 07api-3864016100% (1)

- UNIX ManDocument369 pagesUNIX Mangrees01No ratings yet

- Placement and RoutingDocument40 pagesPlacement and RoutingrajiNo ratings yet

- Integrated Circuit Fabrication Process Study Notes For ECEDocument9 pagesIntegrated Circuit Fabrication Process Study Notes For ECEkrishnaav100% (1)

- Cmos Design Rules Layout PDFDocument33 pagesCmos Design Rules Layout PDFkrishnaavNo ratings yet

- Benefits Static Timing Analysis WPDocument4 pagesBenefits Static Timing Analysis WPAnonymous oRvjAm9nNo ratings yet

- Fpga Vs Asic Design FlowDocument32 pagesFpga Vs Asic Design FlowkrishnaavNo ratings yet

- Synopsys Test BenchDocument294 pagesSynopsys Test BenchkrishnaavNo ratings yet

- Sva CDC Paper Dvcon2006 PDFDocument6 pagesSva CDC Paper Dvcon2006 PDFkrishnaavNo ratings yet

- Verilog HDL: A Solution For Everybody: By, Anil Kumar Ram Rakhyani (Akram@)Document30 pagesVerilog HDL: A Solution For Everybody: By, Anil Kumar Ram Rakhyani (Akram@)naresh_sambhnani5702No ratings yet

- High-Speed Digital System DesignDocument327 pagesHigh-Speed Digital System DesignEnSon ChangNo ratings yet

- Fpga Vs Asic Design FlowDocument32 pagesFpga Vs Asic Design Flowkrishnaav100% (1)

- Fpga Vs Asic Design FlowDocument32 pagesFpga Vs Asic Design FlowkrishnaavNo ratings yet

- Mixed Signal DesignDocument21 pagesMixed Signal Designhe4dsh0kNo ratings yet

- Analog Discovery PDFDocument95 pagesAnalog Discovery PDFkrishnaav100% (1)

- Cadence ManualDocument51 pagesCadence Manualapi-27099960100% (4)

- Kin India ProbabilityDocument38 pagesKin India ProbabilitySrinivasan SridharanNo ratings yet

- Opamps TheoryDocument8 pagesOpamps TheoryZoilo ManzanoNo ratings yet

- Prasad HTC InvoiceDocument2 pagesPrasad HTC InvoicekrishnaavNo ratings yet

- Bridge Axi AhbDocument22 pagesBridge Axi Ahbkrishnaav100% (1)

- MicroDocument20 pagesMicrokrishnaavNo ratings yet

- Improved Accuracy Current-Mode Multiplier Circuits With Applications in Analog Signal Processing PDFDocument5 pagesImproved Accuracy Current-Mode Multiplier Circuits With Applications in Analog Signal Processing PDFkrishnaavNo ratings yet

- K L University: Time: 3 Hours Max. Marks: 100Document1 pageK L University: Time: 3 Hours Max. Marks: 100krishnaavNo ratings yet

- Prasad HTC InvoiceDocument2 pagesPrasad HTC InvoicekrishnaavNo ratings yet

- Bipolar Junction Transistors Talha Syed NaqviDocument51 pagesBipolar Junction Transistors Talha Syed NaqviMuhammad AwaisNo ratings yet

- Analog Communications Laboratory (Document5 pagesAnalog Communications Laboratory (shivam007No ratings yet

- Low Power VLSI 2022-23Document1 pageLow Power VLSI 2022-23souranshusNo ratings yet

- TdaDocument7 pagesTdaΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Design of A Continuous Time Equalizer Circuit (CTLE)Document3 pagesDesign of A Continuous Time Equalizer Circuit (CTLE)Juan Diego Ramírez ArdilaNo ratings yet

- Datasheet ICL7650 REEMPLAZO PARA EL TC911A DEL INCUBATOR SHAKER PARA PLACAS ELISADocument12 pagesDatasheet ICL7650 REEMPLAZO PARA EL TC911A DEL INCUBATOR SHAKER PARA PLACAS ELISAJose GodoyNo ratings yet

- Icom Ic F 3 GT-GSDocument39 pagesIcom Ic F 3 GT-GSradioclubcopiapoNo ratings yet

- The Circuit in Fig. (A) Is Equivalent To The One Shown in Fig. (B)Document15 pagesThe Circuit in Fig. (A) Is Equivalent To The One Shown in Fig. (B)Ameer ShNo ratings yet

- CH 06 FET BiasingDocument20 pagesCH 06 FET BiasingHatem DheerNo ratings yet

- Four Quadrant OperationDocument15 pagesFour Quadrant OperationPrasanna KSNo ratings yet

- Calibration of High Voltage Resistor DividersDocument2 pagesCalibration of High Voltage Resistor DividersLina Muñoz CantilloNo ratings yet

- SCD-1 777ES SupplementDocument14 pagesSCD-1 777ES SupplementamlNo ratings yet

- JammerDocument21 pagesJammeraritra singh100% (5)

- 2m 144mhz-146mhz ReceiverDocument14 pages2m 144mhz-146mhz ReceiverGeorge Leong100% (1)

- 0.6-2.7-Gbs Referenceless Parallel CDR With A Stochastic Dispersion-Tolerant Frequency Acquisition TechniqueDocument7 pages0.6-2.7-Gbs Referenceless Parallel CDR With A Stochastic Dispersion-Tolerant Frequency Acquisition TechniqueMinh KhangNo ratings yet

- Notes 326 Set3Document10 pagesNotes 326 Set3bezasamiNo ratings yet

- ReportDocument33 pagesReportRahatul RifatNo ratings yet

- Eetop - CN ADC LayoutDocument199 pagesEetop - CN ADC LayoutVishnuGundaNo ratings yet

- Ece326 Lab 3 Exp 19Document8 pagesEce326 Lab 3 Exp 19max1039No ratings yet

- MV-1FX Stereo Mod - 5023dbf2ba2b5Document8 pagesMV-1FX Stereo Mod - 5023dbf2ba2b5Wagner GonçalvesNo ratings yet

- Analog MultiplierDocument13 pagesAnalog MultipliersmartdeepjariwalaNo ratings yet

- Motorola Semiconductor Data - MC14510BDocument10 pagesMotorola Semiconductor Data - MC14510BmamamammamammmmNo ratings yet

- Analog MultiplierDocument9 pagesAnalog MultiplierPravin Sanap0% (1)

- Oscillator Design Guide For Stm8af Al S Stm32 Mcus and Mpus StmicroelectronicsDocument56 pagesOscillator Design Guide For Stm8af Al S Stm32 Mcus and Mpus StmicroelectronicsLinh PhạmNo ratings yet

- Lab 3 Spring 2020 LTSpice Edition-1Document6 pagesLab 3 Spring 2020 LTSpice Edition-1dadNo ratings yet

- A Voltage Regulator Is Designed To Automatically Maintain A Constant Voltage LevelDocument3 pagesA Voltage Regulator Is Designed To Automatically Maintain A Constant Voltage LevelAhmad FadhliNo ratings yet

- ECE 4101 Computer and Information Lab III - Experiment 2Document14 pagesECE 4101 Computer and Information Lab III - Experiment 2AHMAD ANWARNo ratings yet

- LIC Lab ManualDocument14 pagesLIC Lab Manuallinusntn59No ratings yet

- IC-2410 Service Manual PDFDocument78 pagesIC-2410 Service Manual PDFssanzonesNo ratings yet

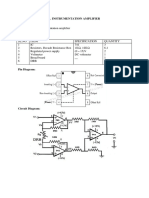

- To Design An Instrumentation AmplifierDocument4 pagesTo Design An Instrumentation AmplifierArun RajeshNo ratings yet