Professional Documents

Culture Documents

Features: 40A Drmos Power Module With Integrated Diode Emulation and Thermal Warning Output

Uploaded by

antoniocljOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Features: 40A Drmos Power Module With Integrated Diode Emulation and Thermal Warning Output

Uploaded by

antoniocljCopyright:

Available Formats

DATASHEET

ISL99140 FN8642

40A DrMOS Power Module with Integrated Diode Emulation and Thermal Rev.2.00

Warning Output Jul 20, 2017

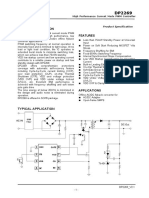

The ISL99140 is a high performance DrMOS power module

designed for high frequency power conversion. By combining a

Features

high performance FET driver and MOSFETs in an advanced • Compliant with Intel DrMOS revision 4.0 specifications

package, high density DC/DC converters can be created. • 40A average output current capability

Combined with an Intersil PWM controller, a complete voltage

• Supports 3-state 3.3V PWM input

regulator solution can be created with reduced external

components and minimum overall PCB real estate. • Supports 2-state 5V PWM input

The ISL99140 features a three-state PWM input that, working • Thermal warning output

together with Intersil’s multiphase PWM controllers, will • Diode emulation option

provide a robust solution in the event of abnormal operating

• Adaptive shoot-through protection

conditions. To further support robust applications, the

ISL99140 features a thermal warning output that can be used • Integrated high-side gate-to-source resistor to prevent self

to notify the power system of an impending thermal fail event. turn-on due to high input bus dV/dt

The ISL99140 supports high efficiency operation not only at • Undervoltage lockout

heavy loads, but also at light loads through its diode emulation • Switching frequencies up to 2MHz

capability. Diode emulation can be disabled for those • Pb-free (RoHS compliant)

applications in which variable frequency operation is not

desired at light loads. • 6x6 QFN package

Related Literature Applications

• For a full list of related documents, visit our website • High frequency and high efficiency VRM and VRD

- ISL99140 product page • Core, graphic, and memory regulators for microprocessors

• High density VR for server, networking, and cloud computing

• POL DC/DC converters and video gaming consoles

+12V

+5V

PVCC

VIN

VCC

EN

BOOT

PHASE

SHOOT-

SMOD

THROUGH LOUT

PROTECTION VOUT

INTERSIL PWM

CONTROLLER PVCC

LOGIC

THDN

EN CONTROL

COUT

AGND

PG ND

GND

FIGURE 1. SIMPLIFIED APPLICATION BLOCK DIAGRAM

FN8642 Rev.2.00 Page 1 of 15

Jul 20, 2017

ISL99140

Ordering Information

PART NUMBER PART TEMP RANGE TAPE AND REEL QUANTITY PACKAGE PKG.

(Notes 1, 2, 3) MARKING (°C) (UNITS) (RoHS Compliant) DWG. #

ISL99140IRZ-T 99140 IRZ -40 to +85 3k 40 Ld Exposed Pad 6x6 QFN L40.6x6A

NOTES:

1. Refer to TB347 for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil

Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), see the product information page for ISL99140. For more information on MSL, see TB363.

TABLE 1. KEY DIFFERENCES BETWEEN FAMILY OF PARTS

CURRENT

RATING PWM THERMAL OCP PACKAGE P2P

PART # (A) (V) FLAG FLAG IMON TMON DWG. # COMPATIBLE USED WITH

5.0V PWM POWER STAGE FAMILY

ISL99125B 25 5.0 No No No No L24.3.5x5W ISL99135B Analog Controllers: ISL633x, ISL636x, ISL637x,

ISL95829, ISL9585x

ISL99135B 35 5.0 No No No No L24.3.5x5W ISL99125B

Digital Hybrid Controllers: ISL68201, ISL6388/98

ISL99227B 60 5.0 Yes Yes Yes Yes L32.5x5V N/A Full Digital Controller: ZL8802

Phase Doublers: ISL6617, ISL6617A

3.3V PWM POWER STAGE FAMILY

ISL99140 40 3.3 Yes No No No L40.6x6A N/A Full Digital Controllers: ISL68/69xxx, ZL8802

Digital Hybrid Controllers: ISL68201, ISL6388/98

ISL99227 60 3.3 Yes Yes Yes Yes L32.5x5V N/A

(3.3V PWM Setting)

Functional Block Diagram

VCC THDN PVCC BOOT PHASE GH VIN

THERMAL

MONITOR

EN POR

20k

29.16k SHOOT-

PWM

THROUGH SW

PWM LOGIC

PROTECTION

12.5k PVCC

500k

AGND

ZERO SW GL

DETECT GH

PGND

SMOD GL PGND

FIGURE 2. FUNCTIONAL BLOCK DIAGRAM

FN8642 Rev.2.00 Page 2 of 15

Jul 20, 2017

ISL99140

Pin Configuration

ISL99140

(40 LD QFN)

TOP VIEW

PHASE

SMOD

AGND

BOOT

PVCC

VCC

VIN

VIN

VIN

GH

10 9 8 7 6 5 4 3 2 1

VIN 11 40 PWM

VIN 12 39 EN

VIN AGND

PAD2 PAD1

VIN 13 38 THDN

VIN 14 37 GND

SW 15 36 GL

PGND 16 35 SW

PGND 17 34 SW

SW

PAD3

PGND 18 33 SW

PGND 19 32 SW

PGND 20 31 SW

21 22 23 24 25 26 27 28 29 30

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

SW

SW

FN8642 Rev.2.00 Page 3 of 15

Jul 20, 2017

ISL99140

Pin Descriptions

PIN NUMBER PIN NAME DESCRIPTION

1 SMOD Input pin to enable or disable diode emulation with built-in pull up of 10μA. When SMOD is LOW, diode emulation

is allowed. Otherwise, continuous conduction mode is forced.

2 VCC +5V logic bias supply. Place a high quality low ESR ceramic capacitor from this pin to GND.

3 PVCC +5V driver bias supply. Place a high quality low ESR ceramic capacitor from this pin to GND. VCC and PVCC often

share the decoupling capacitor (~1μF/0402~0603/ X5R~X7R).

4 BOOT Floating bootstrap supply pin for the upper gate drive. Place a high quality low ESR ceramic capacitor (~0.1μF to

0.22μF) in close proximity across the BOOT and PHASE pins. A series resistor (typically 1.5 to 3.9Ω) with a bootstrap

capacitor is optional, but recommended for high input voltage applications.

5, 37, PAD1 AGND, GND Return of logic bias supply VCC. Connect directly to the system ground plane.

6 GH High-side gate drive output for monitoring/testing. No circuit connection needed.

7 PHASE Return of bootstrap capacitor. Internally connected to SW node. External connection is not needed.

8, 9, 10, 11, 12, 13, VIN Input of Power Stage. Place couple high quality low ESR ceramic capacitor (couple 10μF or higher, X7R) and a high

14, PAD2 frequency decoupling capacitor (0.1μF to 1μF) in close proximity across the VIN and GND planes.

16, 17, 18, 19, 20, PGND Power Stage return. Connect directly to the system ground plane.

21, 22, 23, 24, 25,

26, 27, 28

15, 29, 30, 31, 32, SW Switching junction node between low and high-side MOSFETs. Connect directly to the output inductor.

33, 34, 35, PAD3

36 GL Low-side gate drive output for monitoring/testing. No circuit connection needed.

38 THDN Thermal warning flag, an output open-drain pin. High = Normal operation; Low = Shutdown.

39 EN Enable input pin with 2μA internal weak pull-down. High = Enable; Low = Disable.

40 PWM PWM input of gate driver. The PWM signal can enter three distinct states during operation. Connect this pin to the

PWM output of the controller.

FN8642 Rev.2.00 Page 4 of 15

Jul 20, 2017

ISL99140

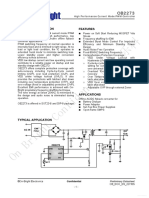

Typical Application Circuits

+5V

VCC

VSEN_OVP

VSEN

RGND VIN VINF

RISENIN1 RISENIN2 RSENIN

SVDATA

ISENIN -

SVALERT#

SVCLK ISENIN +

VR_RDY

VR_HOT# +5V VINF

SM_PM_I2DA ISL99140

VCC BOOT

SM_PMALERT#

UG PHASE

SM_PM_I2CLK

PWM1 PWM LG

VINF

ISEN1-

ISEN1+

EN_PWR_CFP

+5V VINF

ISL99140

CFP VCC BOOT

ISL6388 UG PHASE

PWM4 PWM LG

IMON

ISEN4-

+5V ISEN4+

PWM2,5

2X NVM_BANK_BT

ISEN2,5-

VRSEL _ADDR

ISEN 2,5+

AUTO +5V VINF

ISL99140 LOAD

VCC BOOT

UG PHASE

RSET PWM3 PWM LG

ISEN3-

ISEN3+

+5V VINF

+5V ISL99140

VCC BOOT

UG PHASE

TM_EN_OTP

NTC PWM6 PWM LG

ISEN6-

GND ISEN6+

NTC1 NETWORK IS NOT NEEDED

IF TMS IS USED FOR VR1, GPU

FIGURE 3. TYPICAL APPLICATION CIRCUIT WITH ISL6388

FN8642 Rev.2.00 Page 5 of 15

Jul 20, 2017

ISL99140

Typical Application Circuits (Continued)

VIN

10.8 TO 13.2V R14

C3 CIN1

1 m 1µF

VDD

IINN

IINP

5V

C9 V25

10µF

C10 V5

10µF

V6

PVCC

VIN

C11 U3 L1

10µF

VCC

C4 SW

ISL99140

1µF C1

U1 PHASE R1

AGND C5

SYNC BOOT 0.1 µF

PWMH0 PWM THDN

PGND

R10 SA PWML0 EN SMOD

R11 VSET0 VOUT

R12 UVLO

ISENA0

ISENB0 COUT

R13

5V VIN

CIN2

ZL8800

PVCC

VIN

CONTROL EN L2

AND VCC

STATUS PG SW

C7

ISL99140

V5 1µF R2 C2

AGND U2 PHASE C8

BOOT 0.1µF

R9 PWMH1 PWM

10 k THDN

PGND

PWML1 EN SMOD

INTER-DEVICE DDC

COORDINATION

SYNC ISENA1

(OPTIONAL)

ISENB1

SDA VSEN 0N

PMBus

(OPTIONAL) VSEN0P

SCL

DGND SGND

FIGURE 4. TYPICAL APPLICATION CIRCUIT WITH ZL8800

FN8642 Rev.2.00 Page 6 of 15

Jul 20, 2017

ISL99140

Absolute Maximum Ratings Thermal Information

Continuous Current (Notes 8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40A Thermal Resistance JA (°C/W) JC (°C/W)

VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to 30V 40 Ld 6x6 QFN Package (Notes 4, 5, 7) . . 14.5 5

Supply Voltage (VCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to 7V Maximum Junction Temperature (Plastic Package) . . . . . . . . . . . .+150°C

I/O Voltage (VEN, VPWM, VSMOD, V THDN). . . . . . . . . . . -0.3V to VCC + 0.3V Maximum Storage Temperature Range . . . . . . . . . . . . . .-65°C to +150°C

BOOT Voltage (VBOOT-GND) . . . . . . . . . . -0.3V to 25V (DC) or 36V (<200ns) Pb-Free Reflow Profile . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . see TB493

BOOT To PHASE Voltage (VBOOT-PHASE). . . . . . . . . . . . . . . . -0.3V to 7V (DC)

-0.3V to 9V (<10ns)

PHASE Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . (GND - 0.3V) to 30V Recommended Operating Conditions

(GND - 10V) (<20ns Pulse Width, 10µJ) Ambient Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . -40°C to +85°C

Maximum Operating Junction Temperature . . . . . . . . . . . . . . . . . . +125°C

Supply Voltage, VCC, PVCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5V 5%

Input Supply Voltage, VIN (Notes 9) . . . . . . . . . . . . . . . . . . . . . . . . 0V to 20V

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product

reliability and result in failures not covered by warranty.

NOTES:

4. JA is measured in free air with the component mounted on an Intersil evaluation board with “direct attach” features. Refer to TB379 for general

thermal metric information.

5. For JC, the “case temp” location is the center of the exposed metal pad on the package underside.

6. Jedec Class II pulse conditions and failure criterion used.

7. These ratings vary with PCB layout and operating conditions.

8. Limited to power dissipation, thermal management solution, junction temperature, and over-temperature trip point for continuous operation; lower

power dissipation and better cooling design allow higher continuous current.

9. A tightly decoupling loop across VIN and PGND with input ceramics capacitors is required. See “PCB Layout Considerations” on page 10 for details.

A resistor in series (typically 1.5 to 3.9Ω) with a bootstrap capacitor is optional, but recommended for high input voltage applications to prevent

exceeding the absolute maximum ratings of the device.

Electrical Specifications

/

TA = +25°C; VIN = 12V, VVCC = VPVCC = 5V unless otherwise noted. Boldface limits apply across the

recommended operating temperature range.

MIN MAX

PARAMETER SYMBOL TEST CONDITIONS (Note 10) TYP (Note 10) UNIT

SUPPLY CURRENT

VCC Standby Supply Bias Current IVCC EN = Low, VVCC = 5V 187 µA

EN = High, VPWM = Open 467 µA

EN = High, VPWM = 0V 664 µA

PVCC Supply Bias Current IPVCC EN = High, VPWM = 300kHz, 50% duty cycle 23 mA

EN = High, VPWM = 1MHz, 50% duty cycle 51 mA

POWER-ON RESET AND ENABLE

POR Rising Threshold VPORR 3.40 3.90 V

POR Falling Threshold VPORF 2.3 2.92 V

POR Hysteresis VPORH 570 mV

EN High Threshold VENH 2.0 V

EN Low Threshold VENL 0.8 V

EN Pull-Down Current IENL 2 µA

PWM INPUT

Pull-Up Impedance 29.1 kΩ

Pull-Down Impedance 12.5 kΩ

PWM Rising Threshold VPWMH VVCC = 5V 1.70 2.05 2.35 V

PWM Falling Threshold VPWML VVCC = 5V 0.75 1.00 1.25 V

PWM Tri-State Rising Threshold VTRIH VVCC = 5V 1.10 1.32 1.50 V

FN8642 Rev.2.00 Page 7 of 15

Jul 20, 2017

ISL99140

Electrical Specifications TA = +25°C; VIN = 12V, VVCC = VPVCC = 5V unless otherwise noted. Boldface limits apply across the

recommended operating temperature range. (Continued)

MIN MAX

PARAMETER SYMBOL TEST CONDITIONS (Note 10) TYP (Note 10) UNIT

PWM Tri-State Falling Threshold V TRIL VVCC = 5V 1.60 1.75 1.95 V

PWM Tri-State Rising Hysteresis V TRRH VVCC = 5V 310 mV

PWM Tri-State Falling Hysteresis V TRFH VVCC = 5V 310 mV

SWITCHING TIME

GH Turn-On Propagation Delay tPDHU VVCC = 5V, see Figure 5 (GL Low to GH High) 15 ns

GH Turn-Off Propagation Delay tPDLU VVCC = 5V, see Figure 5 (PWM Low to GH Low) 18 ns

GL Turn-On Propagation Delay tPDHL VVCC = 5V, see Figure 5 (GH Low to GL High) 20 ns

GL Turn-Off Propagation Delay tPDLL VVCC = 5V, see Figure 5 (PWM High to GL Low) 18 ns

GH/GL Exit Tri-State Propagation Delay tPDTS VVCC = 5V, see Figure 5 (Tri-State to GH/GL High) 20 ns

Tri-State Shutdown Hold-Off Time tTSSHD VVCC = 5V, see Figure 5 75 150 225 ns

Minimum GL On-Time in DCM tLGMIN VVCC = 5V 350 ns

SMOD INPUT

SMOD High Threshold VSMODH 2.0 V

SMOD Low Threshold VSMODL 0.8 V

SMOD Pin Pull-Up Current ISMOD 10 µA

THERMAL SHUTDOWN (THDN)

Pull-Down Impedance 1mA 60 Ω

Output Low 1mA 70 mV

Thermal Shutdown Flag Set (Note 11) 150 °C

Thermal Shutdown Flag Clear (Note 11) 135 °C

Hysteresis (Note 11) 15 °C

NOTES:

10. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and

are not production tested.

11. Limits established by characterization and are not production tested.

FN8642 Rev.2.00 Page 8 of 15

Jul 20, 2017

ISL99140

PWM

tPDHU tPDLU

tTSSHD

tPDTS

tPDTS

UGATE tRU tFU

tPDHL

LGATE

tRL

tFL

tPDLL tTSSHD

FIGURE 5. TIMING DIAGRAM

TABLE 2. GATE DRIVE TRUTH TABLE

ENABLE SMOD PWM GL GH

L X X L L

H L L H (Note 12) L

H L H L H

H H L H L

H H H L H

NOTE:

12. The GL stays high until the inductor current drops to zero.

Operation The rising edge on PWM initiates the turn-off of the lower MOSFET.

Adaptive shoot-through circuitry monitors the GL voltage and

The ISL99140 is an optimized driver and power stage solution for determines a safe time for the upper MOSFET to turn on. This

high density synchronous DC/DC power conversion. The prevents the MOSFET’s from conducting simultaneously.

ISL99140 includes a high performance driver, integrated

The falling PWM transition causes the upper FET to turn off and

Schottky bootstrap diode, and MOSFET pair optimized for high

the lower FET to turn-on. Adaptive shoot-through circuitry

switching frequency buck voltage regulators. The ISL99140

monitors the GH to SW voltage to determine a safe time for

includes a driver with advanced power management features

low-side MOSFET turn-on. This prevents the MOSFETs from

that allow direct control of the Lower MOSFET, diode emulation,

conducting simultaneously.

and thermal protection.

If the driver has no bias voltage applied and is unable to actively

Power-On Reset (POR) and EN hold the MOSFETs off, an integrated 20kΩ resistor from the

During initial start-up, the VCC voltage rise is monitored. When upper MOSFET gate-to-source will aid in keeping the device in its

the rising VCC voltage exceeds 3.40V (typically), normal operation off state. This can be especially critical in applications where the

of the driver is enabled. If VCC drops below the falling threshold of input voltage rises before the ISL99140 VCC /PVCC supplies.

2.92V (typically), operation of the driver is disabled.

Tri-State PWM Input

If the EN pin is pulled low, the driver will immediately force both

The ISL99140 supports a tri-level input on the PWM pin. If the pin

MOSFETS to their off states. This action does not depend on the

is pulled into and remains in the tri-state window for a set holdoff

state of the PWM input.

time, the driver will force both MOSFETs to their off states. When

Shoot-Through Protection the PWM signal moves outside the shutdown window, the driver

immediately resumes driving the MOSFETs according to the

Before VCC exceeding its POR level, the undervoltage protection PWM commands.

function is activated and both GH and GL are held active low (off).

When the VCC voltage surpasses the Rising Threshold (see This feature is used by Intersil PWM controllers as a method of

“Electrical Specifications” on page 7) the PWM, SMOD, and DE forcing both MOSFETs off. If the PWM input is left floating, the

signals are used to control both high-side and low-side MOSFETs. pin will be pulled into the tri-state window internally and force

both MOSFETs to a safe off state. The ISL99140’s tri-state levels

are compatible with 3.3V PWM logic.

FN8642 Rev.2.00 Page 9 of 15

Jul 20, 2017

ISL99140

Although PWM input can sustain as high as VCC, the ISL99140 is Thermal Shutdown Warning (THDN)

not compatible with a controller (such as ISL637x family) that

The THDN pin is an open-drain output and is pulled low when the

actively drives its mid level in tri-state higher than 1.7V. However,

internal junction temperature exceeds +150°C. The ISL99140

the ISL99140 can be configured to be compatible with ZL8800 by

does not stop operation when the flag is set. This signal is often

connecting PWMH to PWM and PWML to EN, as shown in Figure 4

fed back to the controller to issue a system thermal shutdown.

on page 6. In this example, the tri-state operation is controlled by

When the junction temperature drops below +135°C, the device

PWML output of ZL8800 through ISL99140’s EN input. For detailed

will clear the THDN signal.

design information, consult the ZL8800 datasheet.

Diode Emulation PCB Layout Considerations

Diode emulation allows for higher converter efficiency under light Proper PCB layout will reduce noise coupling to other circuits,

load situations. With diode emulation active (SMOD pulled low), improve thermal performance, and maximize the efficiency. The

the ISL99140 will detect the zero current crossing of the output following is meant to lead to an optimized layout:

inductor and turn off the low-side gate after the minimum LGATE

ON time of 350ns expires. This ensures that Discontinuous • Place a 0.1µF and multiple 10µF or greater ceramic capacitors

Conduction Mode (DCM) is achieved to minimize losses. Diode directly at device between VIN and PGND as indicated in

emulation is asynchronous to the PWM signal. Therefore, the Figure 7. This is the most critical decoupling and reduces

ISL99140 will respond to the SMOD input immediately after it parasitic inductance in the power switching loop. This will

changes state. reduce overall electrical stress on the device as well as reduce

coupling to other circuits. Best practice is to place the

Bootstrap Function decoupling capacitors on the same PCB side as the device.

The ISL99140 features an internal bootstrap Schottky diode. A • Connect PGND to the system GND plane with a large via array

high quality ceramic capacitor should be placed in close proximity as close to the PGND pins as design rules allow. This improves

across the BOOT and PHASE pins. The bootstrap capacitor can thermal and electrical performance.

range between 0.1µF~0.22µF/0402~0603/X5R~X7R for normal • Place PVCC, VCC, and BOOT-PHASE decoupling capacitors at

buck switching applications. A resistor (typically 1.5Ω to 3.9Ω) in the IC pins with the shortest loop as shown in Figure 7.

series with a bootstrap capacitor is optional, but recommended

for high input voltage application to prevent exceeding the • Note that the SW plane connecting the ISL99140 and inductor

absolute maximum ratings of the device. must carry full load current and will create resistive loss if not

sized properly. However, it is also a very noisy node that should

5V

not be oversized or routed close to any sensitive signals. Best

RBT is optional, practice is to place the inductor as close to the device as

but recommended possible and thus minimize the required area for the SW

for high VIN connection. If the user must choose a long route of either the

PVCC

VIN

VOUT side of the inductor or the SW side, choose the quiet VOUT

VCC side. Best practice is to locate the ISL99140 as close to the

SW

1µF ISL99140 RBT final load as possible and thus avoid noisy or lossy routes to

U1 BOOT the load.

AGND

CBT

PHASE

PWM THDN

PGND

EN SMOD

FIGURE 6. BOOT RESISTOR OPTION

TABLE 3. AVAILABLE EVALUATION BOARDS

SMBus/

EVALUATION BOARDS DESCRIPTION PMBus/I2C

ISL6388EVAL1Z 6-Phase Core VR with ISL99140, 6x6 DrMOS, and the ISL6388, EAPP Digital Controller; Socket R3 Yes

ISL6398EVAL1Z 3-Phase POL VR with ISL99140, 6x6 DrMOS, and the ISL6388, EAPP Digital Controller; On-Board Transient Load Yes

FN8642 Rev.2.00 Page 10 of 15

Jul 20, 2017

ISL99140

FIGURE 7. PCB LAYOUT FOR MINIMIZING CURRENT LOOPS

FN8642 Rev.2.00 Page 11 of 15

Jul 20, 2017

ISL99140

Typical Performance Characteristics

300kHz

600kHz

EFFICIENCY (%)

EFFICIENCY (%)

300kHz

800kHz 600kHz

800kHz

OUTPUT CURRENT (A) OUTPUT CURRENT (A)

FIGURE 8. 1.0V VOUT POWER STAGE EFFICIENCY FIGURE 9. 1.8V VOUT POWER STAGE EFFICIENCY

(VIN = 12V, VCC = PVCC = 5V; LOUT = 0.23µH, 0.23mΩ, (VIN = 12V, VCC = PVCC = 5V; LOUT = 0.23µH, 0.23mΩ,

SLC1175-231; INCLUDE INDUCTOR AND ISL99140 SLC1175-231; INCLUDE INDUCTOR AND ISL99140

LOSSES) LOSSES)

300kHz

300kHz

POWER LOSS (W)

POWER LOSS (W)

600kHz

600kHz

800kHz

800kHz

OUTPUT CURRENT (A) OUTPUT CURRENT (A)

FIGURE 10. 1.0V VOUT POWER STAGE DISSIPATION FIGURE 11. 1.8V VOUT POWER STAGE DISSIPATION

(VIN = 12V, VCC = PVCC = 5V; LOUT = 0.23µH, 0.23mΩ, (VIN = 12V, VCC = PVCC = 5V; LOUT = 0.23µH, 0.23mΩ,

SLC1175-231; INCLUDE INDUCTOR AND ISL99140 SLC1175-231; INCLUDE INDUCTOR AND ISL99140

LOSS) LOSSES)

FN8642 Rev.2.00 Page 12 of 15

Jul 20, 2017

ISL99140

Revision History The revision history provided is for informational purposes only and is believed to be accurate, but not warranted.

Please visit our website to make sure that you have the latest revision.

DATE REVISION CHANGE

Jul 20, 2017 FN8642.2 Updated Related Literature section.

Added Table 1.

Updated the BOOT and VIN pin descriptions.

Added 40A continuous current under absolute maximum ratings.

Updated Theta JA value from “50” to “14.5”.

Updated Note 4.

Added Notes 7, 8, and 9.

Opened up the recommended VIN range from “4.5V to 18V” to “0 to 20V”.

In “Power-On Reset (POR) and EN” on page 9, changed “3.5V” to “3.4V” and “2.95V” to “2.92V” to match

page 7 in the “Electrical Specifications” table.

Updated Note 12, corrected typo LG to GL.

Updated “Bootstrap Function” on page 10.

Added “a 0.1µF and” on first bullet and “the with shortest loop” on the third bullet under PCB Layout

Considerations.

Jan 7, 2016 FN8642.1 Updated the Ordering Information table on page 2 by adding the tape and reel quantity.

Under “Absolute Maximum Ratings” on page 7, added the following:

“Phase Voltage............................(GND - 0.3V) to 30V

(GND-10V) (<20ns Pulse Width, 10µJ)

May 5, 2014 FN8642.0 Initial release

About Intersil

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products

address some of the largest markets within the industrial and infrastructure, mobile computing, and high-end consumer markets.

For the most updated datasheet, application notes, related documentation, and related parts, see the respective product information

page found at www.intersil.com.

For a listing of definitions and abbreviations of common terms used in our documents, visit www.intersil.com/glossary.

You can report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support.

© Copyright Intersil Americas LLC 2014-2017. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted

in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such

modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are

current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its

subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN8642 Rev.2.00 Page 13 of 15

Jul 20, 2017

ISL99140

Package Outline Drawing

L40.6x6A

40 LEAD THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE

Rev 0, 3/14

D A D1 D1

D/2 PIN #1 IDA

B e/2 e L6

30 21 C0.30 x 45° 1 10

31 20

40 11

2 E/2 E1 E1

L2 L1

INDEX AREA

(D/2 x E/2) L3 L1

E

L5

E2 L

e

aaa C

40

2x

11 20 L4

31

1 10 30 21

A3 L5

2x

L D2

aaa C

TOP VIEW BOTTOM VIEW

ccc C A3

C

A

SEATING

PLANE

4

40 x b 3

ddd C A1 bbb M C A B

SIDE VIEW

DIMENSIONS IN MILLIMETERS

SYMBOLS MIN TYP MAX

A 0.70 0.75 0.80

A1 0.00 0.02 0.05

A3 0.20 REF

b 0.20 0.25 0.35

D 6.00 BSC

D1 1.90 2.00 2.10

NOTES:

D2 4.30 4.40 4.50

E 6.00 BSC 1. Dimensions are in millimeters.

E1 1.40 1.50 1.60 2. The location of the terminal #1 identifier and

terminal numbering convention conforms to

E2 2.17 2.27 2.37 JEDEC publication 95 SPP-002.

e 0.50 BSC

3. Dimension b applies to metallized terminal and is

L 0.30 0.40 0.50 measured between 0.20mm and 0.35mm from the

L1 0.15 0.20 0.25 terminal tip. If the terminal has the optional radius

on the other end of the terminal, the dimension b

L2 0.15 0.21 0.26 should not be measured in that radius area.

L3 0.63 0.73 0.83

4. Coplanarity applies to the terminals and all other

L4 0.44 0.54 0.64 bottom surface metallization.

L5 0.30 0.40 0.50

L6 0.27 0.37 0.47

aaa 0.15

bbb 0.10

ccc 0.10

ddd 0.08

FN8642 Rev.2.00 Page 14 of 15

Jul 20, 2017

ISL99140

4.40

2.20

0.40

0.25 0.75

0.54

0.55

2.87

0.20 2.27

0.21

0.52

0.73

2.23

1.50 2.87

0.20 0.37

0.30 x 45°

0.50 REF

0.25

2.00 2.00

2.87 2.87

RECOMMENDED LAND PATTERN

NOTE:

1. Dimensions are in millimeters.

FN8642 Rev.2.00 Page 15 of 15

Jul 20, 2017

You might also like

- Max16833 Max16833gDocument25 pagesMax16833 Max16833gKwun Hok ChongNo ratings yet

- ISL6269 Data SheetDocument14 pagesISL6269 Data SheetSummer SpringNo ratings yet

- HIP6302CBDocument18 pagesHIP6302CBrjbordaNo ratings yet

- tps92210 Led DriverDocument32 pagestps92210 Led DriverRoberto DiasNo ratings yet

- ISL6455 RenesasDocument13 pagesISL6455 RenesasArief MandolloNo ratings yet

- HOJA DE DATOS ncp1083Document17 pagesHOJA DE DATOS ncp1083Diego Javier Ramirez PerezNo ratings yet

- HF920Document26 pagesHF920anon_14062780No ratings yet

- Pdt003a0x3-Srz LynxDocument39 pagesPdt003a0x3-Srz LynxefixlukasNo ratings yet

- TPS92641 BuckDocument42 pagesTPS92641 BuckLeon MartinezNo ratings yet

- Integrated High Power PoE-PD Interface & DC-DC Converter ControllerDocument18 pagesIntegrated High Power PoE-PD Interface & DC-DC Converter ControllerArun PadmanabhanNo ratings yet

- Power Module: Magi CDocument56 pagesPower Module: Magi CGiderosNo ratings yet

- Infineon ICE5ARxxxxBZS DS v02 - 10 EN PDFDocument36 pagesInfineon ICE5ARxxxxBZS DS v02 - 10 EN PDFanand shekhawatNo ratings yet

- Green Mode Power Switch For Valley Switching Converter - Low EMI and High Efficiency FSQ0365, FSQ0265, FSQ0165, FSQ321Document22 pagesGreen Mode Power Switch For Valley Switching Converter - Low EMI and High Efficiency FSQ0365, FSQ0265, FSQ0165, FSQ321Mekkati MekkatiNo ratings yet

- FDMF 6823 DCDocument19 pagesFDMF 6823 DCtechgamebr85No ratings yet

- Tps 56 C 230Document30 pagesTps 56 C 230maxibettNo ratings yet

- 100V Input, 1A High Power LED Driver: The Future of Analog IC TechnologyDocument10 pages100V Input, 1A High Power LED Driver: The Future of Analog IC TechnologyAdrian WongNo ratings yet

- NB676 DatasheetDocument19 pagesNB676 DatasheetRudy BudimanNo ratings yet

- Primary-Side Control, Offline LED Controller With Active PFC, NTC and PWM DimmingDocument19 pagesPrimary-Side Control, Offline LED Controller With Active PFC, NTC and PWM Dimmingzuffflor_925748656No ratings yet

- Bicmos Advanced Phase-Shift PWM Controller: Features DescriptionDocument31 pagesBicmos Advanced Phase-Shift PWM Controller: Features DescriptionSaikumarNo ratings yet

- FDMF6823B FairchildSemiconductorDocument19 pagesFDMF6823B FairchildSemiconductortechgamebr85No ratings yet

- Synchronous Step Down Converter: High Efficiency 3A, 24V, 500KhzDocument16 pagesSynchronous Step Down Converter: High Efficiency 3A, 24V, 500KhzAnonymous 8bbVmLtQNo ratings yet

- Fan 7317Document23 pagesFan 7317Lauswalk WalkNo ratings yet

- Ucc28c40, Ucc28c41, Ucc28c42, Ucc28c43, Ucc28c44, Ucc28c45 Ucc38c40, Ucc38c41, Ucc38c42, Ucc38c43, Ucc38c44, Ucc38c45Document32 pagesUcc28c40, Ucc28c41, Ucc28c42, Ucc28c43, Ucc28c44, Ucc28c45 Ucc38c40, Ucc38c41, Ucc38c42, Ucc38c43, Ucc38c44, Ucc38c45curz0% (1)

- MAX3010 Pulse OximeterDocument32 pagesMAX3010 Pulse OximeterjimmyNo ratings yet

- MAX30102 High-Sensitivity Pulse Oximeter and Heart-Rate Sensor For Wearable HealthDocument32 pagesMAX30102 High-Sensitivity Pulse Oximeter and Heart-Rate Sensor For Wearable Healthjair portillo cardenasNo ratings yet

- MAX30102 High-Sensitivity Pulse Oximeter and Heart-Rate Sensor For Wearable HealthDocument32 pagesMAX30102 High-Sensitivity Pulse Oximeter and Heart-Rate Sensor For Wearable HealthEnya Andrea Ribba HernandezNo ratings yet

- Tps51116-Ep FDocument38 pagesTps51116-Ep FDaniel Norberto DemariaNo ratings yet

- MAX30102 High-Sensitivity Pulse Oximeter and Heart-Rate Sensor For Wearable HealthDocument32 pagesMAX30102 High-Sensitivity Pulse Oximeter and Heart-Rate Sensor For Wearable HealthDymas AgungNo ratings yet

- MAX30102 High-Sensitivity Pulse Oximeter and Heart-Rate Sensor For Wearable HealthDocument32 pagesMAX30102 High-Sensitivity Pulse Oximeter and Heart-Rate Sensor For Wearable HealthBOURAS Ihabe - بوراس إيهابNo ratings yet

- MAX30102 High-Sensitivity Pulse Oximeter and Heart-Rate Sensor For Wearable HealthDocument32 pagesMAX30102 High-Sensitivity Pulse Oximeter and Heart-Rate Sensor For Wearable HealthZulfan JauharNo ratings yet

- MAX30102 High-Sensitivity Pulse Oximeter and Heart-Rate Sensor For Wearable HealthDocument32 pagesMAX30102 High-Sensitivity Pulse Oximeter and Heart-Rate Sensor For Wearable Healthpenetrator123No ratings yet

- Current Mode PWM Controller: General DescriptionDocument12 pagesCurrent Mode PWM Controller: General DescriptionAlex GerasimenkoNo ratings yet

- Tsop 752 WDocument13 pagesTsop 752 WMatias RendonNo ratings yet

- TSOP752.., TSOP754..: Vishay SemiconductorsDocument13 pagesTSOP752.., TSOP754..: Vishay SemiconductorsMaktum KamatNo ratings yet

- Bosch Ic cs600 NewDocument2 pagesBosch Ic cs600 NewAdlan MessaoudNo ratings yet

- FSQ510 85947Document15 pagesFSQ510 85947علی امامیNo ratings yet

- FSQ510, FSQ510H - Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant ConverterDocument15 pagesFSQ510, FSQ510H - Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant ConverterEletronica TecnotronicaNo ratings yet

- DP2269Document7 pagesDP2269GABRIEL AMORIM ARAUJONo ratings yet

- Tps 54140Document52 pagesTps 54140niceautomation8831No ratings yet

- Power Management Ic For Li-Ion Powered Systems: Features DescriptionDocument45 pagesPower Management Ic For Li-Ion Powered Systems: Features DescriptionErmand WindNo ratings yet

- Power Management Ic For Li-Ion Powered Systems: Features DescriptionDocument45 pagesPower Management Ic For Li-Ion Powered Systems: Features DescriptionErmand WindNo ratings yet

- OB2273 On BrightDocument12 pagesOB2273 On BrightCarlos PosadaNo ratings yet

- OB2362 DatasheetDocument10 pagesOB2362 DatasheetTín SmpsNo ratings yet

- Max20050-Max20053 2A Synchronous-Buck Led Drivers With Integrated MosfetsDocument23 pagesMax20050-Max20053 2A Synchronous-Buck Led Drivers With Integrated MosfetsAdrian WongNo ratings yet

- 100V/2A Peak, Low Cost, High Frequency Half Bridge Driver FeaturesDocument13 pages100V/2A Peak, Low Cost, High Frequency Half Bridge Driver FeaturescarcavaNo ratings yet

- SN65HVD1050DR Texas InstrumentsDocument21 pagesSN65HVD1050DR Texas InstrumentsMoises HernandezNo ratings yet

- Tps 51218Document27 pagesTps 51218techgamebr85No ratings yet

- High Performance, Single Synchronous Step-Down Controller For Notebook Power SupplyDocument28 pagesHigh Performance, Single Synchronous Step-Down Controller For Notebook Power Supplym. sochaNo ratings yet

- MP4001 r1.02-474738Document17 pagesMP4001 r1.02-474738gabe1989No ratings yet

- tps73201 EpDocument22 pagestps73201 EpDavid WangNo ratings yet

- HF/VHF Power MOS Transistor: Important NoticeDocument19 pagesHF/VHF Power MOS Transistor: Important Noticegabriel souza silva soares coimbraNo ratings yet

- Av02 0891en - Ds - Acpl m60l - 2017 03 03 1827568Document15 pagesAv02 0891en - Ds - Acpl m60l - 2017 03 03 1827568mikeguo76No ratings yet

- 4.5V To 23V Input, 3-A Synchronous Step-Down SWIFT™ Converter With Eco-Mode™Document23 pages4.5V To 23V Input, 3-A Synchronous Step-Down SWIFT™ Converter With Eco-Mode™temarioNo ratings yet

- 4.5V To 23V Input, 3-A Synchronous Step-Down SWIFT™ Converter With Eco-Mode™Document21 pages4.5V To 23V Input, 3-A Synchronous Step-Down SWIFT™ Converter With Eco-Mode™Egor FedorenkoNo ratings yet

- HCPL 7601 AvagoDocument13 pagesHCPL 7601 AvagoSyed Khawar MukhtarNo ratings yet

- HIP6302CBDocument16 pagesHIP6302CBterry panNo ratings yet

- A1205 Datasheet PDFDocument14 pagesA1205 Datasheet PDFAlekso GjakovskiNo ratings yet

- A1205 DatasheetDocument14 pagesA1205 DatasheetAlekso GjakovskiNo ratings yet

- ISL6363 - Multiphase PWM Regulator For VR12™ Desktop CPUsDocument32 pagesISL6363 - Multiphase PWM Regulator For VR12™ Desktop CPUsАндрій КлепачNo ratings yet

- FSM Implementations: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017Document25 pagesFSM Implementations: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017antoniocljNo ratings yet

- Lecture 5 - Combinatorial and Sequential LogicDocument76 pagesLecture 5 - Combinatorial and Sequential LogicantoniocljNo ratings yet

- Lecture 6 - RTL SynthesisDocument72 pagesLecture 6 - RTL SynthesisantoniocljNo ratings yet

- VHDL Basics: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017Document68 pagesVHDL Basics: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017antoniocljNo ratings yet

- VHDL Basics: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017Document46 pagesVHDL Basics: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017antoniocljNo ratings yet

- Introduction To System Design, VHDL BasicsDocument49 pagesIntroduction To System Design, VHDL BasicsantoniocljNo ratings yet

- Lecture 1 - Introduction: Arto Perttula TIE-50206 Logic Synthesis Tampere University of Technology 2017-2018Document57 pagesLecture 1 - Introduction: Arto Perttula TIE-50206 Logic Synthesis Tampere University of Technology 2017-2018antoniocljNo ratings yet

- MCP 9600Document50 pagesMCP 9600antonioclj100% (1)

- VHDL Coding Rules: Tampere University of Technology Department of Computer Systems Version 4.4 - Jan 2009Document54 pagesVHDL Coding Rules: Tampere University of Technology Department of Computer Systems Version 4.4 - Jan 2009antoniocljNo ratings yet

- Tut Quartus Intro VHDLDocument29 pagesTut Quartus Intro VHDLantoniocljNo ratings yet

- Research ArticleDocument7 pagesResearch ArticleantoniocljNo ratings yet

- Eeol 2008aug01 RFD Intd Ta 01Document3 pagesEeol 2008aug01 RFD Intd Ta 01antonioclj100% (2)

- Max13450e Max13451eDocument17 pagesMax13450e Max13451eantonioclj100% (1)

- Vmware Esxi DatasheetDocument1 pageVmware Esxi DatasheetdinonetNo ratings yet

- Hsn8100Na Product Overview: Flexible Xhaul Solutions For 4G and 5GDocument2 pagesHsn8100Na Product Overview: Flexible Xhaul Solutions For 4G and 5GArun Balaji VNNo ratings yet

- Disassembling The System UnitDocument10 pagesDisassembling The System UnitArman SantiagoNo ratings yet

- Chapter 6 Laplace TransformsDocument20 pagesChapter 6 Laplace TransformshanythekingNo ratings yet

- HP 7700 Access Point Series - 3COM Wireless 7760 11A B G POE AP - SpecificationsDocument4 pagesHP 7700 Access Point Series - 3COM Wireless 7760 11A B G POE AP - Specificationsedgar7venNo ratings yet

- Distributed Control SystemDocument10 pagesDistributed Control SystemRavenShieldX100% (1)

- Unisab III Compressor Control DrawingDocument34 pagesUnisab III Compressor Control DrawingRadwan AL Troug100% (1)

- Course Name ClassstartdateDocument276 pagesCourse Name ClassstartdateRishabh GuptaNo ratings yet

- 92800047176h Manual 3EL2 EN-unlockedDocument16 pages92800047176h Manual 3EL2 EN-unlockedRenraNo ratings yet

- Drive Low Voltage Motors: Manual For M3000 and M2000 RangesDocument13 pagesDrive Low Voltage Motors: Manual For M3000 and M2000 RangesElton PetroliNo ratings yet

- Performance Analysis of Inter-Satellite Optical Wireless Communication (Isowc) System at 980 NM and 1550 NM WavelengthsDocument6 pagesPerformance Analysis of Inter-Satellite Optical Wireless Communication (Isowc) System at 980 NM and 1550 NM WavelengthsJoy MarchNo ratings yet

- Marvel HTC WWE Safety-Regulatory GuideDocument20 pagesMarvel HTC WWE Safety-Regulatory GuiderrNo ratings yet

- XH10P 20P DatasheetDocument1 pageXH10P 20P Datasheetluthfie4uNo ratings yet

- Smart S Mk2 October 2010 HRDocument2 pagesSmart S Mk2 October 2010 HRbujor2000ajaNo ratings yet

- How To Make Mobile Controlled Robot Using BluetoothDocument11 pagesHow To Make Mobile Controlled Robot Using BluetoothAvian WorkshopsNo ratings yet

- Exp - No:4 Date:30.09.2020: Verification of Sampling TheoremDocument9 pagesExp - No:4 Date:30.09.2020: Verification of Sampling TheoremSreemathyNo ratings yet

- t125 Trojan Data SheetsDocument2 pagest125 Trojan Data Sheetsapi-255381998No ratings yet

- Chap 06 SP1 SolutionsDocument23 pagesChap 06 SP1 SolutionsKaleem UllahNo ratings yet

- A Multi Phase Harmonic Load Flow Solution TechniqueDocument9 pagesA Multi Phase Harmonic Load Flow Solution TechniquerameshpampanaNo ratings yet

- Manual O&M Tablero FD120Document32 pagesManual O&M Tablero FD120Nelson IglesiasNo ratings yet

- Chapter 01Document91 pagesChapter 01fangqing chenNo ratings yet

- A Full Wave Rectifier Is A Circuit Arrangement Which Makes Use of Both Half Cycles of Input Alternating CurrentDocument9 pagesA Full Wave Rectifier Is A Circuit Arrangement Which Makes Use of Both Half Cycles of Input Alternating CurrentKaran SoniNo ratings yet

- SCC3 20A 12V Solar Charge Controller Electronic CircuitDocument2 pagesSCC3 20A 12V Solar Charge Controller Electronic CircuituimNo ratings yet

- Comparative Analysis of Low Power 10T and 14T FullDocument6 pagesComparative Analysis of Low Power 10T and 14T Fullkhaja mohiddienNo ratings yet

- Patent Search & Analysis Report (PSAR)Document4 pagesPatent Search & Analysis Report (PSAR)mickyvirusNo ratings yet

- Signal Sampling: - Sampling Is Converting A Signal Into A Signal - CategoriesDocument57 pagesSignal Sampling: - Sampling Is Converting A Signal Into A Signal - Categoriesimranchaudhry12No ratings yet

- Mercedes Sprinter 907 ManualDocument11 pagesMercedes Sprinter 907 ManualRavishka SilvaNo ratings yet

- Salman Salu ElectricalDocument9 pagesSalman Salu ElectricalAzeem AsgharNo ratings yet

- Soft Sensors For ContinuousDocument16 pagesSoft Sensors For ContinuousHari Prasath T RNo ratings yet

- Midea R410A T3 50Hz Split Type Top-Dishcharge Series Technical Manual - V201707Document157 pagesMidea R410A T3 50Hz Split Type Top-Dishcharge Series Technical Manual - V201707kaleabNo ratings yet

- NEMA StandardsDocument87 pagesNEMA StandardsMurugadas Rangasamy0% (2)