Professional Documents

Culture Documents

Documents - Tips Ask FSK PSK QPSK Qam Modu

Documents - Tips Ask FSK PSK QPSK Qam Modu

Uploaded by

Nguyễn HoàngOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Documents - Tips Ask FSK PSK QPSK Qam Modu

Documents - Tips Ask FSK PSK QPSK Qam Modu

Uploaded by

Nguyễn HoàngCopyright:

Available Formats

MỤC LỤC

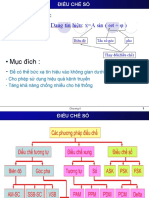

1. GIỚI THIỆU CHUNG.............................................................................................2

2. ĐIỀU CHẾ TƯƠNG TỰ CHO TÍN HIỆU SỐ ASK, FSK, PSK, QPSK, QAM

MODULATION-DEMOLATION.....................................................................................5

2.1. Thiết bị sử dụng..............................................................................................5

2.2. Lý thuyết.........................................................................................................5

2.2.1 Các phương pháp điều chế tương tự cho tín hiệu số.............................5

2.2.1.1. Phương pháp điều chế - Giải điều chế biên độ ASK (Amplitude

Shift Keying).......................................................................................................5

2.2.1.2. Phương pháp điều chế - Giải điều chế biên độ FSK (Frequency

Shift Keying).......................................................................................................6

2.2.1.3. Phương pháp điều chế - Giải điều chế pha PSK (Phase Shift

Keying) 7

2.2.1.4. Phương pháp điều chế - Giải điều chế hỗn hợp pha và biên độ

QAM (Quadrature Amplitude Modulation)........................................................12

2.2.1.5. Phương pháp điều chế - Giải điều chế pha vi phân DPSK

(Differential Phase Shift Keying)......................................................................14

2.2.1.6. Mã truyền và tái lập tín hiệu nhịp...................................................16

2.2.2 Sơ đồ thí nghiệm...................................................................................17

2.2.2.1. Bộ điều chế ASK, FSK, PSK, QPSK, QAM...................................17

2.2.2.2. Bộ Giải điều chế ASK, FSK, PSK, QPSK......................................23

2.3. Cấp nguồn và nối dây...................................................................................27

2.4. Các bài thực hành.........................................................................................28

2.4.1 Khảo sát các phần chức năng...............................................................28

2.4.1.1. Máy phát nhịp tài liệu (Data Sequence Generator).......................28

2.4.1.2. Các sơ đồ tạo mã tài liệu...............................................................28

2.4.1.3. Bộ hình thành sóng mang (carrier generator)................................31

2.4.1.4. Bộ tái lập tín hiệu nhịp và giải mã tài liệu (DECODER & CLOCK

RECOVERY)....................................................................................................31

2.4.2 Điều chế & giải điều chế tương tự cho tín hiệu số................................34

2.4.2.1. Điều chế & giải điều chế ASK........................................................34

2.4.2.2. Điều chế & giải điều chế FSK........................................................39

2.4.2.3. Điều chế và giải điều chế BPSK....................................................43

2.4.2.4. Điều chế & giải điều chế QPSK (hình 2-34)...................................47

2.4.2.5. Điều chế và giải điều chế D-QPSK (Hình 2-35).............................48

2.4.2.6. Điều chế QAM (hình 2-36).............................................................52

PULSE AMPLITUDE MODULATION (PAM)

1

HỆ THỰC HÀNH VỀ ĐIỆN TỬ THÔNG TIN

1. GIỚI THIỆU CHUNG

Hệ thống thiết bị thực hành điện tử viễn thông chuyên đề bao gồm các khối thí

nghiệm, thiết kế theo khối chuẩn (Module), và thiết bị chính TCPS-900.

Các khối thí nghiệm chức năng cho phép tiến hành các bài thực hành về điện

tử thông tin chuyên đề về cơ sở kỹ thuật truyền thông tin (xem mục lục đã liệt kê ở

trên).

Các khối thí nghiệm sử dụng chốt 2 ly để kết nối nguồn và tín hiệu. Trên bảng

mặt khối có biểu thị trực quan sơ đồ nguyên lý và các chốt thử (Test Point) để kiểm

tra tín hiệu.

Thiết bị chính TCPS-900 (Hình 1) dùng cho 1 bàn thí nghiệm, bao gồm:

Khung gá có kích thước 1.200 x 750 mm chứa 2 tầng với rãnh trượt để

gắn các module 297 mm x aM (M = 100mm, a = 1; 2; 3; 4)

Nguồn chuẩn TCPS-900, cung cấp thế chuẩn:

- Nguồn

1 chiều (DC) +12V/2A, -12V/0.75A, +5V/2A,

-5V/0.75A. Sử dụng để nuôi các Module thí nghiệm.

- Nguồn AC 220V với công tắc tự động, dùng để cấp điện cho các thiết bị

khác như dao động ký, máy phát,...

Phân loại tổng quát các phương pháp điều chế - giải điều chế phục vụ cho việc

truyền thông tin được giới thiệu trong Bảng 1.

Truyền các tín hiệu tương tự (lời nói, nhạc,...) theo phương pháp điều biên,

điều tần và điều pha được thực hiện trong phần thực tập điện tử thông tin cơ sở.

Các phương pháp cơ bản điều chế tín hiệu tương tự hoặc số còn lại trong

Bảng 1 được thực hiện trong phần thực hành điện tử thông tin chuyên đề.

PULSE AMPLITUDE MODULATION (PAM)

2

Bảng 1

PULSE AMPLITUDE MODULATION (PAM)

3

Hình 1. Thiết bị chính TCPS-900

PULSE AMPLITUDE MODULATION (PAM)

4

2. ĐIỀU CHẾ TƯƠNG TỰ CHO TÍN HIỆU SỐ ASK, FSK, PSK, QPSK, QAM

MODULATION-DEMOLATION.

2.1. Thiết bị sử dụng

1. Khung chính cho thực tập điện tử viễn thông cơ bản TCPS-900.

2. Các khối thí nghiệm TC-946M, TC-946D cho bài thực tập về điều chế tương

tự cho tín hiệu số (Hình 2-17 & 2-23).

3. Dao động ký 2 tia.

4. Phụ tùng: dây có chốt cắm hai đầu.

2.2. Lý thuyết

2.2.1 Các phương pháp điều chế tương tự cho tín hiệu số

2.2.1.1. Phương pháp điều chế - Giải điều chế biên độ ASK (Amplitude Shift Keying)

Phương pháp điều chế ASK (Hình 2-1) cho phép tạo tín hiệu ASK dạng sin với

hai biên độ. Biên độ tín hiệu ASK tuỳ thuộc giá trị bit tài liệu:

- Khi Data bit = 1 sẽ điều khiển khoá K đóng (Hình 2-1a), sóng ASK

nhận được ở lối ra chính là sóng mang truyền qua, có biên độ bằng biên độ

sóng mang (Hình 2-1b).

- Khi Data bit = 0 sẽ điều khiển khoá K ngắt, sóng mang không truyền

qua khoá. Tín hiệu ASK có biên độ = 0.

Hình 2-1. Phương pháp điều chế ASK

Giải điều chế ASK điều chế thực hiện theo các sơ đồ trên Hình 2-2.

Ở sơ đồ kiểu 2-2a, bộ thu nhận có tái lập sóng mang (Carrier Regenerator) và

nhân sóng này với tín hiệu thu. Bộ lọc thông thấp và sơ đồ ngưỡng cho phép tái lập

tài liệu số được truyền.

Sơ đồ 2-2b đơn giản hơn, thường được sử dụng trong thực tế. Tín hiệu được

tách sóng trực tiếp, sau đó lọc thông thấp và hình thành.

Phương pháp ASK có sơ đồ rất đơn giản, được sử dụng chủ yếu trong kỹ thuật

điện báo.

Hệ thống có các đặc trưng sau:

- Phổ cực tiểu của tín hiệu điều chế (FW) cao hơn tốc độ truyền bit (Fb).

- Hiệu suất truyền nhỏ hơn 1 (xác định bằng (Fb/ FW)<1).

PULSE AMPLITUDE MODULATION (PAM)

5

- “Tốc độ Baud” được định nghĩa như tốc độ điều chế bằng tốc độ truyền

Fb.

Hình 2-2. Phương pháp giải điều chế ASK

2.2.1.2. Phương pháp điều chế - Giải điều chế biên độ FSK (Frequency Shift Keying)

Phương pháp điều chế FSK (Hình 2-3) cho phép tạo tín hiệu FSK dạng sin với

hai tần số. Giá trị tần số của tín hiệu ASK tuỳ thuộc giá trị bit tài liệu. Ví dụ sử dụng

kiểu sơ đồ 2-3a:

- Khi Data bit = 1, điều khiển khoá K ở vị trí nối sóng mang tần số F1 với

lối ra FSK.

- Khi Data bit = 0, điều khiển khoá K ở vị trí nối sóng mang tần số F2 với

lối ra FSK.

- Giản đồ tín hiệu FSK cho trên hình 2-3D.

Hình 2-3. Phương pháp điều chế FSK

PULSE AMPLITUDE MODULATION (PAM)

6

Ở sơ đồ điều chế FSK kiểu 2-3b, sử dụng máy phát điều khiển bằng thế VCO

(Voltage Control Oscillator). Ứng dụng trạng thái “0” hoặc “1” của tài liệu, VCO

sẽ phát hai tần số F1 và F2 tương ứng.

Trên hình 2-3c là sơ đồ điều chế sử dụng các bộ chia với các hệ số chia khác

nhau: N và: M. Data bit sử dụng để điều khiển chọn hệ số chia. Ví dụ, khi Data

bit = 1, bộ chia có hệ số chia N, tạo chuỗi xung ra có tần số F1 = f Clock /N.

còn khi Data bit = 0, bộ chia có hệ số chia M, tạo chuỗi xung ra có tần số F2 =

f Clock /M.

Giải điều chế FSK có thể thực hiện trên cơ sở Hình 2-4. Tín hiệu FSK chứa hai

thành phần tần số được giải điều chế bằng sơ đồ vòng giữ pha ( PLL).

Hình 2-4. Phương pháp giải điều chế FSK

Phương pháp FSK có sơ đồ phức tạp hơn ASK, được sử dụng chủ yếu trong

modem truyền số liệu (kiểu CCITT V21, CCITT V23, BELL 103, BELL

113, BELL 202) và trong kỹ thuật radio số.

- Sai số ít hơn phương pháp ASK.

- Phổ cực tiểu của tín hiệu điều chế (FW) cao hơn tốc độ truyền bit (Fb).

- Hiệu suất truyền nhỏ hơn 1 (xác định bằng (Fb/ FW)<1).

- “Tốc độ Baud” được định nghĩa như tốc độ điều chế bằng tốc độ truyền Fb.

2.2.1.3. Phương pháp điều chế - Giải điều chế pha PSK (Phase Shift Keying)

a. Điều chế - Giải điều chế pha kiểu 2-PSK (BPSK)

Phương pháp điều chế 2-PSK hay BPSK (Binary PSK) hay điều chế ngược

pha PRK (Phase Reversal Keying) được giới thiệu trên Hình 2-5. Sơ đồ tạo

tín hiệu BPSK dạng sin với hai giá trị pha tuỳ thuộc giá trị bit tài liệu:

- Khi Data bit = 1, điều khiển sơ đồ cho sóng BPSK cùng pha với sóng

mang.

- Khi Data bit = 0, điều khiển sơ đồ cho sóng BPSK ngược pha (1800) với

sóng mang.

Sơ đồ điều chế thường được thực hiện trên bộ nhân sóng mang với Data bit.

Giản đồ tín hiệu và giản đồ poha BPSK cho trên Hình 2-5.

PULSE AMPLITUDE MODULATION (PAM)

7

Hình 2-5. Phương pháp điều chế PSK

Giải điều chế BPSK có thể thực hiện trên sơ đồ Hình 2-6. Sơ đồ gồm bộ tái lập

sóng mang và bộ nhân.

Hình 2-6. Phương pháp giải điều chế PSK.

Bộ tái lập sóng mang bao gồm:

- Sơ đồ lấy bình phương ( )2 để chuyển các tín hiệu khác pha về cùng 1 pha.

- Vòng giữa pha PLL phát lại nhịp với tần số gấp đôi tần số mang

- Bộ dịch pha để hiệu chỉnh pha.

- Bộ chia hai để đưa tần số tín hiệu tái lập về bằng tần số sóng mang.

Bộ nhân tín hiệu thực hiện nhân sóng điều chế BPSK với sóng mang tái lập.

Giả sử tần số sóng mang là fC, C = 2fC, ta có hai trường hợp:

- Khi tín hiệu BPSK là +sin(Ct) ứng với Data bit = 1, sóng mang tái

lập là sin(Ct), sơ đồ nhân sẽ cho tín hiệu sin(Ct) sin(Ct) =

sin2(Ct) = ½(1-cos(2 Ct) = ½ - ½cos(2Ct).

Trong biểu thức trên thành phần thứ hai là xoay chiều, có tần số gấp đôi tần số

sóng mang. Khi sử dụng bộ lọc thông thấp với tần số cắt bằng tần số sóng mang, có

thể khử bỏ thành phần xoay chiều và thế dương của thành phần 1 chiều thứ nhất

được giữ lại sẽ biểu diễn trạng thái “1” của Data bit.

- Khi tín hiệu BPSK là -sin(Ct) ứng với Data bit =1, sơ đồ nhân sẽ

cho tín hiệu :

-sin(Ct) sin(Ct) = -sin2(Ct) = -½(1-cos(2 Ct) = -½

+ ½cos(2Ct).

PULSE AMPLITUDE MODULATION (PAM)

8

Trong biểu thức trên thành phần thứ hai là xoay chiều, có tần số gấp đôi tần số

sóng mang. Khi sử dụng bộ lọc thông thấp với tần số cắt bằng tần số sóng mang, có

thể khử bỏ thành phần xoay chiều và thế âm của thành phần 1 chiều thứ nhất được

giữ lại sẽ biểu diễn trạng thái “0” của Data bit.

Sơ đồ điều chế PSK có độ phức tạp trung bình, được sử dụng chủ yếu trong kỹ

thuật radio số. Hệ thống có các đặc trưng sau:

- Sai số ít hơn phương pháp FSK.

- Phổ cực tiểu của tín hiệu điều chế (FW) bằng tốc độ truyền bit (Fb).

- Hiệu suất truyền = 1 (xác định bằng (Fb/ FW) = 1).

- “Tốc độ Baud” được định nghĩa như tốc độ điều chế bằng tốc độ truyền

Fb.

b. Điều chế - Giải điều chế pha kiểu 4-PSK (QPSK)

Phương pháp điều chế 4-PSK hay QPSK (Quadrature PSK) được giới

thiệu trên Hình 2-7. Sơ đồ tạo tín hiệu QPSK dạng sin với bốn giá trị pha, xác định

bởi tổ hợp (cặp) 2 bit liền nhau của tài liệu nhị phân. Tổ hợp 2 bit liền nhau này được

gọi là Dibit có độ dài 2 khoảng bit.

Tài liệu nhị phân trước khi đưa vào sơ đồ điều chế được tạo mã Dibit nhờ

trigger đếm đôi đơn giản. Mã Dibit được biểu thị bằng tín hiệu I và Q:

- Tín hiệu tài liệu I (cùng pha – In Phase) gồm các mức thế ứng với giá trị bit

đầu của cặp bit khảo sát.

- Tín hiệu tài liệu Q (bậc 2 – Quadrature) gồm các mức thế ứng với giá trị bit

thứ hai của cặp bit khảo sát.

Hình 2-7. Phương pháp điều chế QPSK

Các tín hiệu I và Q được nhân với các sóng mang lệch pha nhau 90 0 (gọi là 0

= sin(Ct) và 90 = cos(Ct) ). Kết quả là khi lấy tổng tín hiệu ở cả hai

PULSE AMPLITUDE MODULATION (PAM)

9

nhánh của sơ đồ Hình 2-7, sẽ nhận được các tín hiệu 0 +90; -0 +90; 0

-90; -0 -90.

Bộ điều chế QPSK như vậy được xây dựng trên hai bộ BPSK, tạo ra hai tín hiệu

BPSKI và BPSKQ cho bộ lấy tổng để hình thành tín hiệu 4 pha. Giản đồ pha và dạng

sóng QPSK cho trên Hình 2-7. Trên đồ thị cho thấy với 4 giá trị của Dibit (I-Q),

tín hiệu QPSK có 4 pha khác nhau.

Giải điều chế QPSK có thể thực hiện trên sơ đồ Hình 2-8. Sơ đồ gồm bộ tái lập

sóng mang và các bộ nhân để tái lập Dibit. Mã Dibit sau đó được giải mã để chuyển

về trạng thái tài liệu thông thường.

Hình 2-8. Phương pháp giải điều chế QPSK

Bộ tái lập sóng mang (hình 2-9) bao gồm:

Hình 2-9. Sơ đồ tái lập sóng mang cho giải điều chế QPSK

- Hai sơ đồ lấy bình phương ( ) 2 để chuyển các tín hiệu khác pha về cùng 1

pha.

- Vòng giữ pha PLL phát lại nhịp với tần số gấp bốn tần số mang.

- Bộ dịch pha để hiệu chỉnh pha.

- Bộ chia hai chung để đưa tần số tín hiệu tái lập còn gấp đôi tần số sóng

mang.

- Hai bộ chia hai với nhịp điều khiển đếm lệch pha 90 0 (lấy từ Q đến Q của

bộ chia 2 chung) để tạo các sóng mang tái lập lệch pha nhau 90 0.

Hai bộ nhân tín hiệu thực hiện nhân sóng điều chế QPSK với các sóng mang tái

lập lệch pha. Tín hiệu giải điều chế được lọc thông thấp để tái lập tín hiệu Dibit. Qua

sơ đồ trigger, chuyển mã Dibit về mã tài liệu nhị phân thông thường.

PULSE AMPLITUDE MODULATION (PAM)

10

Sơ đồ điều chế QPSK có độ phức tạp cao, được sử dụng chủ yếu trong modem

truyền số liệu (kiểu CCITT V22, CCITT V26, BELL 201) và trong kỹ thuật

radio số.

Hệ thống có các đặc trưng sau:

- Sai số ít hơn phương pháp FSK.

- Phổ cực tiểu của tín hiệu điều chế (FW) bằng nửa tốc độ truyền bit (=Fb/2).

- Hiệu suất truyền = 2 (xác định bằng (Fb/ FW) = 2).

- “Tốc độ Baud” được định nghĩa như tốc độ điều chế bằng nửa tốc độ

truyền (=Fb/2).

c. Điều chế - Giải điều chế pha kiểu 8-PSK

Phương pháp điều chế 8-PSK tạo tín hiệu dạng sin với tám giá trị pha lệch

nhau 450, xác định bởi tổ hợp 3 bit liền nhau của tài liệu nhị phân. Tổ hợp 3 bit liền

nhau này được gọi là Tribit.

Tài liệu nhị phân trước khi đưa vào sơ đồ điều chế được tạo mã Tribit nhờ các

trigger đếm đôi đơn giản. Mã Tribit được biểu thị bằng tín hiệu I, Q và C.

Trên sơ đồ Hình 2-10 là giản đồ “chòm sao” tài liệu được mã ở dạng tribit

tương ứng với các pha tín hiệu lệch so với nhau 45 0.

Sơ đồ điều chế 8-PSK có độ phức tạp cao, được sử dụng chủ yếu trong

modem truyền số liệu (kiểu CCITT V27, BELL 208) và trong kỹ thuật radio số.

Hệ thống có các đặc trưng sau:

- Sai số ít hơn phương pháp QPSK.

- Phổ cực tiểu của tín hiệu điều chế (FW) bằng 1/3 tốc độ truyền bit (=Fb/3).

- Hiệu suất truyền = 3 (xác định bằng (Fb/ FW) = 3).

- “Tốc độ Baud” được định nghĩa như tốc độ điều chế bằng 1/3 tốc độ truyền

(=Fb/3).

Hình 2-10. Giản đồ “chòm sao cho điều chế 8-PSK và 16-PSK

PULSE AMPLITUDE MODULATION (PAM)

11

d. Điều chế - Giải điều chế pha kiểu 16-PSK

Phương pháp điều chế 16-PSK tạo tín hiệu dạng sin với tám giá trị pha lệch

nhau 22.50, xác định bởi tổ hợp 4 bit liền nhau của tài liệu nhị phân. Tổ hợp 4 bit

liền nhau này được gọi là Quadbit.

Tài liệu nhị phân trước khi đưa vào sơ đồ điều chế được tạo mã Quadbit nhờ

các trigger đếm đôi đơn giản.

Trên sơ đồ Hình 2-10 là giản đồ “chòm sao” tài liệu được mã ở dạng

Quadbit tương ứng với các pha tín hiệu lệch so với nhau 22.50.

Sơ đồ điều chế 16-PSK có độ phức tạp cao, được sử dụng chủ yếu kỹ thuật

radio số.

Hệ thống có các đặc trưng sau:

- Sai số ít hơn phương pháp 8-PSK.

- Phổ cực tiểu của tín hiệu điều chế (FW) bằng 1/4 tốc độ truyền bit (=Fb/4).

- Hiệu suất truyền = 4 (xác định bằng (Fb/ FW) = 4).

- “Tốc độ Baud” được định nghĩa như tốc độ điều chế bằng 1/4 tốc độ

truyền (=Fb/4).

2.2.1.4. Phương pháp điều chế - Giải điều chế hỗn hợp pha và biên độ QAM

(Quadrature Amplitude Modulation)

Trong phương pháp điều chế QAM, thông tin số được điều chế chứa trong cả

pha và biên độ tín hiệu truyền. Các giá trị tín hiệu điều chế có dạng sin với pha và

biên độ được xác định bởi tổ hợp các bit liên nhau của tài liệu nhị phân.

Hệ thống 8-QAM điều chế tín hiệu trên cơ sở tổ hợp Tribit của tài liệu. Một

nhóm trong chúng thay đổi biên độ và 2 nhóm còn lại thay đổi về phía pha. Tín hiệu

điều chế sẽ nhận 4 pha và 2 biên độ khác nhau (xem Bảng 2-1).

Trên sơ đồ hình 2-11 là giản đồ “chòm sao” tài liệu được mã ở dạng Tribit cho

điều chế 8-QAM.

Hệ thống 16-QAM điều chế tín hiệu trên cơ sở tổ hợp Quadbit của tài liệu. Tín

hiệu điều chế sẽ nhận 16 trạng thái khác nhau về pha và biên độ (xem Bảng 2-2).

Bảng 2-1

STT LỐI VÀO NHỊ PHÂN LỐI RA 8-QAM

1 0 0 0 0.716V -1350

2 0 0 1 1.848V -1350

3 0 1 0 0.765V -450

4 0 1 1 1.848V -450

5 1 0 0 0.765V +1350

6 1 0 1 1.848V +1350

7 1 1 0 0.765V +450

8 1 1 1 1.848V +450

PULSE AMPLITUDE MODULATION (PAM)

12

Hình 2-11. Giản đồ “chòm sao” cho điều chế 8-QAM và 16-QAM

Bảng 2.2

STT LỐI VÀO NHỊ PHÂN LỐI RA 16-QAM

1 0 0 0 0 0.311V -1350

2 0 0 0 1 0.850V -1750

3 0 0 1 0 0.311V -450

4 0 0 1 1 0.850V -150

5 0 1 0 0 0.850V -1050

6 0 1 0 1 1.161V -1350

7 0 1 1 0 0.850V -750

8 0 1 1 1 1.161V -450

9 1 0 0 0 0.311V 1350

10 1 0 0 1 0.850V 1750

11 1 0 1 0 0.850V 450

12 1 0 1 1 0.850V 150

13 1 1 0 0 0.850V 1050

14 1 1 0 1 1.161V 1350

15 1 1 1 0 0.850V 750

16 1 1 1 1 1.161V 450

Trên sơ đồ Hình 2-11 là giản đồ “chòm sao” tài liệu được mã ở dạng

Quadbit cho điều chế 16-QAM.

Sơ đồ điều chế QAM có độ phức tạp cao, được sử dụng chủ yếu trong modem

truyền số liệu (kiểu CCITT V22bis, CCITT V29, CCITT V32, CCITT

V33, BELL 209) và trong kỹ thuật radio số.

Hệ thống có các đặc trưng sau:

PULSE AMPLITUDE MODULATION (PAM)

13

- Sai số ít hơn phương pháp PSK.

- Phổ cực tiểu của tín hiệu điều chế ( FW) bằng 1/n tốc độ truyền bit ( =Fb/n),

với n là số bit khảo sát điều chế, ví dụ, n-3 cho 8-QAM, n=4 cho 16-QAM.

- Hiệu suất truyền = n (xác định bằng (Fb/ FW) = n).

- “Tốc độ Baud” được định nghĩa như tốc độ điều chế bằng 1/n tốc độ

truyền (=Fb/n).

2.2.1.5. Phương pháp điều chế - Giải điều chế pha vi phân DPSK (Differential Phase

Shift Keying)

Trong hệ thống điều chế PSK, việc giải điều chế được thực hiện khi so pha tức

thời của PSK với tín hiệu mang tái lập ở bộ thu. Hệ thống PSK với thông tin chứa

trong giá trị pha tuyệt đối còn được gọi là PSK tuyệt đối. Khó khăn của hệ thống này

là cần giữ pha của sóng mang tái lập không đổi.

Hệ thống DPSK được xây dựng cho phép giải quyết khó khăn nêu trên. Thông

tin trong hệ DSPK không chứa trong các giá trị tuyệt đối của pha sóng mang điều chế

mà chứa trong sự lệch pha của hai khoảng điều chế liên tiếp.

a. BPSK vi phân

Phương pháp điều chế BPSK vi phân được mô tả trên Hình 2-12 và 2-13.

Trong đó tài liệu đầu tiên được chuyển thành mã vi phân, sau đó sử dụng bộ BPSK

để điều chế pha.

Sơ đồ EX-OR (hoặc - loại trừ) đã được làm chậm đi 1 khoảng bit. Lối ra EX-

OR sẽ đảo bit ra thứ (n+1) nếu bit thứ (n) là “1” và giữ lối ra không đổi nếu bit

(n) = “0”.

Kết quả là ở lối ra bộ tạo mã vi phân có sự thay đổi pha 1800 ứng với mỗi bit tài

liệu = “1”.

Hình 2-12. Giản đồ mã vi phân.

Bộ giải điều chế BPSK vi phân có hai phần: giải điều chế BPSK thông thường

để nhận lại mã vi phân. Sau đó bộ giải mã vi phân chứa sơ đồ EX-OR và bộ làm

chậm 1 khoảng bit sẽ tái lập lại tài liệu.

PULSE AMPLITUDE MODULATION (PAM)

14

Hình 2-13. Phương pháp điều chế và giải điều chế BPSK vi phân

b. QPSK vi phân.

Phương pháp điều chế QPSK vi phân được mô tả trên Hình 2-14. Trong đó tài

liệu đầu tiên được chuyển thành mã vi phân dạng Dibit cho tín hiệu D-I và D-Q, sau

đó sử dụng bộ vi phân Dibit để điều chế pha vi phân là các sóng sin lệnh pha nhau

00, 900, 1800 và 2700.

Sơ đồ EX-OR (hoặc - loại trừ) được sử dụng làm bộ so sánh tài liệu NRZ lối

vào với tài liệu lối ra bộ so sánh ( EX-OR) đã được làm chậm đi một khoảng bit. Lối

ra EX-OR sẽ đảo bit ra thứ (n+1) nếu bít thứ (n) là “1” và giữ lối ra không đổi

nếu bit (n)= “0”.

Hình 2-14. Phương pháp điều chế và giải điều chế QPSK vi phân

Kết quả là ở lối ra bộ tạo mã vi phân có sự thay đổi pha 1800 ứng với mỗi bit

tài liệu = “1”.

Bảng 2-3 mô tả sự tương ứng giữa tài liệu Dibit và sự dịch pha tín hiệu ra.

Bảng 2-3

DIBIT DỊCH PHA

0 0 00

0 1 900

1 1 1800

1 0 2700

PULSE AMPLITUDE MODULATION (PAM)

15

2.2.1.6. Mã truyền và tái lập tín hiệu nhịp

a. Mã NRZ.

Mã NRZ (Non Return-to-Zero) là dạng mã nhị phân thể hiện bằng bít

“0” và bit “1”, là xung chữ nhật, có mức “-a” hoặc “+a” được giữ trong độ dài

khoảng bit. Mã NRZ thường được chia thành 2 loại NRZ-L (Non Return to

Zero-level) và NRZ-I (Non Return to Zero-inverted).

Trong thí nghiệm, sử dụng trường hợp đặc biệt của mã NRZ-L (Hình 5-5a):

- NRZ - Data có phân cực ngược với tài liệu xác lập bằng các công tắc

Dip-Switch. Đó chính là dạng mã NRZ-L.

- Mức tín hiệu “+a” và “-a” tương ứng với mức “1” và “0” tín hiệu TTL.

Cách tạo mã trên sẽ làm đơn giản thí nghiệm khảo sát các phương pháp truyền

số liệu.

Ở phía thu nhận, các mức “0” và “1” được đọc lại tương ứng với tín hiệu

đồng bộ. Tín hiệu đồng bộ có thể gửi theo đường truyền riêng. Tuy nhiên, thường tín

hiệu đồng bộ được tách từ chuỗi tín hiệu tài liệu nhờ sơ đồ có vòng giữ pha ( PLL).

Hình 2-15. Giản đồ mã NRZ và mã Manchester

b. Tái lập tín hiệu nhịp

Sơ đồ tái lập xung nhịp được mô tả trên Hình 2-16.

Sơ đồ EX-OR được sử dụng để so sánh giữa tín hiệu tài liệu với tín hiệu tài liệu

được làm trễ (thường là khoảng ½ độ dài khoảng bit). Lối ra EX-OR có tín hiệu với

thành phần phổ tần số gấp đôi tín hiệu tài liệu. Sơ đồ vòng giữ pha PLL sẽ nhận

phát lại tín hiệu này với tần số nhịp tái lập bằng đúng tín hiệu nhịp sóng mang. Tín

hiệu nhịp tái lập được sử dụng để tạo nhịp cho các sơ đồ giải điều chế.

Hình 2-16. Sơ đồ tái lập tín hiệu nhịp

PULSE AMPLITUDE MODULATION (PAM)

16

c. Mã Manchester

Khi chuỗi tín hiệu tài liệu có bit 0 hoặc 1 kéo dài liên tục, tần số tín hiệu vào

PLL có thể vượt ra ngoài khoảng đồng bộ, vì vậy chuỗi xung nhịp lối ra được tái lập

có thể sẽ không còn chính xác. Để tránh sai lệch này có thể biểu diễn tài liệu dưới

dạng mã Manchester, trong đó bit 1 kéo dài được biểu diễn bằng chu kỳ xung

nhịp trực tiếp, còn bit 0 kéo dài - biểu diễn bằng chu kỳ xung ngược. Trên Hình 2-15

mô tả giản đồ hình thành xung Manchester từ xung NRZ.

2.2.2 Sơ đồ thí nghiệm

2.2.2.1. Bộ điều chế ASK, FSK, PSK, QPSK, QAM

Sơ đồ khối thí nghiệm TC-946M để điều chế ASK, FSK, PSK, QPSK,

QAM được trình bày trên Hình 2-17. Sơ đồ nguyên lý cho trong phần phụ lục (Hình

PL2-1PL2-4).

Hình 2-17. Khối điều chế tương tự cho tín hiệu số TC-946D.

a. Máy phát nhịp tài liệu (Data Sequence Generator)

Máy phát xung đồng hồ (Clock Generator):

- Máy phát xung đồng hồ tạo tín hiệu nhịp chuẩn cho các bộ hình thành tài liệu

thí nghiệm. Máy phát tạo trên U1 (NE555), phát xung vuông tần số

PULSE AMPLITUDE MODULATION (PAM)

17

2400Hz. Biến trở P1 (Frequency Adjust) cho phép hiệu chỉnh chính

xác tần số nhịp (Hình PL2-1).

- Bộ chia 2 trên trigger d U2A (74LS74) tạo xung nhịp chuẩn

1200Hz.

- Trigger R-S trên cổng U4A,D (74LS00) và nút nhấn START tạo tín

hiệu xoá và khởi động đồng bộ cho việc hình thành tài liệu.

Sơ đồ tạo tín hiệu mẫ thời gian CKI, CKQ, CKC (Timing Circuit):

- Sơ đồ tạo các xung mẫu thời gian được xây dựng trên bộ ghi dịch

U3(74LS96) và chuyển mạch MODE (S2A) chọn kiểu làm việc (hình

PL2-1). Ở chế độ Dibit và Tribit, lối ra song song bộ ghi dịch ( QB hoặc QC)

được đưa trở về lối vào nối tiếp (Serial). Nhờ vậy, bộ ghi dịch U3 có thể phát

chuỗi xung lặp lại.

- Khi nhấn nút START, bộ ghi dịch được xoá và xác lập trạng thái ban đầu từ

các lối vào song song (A = “1”, B, C = “0”) theo nhịp CK .

- Khi chuyển mạch S2A ở vị trí Dibit, lối ra song song QC được đưa về lối vào

nối tiếp (SER).

- Tín hiệu lối vào CK sẽ dịch trạng thái ghi trong U3 và chạy theo vòng, hình

thành tín hiệu CKI và CKQ (giản đồ Dibit trên Hình 2-18). Các tín hiệu này

lệch nhau một chu kỳ xung nhịp, được sử dụng cho thí nghiệm điều chế

QPSK và DQPSK.

- Khi chuyển mạch S2A ở vị trí Tribit, lối ra song song QB được đưa về lối vào

nối tiếp (SER).

- Tín hiệu lối vào CK sẽ dịch trạng thái ghi trong U3 và chạy theo vòng, hình

thành tín hiệu CKI, CKQ và CKC (giản đồ Tribit trên Hình 2-18). Các tín

hiệu này lệch nhau một chu kỳ xung nhịp, được sử dụng cho thí nghiệm điều

chế QAM.

Hình 2-18. Giản đồ thời gian tín hiệu mẫu CKI, CKQ và CKC

Sơ đồ tạo chuỗi xung tài liệu (Data Sequence):

PULSE AMPLITUDE MODULATION (PAM)

18

- Sơ đồ tạo chuỗi xung tài liệu được xây dựng trên các bộ ghi dịch U5U7

(74LS165) và chuyển mạch SW1SW24 đặc số liệu (Hình PL2-1).

- Bộ ghi dịch tạo chuỗi xung 24 bit gồm 3 tầng được nối theo vòng: lối ra nối

tiếp tầng trước nối với lối vào nối tiếp tầng sau. Vì vậy khi dịch số liệu, chuỗi

tài liệu 24 được lặp lại.

- Lối vào song song của 3 bộ ghi dịch nối với 24 công tắc. Với việc đặt các

công tắc này (ON = 1, OFF=0), nhờ tín hiệu START và CK có thể nạp số

liệu ban đầu lựa chọn từ công tắc vào bộ ghi để dịch thành chuỗi tài liệu

DATA tương ứng.

- Trên Hình 2-18 là ví dụ một chuỗi xung tài liệu NRZ tương ứng với cấu hình

công tắc lựa chọn.

b. Các sơ đồ tạo mã tài liệu.

Bộ tạo mã Manchester (Biphase Coder):

Bộ tạo mã Manchester từ tài liệu DATA được xây dựng trên vi mạch U8D,C

(Hình PL2-2), thực hiện so sánh mã tài liệu DATA với CK bằng sơ đồ EX-OR. Tín

hiệu ra sẽ là xung nhịp CK trực tiếp nếu Data bit = 1 và là CK nếu Data

bit = 0 (Hình 2-19).

Hình 2-19. Hình thành mã Manchester.

Bộ tạo mã vi phân 1-bit:

- Mã vi phân bit được tạo khi chuyển mạch S2B và S2D/MODE (Hình PL2-2)

ở vị trí Bit (1). Mã tài liệu DATA qua chuyển mạch này vào sơ đồ EX-

OR/U8A để so sánh với tín hiệu lối ra bộ so sánh ( EX-OR) đã được làm

chậm đi một khoản bit (xem sơ đồ khối Hình 2-13). Bộ làm trễ một khoảng

bit là trigger D/ U2B làm việc theo nhịp CK. Tín hiệu trễ truyền không

đảo qua U9C đưa trở về lối vào bộ so sánh U8A.

- Kết quả là bộ tạo mã vi phân sẽ đảo ngược bit ra thứ (n+1) nếu bit vào thứ

n = 1 và giữ lối ra không đổi nếu bit (n) = 0.

- Giản đồ tín hiệu mã vi phân 1- bit cho trên Hình 2-20.

PULSE AMPLITUDE MODULATION (PAM)

19

Hình 2-20. Hình thành mã vi phân 1-bit

Bộ tạo mã Dibit:

- Để tạo mã Dibit, cần đặt chuyển mạch S2/MODE ở vị trí Dibit (2). Sơ

đồ tạo mã Dibit có lỗi ra I và Q, xây dựng trên các vi mạch U10A,B và

U11A (Hình PL2-2).

- Tín hiệu I được tạo nhờ 2 trigger D mắc nối tiếp (U10A,B). Trigger

U10A được điều khiển bởi nhịp CKI còn trigger U10B - bằng nhịp CKQ.

Lối ra I sẽ có các mức tương ứng với bit thứ nhất của Dibit với độ dài bằng

2 khoảng bit (Hình 2-21).

Hình 2-21. Hình thành mã Dibit

Bộ tạo mã Dibit vi phân:

- Trong hệ điều chế QPSK vi phân, pha của các sóng sin mang có các giá trị

00, 900, 1800 và 2700, được xác định như hàm của tài liệu Dibit (xem

Hình 2-14).

- Bộ tạo mã Dibit vi phân lấy các tín hiệu I và Q ở bộ tạo mã Dibit (đã trình

bày ở phần trên) để tạo mã Dibit vi phân với các lối ra DIFF.I và DIFF.Q.

PULSE AMPLITUDE MODULATION (PAM)

20

- Để tạo mã Dibit vi phân, cần đặt chuyển mạch S2/MODE ở vị trí Dibit

(2).

- Tín hiệu I và Q được đưa vào hai bộ mã vi phân 1-bit để hình thành tín hiệu

ra:

- Tín hiệu DIFF.I hình thành trên bộ so sánh U8A, trigger D làm trễ

U2B (Hình PL2-2)

- Tín hiệu DIFF.Q hình thành trên bộ so sánh U8B, trigger D làm trễ

U2A.

- Trong Bảng 2-4 cho các trạng thái mã ra I&Q, DIFF.I và DIFF.Q ứng với

mã Dibit thứ (n) và (n+1).

Bảng 2-4

Bit thứ (n) Bit thứ (n) Bit thứ (n+1)

DIFF.I DIFF.Q I Q DIFF.I DIFF.Q

0 0 0 0

0 0 0 1 1 0

1 1 1 1

1 0 0 1

0 0 0 1

0 1 0 1 0 0

1 1 1 0

1 0 1 1

0 0 0 1

1 1 0 1 1 0

1 1 0 0

1 0 1 0

0 0 1 0

1 0 0 1 1 1

1 1 0 1

1 0 0 0

Bộ tạo mã Tribit:

- Để tạo mã Tribit, cần đặt chuyển mạch S2/MODE ở vị trí Tribit (3). Sơ

đồ tạo mã Tribit có lối ra I, Q và C, xây dựng trên các vi mạch U10A,B và

U11A,B và U12B (Hình PL2-2).

- Tín hiệu I được tạo nhờ 2 trigger D mắc nối tiếp (U10A,B).

Trigger U10A được điều khiển bởi nhịp CKI còn trigger U10B- bằng

nhịp CKC. Lối ra I sẽ có các mức tương ứng với bit thứ nhất của Tribit với độ

dài bằng 3 khoảng bit (Hình 2-22).

- Tín hiệu Q được tạo nhờ 2 trigger D mắc nối tiếp (U11A,B).

Trigger U11A được điều khiển bởi nhịp CKQ còn trigger U11B- bằng

nhịp CKC. Lối ra Q sẽ có các mức tương ứng với bit thứ hai của Tribit với độ

dài bằng 3 khoảng bit. (Hình 2-22).

- Tín hiệu C được tạo nhờ 2 trigger D - U12B được điều khiển bởi

nhịp CKC. Lối ra C sẽ có các mức tương ứng với bit thứ ba của Tribit với độ

dài bằng 3 khoảng bit. (Hình 2-22).

PULSE AMPLITUDE MODULATION (PAM)

21

Hình 2-22. Hình thành mã Tribit

Máy phát sóng mang (Carrier Generator):

Bộ tạo sóng mang dạng sin sử dụng cho điều chế là các bộ lọc thông thấp xây

dựng trên U14 & U15 (Hình PL2-3). Sơ đồ biến đổi các sóng vuông 1200Hz và

2400Hz từ máy phát nhịp thành sóng son. Sơ đồ dịch pha ( Phase Adj.) nhờ các

mạch RC (P1-C7, P3-C14, P5-C20) mắc ở lối vào các tầng khuếch đại tương

ứng cho phép hiệu chỉnh pha của sóng mang.

Nhánh 1200Hz có hai bộ dịch pha được hiệu chỉnh lệch nhau 900 cho tín hiệu

sin ra 1200Hz-0 và 1200Hz-90.

Bộ điều chế ASK, FSK, PSK, QPSK, QAM:

Các phương pháp điều chế được khảo sát tiến hành trên sơ đồ điều chế cân

bằng U17 và U18 (Hình PL2-4) có bổ sung bộ cộng U19B và bộ suy giảm 6dB-

R49, R53, Q1.

Điều chế ASK:

- Chỉ sử dụng 1 trong hai bộ điều chế cân bằng U17 và U18.

- Khi đưa mã tài liệu tới lối vào DATA và sóng mang tới lối vào CARRIER, bộ

điều chế cân bằng sẽ thực hiện nhân hai tín hiệu này.

- Nếu điều chỉnh biến trở cân bằng sóng mang CARRIER NULL sao cho hệ

mất cân bằng, lối vào DATA sẽ tác động điều khiển đóng ngắt khoá cho tín

hiệu sóng mang truyền qua. Sơ đồ trong chế độ này hoạt động theo kiểu

điều chế ASK.

Điều chế FSK:

- Chỉ sử dụng cả hai bộ điều chế cân bằng U17 và U18.

- Mã tài liệu được đưa tới lối vào DATA cho cả hai bộ điều chế.

PULSE AMPLITUDE MODULATION (PAM)

22

- Sóng mang 1200Hz cấp cho lối vào CARRIER của U17, còn sóng 2400Hz

– cho lối vào CARRIER của U18.

- Mỗi bộ điều chế cân bằng sẽ thực hiện hai tín hiệu DATA và CARRIER ở

các lối vào tương ứng.

- Khi điều chỉnh biến trở cân bằng sóng mang CARRIER NULL sao cho U17

cho tín hiệu ra 1200Hz ứng với DATA bit = 0, còn U18 cho tín hiệu ra

2400Hz ứng với DATA bit = 1.

- Các tín hiệu này được lấy tổng trên U19B và cho tín hiệu FSK ở lối ra OUT.

Điều chế BPSK:

- Chỉ sử dụng 1 trong hai bộ điều chế cân bằng U17 và U18.

- Khi đưa mã tài liệu tới lối vào DATA và sóng mang tới lối vào CARRIER, bộ

điều chế cân bằng sẽ thực hiện nhân hai tín hiệu này.

- Nếu điều chỉnh biến trở cân bằng sóng mang CARRIER NULL sao cho hệ

cân bằng, lối vào DATA sẽ tác động điều khiển pha cho tín hiệu sóng mang

truyền qua. Sơ đồ trong chế độ này hoạt động theo kiểu điều chế BPSK.

- Nếu cấp tín hiệu dạng vi phân 1-bit, tài liệu điều chế sẽ là BPSK vi phân (D-

BPSK).

Điều chế QPSK:

- Trong kiểu điều chế QPSK, các sóng mang lệch nhau 1200Hz-0 và

1200Hz-90 từ máy phát sóng mang được đưa tới lối vào CARRIER của

hai bộ điều chế cân bằng. Tín hiệu Dibit I và Q từ bộ tạo mã Dibit được

cấp cho các lối vào DATA của sơ đồ điều chế.

- Bộ điều chế cân bằng sẽ cấp sóng ra trực tiếp nếu DATA bit = 1 và cấp

sóng ra đảo pha nếu DATA bit = 0. Bộ lấy tổng sẽ hình thành tín hiệu

1200Hz với 4 pha lệch nhau 900 (Hình 2-7).

- Khi sử dụng tín hiệu I & Q làm mã tài liệu DATA, sơ đồ là QPSK tuyệt đối.

Còn khi sử dụng mã DIFF.I và DIFF.Q – sơ đồ là QPSK vi phân (D-

QPSK).

Điều chế QAM:

Điều chế QAM có thể xem như QPSK có biên độ nhận hai giá trị khác nhau. Khi

đó khoảng điều chế phụ thuộc trạng thái Tribit I, Q và C. Hai giá trị I và Q xác

định pha tín hiệu ra giống như QPSK. Tín hiệu C sử dụng điều chỉnh bộ suy giảm

6dB (Q1) để thay đổi biên độ sóng ra.

2.2.2.2. Bộ Giải điều chế ASK, FSK, PSK, QPSK.

Sơ đồ khối thí nghiệm TC-946D để giải điều chế ASK, FSK, PSK, QPSK

được trình bày trên Hình 2-23. Sơ đồ nguyên lý cho trong phần phụ lục (Hình OL2-

5Pl2-8).

PULSE AMPLITUDE MODULATION (PAM)

23

Hình 2-23. Khối giải điều chế TC-946D.

1. Bộ giải điều chế ASK

Bộ giải điều chế ASK là tập hợp các sơ đồ (Hình 2-2) sau:

Bộ thu tín hiệu ASK trong mảng DEMODULATORS / TC-946D (Hình PL2-5).

Bộ lọc thông thấp (tần số cắt ở 1200Hz) trên U7-U8 (Hình PL2-6) và bộ hình

thành xung trên U9 và EX-OR – U10 trong mảng DECODER & CLOCK

RECOVERY / TC-946D.

Dạng tín hiệu ra như trên Hình 2-2.

2. Bộ giải điều chế FSK

Bộ giải điều chế FSK là tập hợp các sơ đồ tương ứng với Hình 2-4 như sau:

- Bộ thu tín hiệu FSK (U2-PLL) trong mảng DEMODULATORS / TC-

946D (Hình PL2-5).

- Bộ lọc thông thấp (tần số cắt ở 1200Hz) trên U7-U8 (Hình PL2-6) và bộ

hình thành xung trên U9 và EX-OR – U10 trong mảng DECODER &

CLOCK RECOVERY / TC-946D.

3. Bộ giải điều chế BPSK

Bộ giải điều chế BPSK là tập hợp các sơ đồ tương ứng với Hình 2-6 như sau:

PULSE AMPLITUDE MODULATION (PAM)

24

Bộ thu tín hiệu PSK/QPSK (U3 và U4) trong mảng DEMODULATORS / TC-

946D (Hình PL2-5).

Bộ tái lập sóng mang (CARRIER RECOVERY) bao gồm:

- Các sơ đồ lấy bình phương sử dụng bộ nhân U5 và U6 cho lối ra SQR4

(Hình PL2-5).

- Vòng giữ pha PLL (U15) phát lại tín hiệu vuông góc. Chuyển mạch S2 ở

vị trí QPSK cho phép chọn tần số trung tâm của PLL ứng với lối ra nhân bốn

của 2 sơ đồ bình phương.

- Bộ dịch pha (U4, P4-C28).

- Các sơ đồ chia 2 trên U2B, U2A và U5A. Các tín hiệu sóng mang tái lập lối

ra lệch nhau 900 lấy ở 0 và 90. Các tín hiệu này được đưa điều khiển

khoá U4 ở sơ đồ DEMODULATORS.

Bộ lọc thông thấp (tần số cắt ở 1200Hz) trên U7-U8 (Hình PL2-6) và bộ hình

thành xung trên U9 và EX-OR – U10 trong mảng DECODER & CLOCK

RECOVERY / TC-946D.

Tài liệu hình thành ở lối ra U4 (I và Q) tương ứng với Dibit.

4. Bộ giải điều chế QPSK

Bộ giải điều chế QPSK là tập hợp các sơ đồ tương ứng với Hình 2-9 như sau:

Bộ thu tín hiệu PSK/QPSK (U3 và U4) trong mảng DEMODULATORS / TC-

946D (Hình PL2-5).

Bộ tái lập sóng mang (CARRIER RECOVERY) bao gồm:

- Các sơ đồ lấy bình phương sử dụng bộ nhân U5 và U6 cho lối ra SQR4

(Hình PL2-5).

- Vòng giữ pha PLL (U15) phát lại tín hiệu vuông góc. Chuyển mạch S2 ở

vị trí QPSK cho phép chọn tần số trung tâm của PLL ứng với lối ra nhân bốn

của 2 sơ đồ bình phương.

- Bộ dịch pha (U4, P4-C28).

- Các sơ đồ chia 2 trên U2B, U2A và U5A. Các tín hiệu sóng mang tái lập lối

ra lệch nhau 900 lấy ở 0 và 90. Các tín hiệu này được đưa điều khiển

khoá U4 ở sơ đồ DEMODULATORS.

Bộ lọc thông thấp (tần số cắt ở 1200Hz) trên U7-U8 (Hình PL2-6) và bộ hình

thành xung trên U9 và EX-OR – U10 trong mảng DECODER & CLOCK

RECOVERY / TC-946D.

Tài liệu hình thành ở lối ra U4 (I và Q) tương ứng với Dibit.

5. Bộ giải mã tài liệu

Để khôi phục lại tài liệu NRZ, tín hiệu lối ra từ các sơ đồ giải điều chế như trình

bày ở phần trên cần được giải mã.

Bộ giải mã (DECODER & CLOCH RECOVERY) chứa các mảng sơ đồ:

PULSE AMPLITUDE MODULATION (PAM)

25

Bộ tái lập xung nhịp tài liệu (PLL & TIMING)

Bộ giải mã Manchester (MANCHESTER DECODER)

Bộ giải mã 1-bit vi phân (DIFFERENTIAL BIT DECODER)

Bộ giải mã Dibit vi phân (DIFFERENTIAL DIBIT DECODER)

Bộ giải mã Dibit (BIT COMBINER)

Bộ tái lập xung nhịp tài liệu (PLL & TIMING):

- Sơ đồ tái lập xung nhịp được xây dựng theo sơ đồ khối Hình 2-15, bao gồm

bộ trễ thời gian R88-C30 và cổng EX-OR để tạo xung có phổ tần số gấp

đôi tín hiệu tài liệu. Vòng giữ pha PLL(U16 – Hình PL2-7) sẽ phát xung CK1

và CK 1 có tần số bằng xung nhịp truyền. Bộ chia 2 trên U17A tạo xung

CK2 có chu kỳ gấp đôi CK1.

- Chuyển mạch S1 cho phép xác lập tần số chuẩn của vòng giữ pha tương

ứng với chế độ giải mã Manchester hoặc BPSK hoặc QPSK.

Bộ giải mã Manchester (MANCHESTER DECODER):

- Giải mã Manchester được thực hiện bằng cách lấy mẫu tín hiệu giải điều

chế ở nửa đầu của khoảng bit. Bộ giải mã gồm Trigger U19 (Hình PL 2-

7) ghi tài liệu mã theo nhịp CK2. Tín hiệu từ các trigger U19 qua sơ đồ

EX-OR U20D và đơn hài trên U23B tạo các xung hẹp mỗi khi có sự thay

đổi từ 0 -> 1 hoặc ngược lại của tài liệu mã. Các xung này đồng bộ với

nhịp CK1 ở U21A để tạo tị ra có mặt dương ứng với nửa đầu của khoảng

bit. Tín hiệu lấy mẫu này sẽ điều khiển U21B ghi nhận tín hiệu mã lối vào để

tái lập mã NRZ từ mã Manchester.

- Giản đồ thời gian của sơ đồ giải mã Manchester cho trên Hình 2-24.

Hình 2-24. Giản đồ thồi gian của sơ đồ giải mã Manchester.

Bộ giải mã 1-bit vi phân (DIFFERENTIAL BIT DECODER):

- Giải mã vi phân 1-bit được thực hiện bằng cách so sánh tín hiệu mã trực tiếp

với tín hiệu làm trễ. Nếu các tín hiệu này khác nhau, nghĩa là tồn tại Data

bit = 1, còn nếu chúng giống nhau – Data bit = 0.

PULSE AMPLITUDE MODULATION (PAM)

26

- Trên sơ đồ PL2-7, U22A ghi tài liệu mã, còn U22B ghi tài liệu mã được làm

trễ theo cùng nhịp CK 1 . Trạng thái ra của các trigger này được so sánh

trên EX-OR U20C. Trigger U23A sử dụng để đồng bộ lại tài liệu với

nhịp CK1.

Bộ giải mã Dibit (BIT COMBINER):

- Bộ giải mã Dibit là bộ ghi dịch U27 (Hình PL2-8). Các tín hiệu I và Q được

nạp vào bộ ghi qua các lối vào song song C và D theo nhịp đếm của chu kỳ

Dibit – CK2. Số liệu được đọc theo chu kỳ xung nhịp tái lập CK1. Lối ra

OUTPUT lấy ở lối song song QD.

Bộ giải mã Dibit vi phân (DIFFERENTIAL DIBIT DECODER):

- Bộ giải mã Dibit vi phân nhận các tín hiệu I vi phân và Q vi phân từ bộ điều

chế để phát lại hai tín hiệu I và Q dạng Dibit.

- Sơ đồ xây dựng trên các vi mạch U24, U25, U26, U18C,D (Hình PL2-8).

Trạng thái tín hiệu ra I và Q tuỳ thuộc trạng thái của hai cặp mã cuối cùng

của Dibit vi phân lối vào trong khoảng 2 bit.

- Trong Bảng 2-5 cho các trạng thái ứng với mã Dibit vi phân thứ (n) và

(n+1).

Bảng 2-5

Bít thứ (n) Bit thứ (n+1) Bit thứ n

DIFF.I DIFF.Q DIFF.I DIFF.Q I Q

0 0 0 0

0 0 0 1 1 0

1 1 1 1

1 0 0 1

0 0 0 1

0 1 0 1 0 0

1 1 1 0

1 0 1 1

0 0 0 1

1 1 0 1 1 0

1 1 0 0

1 0 1 0

0 0 1 0

1 0 0 1 1 1

1 1 0 1

1 0 0 0

2.3. Cấp nguồn và nối dây

Khối TC-946M và TC-946D sử dụng chốt nuôi chung 12V. Khi sử dụng cần

gắn khối TC-946M và TC-946D lên khung chính TCPS-900. Chú ý đưa khối

vào rãnh trên trước rồi mới đặt theo rãnh dưới.

Bộ nguồn chuẩn DC POWER SUPLY của thiết bị TCPS-900 cung cấp các

thế chuẩn +5V/2A, -5V/0.5A, 12V/2A, -12V/1A cố định.

PULSE AMPLITUDE MODULATION (PAM)

27

Khi thực tập, cần nối dây từ chốt ra cần thiết và chốt đất của nguồn TCPS-

900 tới trực tiếp sơ đồ.

Chú ý cắm đúng phân cực của nguồn và đồng hồ đo

2.4. Các bài thực hành

Nhiệm vụ:

Khảo sát nguyên tắc điều chế và giải điều chế tín hiệu số bằng các phương

pháp tương tự.

Các bước thực hiện:

2.4.1 Khảo sát các phần chức năng

2.4.1.1. Máy phát nhịp tài liệu (Data Sequence Generator)

1. Đặt các công tắc SW DIP-8 ở vị trí ứng với Bảng 2-7 (1 = ON, 0 = OFF)

Bảng 2-7

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

1 0 0 1 1 0 0 0 0 1 0 1 0 0 1 1 1 0 1 1 0 0 0 1

2. Sử dụng dao động ký quan sát tín hiệu tại chốt CK. Xác định tần số và vẽ lại

dạng tín hiệu.

3. Nhấn nút Start, sử dụng dao động ký quan sát tín hiệu tại lối Data của bộ

ghi dịch (Shift Register). Vẽ lại dạng xung NRZ cùng giản đồ thời gian với

xung CK ở trên.

4. Đặt chuyển mạch Mode ở vị trí Bit. Nhấn nút Start, quan sát và vẽ lại dạng

xung CKI, cùng giản đồ thời gian với xung CK và NRZ ở trên.

5. Đặt chuyển mạch Mode ở vị trí Dribit. Nhấn nút Start, quan sát và vẽ lại dạng

xung CKI, CKQ cùng giản đồ thời gian ở trên.

6. Đặt chuyển mạch Mode ở vị trí Tribit. Nhấn nút Start, quan sát và vẽ lại

dạng xung CKI, CKQ, CKC cùng giản đồ thời gian ở trên.

7. Thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8), quan sát

tín hiệu NRZ tương ứng ở lối ra Data của bộ ghi dịch.

2.4.1.2. Các sơ đồ tạo mã tài liệu

Bộ tạo mã Manchester:

1. Đặt các công tắc SW DIP-8 (Máy phát nhịp DATA SEQUENCE

GENERATOR) ở vị trí ứng với Bảng 2-8 (1 = ON, 0 = OFF).

Bảng 2-8

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

1 0 0 1 1 0 0 0 0 1 0 1 0 0 1 1 1 0 1 1 0 0 0 1

PULSE AMPLITUDE MODULATION (PAM)

28

Nối lối ra DATA của máy phát nhịp với lối vào DATA của bộ tạo mã ENCODING

(TC-946M).

2. Sử dụng dao động ký quan sát tín hiệu tại chốt CK. Xác định tần số và vẽ lại

dạng tín hiệu.

3. Nhấn nút Start, sử dụng dao động ký quan sát tín hiệu tại chốt DATA của

bộ ghi dịch (Shift Register). Vẽ lại dạng xung DATA (NRZ) cùng giản đồ thời

gian với xung CK ở trên.

4. Nối lối ra DATA (DATA SEQUENCE GENERATOR) với lối vào DATA của bộ

tạo mã (ENCODING).

5. Vẽ giản đồ xung cho các tín hiệu CK và tín hiệu MANCHESTER vào cùng

giản đồ thời gian ở trên.

6. Thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8), lặp lại

các bước thí nghiệm nêu trên

Bộ tạo mã 1-bit vi phân:

1. Đặt các công tắc SW DIP-8 (Máy phát nhịp DATA SEQUENCE

GENERATOR) ở vị trí ứng với Bảng 2-9 (1 = ON, 0 = OFF).

Bảng 2-9

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

1 0 0 1 1 0 0 0 0 1 0 1 0 0 1 1 1 0 1 1 0 0 0 1

Nối lối ra DATA của máy phát nhịp với lối vào DATA của bộ tạo mã ENCODING

(TC-946M).

2. Sử dụng dao động ký quan sát tín hiệu tại chốt CK. Xác định tần số và vẽ lại

dạng tín hiệu.

3. Nhấn nút Start, sử dụng dao động ký quan sát tín hiệu tại chốt DATA của

bộ ghi dịch (Shift Register). Vẽ lại dạng xung DATA (NRZ) cùng giản đồ thời

gian với xung CK ở trên.

4. Nối lối ra DATA (DATA SEQUENCE GENERATOR) với lối vào DATA của bộ

tạo mã (ENCODING).

5. Đặt chuyển mạch Mode ở vị trí Bit. Nhấn nút Start, quan sát và vẽ lại

dạng xung DIFF DATA cùng giản đồ thời gian xung CK và NRZ ở trên.

6. Thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8), lặp lại

các bước thí nghiệm nêu trên.

Bộ tạo mã Dibit:

1. Đặt các công tắc SW DIP-8 (Máy phát nhịp DATA SEQUENCE

GENERATOR) ở vị trí ứng với Bảng 2-10 (1 = ON, 0 = OFF).

PULSE AMPLITUDE MODULATION (PAM)

29

Bảng 2-10

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

1 0 0 1 1 0 0 0 0 1 0 1 0 0 1 1 1 0 1 1 0 0 0 1

Nối lối ra DATA của máy phát nhịp với lối vào DATA của bộ tạo mã ENCODING

(TC-946M).

2. Sử dụng dao động ký quan sát tín hiệu tại chốt CK. Xác định tần số và vẽ lại

dạng tín hiệu.

3. Nhấn nút Start, sử dụng dao động ký quan sát tín hiệu tại chốt DATA của

bộ ghi dịch (Shift Register). Vẽ lại dạng xung DATA (NRZ) cùng giản đồ thời

gian với xung CK ở trên.

4. Nối lối ra DATA (DATA SEQUENCE GENERATOR) với lối vào DATA của bộ

tạo mã (ENCODING).

5. Đặt chuyển mạch Mode ở vị trí Dibit. Nhấn nút Start, quan sát và vẽ lại

dạng xung I, Q vào cùng giản đồ thời gian ở trên.

6. Thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8), lặp lại

các bước thí nghiệm nêu trên.

Bộ tạo mã Dibit vi phân:

1. Đặt các công tắc SW DIP-8 (Máy phát nhịp DATA SEQUENCE

GENERATOR) ở vị trí ứng với Bảng 2-11 (1 = ON, 0 = OFF).

Bảng 2-11

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

1 0 0 1 1 0 0 0 0 1 0 1 0 0 1 1 1 0 1 1 0 0 0 1

Nối lối ra DATA của máy phát nhịp với lối vào DATA của bộ tạo mã

ENCODING (TC-946M).

2. Sử dụng dao động ký quan sát tín hiệu tại chốt CK. Xác định tần số và vẽ lại

dạng tín hiệu.

3. Nhấn nút Start, sử dụng dao động ký quan sát tín hiệu tại chốt DATA của

bộ ghi dịch (Shift Register). Vẽ lại dạng xung DATA (NRZ) cùng giản đồ thời

gian với xung CK ở trên.

4. Nối lối ra DATA (DATA SEQUENCE GENERATOR) với lối vào DATA của bộ

tạo mã (ENCODING).

5. Đặt chuyển mạch Mode ở vị trí Bit. Nhấn nút Start, quan sát và vẽ lại dạng

xung DIFF DATA cùng giản đồ thời gian ở trên.

6. Thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8), lặp lại

các bước thí nghiệm nêu trên

PULSE AMPLITUDE MODULATION (PAM)

30

Bộ tạo mã Tribit:

1. Đặt các công tắc SW DIP-8 (Máy phát nhịp DATA SEQUENCE

GENERATOR) ở vị trí ứng với Bảng 2-12 (1 = ON, 0 = OFF).

Bảng 2-12

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

1 0 0 1 1 0 0 0 0 1 0 1 0 0 1 1 1 0 1 1 0 0 0 1

Nối lối ra DATA của máy phát nhịp với lối vào DATA của bộ tạo mã ENCODING

(TC-946M).

2. Sử dụng dao động ký quan sát tín hiệu tại chốt CK. Xác định tần số và vẽ lại

dạng tín hiệu.

3. Nhấn nút Start, sử dụng dao động ký quan sát tín hiệu tại chốt DATA của bộ

ghi dịch (Shift Register). Vẽ lại dạng xung DATA (NRZ) cùng giản đồ thời

gian với xung CK ở trên.

4. Nối lối ra DATA (DATA SEQUENCE GENERATOR) với lối vào DATA của bộ

tạo mã (ENCODING).

5. Đặt chuyển mạch Mode ở vị trí Bit. Nhấn nút Start, quan sát và vẽ lại

dạng xung DIFF DATA cùng giản đồ thời gian với xung CK và NRZ ở trên.

6. Thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8), lặp lại

các bước thí nghiệm nêu trên.

2.4.1.3. Bộ hình thành sóng mang (carrier generator)

1. Sử dụng dao động ký quan sát tín hiệu ở các chốt thử của bộ hình thành sóng

mang (CSRRIER GENERATOR)

- Tín hiệu vào 1200Hz, 2400Hz dạng vuông.

- Tín hiệu ra các bộ lọc FILTER.

- Tín hiệu ra các bộ chỉnh pha.

- Tín hiệu ra các bộ chỉnh biên độ.

2. Vặn các biến trở chỉnh pha và biên độ cho từng kênh, quan sát hiệu ứng trên

tín hiệu ra.

3. Vẽ lại giản đồ thời gian cho bộ hình thành sóng mang.

2.4.1.4. Bộ tái lập tín hiệu nhịp và giải mã tài liệu (DECODER & CLOCK

RECOVERY)

Bộ giải mã Manchester

1. Tạo mã Manchester như mục II.1.

Đặt các công tắc SW DIP-8 (Máy phát nhịp DATA SEQUENCE

GENERATOR/TC946D) ở vị trí ứng với Bảng 2-13 (1 = ON, 0 = OFF).

PULSE AMPLITUDE MODULATION (PAM)

31

Bảng 2-13

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

1 0 0 1 1 0 0 0 0 1 0 1 0 0 1 1 1 0 1 1 0 0 0 1

Nối lối ra DATA của máy phát nhịp với lối vào DATA của bộ tạo mã ENCODING

(TC-946M).

2. Nối lối ra MANCHESTER bộ tạo mã ENCODING/TC-946M với lối vào IN của

bộ giải mã DECODER & CLOCK RECOVERY / TC-946D. Đặt công tắc S1

chế độ tái lập ở vị trí MANC.

3. Nhấn nút START khởi động chuỗi nhịp. Sử dụng dao động ký quan sát tín

hiệu tại chốt CK1, CK 1 , CK2, CK 2 và lối ra giải mã MANC.OUT. So sánh

dạng tín hiệu DATA trước khi mã và MANC.OUT sau khi giải mã.

4. Nối trực tiếp lối ra DATA (mã NRZ) của máy phát nhịp với lối vào IN của bộ

giải mã DECODER & CLOCK RECOVERY / TC-946D.

5. Quan sát dạng tín hiệu. Nhận xét về tính ổn định của xung nhịp tái lập CK1,

CK2.

Giải thích tại sao khó xác lập nhịp tái lập.

6. Có thể thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8) và

lặp lại các bước thí nghiệm nêu trên.

Bộ giải mã 1-bit vi phân

1. Tạo mã 1-bit vi phân như mục II.2:

Đặt các công tắc SW DIP-8 (Máy phát nhịp DATA SEQUENCE

GENERATOR/TC-946D) ở vị trí ứng với Bảng 2-14 (1 = ON, 0 = OFF).

Bảng 2-14

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

1 0 0 1 1 0 0 0 0 1 0 1 0 0 1 1 1 0 1 1 0 0 0 1

Nối lối ra DATA của máy phát nhịp với lối vào DATA của bộ tạo mã ENCODING

(TC-946M). Chuyển mạch MODE đặt ở vị trí BIT.

2. Nối lối ra DIFF.DATA bộ tạo mã ENCODING/TC-946M với lối vào IN của

bộ giải mã DECODER & CLOCK RECOVERY / TC-946D. Đặt công tắc S1

chế độ tái lập ở vị trí BPSK.

3. Nhấn nút START khởi động chuỗi nhịp. Sử dụng dao động ký quan sát tín

hiệu tại chốt CK1, CK 1 , CK2, CK 2 và lối ra giải mã DBOUT. So sánh dạng

tín hiệu DATA trước khi mã và DBOUT sau khi giải mã.

4. Nối trực tiếp lối ra DATA (mã NRZ) của máy phát nhịp với lối vào IN của bộ

giải mã DECODER & CLOCK RECOVERY / TC-946D.

Quan sát dạng tín hiệu. Nhận xét về tính ổn định của xung nhịp tái lập CK1, CK2.

PULSE AMPLITUDE MODULATION (PAM)

32

Giải thích tại sao khó xác lập nhịp tái lập.

5. Thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8), lặp lại

các bước thí nghiệm nêu trên.

Bộ giải mã Dibit

1. Tạo mã Dibit như mục II.3:

Đặt các công tắc SW DIP-8 (Máy phát nhịp DATA SEQUENCE GENERATOR)

ở vị trí ứng với Bảng 2-15 (1 = ON, 0 = OFF).

Bảng 2-15

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

1 0 0 1 1 0 0 0 0 1 0 1 0 0 1 1 1 0 1 1 0 0 0 1

Nối lối ra DATA của máy phát nhịp với lối vào DATA của bộ tạo mã ENCODING

(TC-946M). Chuyển mạch MODE đặt ở vị trí QPSK.

2. Nối lối ra I và Q bộ tạo mã ENCODING/TC-946M với lối vào I và Q của bộ

giải mã BIT COMBINER / TC-946D. Đặt công tắc S1 chế độ tái lập ở vị

trí MANC.

3. Nhấn nút START khởi động chuỗi nhịp. Sử dụng dao động ký quan sát tín

hiệu tại chốt CK1, CK 1 , CK2, CK 2 và lối ra giải mã MANC.OUT. So sánh

dạng tín hiệu DATA trước khi mã và MANC.OUT sau khi giải mã.

4. Nối trực tiếp lối ra DATA (mã NRZ) của máy phát nhịp với lối vào IN của bộ

giải mã DECODER & CLOCK RECOVERY / TC-946D.

Quan sát dạng tín hiệu. Nhận xét về tính ổn định của xung nhịp tái lập CK1, CK2.

Giải thích tại sao khó xác lập nhịp tái lập.

5. Có thể thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8) và

lặp lại các bước thí nghiệm nêu trên.

Bộ giải mã Dibit vi phân

1. Tạo mã 1-bit vi phân như mục II.4:

Đặt các công tắc SW DIP-8 (Máy phát nhịp DATA SEQUENCE GENERATOR) ở vị

trí ứng với Bảng 2-16 (1 = ON, 0 = OFF).

Bảng 2-16

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

1 0 0 1 1 0 0 0 0 1 0 1 0 0 1 1 1 0 1 1 0 0 0 1

Nối lối ra DATA của máy phát nhịp với lối vào DATA của bộ tạo mã ENCODING (TC-

946M). Chuyển mạch MODE đặt ở vị trí QPSK.

2. Nối lối ra DIFF.I và DIFF.Q của bộ tạo mã ENCODING/TC-946M với lối vào

IDIFF và QDIFF của bộ giải mã DECODER & CLOCK RECOVERY / TC-

PULSE AMPLITUDE MODULATION (PAM)

33

946D. Nối I và Q của bộ giải mã Dibit vi phân DIFFERENTIAL DIBIT

DECODER lối vào I và Q của bộ giải mã BIT COMBINER/TC-946D.

3. Nhấn nút START khởi động chuỗi nhịp. Sử dụng dao động ký quan sát tín

hiệu tại chốt DATA/Máy phát chuỗi tài liệu của TC-946M và MOUT/TC-

946D. So sánh dạng tín hiệu DATA trước khi mã và BCOUT sau khi giải mã

Dibit vi phân.

2.4.2 Điều chế & giải điều chế tương tự cho tín hiệu số

Trong phần thực hành với các khối TC-946M và TC-946D có thể tổ chức

nhiều mục thí nghiệm về truyền số liệu kiểu điều chế tương tự cho tín hiệu số. Dưới

đây được giới thiệu một số bài cơ bản.

2.4.2.1. Điều chế & giải điều chế ASK

Truyền tài liệu trực tiếp (hình 2-25)

1. Xác lập tài liệu DATA chi thí nghiệm:

- Đặt các công tắc SW DIP-8 (DATA SEQUENCE GENERATOR) theo

Bảng 2-17.

Bảng 2-17

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

- Nhấn nút START, kiểm tra và vẽ lại tín hiệu nhịp CK và DATA.

2. Nối lối ra DATA (DATA SEQUENCE GENERATOR) với lối vào DATA/

BALANCED MODULATOR 1 của sơ đồ MODULATORS / TC-946M.

3. Nối tín hiệu sóng mang 2400Hz (CARRIER GENERATOR) với lối vào

CARRIER/ BALANCED MODULATOR 1 của sơ đồ MODULATORS / TC-

946M.

Lối vào CI – điều khiển bộ suy giảm lối ra MODULATORS nối đất.

Điều chỉnh biên độ sóng mang 1 V. Chỉnh lệch pha sóng mang ở MIN.

4. Điều chỉnh biến trở CARRIER NULL của MODULATOR 1 cho mất cân bằng

và biên độ sóng mang thích hợp để nhận tín hiệu ASK. Vẽ dạng tín hiệu vào

giản đồ xung theo CK và DATA ở trên.

5. Nối lối ra MOUT của MODULATORS / TC-946M với lối vào ASK IN của

DEMODULATORS / TC-946D.

Nối lối ra ASK DATA OUT với lối vào FCIN1 bộ lọc và hình thành trong phần

DECODER & CLOCK RECOVERY/TC946D.

6. Quan sát dạng xung ra tại các điểm vào ra của bộ giải điều chế, bộ lọc và

hình thành. Điều chỉnh ngưỡng của COMPARATOR để nhận tín hiệu ra.

7. Vẽ lại dạng các tín hiệu trên vào giản đồ xung. So sánh DATA nhận tại

FCOUT1 với tài liệu DATA (NRZ) truyền.

PULSE AMPLITUDE MODULATION (PAM)

34

8. Thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8), lặp lại

các bước thí nghiệm nêu trên.

Hình 2-25. Điều chế & giải điều chế ASK: Truyền tài liệu trực tiếp.

PULSE AMPLITUDE MODULATION (PAM)

35

Truyền tài liệu kiểu mã Manchester (hình 2-26):

1. Giữ nguyên cấu hình nối ở trên và bổ sung bộ tạo mã và giải mã

Manchester vào sơ đồ:

- Nối lối ra DATA của máy phát tài liệu với lối vào DATA bộ tạo mã

ENCODING.

- Nối lối ra MANCHESTER với lối vào DATA của MODULATOR 1.

- Nối lối ra FCOUT1 của bộ lọc và hình thành /TC-946D với lối vào IN của

bộ giải mã DECODER & CLOCK RECOVERY.

- Tài liệu cuối lấy ở MANC.OUT

- Công tắc S1 đặt ở vị trí MANS

2. Chỉnh ngưỡng của bộ lọc và hình thành xung để nhận tín hiệu ra giải điều chế

giống tín hiệu vào (DATA). Quan sát và vẽ lại dạng tín hiệu vào ra của các

phần chức năng thiết bị. So sánh DATA nhận tại MANC.OUT với tài liệu DATA

(NRZ) truyền.

Truyền tài liệu kiểu mã 1-bit vi phân (hình 2-27):

1. Giữ nguyên cấu hình nối ở trên và bổ sung bộ tạo mã và giải mã 1-bit vào sơ

đồ:

- Công tắc S1 đặt ở vị trí BPSK.

- Nối lối ra DATA của máy phát tài liệu với lối vào DATA bộ tạo mã

ENCODING.

- Nối lối ra DIFF.DATA với lối vào DATA của MODULATOR 1.

- Nối lối ra FCOUT1 của bộ lọc và hình thành với lối vào IN của bộ giải mã

DECODER & CLOCK RECOVERY.

- Chuyển mạch MODE đặt ở BIT

- Tài liệu cuối lấy ở DBOUT.OUT

2. Quan sát và vẽ lại dạng tín hiệu vào ra của các phần chức năng thiết bị. So

sánh DATA nhận tại DBOUT với tài liệu DATA (NRZ) truyền.

PULSE AMPLITUDE MODULATION (PAM)

36

Hình 2-26. Điều chế & giải điều chế ASK: Truyền tài liệu kiểu Manchester.

PULSE AMPLITUDE MODULATION (PAM)

37

Hình 2-27. Điều chế & giải điều chế ASK: Truyền tài liệu kiểu vi phân 1bit

PULSE AMPLITUDE MODULATION (PAM)

38

2.4.2.2. Điều chế & giải điều chế FSK

Truyền tài liệu trực tiếp (hình 2-28)

2. Xác lập tài liệu DATA cho thí nghiệm:

- Đặt các công tắc SW DIP-8 (DATA SEQUENCE GENERATOR) theo

Bảng 2-18.

Bảng 2-18

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

- Nhấn nút START, kiểm tra và vẽ lại tín hiệu nhịp CK và DATA.

2. Nối lối ra DATA (DATA SEQUENCE GENERATOR) với lối vào DATA/

BALANCED MODULATOR 1 của sơ đồ MODULATORS / TC-946M. Nối lối

vào DATA của MODULATOR 1 với MODULATOR 2.

3. Nối tín hiệu sóng mang 1200Hz (CARRIER GENERATOR) với lối vào

CARRIER/ BALANCED MODULATOR 1 của sơ đồ MODULATORS / TC-

946M.

Nối tín hiệu sóng mang 2400Hz (CARRIER GENERATOR) với lối vào

CARRIER/ BALANCED MODULATOR 2 của sơ đồ MODULATORS / TC-946M.

Lối vào CI – điều khiển bộ suy giảm lối ra MODULATORS nối đất.

Điều chỉnh biên độ sóng mang 2 V. Chỉnh lệch pha sóng mang ở MIN.

4. Điều chỉnh biến trở CARRIER NULL của MODULATOR 1 - 2 và tinh chỉnh

pha sóng mang thích hợp để nhận tín hiệu FSK (xem Hình 2-4). Vẽ dạng tín

hiệu vào giản đồ xung theo CK và DATA ở trên.

5. Nối lối ra MOUT của MODULATORS / TC-946M với lối vào FSK IN của

DEMODULATORS / TC-946D.

Nối lối ra FSK DATA OUT với lối vào FCIN1 bộ lọc và hình thành trong phần

DECODER & CLOCK RECOVERY/TC946D.

6. Quan sát dạng xung ra tại các điểm vào ra của bộ giải điều chế, bộ lọc và

hình thành.

7. Vẽ lại dạng các tín hiệu trên vào giản đồ xung. So sánh DATA nhận tại

FCOUT1 với tài liệu DATA (NRZ) truyền.

8. Thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8), lặp lại

các bước thí nghiệm nêu trên.

Truyền tài liệu kiểu mã 1-bit vi phân (hình 2-29)

1. Giữ nguyên cấu hình nối ở trên và bổ sung bộ tạo mã và giải mã 1-bit vi phân

vào sơ đồ:

- Nối lối ra DATA của máy phát tài liệu với lối vào DATA bộ tạo mã

ENCODING.

- Nối lối ra DIFF.DATA với lối vào DATA của MODULATOR 1 - 2.

PULSE AMPLITUDE MODULATION (PAM)

39

- Nối lối ra FCOUT1 của bộ lọc và hình thành / TC-946D với lối vào IN bộ giải

mã DECODER & CLOCK RECOVERY.

- Chuyển mạch MODE đặt ở MANC.

- Tài liệu cuối lấy ở MANC.OUT.

2. Quan sát và vẽ lại dạng tín hiệu vào ra của các phần chức năng thiết bị. So

sánh DATA nhận tại MANC.OUT với tài liệu DATA (NRZ) truyền.

Truyền tài liệu kiểu mã 1-bit vi phân (hình 2-30)

1. Giữ nguyên cấu hình nối ở trên và bổ sung bộ tạo mã và giải mã 1-bit vi phân

vào sơ đồ:

- Nối lối ra DATA của máy phát tài liệu với lối vào DATA bộ tạo mã

ENCODING.

- Nối lối ra DIFF.DATA với lối vào DATA của MODULATOR 1 - 2.

- Nối lối ra FCOUT1 của bộ lọc và hình thành với lối vào IN bộ giải mã

DECODER & CLOCK RECOVERY.

- Chuyển mạch MODE/TC-946M đặt ở BIT. Chuyển mạch S1 và S2 /TC-

946D đặt ở BPSK.

- Tài liệu cuối lấy ở DBOUT.

2. Quan sát và vẽ lại dạng tín hiệu vào ra của các phần chức năng thiết bị. So

sánh DATA nhận tại DBOUT với tài liệu DATA (NRZ) truyền.

PULSE AMPLITUDE MODULATION (PAM)

40

Hình 2-28. Điều chế & giải điều chế FSK: Truyền tài trực tiếp.

PULSE AMPLITUDE MODULATION (PAM)

41

Hình 2-29. Điều chế & giải điều chế FSK: Truyền tài kiểu vi phân 1bit

PULSE AMPLITUDE MODULATION (PAM)

42

2.4.2.3. Điều chế và giải điều chế BPSK

Truyền tài liệu trực tiếp (hình 2-30)

1. Xác lập tài liệu DATA cho thí nghiệm:

- Đặt các công tắc SW DIP-8 (DATA SEQUENCE GENERATOR) theo Bảng

2-19.

Bảng 2-19

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0

- Nhấn nút START, kiểm tra và vẽ lại tín hiệu nhịp CK và DATA.

2. Nối lối ra DATA (DATA

SEQUENCE GENERATOR) với lối vào DATA/

BALANCED MODULATOR 1 của sơ đồ MODULATORS / TC-946M.

3. Nối tín hiệu sóng mang 2400Hz (CARRIER GENERATOR) với lối vào

CARRIER/ BALANCED MODULATOR 1 của sơ đồ MODULATORS / TC-

946M.

Lối vào CI – điều khiển bộ suy giảm lối ra MODULATORS nối đất.

Điều chỉnh biên độ sóng mang 2 V. Chỉnh lệch pha sóng mang ở MIN.

4. Điều chỉnh biến trở CARRIER NULL của MODULATOR 1 và tinh chỉnh pha

sóng mang thích hợp để nhận tín hiệu BPSK như Hình 2-5. Vẽ dạng tín hiệu

vào giản đồ xung theo CK và DATA ở trên.

5. Nối lối ra MOUT của MODULATORS / TC-946M với lối vào PSK/QPSK IN

của DEMODULATORS / TC-946D.

Nối lối ra bình phương SQR2 với lối vào PPL IN (CARRIER RECOVERY).

Công tắc S2 đặt ở BPSK.

Nối lối ra PA2 của bộ chia 2 với chốt điều khiển khoá 0 của PSK/QPSK

DEMODULATIONS/TC-946D.

Nối lối ra I với lối vào FCIN1 bộ lọc và hình thành trong phần DECODER &

CLOCK RECOVERY/TC946D.

Điều chỉnh ngưỡng bộ lọc và hình thành để nhận tín hiệu ra.

6. Quan sát dạng xung ra tại các điểm vào ra của bộ giải điều chế BPSK, bộ lọc

và hình thành.

7. Vẽ lại dạng các tín hiệu trên vào giản đồ xung. So sánh DATA nhận tại

FCOUT1 với tài liệu DATA (NRZ) truyền.

8. Thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8), lặp lại các

bước thí nghiệm nêu trên.

PULSE AMPLITUDE MODULATION (PAM)

43

Hình 2-30. Điều chế - giải điều chế BPSK

PULSE AMPLITUDE MODULATION (PAM)

44

Truyền tài liệu kiểu D-BPSK (Hình 2-31)

1. Giữ nguyên cấu hình nối ở trên và bổ sung tạo mã và giải mã 1-bit vi phân

vào sơ đồ:

- Nối lối ra DATA của máy phát tài liệu với lối vào DATA bộ tạo mã

ENCODING.

- Nối lối ra DIFF.DATA với lối vào DATA của MODULATOR 1.

- Nối lối ra FCOUT1 của bộ lọc và hình thành với lối vào IN bộ giải mã

DECODER & CLOCK RECOVERY.

- Chuyển mạch MODE/TC-946M đặt ở BIT. Chuyển mạch S1 và S2 /TC-

946D đặt ở BPSK.

- Tài liệu cuối lấy ở DBOUT.

2. Quan sát và vẽ lại dạng tín hiệu vào ra của các phần chức năng thiết bị. So

sánh DATA nhận tại DBOUT với tài liệu DATA (NRZ) truyền.

PULSE AMPLITUDE MODULATION (PAM)

45

Hình 2-31. Điều chế & giải điều chế BPSK vi phân

PULSE AMPLITUDE MODULATION (PAM)

46

2.4.2.4. Điều chế & giải điều chế QPSK (hình 2-34)

1. Xác lập tài liệu DATA cho thí nghiệm

- Đặt các công tắc SW DIP-8 (DATA SEQUENCE GENERATOR) theo Bảng

2-20.

Bảng 2-20

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0

- Nhấn nút START, kiểm tra và vẽ lại tín hiệu nhịp CK và DATA.

2. Nối lối ra DATA (DATA SEQUENCE GENERATOR) với lối vào DATA/

ENCODING/ TC-946M để nhận mã Dibit - I và Q.

Chuyển mạch MODE đặt ở DIBIT.

3. Nối lối ra I và Q tương ứng với lối vào CARRIER/BALANCED MODULATOR

1 và 2 của sơ đồ MODULATORS / TC-946M.

4. Điều chỉnh biên độ sóng mang ~ 1 V. Chỉnh biến trở pha để có các sóng

mang 1200Hz lệch pha nhau 900 như Hình 2-32.

Hình 2-32. Dạng sóng mang lệch pha 900

5. Nối tín hiệu sóng mang 1200Hz-0 và 1200Hz-90 (CARRIER

GENERATOR) với các lối vào CARRIER/BALANCED MODULATOR 1 và 2

của sơ đồ MODULATORS / TC-946M. Lối vào CI – điều khiển bộ suy giảm

lối ra MODULATORS nối đất.

6. Điều chỉnh biến trở CARRIER NULL của MODULATOR 1-2 và biên độ sóng

mang thích hợp để nhận tín hiệu QPSK. Vẽ dạng tín hiệu vào giản đồ xung

theo CK và DATA ở trên. (xem giản đồ mẫu Hình 2-33)

7. Nối lối ra MOUT của MODULATORS / TC-946M với lối vào PSK/QPSK IN

của DEMODULATORS / TC-946D.

- Nối lối ra của hai bộ bình phương SQR4 với lối vào PPL IN (CARRIER

RECOVERY).

- Nối lối ra 0 của bộ tái lập sóng mang với chốt điều khiển khoá 0 của

PSK/QPSK DEMODULATIONS/TC-946D.

PULSE AMPLITUDE MODULATION (PAM)

47

- Nối lối ra 90 của bộ tái lập sóng mang với chốt điều khiển khoá 90 của

PSK/QPSK DEMODULATIONS/TC-946D.

- Nối lối ra I/DEMODULATION với lối vào FCIN1 bộ lọc và hình thành trong

phần DECODER & CLOCK RECOVERY/TC946D.

- Nối lối ra Q/DEMODULATION với lối vào FCIN2 bộ lọc và hình thành trong

phần DECODER & CLOCK RECOVERY/TC946D.

- Nối lối ra FCOUT1 với lối vào I bộ giải mã Dibit ( Bit COMBINER) và với lối

vào IN.

- Nối lối ra FCOUT2 với lối vào Q bộ giải mã Dibit (Bit COMBINER).

- Chuyển mạch S1 và S2 đặt ở QPSK.

- Tài liệu ra lấy ở BCOUT.

Điều chỉnh ngưỡng bộ lọc và hình thành để nhận tín hiệu ra.

Hình 2-33. Tín hiệu QPSK.

8. Quan sát dạng xung ra tại các điểm vào-ra của bộ giải điều chế QPSK, bộ lọc

và hình thành.

9. Vẽ lại dạng các tín hiệu trên vào giản đồ xung. So sánh tín hiệu nhận tại

FCOUT với tài liệu DATA (NRZ) truyền.

10. Thay đổi cấu hình công tắc đặt số liệu cho bộ ghi dịch ( SW DIP-8), lặp lại thí

nghiệm.

2.4.2.5. Điều chế và giải điều chế D-QPSK (Hình 2-35)

1. Giữ nguyên cấu hình nối ở trên và bổ sung bộ tạo mã và giải mã Dibit vi phân

vào sơ đồ:

- Nối lối ra DATA của máy phát tài liệu với lối vào DATA bộ tạo mã

ENCODING.

- Nối lối ra DIFF.I với lối vào DATA của MODULATOR 1.

PULSE AMPLITUDE MODULATION (PAM)

48

- Nối lối ra DIFF.Q với lối vào DATA của MODULATOR 2.

- Nối lối ra FCOUT1 của bộ lọc và hình thành với lối vào IDIFF bộ giải mã

DECODER & CLOCK RECOVERY.

- Nối lối ra FCOUT2 của bộ lọc và hình thành với lối vào QDIFF bộ giải mã

DECODER & CLOCK RECOVERY.

- Nối lối ra I của bộ giải mã Dibit vi phân ( DIFF.DIBIT DECODER) với lối

vào I bộ giải mã Dibit (BIT COMBINER).

- Nối lối ra Q của bộ giải mã Dibit vi phân ( DIFF.DIBIT DECODER) với lối

vào Q bộ giải mã Dibit (BIT COMBINER).

- Chuyển mạch MODE đặt ở BIT.

- Tài liệu cuối lấy ở DBOUT

2. Quan sát và vẽ lại dạng tín hiệu vào ra của các phần chức năng thiết bị. So

sánh DATA nhận tại DBOUT với tài liệu DATA (NRZ) truyền.

PULSE AMPLITUDE MODULATION (PAM)

49

Hình 2-34. Điều chế - giải điều chế QPSK

PULSE AMPLITUDE MODULATION (PAM)

50

Hình 2-35. Điều chế - giải điều chế D-QPSK

PULSE AMPLITUDE MODULATION (PAM)

51

2.4.2.6. Điều chế QAM (hình 2-36)

1. Xác lập tài liệu DATA cho thí nghiệm.

- Đặt các công tắc SW DIP-8 (DATA SEQUENCE GENERATOR) theo Bảng

2-21.

Bảng 2-21

SW 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4

0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0

- Nhấn nút START, kiểm tra và vẽ lại tín hiệu nhịp CK và DATA.

2. Nối lối ra DATA (DATA SEQUENCE GENERATOR) với lối vào DATA/

ENCODING/ TC-946M để nhận mã Tribit – I, Q và C.

Chuyển mạch MODE đặt ở TRIBIT.

3. Nối lối ra I và Q tương ứng với lối vào CARRIER/BALANCED MODULATOR

1 và 2 của sơ đồ MODULATORS / TC-946M.

4. Nối lối ra C với các lối vào CI của bộ suy giảm / MODULATORS / TC-946M.

5. Nối tín hiệu sóng mang 1200Hz-0 và 1200Hz-90 (CARRIER

GENERATOR) với các lối vào CARRIER/ BALANCED MODULATOR 1 và 2

của sơ đồ MODULATORS / TC-946M.

6. Điều chỉnh CARRIER NULL của các bộ điều chế cân bằng để nhận tín hiệu

ra QAM tại MOUT.

7. Vẽ lại dạng các tín hiệu ra và giản đồ.

PULSE AMPLITUDE MODULATION (PAM)

52

Hình 2-36. Điều chế QAM

PULSE AMPLITUDE MODULATION (PAM)

53

Hình PL2-1: Timing & Pattern

PULSE AMPLITUDE MODULATION (PAM)

54

Hình PL2-1. TIMING & PATTERN

Hình PL2-2: Encoding

PULSE AMPLITUDE MODULATION (PAM)

55

Hình PL2-3: Carrier Generator

PULSE AMPLITUDE MODULATION (PAM)

56

Hình PL2-4: Modulators

PULSE AMPLITUDE MODULATION (PAM)

57

Hình PL2-5: Demodulators & Squarers

PULSE AMPLITUDE MODULATION (PAM)

58

Hình PL2-6: Low-Pass Filter & Voltage Comparator Carrier Recovery

PULSE AMPLITUDE MODULATION (PAM)

59

Hình PL2-7

PULSE AMPLITUDE MODULATION (PAM)

60

Hình PL2-8

PULSE AMPLITUDE MODULATION (PAM)

61

You might also like

- CÂU HỎI TRẮC NGHIỆM ÔN TẬP THÔNG TIN DI ĐỘNGDocument24 pagesCÂU HỎI TRẮC NGHIỆM ÔN TẬP THÔNG TIN DI ĐỘNGkiemsiw100% (1)

- Mã Hóa Truyền Và Giải Mã Tín Hiệu Âm Thanh Thời Gian Thực Trên MatlabDocument20 pagesMã Hóa Truyền Và Giải Mã Tín Hiệu Âm Thanh Thời Gian Thực Trên MatlabHieu VoNo ratings yet

- Bao Cao VTChuanDocument13 pagesBao Cao VTChuanphamchan2251987No ratings yet

- Điều chế MSK, 16-QAMDocument11 pagesĐiều chế MSK, 16-QAMHau NguyenNo ratings yet

- BTL Mô PhỏngDocument15 pagesBTL Mô PhỏngNguyễn Kiên100% (5)

- Tìm Hiểu Thiết Bị Viba Số RMD-904Document17 pagesTìm Hiểu Thiết Bị Viba Số RMD-904Trần Đinh Xuân ThànhNo ratings yet

- Điều Chế PSKDocument38 pagesĐiều Chế PSKĐài PhanNo ratings yet

- Slide bài giảng - Thầy Nguyễn Viết ĐảmDocument427 pagesSlide bài giảng - Thầy Nguyễn Viết ĐảmTuanEngland100% (1)

- Bài tập C2Document3 pagesBài tập C2D18CQVT01-N VO ANH DUYNo ratings yet

- CohaDocument26 pagesCohaminhduongNo ratings yet

- On Tap - Co So Ky Thuat Thong Tin Vo Tuyen - D14VTDocument8 pagesOn Tap - Co So Ky Thuat Thong Tin Vo Tuyen - D14VTNam TàoNo ratings yet

- (123doc) - Mo-Phong-He-Thong-8-Psk-Qua-Kenh-AwgnDocument14 pages(123doc) - Mo-Phong-He-Thong-8-Psk-Qua-Kenh-AwgnLiengirl CandyNo ratings yet

- BTL Mo PhongDocument18 pagesBTL Mo PhongHồ Đức DuyNo ratings yet

- On Tap CSKTTTVT He2019Document8 pagesOn Tap CSKTTTVT He2019Đạt Hoàng PhướcNo ratings yet

- Báo cáo Mô phỏngDocument8 pagesBáo cáo Mô phỏngNguyễn ThanhNo ratings yet

- BTL mô phỏngDocument17 pagesBTL mô phỏngVũ AnNo ratings yet

- Nhóm 8 - Thiết kế đường truyền vệ tinhDocument31 pagesNhóm 8 - Thiết kế đường truyền vệ tinhNguyễn ĐôngNo ratings yet

- Báo Cáo Môn Học Mô Phỏng Hệ Thống Truyền ThôngDocument17 pagesBáo Cáo Môn Học Mô Phỏng Hệ Thống Truyền ThôngNguyễn Khắc AnhNo ratings yet

- CHUONG4điều chế sốDocument29 pagesCHUONG4điều chế sốhương nguyễnNo ratings yet

- Báo cáo tìm hiểu RIPv1, RIPv2Document30 pagesBáo cáo tìm hiểu RIPv1, RIPv2electron1230No ratings yet

- File 1Document9 pagesFile 1Trần Xuân Quỳnh -D18VT345No ratings yet

- Nguyễn ĐÌnh Hải Nam-B20DCVT261-BTL mô phỏngDocument18 pagesNguyễn ĐÌnh Hải Nam-B20DCVT261-BTL mô phỏngTạ Xuân HùngNo ratings yet

- Phân tích biểu thức PSD của tín hiệu BPSK:: A - P A ± Tb A ϕ - sinc f.T R f RDocument6 pagesPhân tích biểu thức PSD của tín hiệu BPSK:: A - P A ± Tb A ϕ - sinc f.T R f Rthao luongNo ratings yet

- Bai 1 - Mo Phong BER Qua Kenh AWGNDocument6 pagesBai 1 - Mo Phong BER Qua Kenh AWGNDương HoàngNo ratings yet

- Các Kênh Vô Tuyến GSMDocument28 pagesCác Kênh Vô Tuyến GSMPhat PhamNo ratings yet

- Huong Dan Optisystem 6067Document20 pagesHuong Dan Optisystem 6067Dũng HoàngNo ratings yet

- MatlabDocument2 pagesMatlabzangheNo ratings yet

- Mo Phong Tin Hieu Va Qua Trinh Thu PhatDocument103 pagesMo Phong Tin Hieu Va Qua Trinh Thu PhatNguyễn NgọcNo ratings yet

- Ma Khoi Tuyen TinhDocument12 pagesMa Khoi Tuyen Tinhminhtuan_atkNo ratings yet

- Dieu Che QAMDocument9 pagesDieu Che QAMThắng Phan ĐạiNo ratings yet

- Thực Hành Buổi 2 Cơ Sở Kỹ Thuật Thông Tin Vô Tuyến.Document1 pageThực Hành Buổi 2 Cơ Sở Kỹ Thuật Thông Tin Vô Tuyến.Nguyễn Văn NhânNo ratings yet

- Đáp Án Mô Phỏng HTTT-D09VT1Document8 pagesĐáp Án Mô Phỏng HTTT-D09VT1Ta Duc HungNo ratings yet

- Nhóm 10. Hệ Thống Báo Hiệu Số 7Document17 pagesNhóm 10. Hệ Thống Báo Hiệu Số 7Ng MạnhNo ratings yet

- HỌC VIỆN CÔNG NGHỆ BƯU CHÍNH VIỄN THÔNGDocument19 pagesHỌC VIỆN CÔNG NGHỆ BƯU CHÍNH VIỄN THÔNGNguyễn ThanhNo ratings yet

- On Tap CSKTTTVT 2018 FianlDocument7 pagesOn Tap CSKTTTVT 2018 FianlNam TàoNo ratings yet

- Phu Luc EFO 1101 PDFDocument4 pagesPhu Luc EFO 1101 PDFAnonymous fdW3zKcYdiNo ratings yet

- Nguyên Lý Ho T Đ NG C A EDFADocument6 pagesNguyên Lý Ho T Đ NG C A EDFAPhạm QuangNo ratings yet

- Môn Cơ S Thông Tin QuangDocument34 pagesMôn Cơ S Thông Tin QuangHùng Nguyễn MạnhNo ratings yet

- Bai Tap Anten Truyen Song BKHN Co Loi GiaiDocument11 pagesBai Tap Anten Truyen Song BKHN Co Loi GiaiDân0% (1)

- FILE - 20201211 - 115302 - Ôn Thi T So NDocument11 pagesFILE - 20201211 - 115302 - Ôn Thi T So NChi NguyenNo ratings yet

- bai5 KỸ THUẬT GHÉP KÊNHDocument36 pagesbai5 KỸ THUẬT GHÉP KÊNHNhất JocelynNo ratings yet

- Câu 1Document9 pagesCâu 1Kudo KidNo ratings yet

- Trần Thị Tuyết Mai - B18DCVT278 -NLT2 -MPHTTT -Bài tậpDocument7 pagesTrần Thị Tuyết Mai - B18DCVT278 -NLT2 -MPHTTT -Bài tậpTrần Thị Tuyết Mai - B18DCVT278No ratings yet

- Công nghệ vô tuyến thế hệ mớiDocument79 pagesCông nghệ vô tuyến thế hệ mớiCopperNo ratings yet

- Mau Bao Cao TH Mo Phong AntenDocument6 pagesMau Bao Cao TH Mo Phong AntenNguyễn ThanhNo ratings yet

- ÔN TẬP MẠNG THẾ HỆ MỚI 1Document11 pagesÔN TẬP MẠNG THẾ HỆ MỚI 1Hoài PhúcNo ratings yet

- Baocao BTLThongtinquang 20191Document38 pagesBaocao BTLThongtinquang 20191Nguyễn Hoàng Hải100% (1)

- Ask FSK PSK QPSK Qam Modulation DemolationDocument64 pagesAsk FSK PSK QPSK Qam Modulation DemolationLiengirl CandyNo ratings yet

- Giáo trình thực hành hệ thống truyền thông - 704903Document41 pagesGiáo trình thực hành hệ thống truyền thông - 704903Ngo Tuan DuyNo ratings yet

- TIEULUANTRUYENSOLIEUDocument14 pagesTIEULUANTRUYENSOLIEUNGUYỄN LÊ BẢO DUYNo ratings yet

- báo cáo viễn thông 1Document19 pagesbáo cáo viễn thông 1Duy Tân NguyễnNo ratings yet

- Tieuluantruyensolieu Nhom11 Detai6Document14 pagesTieuluantruyensolieu Nhom11 Detai6NGUYỄN LÊ BẢO DUYNo ratings yet

- B TH C Hành Com 115Document9 pagesB TH C Hành Com 115Harry TùngNo ratings yet

- Dieu Che Va Giai Dieu Che FSK.Document12 pagesDieu Che Va Giai Dieu Che FSK.ngandtvtNo ratings yet

- 6. Điều chế QPSKDocument9 pages6. Điều chế QPSKAnhBốnNo ratings yet

- Báo Cáo KTHTVT Nhóm 10Document7 pagesBáo Cáo KTHTVT Nhóm 10Phùng AnNo ratings yet

- 8.1 BPSKDocument9 pages8.1 BPSKHeo Heo ÚNo ratings yet

- Điều chế GMSK trong GSMDocument4 pagesĐiều chế GMSK trong GSMthecanh_920% (1)

- 111Equation Chapter 1 Section 1 TRƯỜNG ĐẠI HỌC BÁCH KHOA HÀ Trường Điện - Điện TửDocument16 pages111Equation Chapter 1 Section 1 TRƯỜNG ĐẠI HỌC BÁCH KHOA HÀ Trường Điện - Điện Tửhuy2bitNo ratings yet

- Giai Dieu Che AMDocument11 pagesGiai Dieu Che AMHeo Heo ÚNo ratings yet

- Bai Giang Mang Cam BienDocument112 pagesBai Giang Mang Cam BienKhương RâuNo ratings yet

- Do An Canh Bao Ro Gas Dung MQ6Document20 pagesDo An Canh Bao Ro Gas Dung MQ6Kudo Shinichi0% (1)

- Mạch Còi Điện TửDocument50 pagesMạch Còi Điện Tửndt2110No ratings yet

- Mạch Còi Điện TửDocument50 pagesMạch Còi Điện Tửndt2110No ratings yet