Professional Documents

Culture Documents

Corrigé Type TD03: Exercice 01

Uploaded by

Salah Eddine AtitallahOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Corrigé Type TD03: Exercice 01

Uploaded by

Salah Eddine AtitallahCopyright:

Available Formats

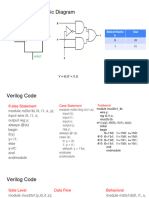

Corrigé type TD03

Exercice 01 :

Table de vérité d’un multiplexeur 2 à 1 : Expression logique pour le mux2x1 :

Sel S

0 .e0

1 .e1

S = e0 . sel + e1 . sel

Table de vérité d’un multiplexeur 4 à 1 : Expression logique pour le mux4x1 :

.sel1 .sel0 s

0 0 .e0

0 1 .e1

1 0 .e2

1 1 .e3

S = e0 . sel1 . sel0 + e1 . sel1 . sel0 + e2 . sel1 . sel0 + e3 . sel1 . sel0

Code VHDL pour le mux 2 à 1 :

Entity MUX2x1is

Port ( e0, e1, sel : in std_logic ;

S : out std_logic) ;

End MUX2x1 ;

Architecture BEHAV of MUX2x1 is

Begin

Process(sel)

Begin

If (sel =’0’) then

S <= e0;

Else

S <= e1;

End if; end process; end BEHAV;

Code VHDL pour le mux 4 à 1 :

Entity MUX4x1is

Port ( e0, e1, e2,e3, sel1,sel0 : in std_logic ;

S : out std_logic) ;

End MUX4x1 ;

Architecture BEHAV of MUX4x1 is

Sel <= sel1&sel0 ;

Signal sel : std_logic;

Begin

Process(sel )

Begin

Case sel is

When “00” => s<=e0;

When “01” => s<=e1;

When “10” => s<=e2;

When others => s<=e3;

End case; end process; end BEHAV;

Exercice 02 :

Table de vérité d’un additionneur complet :

Rin A B S Rout

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Expressions logiques des sorties : (+) représente le xor

S = Rin . (A .B + A. B) + Rin . (A .B + A. B) = Rin . (A (+) B) + Rin . (A (+) B) = Rin (+) A (+) B

Rout = Rin . (A (+) B) + A.B

Code VHDL FADD de type data flow :

Entity FADD is

Port(Rin, A,B: in std_logic;

S, Rout: out std_logic) ;

End FADD ;

Architecture DF of FADD is

Begin

S <= Rin xor A xor B;

Rout <= (Rin and (A xor B)) or (A and B);

End DF;

Code VHDL FADD de type comportemental :

Entity FADD is

Port(Rin, A,B: in std_logic;

S, Rout: out std_logic) ;

End FADD ;

Architecture DF of FADD is

Signal inp: std_logic_vector(2 downto 0);

Begin

Process(inp)

Begin

Case inp is

When “000” => S <= ‘0’, Rout <= ‘0’;

When “001” => S <= ‘1’, Rout <= ‘0’;

When “010” => S <= ‘1’, Rout <= ‘0’;

When “011” => S <= ‘0’, Rout <= ‘1’;

When “100” => S <= ‘1’, Rout <= ‘0’;

When “101” => S <= ‘0’, Rout <= ‘1’;

When “110” => S <= ‘0’, Rout <= ‘1’;

When others => S <= ‘1’, Rout <= ‘1’;

End case;

End process;

End DF;

You might also like

- VHDL ProgramsDocument49 pagesVHDL Programsapi-369623583% (12)

- Multiplexeur 4 Vers 1:: La Description en Langage VHDL AvecDocument3 pagesMultiplexeur 4 Vers 1:: La Description en Langage VHDL AvecbouchraNo ratings yet

- EE/CPE 428, CPE 528 Homework 1 Solutions: Exercise 1.Document7 pagesEE/CPE 428, CPE 528 Homework 1 Solutions: Exercise 1.Devaraj SubrmanayamNo ratings yet

- TugasLab1a - Ichsan Harun Wicaksono - 195060307111011Document16 pagesTugasLab1a - Ichsan Harun Wicaksono - 195060307111011Ichsan WicaksonoNo ratings yet

- VHDL Tutorial: Nand GatesDocument11 pagesVHDL Tutorial: Nand GatessikopikoNo ratings yet

- Combinational Logic Circuits: Prof. David Márquez ViloriaDocument16 pagesCombinational Logic Circuits: Prof. David Márquez ViloriaJose Mateo Aristizabal DiazNo ratings yet

- Mux DemuxDocument4 pagesMux DemuxVinay RaiNo ratings yet

- Prepa ExamDocument4 pagesPrepa ExamHAHANo ratings yet

- MATLAB Examples: Linear Block Codes: 1 The Galois Field F For Prime PDocument9 pagesMATLAB Examples: Linear Block Codes: 1 The Galois Field F For Prime PFarhaan BudalyNo ratings yet

- VHDL CodeDocument34 pagesVHDL CodeHimanshu Thakur100% (1)

- Cryptography Mid-Semester SolutionDocument6 pagesCryptography Mid-Semester Solutionkool joolNo ratings yet

- Introduction To VHDL: CSCE 496/896: Embedded SystemsDocument20 pagesIntroduction To VHDL: CSCE 496/896: Embedded Systemssageesht-1No ratings yet

- Unit 3: Combinational Circuit DesignDocument30 pagesUnit 3: Combinational Circuit DesignKarn AroraNo ratings yet

- EXOR Gate Using Concurrent Statements: RTL ViewDocument59 pagesEXOR Gate Using Concurrent Statements: RTL ViewSurbhit SinhaNo ratings yet

- VHDL Slides For Cstruct Mux & DecoderDocument30 pagesVHDL Slides For Cstruct Mux & DecoderLiron lNo ratings yet

- ELEC2041 Microprocessors and Interfacing Lectures 20: Floating Point Number Representation - IiDocument29 pagesELEC2041 Microprocessors and Interfacing Lectures 20: Floating Point Number Representation - IiRaj KumarNo ratings yet

- Corrigé TD2Document9 pagesCorrigé TD2All AhmeDciaNo ratings yet

- hw1 PDFDocument3 pageshw1 PDFDevaraj SubrmanayamNo ratings yet

- Mux DemuxDocument8 pagesMux DemuxAadesh LabdeNo ratings yet

- 4.4. Arithmetic CodingDocument30 pages4.4. Arithmetic CodingperhackerNo ratings yet

- Assignment 1Document74 pagesAssignment 1Rajesh PathakNo ratings yet

- CA PracticalDocument11 pagesCA PracticalBidhan BaraiNo ratings yet

- S1 Not (A Xor B) S2 Not D or (C and D) S S2 and (E Xor S1)Document11 pagesS1 Not (A Xor B) S2 Not D or (C and D) S S2 and (E Xor S1)oussama elkaissiNo ratings yet

- Lecture8 1 (CL Examples)Document5 pagesLecture8 1 (CL Examples)litoduterNo ratings yet

- VHDL Code MUX and DeMUX PDFDocument2 pagesVHDL Code MUX and DeMUX PDFAbdul RehmanNo ratings yet

- TP3-VHDL SolutionsDocument3 pagesTP3-VHDL SolutionsfalaNo ratings yet

- Experiment-1: Simulation Result For Half Adder and Full Adder CircuitDocument7 pagesExperiment-1: Simulation Result For Half Adder and Full Adder CircuitHimanshu Rajan jainNo ratings yet

- Intro To Python Programming NotesDocument29 pagesIntro To Python Programming NotesVineetha BheemarasettyNo ratings yet

- Expt 2 Mux 4 1Document3 pagesExpt 2 Mux 4 1Steven VazhappullyNo ratings yet

- Multiplexers in VHDL: Four-Bit Wide 2 To 1 MultiplexerDocument4 pagesMultiplexers in VHDL: Four-Bit Wide 2 To 1 Multiplexeranon_818776315No ratings yet

- Digital System DesignDocument10 pagesDigital System DesignGourav VashistNo ratings yet

- Multiplexer, Encoder and Decoder: Prepared By: Rakesh MahtoDocument14 pagesMultiplexer, Encoder and Decoder: Prepared By: Rakesh MahtoAngel JothiNo ratings yet

- ECE 223 Logic MinimizationDocument14 pagesECE 223 Logic Minimizationujjwal123456No ratings yet

- Unit I HDL DesignDocument81 pagesUnit I HDL DesignvinodNo ratings yet

- Cse 205: Digital Logic DesignDocument60 pagesCse 205: Digital Logic DesignIFTEKHAR E MAHBUB ZEEONNo ratings yet

- Digital Logic Design: VHDL Coding For Fpgas Unit 3Document20 pagesDigital Logic Design: VHDL Coding For Fpgas Unit 3Srinivas CherukuNo ratings yet

- Digital Assignment-4Document4 pagesDigital Assignment-4HAVILA REDDY D 19BCT0211No ratings yet

- Experiment No.1: A Binary To Gray ConverterDocument26 pagesExperiment No.1: A Binary To Gray ConverterVarun SharmaNo ratings yet

- Code VHDL Trascodeur 7 SegmentsDocument5 pagesCode VHDL Trascodeur 7 SegmentsBen Ahmed AbdelhamidNo ratings yet

- Design and Simulation of Logic Gates Using VHDLDocument26 pagesDesign and Simulation of Logic Gates Using VHDLSushanth BabuNo ratings yet

- VHDL Cheat SheetDocument2 pagesVHDL Cheat SheetCory Mayer100% (2)

- EncoderDocument10 pagesEncoderSiva Shankar0% (1)

- VerilogTutorial1 ECEDocument30 pagesVerilogTutorial1 ECECu LucNo ratings yet

- Verilog - Mux, Demux, Encoder, DecoderDocument9 pagesVerilog - Mux, Demux, Encoder, Decoderavinashmasani7No ratings yet

- Micro TPDocument7 pagesMicro TPsebastienNo ratings yet

- Numeric Solutions of ODEs in MapleDocument6 pagesNumeric Solutions of ODEs in MapleNasg KulNo ratings yet

- Haykin9 PDFDocument46 pagesHaykin9 PDFdhananjayan89100% (1)

- Experiment-3: Aim: Activity1 Truth TableDocument7 pagesExperiment-3: Aim: Activity1 Truth TableHimanshu Rajan jainNo ratings yet

- VHDL Program: Experiment: 1 Aim: To Write A VHDL Program For: I) 8 Bit ComparatorDocument6 pagesVHDL Program: Experiment: 1 Aim: To Write A VHDL Program For: I) 8 Bit ComparatorVidhya DsNo ratings yet

- Tarea DigitalesDocument14 pagesTarea DigitalesJhulian VillafuerteNo ratings yet

- Experiment-5: Aim: To Write VHDL Code For 4 To 1 MUX and Observe The Waveform and Synthesize The CodeDocument3 pagesExperiment-5: Aim: To Write VHDL Code For 4 To 1 MUX and Observe The Waveform and Synthesize The CodeYidnekachwe MekuriaNo ratings yet

- VHDL CodesDocument15 pagesVHDL Codesrksinha25No ratings yet

- Green's Function Estimates for Lattice Schrödinger Operators and Applications. (AM-158)From EverandGreen's Function Estimates for Lattice Schrödinger Operators and Applications. (AM-158)No ratings yet

- Digital Electronics For Engineering and Diploma CoursesFrom EverandDigital Electronics For Engineering and Diploma CoursesNo ratings yet

- Tables of the Function w (z)- e-z2 ? ex2 dx: Mathematical Tables Series, Vol. 27From EverandTables of the Function w (z)- e-z2 ? ex2 dx: Mathematical Tables Series, Vol. 27No ratings yet

- Differentiation (Calculus) Mathematics Question BankFrom EverandDifferentiation (Calculus) Mathematics Question BankRating: 4 out of 5 stars4/5 (1)

- Tables of Laguerre Polynomials and Functions: Mathematical Tables Series, Vol. 39From EverandTables of Laguerre Polynomials and Functions: Mathematical Tables Series, Vol. 39No ratings yet

- Hyperbolic Functions (Trigonometry) Mathematics E-Book For Public ExamsFrom EverandHyperbolic Functions (Trigonometry) Mathematics E-Book For Public ExamsNo ratings yet