Professional Documents

Culture Documents

Digital Logic Design Syllabus

Uploaded by

ollata kalanoOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Logic Design Syllabus

Uploaded by

ollata kalanoCopyright:

Available Formats

1

DIGITAL LOGIC DESIGN

(REC-301)

B.Tech 2nd Year (EC & CS Branch)

Mr. Navneet Pal

Assistant Professor

Electronics & Communication Department

Syllabus

Digital Logic Design (REC-301)

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

2

Unit Topic

Digital System And Binary Numbers: Number System and its arithmetic

, Signed binary numbers, Binary codes, Cyclic codes, Hamming Code,

the map method up to five variable, Don’t care conditions, POS

I

simplification, NAND and NOR implementation, Quine Mc-Clusky

method (Tabularmethod).

Combinational Logic: Combinational Circuits: Analysis Procedure,

Design procedure, Binary adder -subtractor, Decimal adder, Binary

II multiplier, Magnitude comparator, Multiplexers, Demultiplexers,

Decoders, Encoders.

Sequential Logic And Its Applications : Storage elements: latches & flip

flops, Characteristic Equations of Flip Flops, Flip Flop Conversion, Shift

III Registers, Ripple Counters, Synchronous Counters, Other Counters:

Johnson & Ring Counter.

Synchronous & Asynchronous Sequential Circuits Analysis of clocked

sequential circuits with state machine designing, State reduction and

assignments, Design procedure. Analysis procedure of Asynchronous

IV

sequential circuits, circuit with latches, design procedure, Reduction of

state and flow table, Race-free state assignment, Hazards

Memory & Programmable Logic Devices: Digital Logic Families: DTL,

DCTL, TTL, ECL & CMOS etc., Fan Out, Fan in, Noise Margin; RAM,

V ROM, PLA, PAL; Circuits of Logic Families, Interfacing of Digital

Logic Families, Circuit Implementation using ROM, PLA and PAL;

CPLD and FPGA.

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

3

UNIT-1

Content

Digital System And Binary Numbers:

Number System and its arithmetic

Signed binary numbers

Binary codes

Cyclic codes,

Hamming Code

The map method up to five variable

Don’t care conditions,

POS simplification,

NAND and NOR implementation,

Quine Mc-Clusky method (Tabularmethod).

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

4

Very Short Questions and Answers

Q1. What are weighed codes? Give examples.

Ans: The weighed codes are the codes that have assigned weights or values for each bit position. A code

in which each bit position has a certain numeric value assigned. Several such codes exist, such as 8-4-2-1,

7-4-2-1, 6-3-1 -1, Excess – 3 code.

Q2. What are cyclic codes?

Ans: An (n, k) linear code C is called a cyclic code if any cyclic shift of a codeword is another codeword.

That is,

Q3. What are self complementing codes?

Ans: A self-complementing code is the one in which the members of the number system complement on

themselves. This requires the following two conditions to be satisfied.

a). The complement of the number should be obtained from that number by replacing 1s with 0s and

0s with 1s.

b). The sum of the number and its complement should be equal to decimal 9. Example of a self-

complementing code is 2-4-2-1 code, Excess-3 code. , BCD code

Q4. What are BCD codes?

Ans:A special binary code used to directly represent the decimal characters. Each four bit value in BCD

represents a single decimal character.

Q5. What are alphanumeric codes?

Ans: A binary code used to represent the alphabets, numbers and punctuation marks as well as control

characters for controlling a printer or display. Eg – ASCII, EBCD

Q6. What is an Excess – 3 code?

Ans: A self complementing code used to represent BCD numbers. It is self complementing because the 1’s

complement is also the 9’s complement of the BCD number. It is widely used in BCD arithmetic circuits.

Examble: 1000 of 8421 = 1011 in Excess-3

Q7. What is a Gray code? (or) What is a unit distance code? Give an example

Ans:A reflective, unit distance code where only one bit position changes for each adjacent change in

value.

Q8 What is a reflective code?

Ans: A code is said to be reflective when code for 9 is complement for the code for 0, and so is for 8 and 1

codes, 7 and 2, 6 and 3, 5 and 4. Codes 2421, 5211, gray and excess-3 are reflective, whereas the 8421

code is not.

Q9. What is meant by parity bit?

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

5

Ans: Parity bit is an extra bit included with a binary message to make the number of 1’s either odd or

even. The message, including the parity bit is transmitted and then checked at the receiving and for

errors.

Q.10 Define duality property

Ans :Duality property states that every algebraic expression deducible from the postulates of Boolean

algebra remains valid if the operators and identity elements are interchanged. If the dual of an algebraic

expression is desired, we simply interchange OR and AND operators and replace 1’s by 0’s and 0’s by 1’s.

Q11. State De Morgan’s theorem.

Ans: De Morgan suggested two theorems that form important part of Boolean algebra.

1) The complement of a product is equal to the sum of the complements.

(AB)’ = A’ + B’

2) The complement of a sum term is equal to the product of the complements.

(A + B)’ = A’B’

Q12. What are called don’t care conditions?

Ans: In some logic circuits certain input conditions never occur, therefore the corresponding output never

appears. In such cases the output level is not defined, it can be either high or low. These output levels are

indicated by ‘X’ or‘d’ in the truth tables and are called don’t care conditions or incompletely specified

functions

Q13. Convert the given expression in canonical SOP form Y = AC + AB + BC

Ans: Y = AC + AB + BC

=AC(B + B’ ) + AB(C + C’ ) + (A + A’)BC

=ABC + ABC’ + AB’C + AB’C’ + ABC + ABC’ + ABC

=ABC + ABC’ +AB’C + AB’C’

Q14 Simplify F = ABC +AB’C + A’C + AB’

Ans:

F = ABC +AB’C + A’C + AB’

= AC(B+B’) + A’C + AB’

= AC + A’C + AB’

= C + AB’

Q15. Simplify the expression Z= AB + AB’(A’C’)’

Ans:

Z= AB + AB’(A’C’)’

= AB + AB’(A+C)

= AB + AB’ + AB’C

= A (B + B’ +B’C)

= A (1+B’C) = A

Q16. What are the different classification of binary codes?

Ans • Weighted codes

• Non - weighted codes

• Reflective codes

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

6

• Sequential codes

• Alphanumeric codes

• Error Detecting and correcting codes.

Q17. Why are NAND and NOR gates known as universal gates?

Ans: The NAND and NOR gates are known as universal gates, since any logic function can be implemented

using NAND or NOR gates.

Q18 Simplify the function Y = m(1,3,5,7)

Ans:

Y=C

Short and Long Type Questions

Q19.Explain or list out the advantages and disadvantages of K-map method?

Ans: The advantages of the K-map method are

i. It is a fast method for simplifying expression up to four variables.

ii. It gives a visual method of logic simplification.

iii. Prime implicants and essential prime implicants are identified fast.

iv. Suitable for both SOP and POS forms of reduction.

v. It is more suitable for class room teachings on logic simplification.

The disadvantages of the K-map method are

i. It is not suitable for computer reduction.

ii. K-maps are not suitable when the number of variables involved exceed four.

iii. Care must be taken to fill in every cell with the relevant entry, such as a 0, 1 (or) don’t care terms

Q20:What is Hamming code?

Ans: One of the most common error-correcting codes used in random-access memories was devised by R.

W. Hamming. In the Hamming code, k parity bits are added to an n-bit data word, forming a new word of

n + k bits. The bit positions are numbered in sequence from I to n + k. Those positions numbered as a

power of 2 are reserved for the parity bits. The remaining bits are the data bits. The code can be used

with words of any length.

Q21:c Explain Logic Gates.

Ans: Logic gates

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

7

Digital systems are said to be constructed by using logic gates. The basic gates are the AND, OR,

NOT gates. The basic operations are described below with the aid of tables in the following, called

truth tables.

AND gate

The AND gate is an electronic circuit that gives a high output (1) only if all its inputs are high. A dot

(.) is used to show the AND operation i.e. A.B. Bear in mind that this dot is sometimes omitted i.e.

AB

OR gate

The OR gate is an electronic circuit that gives a high output (1) if one or more of its inputs are

high. A plus (+) is used to show the OR operation.

NOT gate

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

8

The NOT gate is an electronic circuit that produces an inverted version of the input at its output. It

is also known as an inverter. If the input variable is A, the inverted output is known as NOT A. This

is also shown as A', or A with a bar over the top, as shown at the outputs.

Q22 Explain Principle of DUALITY.

Ans: PRINCIPLE OF DUALITY

According to this principle, For every valid expression in Boolean Algebra there exists an equally

valid dual expression. The dual expression can be obtained by following the following three steps:

i) Complement each 0 and 1 (Change the 0’s to 1’s and 1’s to 0’s)

ii) Replace each OR (+) sign by AND (.) and each AND (.) sign by OR (+)

iii) Leave NOTs unchanged.

The dual of i) X.1 = X is X + 1= X

ii) X + (YZ) is X . (Y+ Z)

iii) X.(Y+Z) is X+ (Y.Z)

Q23 Write Postulates of Boolean Algebra.

Ans: Basic Postulates of Boolean Algebra

a) A+ 0 = A

b) A+1 = 1, In fact 1 OR anything will be 1 as , as long as one of the inputs for the

OR operation is true the output will be true.

c) A. 0 = 0 , 0 AND anything will be 0 as all the inputs for the AND operation must

be true for the output to be true.

d) A.1 = A

e) A+ A’= 1, As if A is 0 , A’ will be 1 and if A is 1 ,A’ will be 0. 1 OR anything is 1

A+A’ , is Tautology as its value is always true.

f) A. A’ = 0, As either a or A’ will be 0 as 0 and anything is 0.

A.A’ is Fallacy as its value is always false.

g) A+A= A Proof: A+A= (A+A).1=(A+A)(A+A’)=A+A.A’=A

Idempotent Law

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

9

h) A. A = A Proof: A.A=A.A+0=A.A+A.A’=A(A+A’)= A.1=A

i) A.B=B.A Proof : By making the truth table and showing LHS=RHS

Commutative Law

j) A+B=B+A

k) (A+B)+C=A+(B+C) Proof: By truth table

Associative Law

l) (A.B).C=A.(B.C)

m) A+ AB = A , Proof: A+AB= A( 1+ B) = A. 1= A

Absorption Law

n) A.(A+B)=A

o) A.(B+C)=AB+AC Proof: (A+B).(A+C)=AA+AC+AB+BC

Distributive Law =A(1+A+C+B)+BC

p) A+BC=(A+B).(A+C) =A+BC

q) A’’ = A Involution

r) A+ A’B = A+B A(B+B’)+A’B = AB+AB’+ A’B+AB since AB+AB=AB

= A(B+B’)+B(A+A’) =A+B

Q24 Write De’ Morgen’s Law

Ans: De’Morgan’s Theorems

De’Morgan’s Theorems’ are useful in changing the forms of Boolean expressions . The two

theorems are:

i) The complement of the sum is equivalent to the product of individual

complements.

( A+B)’ = A’ . B’

ii) The complement of the product is equal to the sum of individual complements.

(A.B)’ = A’ + B’

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

10

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

11

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

12

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

13

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

14

Practice Questions

NUMBER SYSTEM & BOOLEAN ALGEBRA

1. Determine the decimal value of the fractional binary number 0.1011.

2. Perform 2’s complement subtraction of 010110-100101

3. Convert (53) 10 to EX-3 code.

4. Why digital circuits are more frequently constructed with NAND or NOR gates than

with AND & OR gates .

5. Convert 110011 into hexadecimal through octal.

6. What is variable mapping?

7. What is the feature of gray code?

8. Name the two canonical forms for Boolean algebra.

9. What is the BCD equivalent for the gray code 1110?

10. Obtain the minimum sop using QUINE- McCLUSKY method and verify using K-map

F=m0+m2+m4+m8+m9+m10+m11+m12+m13.

11. Reduce the following using tabulation method.

F=m2+m3+m4+m6+m7+m9+m11+m13.

12. Reduce the Boolean function using k-map technique and implement using gates

f (w, x, y,z)= ∑m (0,1,4,8,9,10) which has the don’t cares condition

d (w, x, y, z)= ∑ m (2,11).

13. Find the minimum SOP expression using K-map for the function

f= ∑m (7, 9, 10, 11, 12, 13, 14, 15) and realize the minimized function using only

NAND gates.

15. Expand the following Boolean expression to minterms and maxterms

A+BC’+ABD’+ABCD

16 .Prove the following (A+B) ((AC)’+C) (B’+AC)’=A’B.

Digital Logic Design (REC-301) By: Navneet Pal ( Assistant Professor)

You might also like

- SMAN52730 - Wiring Diagram B11RaDocument58 pagesSMAN52730 - Wiring Diagram B11RaJonathan Nuñez100% (1)

- Digital Electronics - 2 Marks With Answers PDFDocument40 pagesDigital Electronics - 2 Marks With Answers PDFMANJU C S100% (22)

- SAP Shortcut Keys PDFDocument5 pagesSAP Shortcut Keys PDFHarish KumarNo ratings yet

- Course Title of Computer Applications in Power SystemsDocument2 pagesCourse Title of Computer Applications in Power Systemsollata kalano100% (3)

- Huawei AI OverviewDocument69 pagesHuawei AI OverviewminatoonNo ratings yet

- Manufacturing Process PP BagsDocument17 pagesManufacturing Process PP Bagsollata kalano50% (2)

- Cs8351-Digital Principles and System DesignDocument4 pagesCs8351-Digital Principles and System DesignsathishNo ratings yet

- DPSD 2 MarksDocument19 pagesDPSD 2 MarksKavya DharshiniNo ratings yet

- 2 QB104321Document4 pages2 QB104321DevisriNo ratings yet

- Digital Principles UNIT 1 FinalDocument86 pagesDigital Principles UNIT 1 FinalSathish Kumar0% (1)

- Digital Principle and System DesignDocument26 pagesDigital Principle and System Designainugiri100% (4)

- Digital Principels and System DesignDocument53 pagesDigital Principels and System Designnofeelingrahul100% (1)

- DPSD 2marksDocument17 pagesDPSD 2marksToni GonzalezNo ratings yet

- Common To E&C, EI&C, CS & IS: Department of Technical Education Subject: Digital ElectronicsDocument9 pagesCommon To E&C, EI&C, CS & IS: Department of Technical Education Subject: Digital ElectronicsVikram RaoNo ratings yet

- Cse1003 Digital-logic-And-Design Eth 1.1 47 Cse1003Document8 pagesCse1003 Digital-logic-And-Design Eth 1.1 47 Cse1003Shiva Charan0% (1)

- Latha Mathavan Engineering College Latha Madhavan Nagar, Kidaripatti Madurai - 625301Document160 pagesLatha Mathavan Engineering College Latha Madhavan Nagar, Kidaripatti Madurai - 625301priya dharshiniNo ratings yet

- Allama Iqbal Open University, Islamabad Warning: (Department of Computer Science)Document3 pagesAllama Iqbal Open University, Islamabad Warning: (Department of Computer Science)Kashif ImranNo ratings yet

- Digital Electronics and Microcontroller Applications Winter 2019 Answer PaperDocument15 pagesDigital Electronics and Microcontroller Applications Winter 2019 Answer PaperShreyas KingeNo ratings yet

- Common To E&C, EI&C, CS&E & IS&E: Subject: Digital Electronics-1Document9 pagesCommon To E&C, EI&C, CS&E & IS&E: Subject: Digital Electronics-1Vikram RaoNo ratings yet

- Advantages of Digital SystemsDocument26 pagesAdvantages of Digital Systemsayyanar7No ratings yet

- ECE213: Digital Electronics Course OverviewDocument1 pageECE213: Digital Electronics Course OverviewAryan GourNo ratings yet

- Performance Comparison of LDPC Codes and Turbo CodesDocument8 pagesPerformance Comparison of LDPC Codes and Turbo CodesSinshaw BekeleNo ratings yet

- Digital Logic Design ModuleDocument322 pagesDigital Logic Design ModuleAklilu HailuNo ratings yet

- CS2031 Digital Logic Design OBE AdnanDocument4 pagesCS2031 Digital Logic Design OBE Adnanseemialvi6No ratings yet

- Digital Electronics TEE: CO1 CO2 CO3 CO4 CO5 CO6Document2 pagesDigital Electronics TEE: CO1 CO2 CO3 CO4 CO5 CO6Anonymous HyOfbJ6No ratings yet

- 2 MarkDocument28 pages2 Markcoolrammi19No ratings yet

- Digital Techniques VIVA ANSWERS 3rd SEMDocument6 pagesDigital Techniques VIVA ANSWERS 3rd SEMOSA MEMBERNo ratings yet

- Lectures No. 13 and 14: Channel CodingDocument13 pagesLectures No. 13 and 14: Channel CodingSateesh ChekuriNo ratings yet

- Digital System (Full PDFDocument150 pagesDigital System (Full PDFAmit RajputNo ratings yet

- Elliptic Curve Cryptography: Shane Almeida Saqib Awan Dan PalacioDocument37 pagesElliptic Curve Cryptography: Shane Almeida Saqib Awan Dan PalacioPhuc HoangNo ratings yet

- Fpga ImpDocument11 pagesFpga ImpDhivya rajanNo ratings yet

- Digital System DesignDocument318 pagesDigital System DesignNivetha ANo ratings yet

- Chapter 8 Digital ElectronicsDocument15 pagesChapter 8 Digital ElectronicsSai PrintersNo ratings yet

- An Efficient FPGA Implementation of IEEE 802.16e LDPC EncoderDocument56 pagesAn Efficient FPGA Implementation of IEEE 802.16e LDPC EncoderAnonymous cjzDyR6No ratings yet

- LDPCDocument40 pagesLDPCAli Subhi Al-SadiNo ratings yet

- Cour Se or Ient at Ion: Course Description: This Course Is The FirstDocument55 pagesCour Se or Ient at Ion: Course Description: This Course Is The FirstLeonelyn Hermosa Gasco - CosidoNo ratings yet

- Codes Decoding: Design and Analysis: Feng Lu Chuan Heng Foh, Jianfei Cai and Liang-Tien ChiaDocument5 pagesCodes Decoding: Design and Analysis: Feng Lu Chuan Heng Foh, Jianfei Cai and Liang-Tien ChiaViet Tuan NguyenNo ratings yet

- Digital Principle and System Design 2marks and 12 MarksDocument43 pagesDigital Principle and System Design 2marks and 12 MarksTamil Mani100% (1)

- LDPC - Low Density Parity Check CodesDocument6 pagesLDPC - Low Density Parity Check CodespandyakaviNo ratings yet

- B.SC Electronics - Digital Principles and Applications (.PDF) - Course Syllabus & Material - All Units (Bharathiar University)Document110 pagesB.SC Electronics - Digital Principles and Applications (.PDF) - Course Syllabus & Material - All Units (Bharathiar University)KUMARNo ratings yet

- G12cs-Ms-Preboard1 2022-23Document21 pagesG12cs-Ms-Preboard1 2022-23shabazdxb8No ratings yet

- Electronics 4Document4 pagesElectronics 4drkhamuruddeenNo ratings yet

- Digital Logic Design: Sessional Marks:40 End Exam: 3 Hours End Exam Marks:60Document2 pagesDigital Logic Design: Sessional Marks:40 End Exam: 3 Hours End Exam Marks:60R ChandrasekharNo ratings yet

- Comparison of Convolutional Codes With Block CodesDocument5 pagesComparison of Convolutional Codes With Block CodesEminent AymeeNo ratings yet

- 50ICRASE130513Document4 pages50ICRASE130513Kanaga VaratharajanNo ratings yet

- Iare de Lecture Notes PDFDocument147 pagesIare de Lecture Notes PDFRajkumar RajNo ratings yet

- Chapter I Review of Basics of Digital ElectronicsDocument21 pagesChapter I Review of Basics of Digital ElectronicsMia LateNo ratings yet

- Low Density Parity Check Codes1Document41 pagesLow Density Parity Check Codes1Prithvi RajNo ratings yet

- Digital ElectronicsDocument169 pagesDigital ElectronicsParthNo ratings yet

- Linear Block CodingDocument18 pagesLinear Block CodingPavuluri SairamNo ratings yet

- Digital Electronics Question Bank, Digital Electronics 2 Mark Questions & AnswersDocument22 pagesDigital Electronics Question Bank, Digital Electronics 2 Mark Questions & Answerssaipradeepkp92% (74)

- CEN-220 Digital Logic Design: Fall 2010 Instructor: Mansoor NaseerDocument47 pagesCEN-220 Digital Logic Design: Fall 2010 Instructor: Mansoor NaseerSohaib MaqsoodNo ratings yet

- Number System and RepresentationDocument4 pagesNumber System and RepresentationVani telluriNo ratings yet

- Obe Curriculum For The Course: RGPV (Diploma Wing) BhopalDocument22 pagesObe Curriculum For The Course: RGPV (Diploma Wing) BhopalHarshit Sahu CS-26No ratings yet

- Comparison Between E54 and EC41: Tashi Asst. Lecturer Ece, CST Rinchending, Phuentsholing Aug. 2012Document15 pagesComparison Between E54 and EC41: Tashi Asst. Lecturer Ece, CST Rinchending, Phuentsholing Aug. 2012tashidendupNo ratings yet

- Material DicaDocument157 pagesMaterial DicaganeshNo ratings yet

- Design of (15, 11) Hamming Code Encoding and Decoding System Based On FPGADocument4 pagesDesign of (15, 11) Hamming Code Encoding and Decoding System Based On FPGAenes yükselNo ratings yet

- Digital Circuits and SystemsDocument2 pagesDigital Circuits and SystemsSuvdeep NayakNo ratings yet

- Logic DesignDocument3 pagesLogic DesignHarsh BharadwajNo ratings yet

- Bebop to the Boolean Boogie: An Unconventional Guide to ElectronicsFrom EverandBebop to the Boolean Boogie: An Unconventional Guide to ElectronicsNo ratings yet

- Design of Solar Powered Induction Motor Drive For Pumping ApplicationDocument10 pagesDesign of Solar Powered Induction Motor Drive For Pumping Applicationollata kalanoNo ratings yet

- Labvolt Series 9063: Data Acquisition and Control InterfaceDocument2 pagesLabvolt Series 9063: Data Acquisition and Control Interfaceollata kalanoNo ratings yet

- Chapter 3Document66 pagesChapter 3ollata kalanoNo ratings yet

- DC-AC Converter-Inverter GuideDocument27 pagesDC-AC Converter-Inverter GuideYimy Garcia100% (1)

- Network Services and ApplicationsDocument50 pagesNetwork Services and Applicationsollata kalanoNo ratings yet

- ECEN 4517/5517 Spring 2020 Online Experiment 4, Part 1 SimulationDocument7 pagesECEN 4517/5517 Spring 2020 Online Experiment 4, Part 1 Simulationollata kalanoNo ratings yet

- Ee432 Power Electronics: Dr. Ali M. Eltamaly King Saud UniversityDocument79 pagesEe432 Power Electronics: Dr. Ali M. Eltamaly King Saud Universityollata kalanoNo ratings yet

- Lecture Notes Electrical Machines IV Code: CECE437 Level: Four Points: 100 25+15+60Document15 pagesLecture Notes Electrical Machines IV Code: CECE437 Level: Four Points: 100 25+15+60ollata kalanoNo ratings yet

- AI-ques-ans-Unit-1 Prof. Anuj Khanna KOITDocument17 pagesAI-ques-ans-Unit-1 Prof. Anuj Khanna KOITAmit RawatNo ratings yet

- Course Title of Energy Conversion and Rural ElectrificationDocument2 pagesCourse Title of Energy Conversion and Rural Electrificationollata kalano100% (1)

- ECEN 4797 Homework Assignment #1 AnalysisDocument3 pagesECEN 4797 Homework Assignment #1 Analysisollata kalanoNo ratings yet

- Formación de BUS matriz en presencia de elementos mutuamente acopladosDocument7 pagesFormación de BUS matriz en presencia de elementos mutuamente acopladoskinny1974No ratings yet

- ECEG-3131 Introduction to Electrical MachinesDocument52 pagesECEG-3131 Introduction to Electrical Machinesollata kalanoNo ratings yet

- Load Flow Analysis: Modeling of Power System ComponentsDocument8 pagesLoad Flow Analysis: Modeling of Power System ComponentsSai SivaNo ratings yet

- Chapter 21 Harmonic Analysis PSCADDocument48 pagesChapter 21 Harmonic Analysis PSCADgtgreat100% (3)

- Investigating Cable Transfer ImpedanceDocument11 pagesInvestigating Cable Transfer Impedanceollata kalanoNo ratings yet

- Harmonic Resonance Mode AnalysisDocument9 pagesHarmonic Resonance Mode AnalysisJorge CamposNo ratings yet

- Measurement and Calculation of Harmonics in Distribution Power System With Connected Small Co-Generation Facility EtanDocument4 pagesMeasurement and Calculation of Harmonics in Distribution Power System With Connected Small Co-Generation Facility Etanollata kalanoNo ratings yet

- Measurement and Calculation of Harmonics in Distribution Power System With Connected Small Co-Generation Facility EtanDocument4 pagesMeasurement and Calculation of Harmonics in Distribution Power System With Connected Small Co-Generation Facility Etanollata kalanoNo ratings yet

- From Several Sources To Be Routed Onto A Single LineDocument17 pagesFrom Several Sources To Be Routed Onto A Single Lineollata kalanoNo ratings yet

- Evaluating The Level of Harmonic Distortion in A Typical Distribu PDFDocument124 pagesEvaluating The Level of Harmonic Distortion in A Typical Distribu PDFollata kalanoNo ratings yet

- Final Template SampleDocument8 pagesFinal Template SamplelisaNo ratings yet

- Lecture 1Document28 pagesLecture 1Kamara KumaraNo ratings yet

- 5.60 Thermodynamics & Kinetics: Mit OpencoursewareDocument6 pages5.60 Thermodynamics & Kinetics: Mit OpencoursewarecaptainhassNo ratings yet

- Continuous: Sine WaveaDocument1 pageContinuous: Sine Waveaollata kalanoNo ratings yet

- Synopsis MphilDocument10 pagesSynopsis MphilAyesha AhmadNo ratings yet

- Cylinder Head Cover, 6T-830 and 6ta-830 Emissions Certified EngineDocument3 pagesCylinder Head Cover, 6T-830 and 6ta-830 Emissions Certified EngineJose A PerezNo ratings yet

- Toyota Camry ANCAP PDFDocument2 pagesToyota Camry ANCAP PDFcarbasemyNo ratings yet

- Nucleus ERPDocument3 pagesNucleus ERPdimensionone1No ratings yet

- Tutorial Chapter 1 Thermochemistry QuestionsDocument4 pagesTutorial Chapter 1 Thermochemistry Questionssiti nur masyitah nasaruddinNo ratings yet

- Sa Sem Iv Assignment 1Document2 pagesSa Sem Iv Assignment 1pravin rathodNo ratings yet

- Module 4.Document16 pagesModule 4.Sania MaqsoodNo ratings yet

- R7 Injection CheatSheet.v1Document1 pageR7 Injection CheatSheet.v1qweNo ratings yet

- Cosmos Carl SaganDocument18 pagesCosmos Carl SaganRabia AbdullahNo ratings yet

- Philippine Legal CitationDocument72 pagesPhilippine Legal CitationArwella GregorioNo ratings yet

- Gerunds vs InfinitivesDocument87 pagesGerunds vs InfinitivesDeby NavarroNo ratings yet

- HoraceDocument8 pagesHoraceapolonius31No ratings yet

- Mercury MasterDocument18 pagesMercury MastersatishmuggulaNo ratings yet

- DL1 - Epicyclic Gear Train & Holding Torque ManualDocument4 pagesDL1 - Epicyclic Gear Train & Holding Torque Manualer_arun76100% (1)

- Bi006008 00 02 - Body PDFDocument922 pagesBi006008 00 02 - Body PDFRamon HidalgoNo ratings yet

- 9607 Syllabus Media StudiesDocument28 pages9607 Syllabus Media StudiesmisterNo ratings yet

- Ooplabmanual 150412132629 Conversion Gate01 PDFDocument146 pagesOoplabmanual 150412132629 Conversion Gate01 PDFyawerjs33% (6)

- Piperack Design PhiloshipyDocument10 pagesPiperack Design PhiloshipyGautam PaulNo ratings yet

- Phrase Structure AnalysisDocument2 pagesPhrase Structure Analysismerlino99No ratings yet

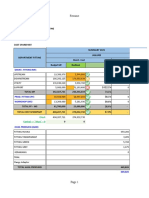

- Resume summary of monthly sparepart costs and production in 2021Document590 pagesResume summary of monthly sparepart costs and production in 2021winda listya ningrumNo ratings yet

- UID Module Wise TopicsDocument3 pagesUID Module Wise TopicsPavan KumarNo ratings yet

- Circuit Breaker GTSDocument31 pagesCircuit Breaker GTScpandey01_688066930No ratings yet

- Tda7266 PDFDocument9 pagesTda7266 PDFRenato HernandezNo ratings yet

- TOS - MathDocument4 pagesTOS - MathGeorge Ezar N. QuiriadoNo ratings yet

- Efficiently Transfer Stock Between PlantsDocument6 pagesEfficiently Transfer Stock Between PlantsSantosh KumarNo ratings yet

- Management Science PDFDocument131 pagesManagement Science PDFAngela Lei SanJuan BucadNo ratings yet

- In2it: A System For Measurement of B-Haemoglobin A1c Manufactured by BIO-RADDocument63 pagesIn2it: A System For Measurement of B-Haemoglobin A1c Manufactured by BIO-RADiq_dianaNo ratings yet

- BfgsDocument10 pagesBfgshusseinNo ratings yet

- Writing Visual Basic ProjectsDocument1 pageWriting Visual Basic ProjectsAmmuKuttyNo ratings yet